数字集成电路课后习题1-4章作业解析

数字电子技术基础第四章习题及参考答案

数字电子技术基础第四章习题及参考答案第四章习题1.分析图4-1中所示的同步时序逻辑电路,要求:(1)写出驱动方程、输出方程、状态方程;(2)画出状态转换图,并说出电路功能。

CPY图4-12.由D触发器组成的时序逻辑电路如图4-2所示,在图中所示的CP脉冲及D作用下,画出Q0、Q1的波形。

设触发器的初始状态为Q0=0,Q1=0。

D图4-23.试分析图4-3所示同步时序逻辑电路,要求:写出驱动方程、状态方程,列出状态真值表,画出状态图。

CP图4-34.一同步时序逻辑电路如图4-4所示,设各触发器的起始状态均为0态。

(1)作出电路的状态转换表;(2)画出电路的状态图;(3)画出CP作用下Q0、Q1、Q2的波形图;(4)说明电路的逻辑功能。

图4-45.试画出如图4-5所示电路在CP波形作用下的输出波形Q1及Q0,并说明它的功能(假设初态Q0Q1=00)。

CPQ1Q0CP图4-56.分析如图4-6所示同步时序逻辑电路的功能,写出分析过程。

Y图4-67.分析图4-7所示电路的逻辑功能。

(1)写出驱动方程、状态方程;(2)作出状态转移表、状态转移图;(3)指出电路的逻辑功能,并说明能否自启动;(4)画出在时钟作用下的各触发器输出波形。

CP图4-78.时序逻辑电路分析。

电路如图4-8所示:(1)列出方程式、状态表;(2)画出状态图、时序图。

并说明电路的功能。

1C图4-89.试分析图4-9下面时序逻辑电路:(1)写出该电路的驱动方程,状态方程和输出方程;(2)画出Q1Q0的状态转换图;(3)根据状态图分析其功能;1B图4-910.分析如图4-10所示同步时序逻辑电路,具体要求:写出它的激励方程组、状态方程组和输出方程,画出状态图并描述功能。

1Z图4-1011.已知某同步时序逻辑电路如图4-11所示,试:(1)分析电路的状态转移图,并要求给出详细分析过程。

(2)电路逻辑功能是什么,能否自启动?(3)若计数脉冲f CP频率等于700Hz,从Q2端输出时的脉冲频率是多少?CP图4-1112.分析图4-12所示同步时序逻辑电路,写出它的激励方程组、状态方程组,并画出状态转换图。

数字集成电路习题答案

1.5 115 106

0.63 3 0.06 0.1

30 106

1.0

21.05

VIL

VM

VDD VM g

1.25 2.5 1.25 21.05

1.19V

VIH

VM

VM g

1.25 1.25 21.05

1.31V

NVH VDD VIH 2.5 1.31 1.19 NM L VIL 1.19

115 (2.072 2.072 )(1 0.06 2.5) 2

283.3A

(2) pmos :

VGT VGS VT 0 0.5 0.4 0.1 VDS

pmos处于饱和区,Vmin 0.1v

ID

kn'

(W L

) (VGTVm in

Vm2in 2

)(1

VDS

)

30 (0.1 0.05) 0.1 (1 0.11.25)

VT0(V) 0.43 -0.4

(V0.5) 0.4 -0.4

VDSAT(V) 0.63 -1

k’(A/V2) 115×10-6 -30×10-6

(V-1) 0.06 -0.1

1.假设设计一个通用0.25m CMOS工艺的反相器,其中PMOS晶体管的 最小尺寸为(W=0.75m,L=0.25m,即W/L=0.75/0.25) , NMOS晶体管

2.如下图所示,由NMOS组成的反相器,输出电容 CL=3pF,W/L=1.5um/0.5um,求tpHL,tpLH和tp

t pHL

ln 2ReqnCL

0.69 13k 3

3 pF

8.97ns

t pLH ln 2RLCL 0.69 75k 3 pF 155.25ns

康华光《电子技术基础-数字部分》(第5版)课后习题-第一章至第四章【圣才出品】

(1)(43)D=(101011)B=(53)O=(2B)H;

3 / 111

表 1-1

解:由表 1-1 可知,(1)、(5)属于超大规模集成电路;(2)、(3)属于中规模集成电 路;(4)属于小规模集成电路。

1.1.2 一数字信号波形如图 1-1 所示,试问该波形所代表的二进制数是什么?

图 1-1 解:低电平用 0 表示,高电平用 1 表示,则图 1-1 所示波形用二进制可表示为: 010110100。

1.2.6 将下列十六进制数转换为十进制数:

(1)(103.2)H (2)(A45D.0BC)H

解:(1) 103.2H

1162

3160

2 16 1

259.125

D

;

同理(2) A45D.0BC H

42077.0459

D

。

1.3 二进制的算术运算

1.3.1 写出下列二进制数的原码、反码和补码: (1)(+1110)B (2)(+10110)B (3)(-1110)B (4)(-10110)B 解:正数的反码、补码与原码相同,负数的反码等于原码的数值位逐位取反,负数的补 码等于反码加 1。

图 1-2 1.1.4 一周期性数字波形如图 1-3 所示,试计算:(1)周期;(2)频率;(3)占空比。

图 1-3

解:由图 1-3 可知该波形为周期性数字波形,则有

周期:T=11 ms-1 ms =10 ms(两相邻上升沿之差);

四篇-1章浙大版集成电路课后答案(汇编)

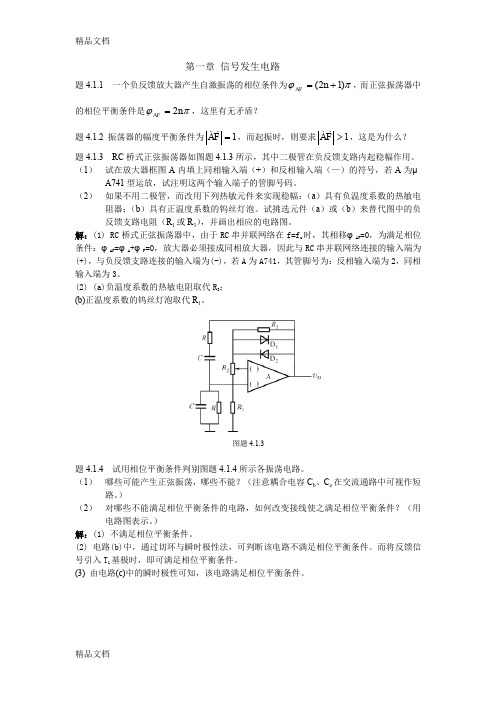

第一章 信号发生电路题4.1.1 一个负反馈放大器产生自激振荡的相位条件为πϕ)12(+=n AF ,而正弦振荡器中的相位平衡条件是πϕn AF 2=,这里有无矛盾?题4.1.2 振荡器的幅度平衡条件为1=F A,而起振时,则要求1>F A ,这是为什么? 题4.1.3 RC 桥式正弦振荡器如图题4.1.3所示,其中二极管在负反馈支路内起稳幅作用。

(1) 试在放大器框图A 内填上同相输入端(+)和反相输入端(—)的符号,若A 为μA741型运放,试注明这两个输入端子的管脚号码。

(2) 如果不用二极管,而改用下列热敏元件来实现稳幅:(a )具有负温度系数的热敏电阻器;(b )具有正温度系数的钨丝灯泡。

试挑选元件(a )或(b )来替代图中的负反馈支路电阻(R 1或R 3),并画出相应的电路图。

解:(1) RC 桥式正弦振荡器中,由于RC 串并联网络在f=f o 时,其相移φAF =0,为满足相位条件:φAF =φA +φF =0,放大器必须接成同相放大器,因此与RC 串并联网络连接的输入端为(+),与负反馈支路连接的输入端为(-),若A 为A741,其管脚号为:反相输入端为2,同相输入端为3。

(2) (a)负温度系数的热敏电阻取代R 3; (b)正温度系数的钨丝灯泡取代R 1。

图题4.1.3题4.1.4 试用相位平衡条件判别图题4.1.4所示各振荡电路。

(1) 哪些可能产生正弦振荡,哪些不能?(注意耦合电容C b 、C e 在交流通路中可视作短路。

)(2) 对哪些不能满足相位平衡条件的电路,如何改变接线使之满足相位平衡条件?(用电路图表示。

)解:(1) 不满足相位平衡条件。

(2) 电路(b)中,通过切环与瞬时极性法,可判断该电路不满足相位平衡条件。

而将反馈信号引入T 1基极时,即可满足相位平衡条件。

(3) 由电路(c)中的瞬时极性可知,该电路满足相位平衡条件。

图题4.1.4题4.1.5 电路如图题4.1.5所示,稳压管D z 起稳幅作用,其稳定电压±V Z =±6V 。

电子技术相关 《数字集成电路基础》作业答案

《数字集成电路基础》作业答案第一次作业1、查询典型的TTL与CMOS系列标准电路各自的VIH、VIL、VOH和VOL,注明资料出处。

2、简述摩尔定律的内涵,如何引领国际半导体工艺的发展。

第二次作业1、说明CMOS电路的Latch Up效应;请画出示意图并简要说明其产生原因;并简述消除“Latch-up”效应的方法。

答:在单阱工艺的MOS器件中(P阱为例),由于NMOS管源与衬底组成PN结,而PMOS 管的源与衬底也构成一个PN结,两个PN结串联组成PNPN结构,即两个寄生三极管(NPN 和PNP),一旦有因素使得寄生三极管有一个微弱导通,两者的正反馈使得电流积聚增加,产生自锁现象。

影响:产生自锁后,如果电源能提供足够大的电流,则由于电流过大,电路将被烧毁。

消除“Latch-up”效应的方法:版图设计时:为减小寄生电阻Rs和Rw,版图设计时采用双阱工艺、多增加电源和地接触孔数目,加粗电源线和地线,对接触进行合理规划布局,减小有害的电位梯度;工艺设计时:降低寄生三极管的电流放大倍数:以N阱CMOS为例,为降低两晶体管的放大倍数,有效提高抗自锁的能力,注意扩散浓度的控制。

为减小寄生PNP管的寄生电阻Rs,可在高浓度硅上外延低浓度硅作为衬底,抑制自锁效应。

工艺上采用深阱扩散增加基区宽度可以有效降低寄生NPN管的放大倍数;具体应用时:使用时尽量避免各种串扰的引入,注意输出电流不易过大。

2、什么是器件的亚阈值特性,对器件有什么影响?答:器件的亚阈值特性是指在分析MOSFET时,当Vgs<Vth时MOS器件仍然有一个弱的反型层存在,漏源电流Id并非是无限小,而是与Vgs呈现指数关系,这种效应称作亚阈值效应。

影响:亚阈值导电会导致较大的功率损耗,在大型电路中,如内存中,其信息能量损耗可能使存储信息改变,使电路不能正常工作。

3、什么叫做亚阈值导电效应?并简单画出logI D-V GS特性曲线。

答:GS在分析MOSFET时,我们一直假设:当V GS下降到低于V TH时器件会突然关断。

数字电路第五版课后答案

第一章数字逻辑习题1.1 数字电路与数字信号图形代表的二进制数1.1.4 一周期性数字波形如图题所示,试计算:(1)周期;(2)频率;(3)占空比例MSB LSB0 1 2 11 12 (ms)解:因为图题所示为周期性数字波,所以两个相邻的上升沿之间持续的时间为周期,T=10ms 频率为周期的倒数,f=1/T=1/=100HZ占空比为高电平脉冲宽度与周期的百分比,q=1ms/10ms*100%=10%数制将下列十进制数转换为二进制数,八进制数和十六进制数(要求转换误差不大于2−4(2)127 (4)解:(2)(127)D= 27 -1=()B-1=(1111111)B=(177)O=(7F)H(4)()D=B=O=H二进制代码将下列十进制数转换为 8421BCD 码:(1)43 (3)解:(43)D=(01000011)BCD试用十六进制写书下列字符繁荣ASCⅡ码的表示:P28(1)+ (2)@ (3)you (4)43解:首先查出每个字符所对应的二进制表示的ASCⅡ码,然后将二进制码转换为十六进制数表示。

(1)“+”的ASCⅡ码为 0101011,则(00101011)B=(2B)H(2)@的ASCⅡ码为 1000000,(01000000)B=(40)H(3)you 的ASCⅡ码为本 1111001,1101111,1110101,对应的十六进制数分别为 79,6F,75(4)43 的ASCⅡ码为 0110100,0110011,对应的十六紧张数分别为 34,33逻辑函数及其表示方法在图题 1. 中,已知输入信号 A,B`的波形,画出各门电路输出 L 的波形。

解: (a)为与非, (b)为同或非,即异或第二章逻辑代数习题解答用真值表证明下列恒等式(3)A⊕ =B AB AB+ (A⊕B)=AB+AB解:真值表如下由最右边2栏可知,A⊕B与AB+AB的真值表完全相同。

用逻辑代数定律证明下列等式(3)A+ABC ACD C D E A CD E++ +( ) = + +解:A+ABC ACD C D E++ +( )=A(1+BC ACD CDE)+ += +A ACD CDE+= +A CD CDE+ = +A CD+ E用代数法化简下列各式 (3)ABC B( +C)解:ABCB( +C)= + +(A B C B C)( + )=AB AC BB BC CB C+ + + + +=AB C A B B+ ( + + +1)=AB C+(6)(A + + + +B A B AB AB ) ( ) ( )() 解:(A + + + +B A B AB AB ) () ( )( )= A B ⋅+ A B ⋅+(A + B A )(+ B )=AB(9)ABCD ABD BCD ABCBD BC + + + +解:ABCD ABD BCD ABCBD BC +++ +=ABC D D ABD BC D C ( + +) + ( + ) =B AC AD C D ( + + + ) =B A C AD ( + + + ) =B A C D ( + + ) =AB BC BD + +画出实现下列逻辑表达式的逻辑电路图,限使用非门和二输入与非门B AB AB = + + AB B = + A B = +(1)L AB AC =(2) ( ) L DAC = +已知函数L (A ,B ,C ,D )的卡诺图如图所示,试写出函数L 的最简与或表达式用卡诺图化简下列个式(3) ( )() L ABCD=+ +解: ( , , , ) L ABCDBCDBCDBCDABD = + + +(1)ABCD ABCD AB AD ABC+ + + +解:ABCD ABCD AB AD ABC+ + + +=ABCD ABCD ABC C D D AD B B C C ABC D D++ ( + )( + +)( + )( + +)( + )=ABCD ABCD ABCD ABCD ABCD ABCD ABCD+ + + + + +(6)L A B C D( , , , )=∑m(0,2,4,6,9,13)+∑d(1,3,5,7,11,15)解:L= +A D(7)L A B C D( , , , )=∑m(0,13,14,15)+∑d(1,2,3,9,10,11)解:L AD AC AB= + +已知逻辑函数L AB BC CA=+ + ,试用真值表,卡诺图和逻辑图(限用非门和与非门)表示解:1>由逻辑函数写出真值表用摩根定理将与或化为与非表达式L = AB + BC + AC = AB BC AC ⋅ ⋅4>由已知函数的与非-与非表达式画出逻辑图2> 由真值表画出卡诺图3> 由卡诺图,得逻辑表达式 LABBCAC = + +第三章习题MOS 逻辑门电路根据表题所列的三种逻辑门电路的技术参数,试选择一种最合适工作在高噪声环境下的门电路。

数字电子技术基础(第4版)课后习题答案详解

(9)Y = BC + AD + AD

1.9 (a) Y = ABC + BC

(10)Y = AC + AD + AEF + BDE + BDE (b) Y = ABC + ABC

(c) Y1 = AB + AC D,Y2 = AB + AC D + ACD + ACD

(d) Y1 = AB + AC + BC,Y2 = ABC + ABC + ABC + ABC 1.10 求下列函数的反函数并化简为最简与或式

(1)Y = AC + BC

(2)Y = A + C + D

(3)Y = (A + B)( A + C)AC + BC 解:Y = ( A + B)(A + C)AC + BC = [( A + B)( A + C) + AC]⋅ BC = ( AB + AC + BC + AC)(B + C) = B + C

= 0.05mA <

I

,

B

∴

T饱和,

v o=0.2V

(0

~

0.3V都行)

2.3 解:

s 闭合时,输入低电平,此时

VIL = R2 × 5I I′L ≤ 0.4V

R2

≤

0.4 5I I′L

=

0.4V 2mA

= 200Ω

s 断开时,输入为高电平,此时

R2的最大允许值为200Ω

VIH = Vcc − (R1 + R2 ) × 5I IH ≥ 4V ∴ R1最大允许值为10K-R 2

第1章数字电路和集成逻辑门电路习题解答

第1章数字电路和集成逻辑门电路习题解答思维题和习题1-1填空题1)三极管截止条件为UBE ≤0V三极管饱和导通条件为IB≥IBS三极管饱和导通的IBS为IBS ≥ (VCC-UCES)/β RC2)当栅极电路输出为高电平时的负载是拉电流负载,当输出为低电平时的负载是填充电流负载3)当晶体管用作电子开关时,其工作状态必须是饱和或关断4)74LTL电路的电源电压值和输出电压的高低电平值分别约为5V、2.7V和0.5V74TTL电路的电源电压值和输出电压的高低电平值分别约为5V、2.4V和0.4V5)OC门被称为开集电极门。

多个OC门输出可以并联实现线路和功能CMOS门电路的输入电流始终为零7)不能暂停CMOS门电路的空闲输入。

与门应连接到高电平,或门应连接到低电平。

1-2选择题1) abc常用于以下电路中的总线应用A。

TSL门电路、0C门电路、漏极开路门电路、互补金属氧化物半导体与非门(2)TTL与非门有n个同类门电路,低电平输入电流为1.5毫安,高电平输入电流为10毫安,最大填充电流为15毫安,最大拉电流为400毫安。

选择正确答案n和最多b。

a . n = 5b . n = 10c . n = 20d . n = 403)与TTL数字集成电路相比,CMOS数字集成电路的突出优势是ACD A。

当三极管用作开关时,为了提高开关速度,da .降低饱和深度b .增加饱和深度c .采用有源漏极电路d .采用反饱和三极管5)进行TTL与非门空闲输入处理,可以使用ABDa。

连接到电源b,连接到电源c,连接到地d,通过电阻3kω并联连接到有用输入6)。

光盘可以在以下电路中实现“线和”功能当A与非门b三态输出门c打开集电极门d打开漏极门7)三态门输出高阻抗状态时,ABD是正确的a .使用电压表测量指针不动b .相当于暂停c .电压不是高或低d .测量电阻指针不动8)已知正向电压降UD = 1.7V,参考工作电流ID = 10mA,TTL门的输出高和低电平分别为UOH = 3.6V,UOL = 0.3V,允许充电电流和牵引电流分别为IOL = 15mA,IOH = 4mA那么电阻r应该选择d。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

VOH = VGG − VT = VDD − VT 0 + γ

(

(V

SB

+ 2 φf − 2 φf

))

= VGG − VT 0 − γ VOH + 2 φ f + γ 2 φ f = 1.6 − 0.4 − 0.2 VOH + 0.88 + 0.2 0.88 = 1.388 − 0.2 VOH + 0.88

QOX 6 ×1011 ×1.6 ×10−19 0.06 V = = COX 1.6 ×10−6 VT0 =−0.99 − (−0.88) − (−0.188) − 0.060 =+0.018 V

计算 PMOS 器件的阈值电压: kT N D 3 ×1017 = φFn = ln 0.026 ln = 0.44 V q ni 1.4 ×1010

VOL 2 (0.1×10−4 )(8 ×106 )(1.6 − VOL − 0.4) 2 1 270 1.2 0.4 V − − ( ) OL = 0.1 VOL 2 (1.6 − VOL − 0.4) + 0.6 1 + 0.6

+0.99 V φGC = φFn − φG ( gate ) = 0.44 + 0.55 = QB 0 3 ×10−7 = = +0.188 V QB 0 = 3 ×10−7 C / cm 2 COX 1.6 ×10−6 QOX 6 ×1011 ×1.6 ×10−19 = = 0.06 V COX 1.6 ×10−6 VT0 =0.99 − (+0.88) − (+0.188) − 0.060 =−0.138 V

VOH = 1.11V 由此可知,VGG 实际要大于 1.6 V,接近 1.7 V,才能使 VOH 达到 1.2 V。 计算 VOL 时忽略体效应, ∴

µ N Cox WI LI VOL 1 + ECN LI

VOL 2 WLν sat Cox (VGG − VOL − VTL ) 2 V − V V − ) ( DD TI OL = 2 (VGG − VOL − VTL ) + ECN LL

可算得: F =AB + AC + BC =( A + B )( A + C )( B + C )

b. F = DC A + DCA + D A C + D CA D AC 0 1 00 01 0 0 1 1 Table 3 11 1 0 10 1 0

可算得:

F =D A + DA =( A + D ) ( A + D )

ρ

P4.1. 见图 P4.1。 a. 当输入为高电平时,除了 CMOS 反相器以外的其它反相器都需要消耗静态功 耗。对于前三个反相器而言,当输入为高电平的时候,总是有一个静态电流从 VDD 流向 GND。 b. 当输入为低电平时,所有反相器都不消耗静态功耗,因为 VDD 和 GND 之间是 断开的。 c. 除了饱和增强型反相器外,其它反相器的 VOH 都为 1.2 V。 d. 只有 CMOS 反相器的 VOL 为 0 V。 e. 除了 CMOS 反相器,其它反相器的工况都取决于晶体管(负载和反相)的尺寸 比。

(d) 晶体管工作在饱和区: I DS = Wν sat Cox (VGS − VT ) 2 (VGS − VT ) + Ec L

= (0.4)10−4 (8 ×106 )(1.6 ×10−6 ) I DS

(0.8 − 0.4) 2 = 82 µ A (0.8 − 0.4) + 0.6

P3.11 促使互连线从 Al 转换到 Cu 的主要因素是互联电阻和电迁移(Electromigration)。因 为铜的电阻率更小,同时不易受电迁移的影响。但铜也有自身的问题,它容易氧 化,因此铜线需要包覆起来,防止氧化。 开发低 K 电介质,主要是为了减少信号延迟和互连线间的电容耦合。目标值为 2。 开发高 K 电介质是用来作为 MOS 器件的栅氧化层。它在保持栅电容不变的情况下 允许栅氧化层做得厚一些,因此可以有效地减少栅极与衬底间的漏电流,提高器件 的可靠性。

P1.3 a.

F AB + BC =

= AB + BC = AB + BC

A B C

b.

F = A⊕ B ⊕C

= ABC + ABC + ABC + ABC = ABC + ABC + ABC + ABC = ABC ⋅ ABC ⋅ ABC ⋅ ABC

P2.1

a) 零偏压阈值电压 VT0 计算公式为 VT 0 =VFB − 2φF −

VOH = 0.734 V

计算 VOL 时忽略体效应,

∴

µN WI LI VOL 1 + ECN LI

VOL 2 WLν sat (VDD − VOL − VTL ) 2 V − V V − ( ) DD TI OL = 2 (VDD − VOL − VTL ) + ECN LL

qN I = QI NI = QI q

对于(a)中的 NMOS 器件: Q 0.6 ×10−6 NI = − I = − = 3.82 ×1012 ions / cm 2 (P 型) q 1.6 ×10−19 对于(a)中的 PMOS 器件:

QI (1.6 ×10−6 )(0.4 − 0.138) 2.62 ×1012 ions / cm 2 (N 型) − = − = NI = −19 1.6 ×10 q

P1.1

先构建真值表,再依据真值表画出卡诺图。然后找到 1 作为积之和,找到 0 作为和 之积。 a. F = CBA + CBA + CBA + CBA A 0 0 0 0 1 1 1 1 C AB 0 1 B C 0 0 0 1 1 0 1 1 0 0 0 1 1 0 1 1 Table 1 00 01 0 0 0 1 Table 2 F 0 0 0 1 0 1 1 1 11 1 1 10 0 1

QB COX

计算每个部分得到 NMOS 阈值电压:

ln i = −0.026 ln = −0.44 V φFp = 10 −0.44 − 0.55 = −0.99 V φGC =− φFp φG ( gate ) = 4ε 0 = 3.5 ×10−13 F/cm ε OX = QB 0 =−3 ×10−7 C / cm 2 COX = 1.6 ×10−6 F/cm 2 QB 0 −3 ×10−7 = =−0.188 V COX 1.6 ×10−6 kT q n NA 3 ×1017 1.4 ×10

P4.2. 见图 P4.2。 a. 电阻负载型 VOH = VDD VOL = VDD VDD = 1 + kRL (VDD − VT ) 1 + µ C W R V − V N OX L ( DD T) L 1.2 = 0.034 V 1 1 + ( 270 ) (1.6 ×10−6 ) (10 ×103 ) (1.2 − 0.4 ) 0.1

b. 饱和增强型

VOH = VDD − VT = VDD − VT 0 + γ

(

(V

SB

+ 2 φf − 2 φf

))

= VDD − VT 0 − γ VOH + 2 φ f + γ 2 φ f = 1.2 − 0.4 − 0.2 VOH + 0.88 + 0.2 0.88 = 0.988 − 0.2 VOH + 0.88

P2.4

指导方针:比较 VGS 和 VT 决定器件导通与否(此处的 VT 可能涉及到体效应)。另 外,还要比较 VDS 和 VDSAT 来判断是在线性区还是饱和区。 a. 截止 VGS = VG − VS = 0.2 − 0 = 0.2V V = V = 0.4V T T0 ∴ VGS < VT b. 截止 VGS = VG − VS = 1.2 − 1.1 = 0.1V = = V V 0.4V T T0 ∴ VGS < VT c. 线性 VGS = VG − VS = 1.2 − 0 = 1.2V = = V V 0.4V T T0 ∴ VGS > VT 不在饱和区的判断依据: = VDSAT VGS − VT ) EC L (1.2 − 0.4 )( 6 )( 0.2 ) (= = VGS − VT + EC L 1.2 − 0.4 + ( 6 )( 0.2 ) VDS = 0.2V ∴ VDS < VDSAT d. 饱和 VGS>VT , VD > VG 肯定工作在饱和区。对于长沟道器件,如果满足这个关系 就工作在饱和区。而发生速度饱和的短沟道器件的 VDSAT 比长沟道器件的要 小,如果电压偏置能使长沟道器件饱和,那么肯定能使速度饱和的短沟道器件 饱和。 0.48V

P2.5

先计算 VG 对应的 VX 最大值,如果这个值小于漏极电压 VD,那么 VX = VX ,max ,否则 VX = VD 。 VX 最大值为 VG − VT ,由于体效应的存在,此处的 VT ≠ VT 0 。 VX ,max = VG − VT = VG − VT 0 + γ =VG − VT 0 − γ

对于(b)中的 PMOS 器件: Q (1.6 ×10−6 )(1.24 − 0.4) − I = − = 8.4 ×1012 ions / cm 2 (P 型) NI = −19 q 1.OS 用 N 型多晶硅栅和 PMOS 用 P 型多晶硅栅算得的阈值 电压比较小,在沟道区使用与衬底相同的离子掺杂即可调整到期望值(NMOS:P 型注 入;PMOS:N 型注入)。如果我们在 MOS 管的栅极中采用跟衬底相同类型的离子注 入,得到的阈值电压很大,偏离期望值很多,调整起来比较困难。另外,源极和漏极 的制作过程采用自对准工艺,如果栅极的注入类型和源漏一致,一步即可完成离子注 入,简化了器件制作的工艺流程。