异步串行通信接口实验

DSP实验手册 实验三 异步串口实验

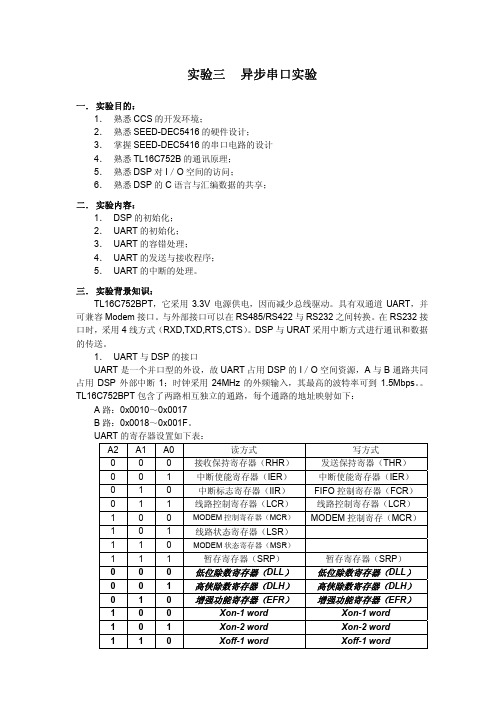

实验三异步串口实验一. 实验目的:1.熟悉CCS的开发环境;2.熟悉SEED-DEC5416的硬件设计;3.掌握SEED-DEC5416的串口电路的设计4.熟悉TL16C752B的通讯原理;5.熟悉DSP对I/O空间的访问;6.熟悉DSP的C语言与汇编数据的共享;二. 实验内容:1. DSP的初始化;2. UART的初始化;3. UART的容错处理;4. UART的发送与接收程序;5. UART的中断的处理。

三. 实验背景知识:TL16C752BPT,它采用3.3V电源供电,因而减少总线驱动。

具有双通道UART,并可兼容Modem接口。

与外部接口可以在RS485/RS422与RS232之间转换。

在RS232接口时,采用4线方式(RXD,TXD,RTS,CTS)。

DSP与URAT采用中断方式进行通讯和数据的传送。

1. UART与DSP的接口UART是一个并口型的外设,故UART占用DSP的I/O空间资源,A与B通路共同占用DSP外部中断1;时钟采用24MHz的外频输入,其最高的波特率可到1.5Mbps。

TL16C752BPT包含了两路相互独立的通路,每个通路的地址映射如下:A路:0x0010~0x0017B路:0x0018~0x001F。

UART的寄存器设置如下表:A2 A1 A0 读方式写方式0 0 0 接收保持寄存器(RHR)发送保持寄器(THR)0 0 1 中断使能寄存器(IER)中断使能寄存器(IER)0 1 0 中断标志寄存器(IIR) FIFO控制寄存器(FCR)0 1 1 线路控制寄存器(LCR)线路控制寄存器(LCR)1 0 0 MODEM控制寄存器(MCR)MODEM控制寄存(MCR)1 0 1 线路状态寄存器(LSR)1 1 0 MODEM状态寄存器(MSR)1 1 1 暂存寄存器(SRP)暂存寄存器(SRP)0 0 0 低位除数寄存器(DLL)低位除数寄存器(DLL)0 0 1 高侠除数寄存器(DLH)高侠除数寄存器(DLH)0 1 0 增强功能寄存器(EFR)增强功能寄存器(EFR)1 0 0 Xon-1 word Xon-1 word1 0 1 Xon-2 word Xon-2 word1 1 0 Xoff-1 word Xoff-1 word1 1 1 Xoff-2 word Xoff-2 word1 1 0 发送控制寄存器(TCR ) 发送控制寄存器(TCR ) 1 1 1 触发等级寄存器(TLR ) 触发等级寄存器(TLR )黑斜体的部分为二次寻址的寄存器。

接口实验报告8251

实验报告实验名称__8251A串行口实验____课程名称__微机原理与接口技术__院系部: 专业班级:学生姓名:学号:同组人: 实验台号:指导教师: 成绩:实验日期:华北电力大学一、实验目的及要求:(1)了解串行通信的一般原理和8251A的工作原理。

(2)掌握8251A的编程方法。

二、仪器用具:三、实验原理:1.串行通信的原理串行通信是通过一位一位地进行数据传输来实现通信。

具有传输线少,成本低等优点,适合远距离传送;缺点是速度慢。

完成串行通信任务的接口称为串行通信接口,简称串行接口。

串行接口作为输入时,完成串行到并行格式转换,作为输出时,完成并行到串行格式转换。

图1是串行通信的一般模型。

图1 串行通信的一般模型2.8251A的工作原理825lA是可编程的串行通信接口芯片,是Intel公司生产的一种通用同步/异步数据收发器(USART),可工作在同步方式,也可工作在异步方式,且能进行出错检测。

其内部结构框图如图2所示。

图2 8251A内部结构框图由图可知,8251A由数据总线缓冲器、读/写控制逻辑、调制/解调器控制逻辑、发送缓冲器、发送控制器、接收缓冲器、接收控制器等组成。

(1)在同步方式时,每个字符可定义为5、6、7或8位。

两种方法实现同步,由内部自动检测同步字符或由外部给出同步信号。

允许同步方式下增加奇/偶校验位进行校验。

(2)在异步方式下,每个字符可定义为5、6、7或8位,用1位作奇偶校验。

时钟速率可用软件定义为波特率的l、16或64倍。

另外,8251A在异步方式下能自动为每个被输出的数据增加1个起始位,并能根据软件编程为每个输出数据设置1位、1.5位或2位停止位。

(3)能进行出错检测。

带有奇偶、溢出和帧错误等检测电路,用户可通过输入状态寄存器的内容进行查询。

3.8251A的编程(1)8251A的编程地址:8251A只需要两个端口地址,一个用于数据端口,一个用于控制端口。

数据输入输出用读信号RD和写WR信号区分;状态端口只能读不能写,控制端口只能写不能读。

最新异步通信控制器--课程设计实验报告1

三、输入原文件(带注释VHDL源程序)

(1)异步发送模块VHDL源代码:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY transmitter IS --定义发送模块实体,实体名transmitter

1、程序中主要用到了发送双缓冲和计数器。发送双缓冲:包括‘发送缓冲寄存器TB(Tx Buffer)’和‘发送移位寄存器TS(Tx Shifter)’;TB用于暂时存储输入的8位数据,TS用于移位输出(并串变换)。计数器代替状态机用于状态控制计数,用来指示数据发送完成。

2、实验中设置发送字长=8位,最高位是奇校验位;发送停止位至少为1位;另外,为了发送的准确性,要求发送速率由发送时钟TCLK输入确定,是TCLK频率的1/8。

WHEN S3=>

IF RXD='0' THEN

STATE<=S4;LDSR<='0';LDRB<='0';SCLK<='1';FE<='0';

ELSE

STATE<=S0;LDSR<='0';LDRB<='0';SCLK<='0';FE<='0';

dsp实验报告哈工大实验二异步串口通信实验

dsp实验报告哈工大实验二异步串口通信实验异步串口通信实验一. 实验目的1. 了解*****F2407A DSP 片内串行通信接口(SCI)的特点。

2. 学会设置SCI 接口进行通信。

3. 了解ICETEK-LF2407-A 板上对SCI 接口的驱动部分设计。

4. 学习设计异步通信程序。

二. 实验设备计算机,ICETEK-LF2407-EDU 实验箱(或ICETEK 仿真器+ICETEK-LF2407-A 系统板+相关连线及电源)。

三. 实验原理1. *****F2407A DSP 串行通信接口模块*****F240x 器件包括串行通信接口SCI 模块。

SCI 模块支持CPU 与其他使用标准格式的异步外设之间的数字通信。

SCI 接收器和发送器是双缓冲的,每一个都有它自己单独的使能和中断标志位。

两者都可以独立工作,或者在全双工的方式下同时工作。

2. ICETEK-LF2407-A 板异步串口设计由于DSP 内部包含了异步串行通信控制模块,所以在板上只需加上驱动电路部分即可。

驱动电路主要完成将SCI 输出的0-3.3V 电平转换成异步串口电平的工作。

转换电平的工作由MAX232 芯片完成,但由于它是5V 器件所以它同DSP 间的信号线必须有电平转换,此板采用的是74LS245。

3. 串行通信接口设置CPU 进行串行通信时可以采用两种方式,一种是轮询方式,即CPU 不断查询串口状态进行接收和发送,缺点是占用CPU 时间太多;另一种是中断方式,SCI 的接收和发送都可以产生中断信号,这样CPU 可以在完成其他一些工作的同时进行串行通信。

串行通信接口波特率计算,内部生成的串行时钟由系统时钟SYSCLK 频率和波特率选择寄存器决定。

串行通信接口使用16 位波特率选择寄存器,数据传输的速度可以被编程为***** 多种不同的方式。

不同通信模式下的串行通信接口异步波特率由下列方法决定:BRR=1―***** 时的串行通信接口异步波特率:SCI 异步波特率=SYSCLK/ [( BRR+1)*8]其中,BRR=SYSCLK/(SCI 异步波特率*8)-1;BRR=0 时的串行通信接口异步波特率:SCI 异步波特率=SYSCLK/16这里BRR 等于波特率选择寄存器的16 位值。

异步串行接口电路及通信系统设计设计报告

异步串行接口电路及通信系统设计设计报告2009级可编程逻辑课程名称: 实验题目:学生姓名: YC 开课学院: Bio开课时间: 2011课程设计可编程逻辑设计异步串行接口电路及通信系统设计、SXL、ZY、YLJ、WJ 学院至2012学年第二学期重庆大学本科学生课程设计指导教师评定成绩表学院年级学生姓名课程设计题目be学院2009级指导教师专业Zxm. Wxp. BME YC、SXL、ZY、YLJ、WJ 异步串行接口电路及通信系统设计指导教师评语课程设计成绩指导教师签名:年月日重庆大学本科学生课程设计任务书课程设计题目学院BE学院异步串行接口电路及通信系统设计专业BME 年级、班09 BME 01、02班设计要求:设计一个能进行异步全双工串行通信的模块,该模块以固定的串行数据传送格式收发数据。

1)每帧数据供10 位,其中1位启动位,8位数据位,1位停止位。

2)波特率为:9600。

3)收发误码率摘要摘要通用串口是远程通信接口,在数字系统使用很普遍,是一个很重要的部件。

本论文使用VHDL语言描述硬件功能,并适当借助Verilog HDL 语言,利用在FPGA 芯片上的综合描述,采用模块化设计方法设计UART的各个模块。

其中包括波特率发生器,程序控制器,UART数据接收器和UART数据发送器,采用的外部时钟为50MHZ,波特率为9600。

在QuartusII 环境下进行设计、编译和仿真。

最后的程序编译仿真结果及硬件测试结果表明系统设计完全正确。

关键字:VHDL; Verilog HDL;UART; 帧格式; FPGA;异步通信I 摘要Abstract In this paper, the use ofhardware description languages VHDL function, the Verilog HDL language ,the use of Altera’s FPGA chips, the design of modular design method of UART (Universal Asynchronous Receiver Transmitter) of each module, including Porter, generators, process controllers, UART receiver data and the UART transmitter data. QuartusII and in environment design, compilation, simulation and downloading. Finally, simulation results show that the procedures for compiling data entirely correct. Key words: VHDL; VerilogHDL; UART; frame format; FPGA; Asynchronous Communication II目录目录一、课题设计概述及原理??????????????????????????1 设计目的???????????????????????????????1 设计要求???????????????????????????????1 设计内容???????????????????????????????1 设计原理???????????????????????????????1 串行通信的基本概念????????????????????????1数据传输方式????????????????????????1 波特率????????????????????????????2 误码率????????????????????????????2 串行通信的基本方式??????????????????????2 异步串行通信标准接口???????????????????????2 异步通信的控制时钟????????????????????????3 全双工串行通信模块UART ?????????????????????4 二、系统设计方案??????????????????????????????6 顶层逻辑设计图???????????????????????????6 设计说明??????????????????????????????6单元程序设计及仿真分析???????????????????????7 三、单元程序设计及仿真分析?????????????????????????7 系统时钟50分频???????????????????????????8 1MHz时钟1M分频???????????????????????????8 波特率产生模块????????????????????????????9 地址寻址模块电路图?????????????????????????10 数据接收模块????????????????????????????11 数据发送模块电路图?????????????????????????12 LED 显示模块???????????????????????????13 ROM数据存储模块???????????????????????????14 四、系统原理图设计及仿真分析????????????????????????15 五、硬件实验结果及时序分析结果?????????????????????16 六、总结??????????????????????????????????17 七、异步串行接口电路及通信系统设计下同步地接收并且保存RS-232接收端口上的串行数据;在数据发送时,UART内核模块首先依据待发送的数据和奇偶校验位的设置产生完整的发送序列,之后控制移位寄存器将序列加载到移位寄存器的内部寄存器里,最后再控制波特率发生器驱动移位寄存器将数据串行输出。

实验七串行口通讯实验报告

实验七串行口通讯实验报告一、引言串行口通讯是一种常见的数据传输方式,通过串行口可以在计算机和其他设备之间实现数据的传输和通信。

本实验通过使用Arduino开发板,以及利用串行口通讯实现从计算机向Arduino开发板发送指令,控制LED 灯的亮灭。

二、实验目的1.了解串行口通讯的基本原理和工作方式;2.掌握Arduino上位机通讯程序的编写及与硬件的串行口通讯方法;3.通过串行口通讯实现计算机对Arduino开发板的远程控制。

三、实验设备和器材1. Arduino Uno板;2.计算机;B数据线;4.杜邦线;5.LED灯。

四、实验原理当计算机与Arduino开发板连接时,可以通过串行口通讯实现双方之间的数据传输。

串行口通讯使用两根信号线:一根发送线(TX),用于发送数据;一根接收线(RX),用于接收数据。

通讯的双方都必须发送和接收数据,因此需要双向数据传输,即双向通讯。

五、实验步骤1. 连接Arduino开发板和计算机,使用USB数据线将两者连接;2. 打开Arduino IDE开发环境,编写以下代码并上传到Arduino开发板:```c++int ledPin = 13;void setuSerial.begin(9600);pinMode(ledPin, OUTPUT);void looif (Serial.available( > 0) { // 如果串行口接收到数据digitalWrite(ledPin, HIGH);digitalWrite(ledPin, LOW);}}```3. 打开串行监视器(Serial Monitor),设置波特率为9600,并选择“无”作为换行符;4.在串行监视器中输入“1”,回车,LED灯将点亮;5.在串行监视器中输入“0”,回车,LED灯将熄灭;6.关闭串行监视器。

六、实验结果和分析在本实验中,通过串行口通讯实现了从计算机向Arduino开发板发送指令,控制LED灯的亮灭。

串行通讯实验报告

串行通讯实验报告实验目的:1.了解串行通讯的基本概念和原理。

2.学习串行通讯的常用协议和流程。

3.实现串行通讯的发送和接收功能。

4.掌握使用串行通讯进行数据传输的方法。

实验器材:1.PC机一台。

2.串行通讯扩展板一块。

3.经典串行通讯工具软件。

实验原理:串行通讯是指信息逐位地按顺序进行传输的通讯方式。

串行通讯需要通过物理通道将数据逐位地传输给接收方。

常用的串行通讯协议有UART (通用异步收发传输)协议、SPI(串行外设接口)协议和I2C(串行外设接口)协议等。

实验步骤:1.将串行通讯扩展板连接到PC机上的串行通讯端口。

2.在PC机上安装串行通讯工具软件,并打开软件。

3.配置串行通讯参数,包括波特率、数据位、停止位和校验位等。

4.在串行通讯工具软件中编写发送数据的程序,并发送数据。

5.在串行通讯工具软件中接收数据,并验证接收的数据是否正确。

实验结果与分析:在实验中,我们使用串行通讯扩展板和串行通讯工具软件实现了串行通讯的发送和接收功能。

我们先配置了串行通讯的参数,在发送数据之前,我们选择了合适的波特率、数据位、停止位和校验位等。

然后,在发送数据之后,我们使用串行通讯工具软件接收数据,并验证接收的数据是否正确。

实验中我们可以观察到发送和接收的数据都是逐位地传输的,并且发送和接收的数据需要保持一致。

如果发送和接收的数据不一致,可能是由于串行通讯参数配置错误或者数据传输过程中产生了错误。

实验总结:通过本次实验,我们了解了串行通讯的基本概念和原理,学习了串行通讯的常用协议和流程,掌握了使用串行通讯进行数据传输的方法。

在实验中,我们成功完成了串行通讯的发送和接收功能,并验证了接收的数据是否正确。

实验中还存在一些问题,比如串行通讯的参数配置可能会影响数据的传输效果,我们需要根据具体情况选择合适的参数。

另外,数据传输中可能会产生噪声和错误,我们需要采取一些纠错措施来提高数据的传输可靠性。

总的来说,本次实验对我们了解串行通讯的原理和应用有很大帮助,为今后的学习和实践打下了良好的基础。

数电实验报告串行(3篇)

第1篇一、实验目的1. 理解串行通信的基本原理和方式。

2. 掌握串行通信接口电路的设计与调试方法。

3. 熟悉串行通信在实际应用中的使用。

二、实验原理串行通信是一种数据传输方式,它将数据一位一位地顺序传送,每位的持续时间远远大于数据信号的持续时间。

与并行通信相比,串行通信具有传输距离远、抗干扰能力强、成本低等优点。

串行通信方式主要有两种:同步串行通信和异步串行通信。

同步串行通信使用统一的时钟信号来同步发送和接收设备,而异步串行通信则使用起始位和停止位来同步。

三、实验器材1. 实验箱2. 串行通信模块3. 信号发生器4. 示波器5. 计算器四、实验步骤1. 连接电路根据实验要求,将串行通信模块、信号发生器、示波器等设备正确连接到实验箱上。

2. 设置参数根据实验要求,设置串行通信模块的波特率、数据位、停止位和校验位等参数。

3. 发送数据使用信号发生器生成要发送的数据信号,通过串行通信模块发送出去。

4. 接收数据通过示波器观察接收到的数据信号,分析其波形和参数。

5. 调试与优化根据观察到的波形和参数,对串行通信模块进行调试和优化,确保数据传输的准确性和可靠性。

五、实验结果与分析1. 发送数据波形观察到发送的数据信号波形符合要求,波特率、数据位、停止位和校验位等参数设置正确。

2. 接收数据波形观察到接收到的数据信号波形与发送端一致,说明数据传输过程中没有发生错误。

3. 调试与优化通过调整串行通信模块的参数,提高了数据传输的稳定性和抗干扰能力。

六、实验结论1. 通过本次实验,掌握了串行通信的基本原理和方式。

2. 熟悉了串行通信接口电路的设计与调试方法。

3. 了解了串行通信在实际应用中的重要性。

七、实验心得1. 串行通信在实际应用中具有广泛的应用前景,如工业控制、远程通信等。

2. 在设计和调试串行通信接口电路时,要充分考虑抗干扰能力和数据传输的稳定性。

3. 要熟练掌握串行通信模块的参数设置,以确保数据传输的准确性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

计算机系统的通信实验一.目的:了解计算机间的数据通信的基本技术;了解RS─232C的结构及使用方法。

RS----232C 9芯连接器插针定义如下:二.使用设备:带有RS─232C通信接口的微型计算器及一根多芯电缆。

三.8250异步串行接口:IBM PC系统可选的串行异步通信接口板上用的UART是一片INS8250,以它为核心,附加一些辅助电路,如I / O地址译码电路电平变换电路等,组成了RS232C接口,所以,对RS232C编程实际上是对8250的编程。

8250的逻辑框图如下:(一)8250的编程模型8250异步串行接口是用于IBM PC串行通讯的接口芯片,8250内含比特率分频器,无须外接,所以用它构成接口非常简单。

有两个串口,每个串口上有10个寄存器,IBM PC系统只为这10个寄存器分配了连续的7个端口地址,其端口地址分配如下:分配的端口地址输入还是输出相应寄存器3F8H/2F8H*输出发送数据寄存器3F8H/2F8H*输入接收数据寄存器3F8H/2F8H+输出波特率分频器L(数据传输速度)3F9H/2F9H+输出波特率分频器H3F9H/2F9H*输出中断允许寄存器3FAH/2FAH 输入中断标识寄存器3FBH/2FBH 输出线控制寄存器3FCH/2FCH 输出Modem控制寄存器3FDH/2FDH 输入线狀态寄存器3FEH/2FEH 输入Modem狀态寄存器注:标有*寄存器地址是线控制存器7位为0时的寄存器地址,标有+寄存器地址是线控制存器7位为1时的寄存器地址。

从功能上分,这10个寄存器可分为两组:一组用于工作方式,通信参数的控置和设置。

如数据格式有关参数的设置,是否允许中断方式的设置以及是否使用RTS,DTR等联络控制信号等,属于这一组的有5个寄存器:波特率分频器L(低位)和H(高位)线控制寄存器,Moden控制寄存器,中断允许寄存器。

这5个寄存器都是在8250初始化时用OUT指令向其中置入初值的。

另一组寄存器用于实现通信传输,有5个寄存器,它包括:输入和输出的缓冲寄存器——接收数据寄存器和发送保持寄存器,记忆当前状态的寄存器——线状态寄存器,Moden状态寄存器和中断标识寄存器。

(二)8250的初始化:1.波特率的设置:(波特率分频器L和H)是用OUT指令向地址为3F8H和3F9H的两个波特率分频器置入合适的值实现的。

在初始化时,将线控寄存器最高为置1,然后写3F8H,3F9H便可对串行传送速率进行初始化。

波特率分频器确定串行传送的速率(每秒传送的位数)如下:波特率分频器H 分频器L50 09H 00H75 06H 00H110 04H 17H134.5 03H 59H150 03H 00H300 01H 80H600 00H C0H1200 00H 60H1800 00H 40H2000 00H 3AH2400 00H 30H3600 00H 20H4800 00H 18H7200 00H 10H9600 00H 0CH19200 00H 06H2.对线控制寄存器初始化:(线控制寄存器: 3FBH/2FBH)写线控制寄存器可以设置串行数据的格式和选择是否设置波特率,其各位定义如下:D7 D6 D5 D4 D3 D2 D1 D0数据定位0 0 5位0 1 6位1 0 7位1 1 8位停止位0 1位1 1. 5位(D1 D0=00)1 2位(D1 D0≠00)校验X 0 无校验位0 1 形成奇校验位1 1 形成偶校验位是否为不变校验位01 否0 校验位永为1(D4 D3=01)0 校验位永为0(D4 D3=11)0 永无校验位(D3=0)是否置段点电平00 否1 是,强迫在送数据线上输出01 置波特率0 其它3. 对MODEM控制寄存器初始化:(MODEM控制寄存器: 3FCH/2FCH)MODEM控制寄存器各位意义如下:0 0 0 D4 D3 D2 D1 D01 使DTR输出有效准备好1 使RTS输出有效1 使OUT1输出有效(没利用)01使OUT2输出有效(用于开放和禁止中断)0(这节课)1使SOUT与SIN内部接通04.中断允许寄存器初始化:(中断允许寄存器:3F9H/2F9H)8250具有形成和发出中断请求信号的功能(见逻辑框图的INTRPT),在IBM PC的RS232C接口板上,这个信号从插头上输出,在接口板插入系统总线插槽时,这个信号接点与系统总线的IRQ4相接,是否利用中断功能,可以由编程设定。

对IBM PC而言,只有在置MODEN控制寄存器第3位OUT2为1时,才能允许下图所示的各种中断,中断允许寄存器各位意义如下:0 0 0 0 D3 D2 D1 D01 允许接收数据寄存器满发中断1允许发送数据寄存器空发中断1 允许接收字符出错或收到断点发中断1 允许MODEM状态改变发中断(三)收发通信编程:在8250初始化之后就可以通信了。

接收的基本操作是对接收数据寄存器(地址为3F8H)执行IN指令:MOV DX,3F8HIN AL,DX 发送的基本操作是对发送保持寄存器(地址为3F8H)执行OUT指令:MOV DX,3F8HOUT DX,AL 为了在发送和接收过程中不丢失信息,除上述基本操作外,还有许多问题需要解决。

在通信技术术语中,解决串行通信过程中在接口丢失信息的问题,称为流量控制(Flow Control)。

流量控制有两种方法:一种是完全用程序控制,另一种是程序借助接口硬件实现。

1.完全用程序实现流量控制,如果计算机的RS232C接口与一个输出设备相接,这时要求设备具有向计算机发XOFF和XON代码的功能,而计算机用程序与之相配合实现流量控制。

同样,如果与计算机的RS232C接口相接的是输入设备,要求它具有对XOFF和XON代码有合适的响应能力:当计算机来不及处理接收的数据时,向输入设备发XOFF代码,输入设备的响应应该是暂停向计算机发字符代码;计算机希望输入设备恢复发来代码时,向输入设备发XON代码,输入设备的响应应该是恢复向计算机发送数据,有些外部设备与计算机之间是双向传送的,这要根据这种外设是否有发出和响应XOFF和XON的功能,来决定是否能用程序进行流量控制。

2.借助接口硬件实现流量控制。

借助接口硬件实现流量控制,必须依靠接口中的状态信息和控制功能。

这实际上是把Moden状态寄存器,线状态寄存器提供的信息利用起来,并通过Moden控制寄存器实施控制。

在用IN指令输入代码前,必须先测试状态信息的位0是否已经为1,在对接收数据寄存器执行IN指令时,将使线状态寄存器的位0置0,表示数据已取走。

在发送数据时,要先测试位5是否为1。

向发送保持寄存器发送新的代码后,使状态位5置0。

(a).线状态寄存器: 3FDH/2FDH读线状态寄存器可以了解线路传输状态,其各位定义如下:0 D6 D5 D4 D3 D2 D1 D01 接收数据寄存器满(接收准备好)1 数据重迭错1 奇偶出错1 数据格式出错1 检出断点1 发送数据寄存器空(发送准备好)1 发送移位寄存器空发送数据寄存器空,表示CPU送给8250的数据已从发送数据寄存发送移位寄存器。

此时8250又可以接收CPU的新数据,也就是发送准备好,写发送数据寄存器将使本位复位。

发送移位寄存器空,表示发送移位寄存器已将从发送数据寄存器收到的数据移位输出完备。

此时又可从发送数据寄存器接收新数据。

接收数据寄存器满,表示已经接收完一个数据,放在接收数据寄存器中,此时CPU可已从8250读入数据,也就是接收准备好,读接收数据寄存器将使本位复位。

数据重迭错,表示接收数据寄存器满时,CPU尚未取走这个数据,又一个新接收到的串行数据又收完,并送入接收数据寄存器。

这样,原来的数据就被冲掉。

这就称为重迭错,或溢出错。

数据格式出错,8250接收一个串行数据,经过起始位,数据位和奇偶校验位后应收到停止位“1”。

如果此时仍收到“0”,则发生格式错。

检出断点,表示8250收到“0”电平的持续时间超过从起始位到停止位的总时间,注意检出断点和收到全0字节是完全不同的。

读线状态寄存器将使D1——D4位复位。

(b).MODEM状态寄存器: 3FEH/2FEHMODEM状态寄存器各位意义如下:D7 D6 D5 D4 D3 D2 D1 D01 CTS上的信号改变过1 DSR上的信号改变过1 RI上信号改变过1 DCD上的信号改变过CTS状态DST状态RI 状态D CD状态表示接口对方当前状态的信息有四位:位4—位7CTS:对方通知本方可以向对方发送信息DSR:对方通知本方对方已可以工作RI:对方来的铃响信号指示DCD:对方通知本方已检测到线路有载波要正确进行通信操作,只有这4位状态信息是不够的,还要根据Moden状态寄存器低4位提供的信息来进行通信操作。

每次对这个状态寄存器执行IN指令都将使低4位清0,只有相应的状态信号线上的有效信号重新到来,才能使低4位内相应位置1。

其中,低4位所谓信号改变过是指从上次读MODEM状态寄存器以来信号改变过。

(c).对上述两个状态寄存器状态的测试,可以决定是否用指令输入或输出字符代码。

Moden控制寄存器的控制字节可以用来向对方提供状态信息。

Moden控制寄存器的位0和位1分别控制发出DTR和RTS信号:DTR信号表示本方接口是否正常工作RTS是向对方表示是否将向对方发送代码,对方可以判别这两个信号,决定自己的操作。

综上所述,借助硬件实现流量控制的过程就是,无论读入字符还是发送字符前,要先测试线路状态和对方(Moden)的状态,根据测试结果再决定下面操作,另一方面,向对方提供自己的状态,使对方也能根据对本方状态的测试决定如何操作。

3.发送数据寄存器:(3F8H/2F8H)它寄存CPU送给8250的8位并行数据,8250内部电路再将它送到移位寄存器,变成串行数据输出。

4.接收数据寄存器:( 3F8H/2F8H)它寄存8250将要送给CPU的8位并行数据,8250收到串行数据通过移位寄存器变成并行数据,然后存入接收数据寄存器中。

(四).中断功能的实现用编程的方法可以使8250具有发出中断请求的能力。

IBM PC系统的串行接口板的中断请求信号是通过系统总线的IRQ4端加入的。

中断服务程序的入口地址应该在中断向量地址表的0000:0030H开始的4个单元内。

8250内对中断起作用的是Moden控制寄存器位3(OUT2), 中断允许寄存器和中断标识寄存器。

Moden 控制寄存器位3在初始化时必须设置为1,8250内的中断管理机构才起作用。

1.中断允许寄存器中断允许寄存器的位0—位3分别管理4种中断源,初始化时,将中断允许寄存器的位0—位3的一位或几位置1,就能在对应的条件出现时发出中断请求。