CMOS模拟集成电路第12章―开关电容电路PPT课件

合集下载

CMOS 模拟集成电路课件完整

反偏电压将使耗尽区变宽,从而降低了有效沟道深度。因此,需 要施加更大的栅极电压以弥补沟道深度的降低,VSB偏压会影响 MOSFET的有效阈值电压VTH。随着VSB反偏电压的增加导致VTH的增 加,这种效应称为“体效应”。这种效应也称为“衬底偏置效应” 或“背栅效应”。

VTHN VTHN0

2qsi Na Cox

VGS 1 0 1.0 VDS 2 0 5

.op .dc vds 0 5 .2 Vgs 1 3 0.5 .plot dc -I(vds) .probe

*model .MODEL MNMOS NMOS VTO=0.7 KP=110U +LAMBDA=0.04 GAMMA=0.4 PHI=0.7

.end

Systems

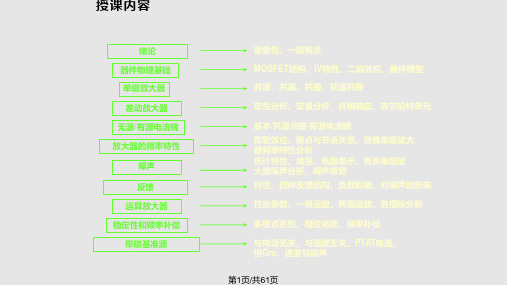

Ch13 开关电容电路

Ch14 DAC/ADC

complex Ch10 运算放大器 Ch7 频率响应

Ch11 稳定性和频 率补偿

Ch8 噪声

Ch12 比较器 Ch9 反馈

Ch3 电流源电流镜 simple Ch4 基准源 Circuits

Devices

Ch5 单级放大器 ch2 MOS器件

*Output Characteristics for NMOS M1 2 1 0 0 MNMOS w=5u l=1.0u

VGS 1 0 1.0 VDS 2 0 5

设计

属性/规范

系统/电路1

系统/电路2 系统/电路3

……

一般产品描述、想法 系统规范要求的定义

系统设计 电路模块规范定义

电路实现 电路仿真

否

是否满足系统规范

是 物理(版图)设计

物理(版图)验证

寄生参数提取及后仿真

否

是否满足系统规范

VTHN VTHN0

2qsi Na Cox

VGS 1 0 1.0 VDS 2 0 5

.op .dc vds 0 5 .2 Vgs 1 3 0.5 .plot dc -I(vds) .probe

*model .MODEL MNMOS NMOS VTO=0.7 KP=110U +LAMBDA=0.04 GAMMA=0.4 PHI=0.7

.end

Systems

Ch13 开关电容电路

Ch14 DAC/ADC

complex Ch10 运算放大器 Ch7 频率响应

Ch11 稳定性和频 率补偿

Ch8 噪声

Ch12 比较器 Ch9 反馈

Ch3 电流源电流镜 simple Ch4 基准源 Circuits

Devices

Ch5 单级放大器 ch2 MOS器件

*Output Characteristics for NMOS M1 2 1 0 0 MNMOS w=5u l=1.0u

VGS 1 0 1.0 VDS 2 0 5

设计

属性/规范

系统/电路1

系统/电路2 系统/电路3

……

一般产品描述、想法 系统规范要求的定义

系统设计 电路模块规范定义

电路实现 电路仿真

否

是否满足系统规范

是 物理(版图)设计

物理(版图)验证

寄生参数提取及后仿真

否

是否满足系统规范

模拟CMOS集成电路设计单级放大器PPT课件

Av0

Gm Rout

gm 1 gm RS

RD

RD RS

(gmRS 1)

Amplifiers Ch.3 # 25

第25页/共55页

带源极负反馈的共源级(3)

Rup Rdown

Gm

gm 1 gmRS

Rup RD

Rdown gm1ro1RS

Rout Rup || Rdown RD (Rdown Rup )

第3页/共55页

放大器的性能指标

• 增益 • 速度(带宽、转换速率) • 功耗 • 电源电压、电源电压抑制比 • 线性度 • 噪声 • 输入摆幅、输出摆幅 • 输入/输出阻抗

北大微电子:模拟集成电路原理

Amplifiers Ch.3 # 4

第4页/共55页

模电设计中的八边形法则

北大微电子:模拟集成电路原理

信号放大

• 为什么信号需要放大? • 信号太弱,不能驱动负载:阻抗匹配 • 降低后续噪声影响 • 用于反馈电路

• 放大前后信号可同量纲,也可不同量纲

• 同量纲时放大倍数可大于1,也可小于1

北大微电子:模拟集成电路原理

Amplifiers Ch.3 # 1

第1页/共55页

放大器的种类

电流放大器

V-V

Rup

1 gm2

Rdown ro1

Rout

Rup

||

Rdown

1 gm2

|| ro1

ro1 1 gm2ro1

1 gm2

(

1 gm2

ro1 )

Av0

Vout Vin

g R m1 out

gm1 gm2

Amplifiers Ch.3 # 16

第16页/共55页

CMOS门电路PPT课件

一、MOS管的开关特性

1. MOS管的结构和工作原理

-

S

vGS

vDS +

G

+ iD

D

N+

N+

G

P型衬底(B)

第三节 CMOS门电路

D B

S

当vDS> 0,但 vGS= 0 时,D-S间2不021/3导/9 通, iD= 0 。 当vDS> 0, 且vGS> vGS(th) (MOS管的开启电压)

时,栅极下面的衬底表面形成一个N型反型层。 这个反型层构成了D-S间的导电沟道,有 iD流通。

2. 电压传输特性

AB段:

vO

VDD A B

T1的开 启电压

T1导通, T2截止, VO = VOH ≈ VDD。

CD段:

1

2 V D D VGH(th)N

VGH(th)P

T2导通, T1截止, VO = VOL ≈ 0。

CD

T2的开 O 启电压

1 2 V DD

VDD

vI

2021/3/9

CMOS反相器的电压传输特性 BC段:

27

放映结束 感谢各位的批评指导!

谢 谢!

让我们共同进步

2021/3/9

28

C

C

V DD

T2

vI / vO T 1

v O / v I v I / v O TG

C

C

2021/3/9

C1,C0 时,传输门导通。

C0,C1 时,传输门截止。

vO / vI

20

第三节 CMOS门电路

利用 CMOS传输门和CMOS反相器可以组合成各种 复杂的逻辑电路, 如异或门、数据选择器、寄存器、计数器等。

1. MOS管的结构和工作原理

-

S

vGS

vDS +

G

+ iD

D

N+

N+

G

P型衬底(B)

第三节 CMOS门电路

D B

S

当vDS> 0,但 vGS= 0 时,D-S间2不021/3导/9 通, iD= 0 。 当vDS> 0, 且vGS> vGS(th) (MOS管的开启电压)

时,栅极下面的衬底表面形成一个N型反型层。 这个反型层构成了D-S间的导电沟道,有 iD流通。

2. 电压传输特性

AB段:

vO

VDD A B

T1的开 启电压

T1导通, T2截止, VO = VOH ≈ VDD。

CD段:

1

2 V D D VGH(th)N

VGH(th)P

T2导通, T1截止, VO = VOL ≈ 0。

CD

T2的开 O 启电压

1 2 V DD

VDD

vI

2021/3/9

CMOS反相器的电压传输特性 BC段:

27

放映结束 感谢各位的批评指导!

谢 谢!

让我们共同进步

2021/3/9

28

C

C

V DD

T2

vI / vO T 1

v O / v I v I / v O TG

C

C

2021/3/9

C1,C0 时,传输门导通。

C0,C1 时,传输门截止。

vO / vI

20

第三节 CMOS门电路

利用 CMOS传输门和CMOS反相器可以组合成各种 复杂的逻辑电路, 如异或门、数据选择器、寄存器、计数器等。

集成电路中元器件PPT课件

• 对于不同材料的连线,其串联寄生电阻大小也有所不 同。对应不同材料连线的方块电阻分别为:

第21页/共25页

连线上的寄生参数将对电路性能产生影响,如: 电源线上的寄生电阻会带来电源电压的衰减; 信号线上的寄生电阻和寄生电容将带来信号延迟; 导线互相平行或不同层导线交叉时,将带来相互串

扰。

第22页/共25页

MOS电容是非线性电容,主要用于电源滤 波电路。

第7页/共25页

4. “夹心”电容

总电容值C=C1+C2+C3+C4 该电容是一种线性电容,其底板寄生电容约为:

Cp≈(50%~60%)C

第8页/共25页

5. MOS管的极间电容和寄生电容

MOS管的极间电容存在于4个端子中的任意两端之间, 这些电容的存在影响了器件和电路的高频交流特性。包括:

第17页/共25页

6. 拐弯电阻计算

第18页/共25页

三、连线

第19页/共25页

概念

• 元件与元件之间必须通过“连线”才构成电路。理想的连线在实现连线的功能 时,不应带来额外的寄生效应;

• 在集成电路中,用于连线的有:金属、扩散区、多晶硅等。

第20页/共25页

• 上图为连线的寄生模型,图中R为串联寄生电阻,C为 并联寄生电容。连线越长,寄生参数也越大

第6页/共25页

3. MOS电容—栅极与沟道之间的电容 Cch

这种电容结构与MOS管一样,当栅极加 上电压形成沟道时电容就存在了,其一个极板是 栅极,另一个极板为沟道,沟道这一极由源极与 漏极短接而引出。

这种电容具有单位面积的最大电容,实际 上还存在沟道电阻问题。为减小沟道电阻,当L较 大时,可将栅极做成梳状形式。

• 设计时必须充分考虑电容的因素。

第21页/共25页

连线上的寄生参数将对电路性能产生影响,如: 电源线上的寄生电阻会带来电源电压的衰减; 信号线上的寄生电阻和寄生电容将带来信号延迟; 导线互相平行或不同层导线交叉时,将带来相互串

扰。

第22页/共25页

MOS电容是非线性电容,主要用于电源滤 波电路。

第7页/共25页

4. “夹心”电容

总电容值C=C1+C2+C3+C4 该电容是一种线性电容,其底板寄生电容约为:

Cp≈(50%~60%)C

第8页/共25页

5. MOS管的极间电容和寄生电容

MOS管的极间电容存在于4个端子中的任意两端之间, 这些电容的存在影响了器件和电路的高频交流特性。包括:

第17页/共25页

6. 拐弯电阻计算

第18页/共25页

三、连线

第19页/共25页

概念

• 元件与元件之间必须通过“连线”才构成电路。理想的连线在实现连线的功能 时,不应带来额外的寄生效应;

• 在集成电路中,用于连线的有:金属、扩散区、多晶硅等。

第20页/共25页

• 上图为连线的寄生模型,图中R为串联寄生电阻,C为 并联寄生电容。连线越长,寄生参数也越大

第6页/共25页

3. MOS电容—栅极与沟道之间的电容 Cch

这种电容结构与MOS管一样,当栅极加 上电压形成沟道时电容就存在了,其一个极板是 栅极,另一个极板为沟道,沟道这一极由源极与 漏极短接而引出。

这种电容具有单位面积的最大电容,实际 上还存在沟道电阻问题。为减小沟道电阻,当L较 大时,可将栅极做成梳状形式。

• 设计时必须充分考虑电容的因素。

CMOS门电路实用PPT课件

( N沟道增强型 MOS 管为例)

VDD

RD

ID

D

uO

G

ui

S•

0

VGS(TH)

ID vGS 0

vGS>VGS(TH)

vGS<VGS(TH) vDS

➢ 当vI<VGS(TH)时:

MOS管工作在截止区,

vO=VOH≈VDD

➢ 当vI>VGS(TH)时:

在可变电阻区,沟道电阻很小,

vO=VOL≈0V

10

✓ vI = VDD-|VTP|~VDD段:仍假设TN导通,则vI传到vO后,有UGS(TN)<VTN→ TN 截止,与假设相矛盾。故此段TN截止。

第27页/共34页

vI 0 VTN

VDD-|VTP| VDD

C’=0 VDD

TP

G

S

D

TN通

TN止 TN

vI

vo

TP止

TP通

TP

TN D

S

RL

G

C=VDD

① CMOS传输门:控制信号传输的门

可实现双向传输

ui/uo

利用P沟道MOS管和N沟道MOS管的互补性构 成。

C和C'是一对互补的控制信号。

C' TP

VDD uo/ui

TN C

电路结构

TP : VTP < 0 TN : VTN > 0

︱UGS(TP)︱ >︱ VTP︱ UGS(TN) > VTN

VTN=︱VTP︱

定义: 开启电压( UT)—— 沟道刚开始形成时的栅源 电压UGS。(一般2 ~ 3V)

S VDS

-

VGS

-D -G iD

模拟cmos集成电路设计拉扎维MOS器件物理基础PPT课件

定义从D流 向S为正 PMOS管电流驱动能力比NMOS管差 0.8 m nwell:p=250cm2/V-s, n=550cm2/Vs 0.5 m nwell:p=100cm2/V-s, n=350cm2/V-

第23页/共61页

跨导gm

VGS对IDS的控制能力 IDS对VGS变化的灵敏度

gm ID VGS VDS cons tant

• 直流关系式-I/V特性 • 交流关系式-小信号电路中的参数

第6页/共61页

MOS管简化模型

简化模型——开关 由VG控制的一个开关

第7页/共61页

MOS管的结构

Bulk(body)

源漏在物理结构上是完全对称的,靠什么区分开?

提供载流子的端口为源,收集载流子的端口为漏

最重要的工作区域?

受VG控制的沟道区

• 小信号模型 • 信号相对于偏置工作点而言比较小、不会显著影响偏置工作点时用该模型简化计算 • 由gm、 gmb、rO等构成低频小信号模型,高频时还需加上 CGS等寄生电容、寄生电阻(接触孔电阻、 导电层电阻等)

沟道电荷的产生

当VG大到一定 程度时,表面势 使电子从源流向 沟道区 VTH定义为表面电 子浓度等于衬底 多子浓度时的VG

第12页/共61页

阈值电压

0 栅与衬底功函数差

COX

OX

TOX

常通过沟道注入把VTH0调节到合适值 工艺确定后,VTH0就固定了,设计者无法改变

第13页/共61页

I/V特性-沟道随VDS的变化

第3页/共61页

掌握器件物理知识的必要性

• 数字电路设计师一般不需要进入器件内部,只把它当开关用即可 • AIC设计师必须进入器件内部,具备器件物理知识

• MOS管是AIC的基本元件 • MOS管的电特性与器件内部的物理机制密切相关,设计时需将两者结

第23页/共61页

跨导gm

VGS对IDS的控制能力 IDS对VGS变化的灵敏度

gm ID VGS VDS cons tant

• 直流关系式-I/V特性 • 交流关系式-小信号电路中的参数

第6页/共61页

MOS管简化模型

简化模型——开关 由VG控制的一个开关

第7页/共61页

MOS管的结构

Bulk(body)

源漏在物理结构上是完全对称的,靠什么区分开?

提供载流子的端口为源,收集载流子的端口为漏

最重要的工作区域?

受VG控制的沟道区

• 小信号模型 • 信号相对于偏置工作点而言比较小、不会显著影响偏置工作点时用该模型简化计算 • 由gm、 gmb、rO等构成低频小信号模型,高频时还需加上 CGS等寄生电容、寄生电阻(接触孔电阻、 导电层电阻等)

沟道电荷的产生

当VG大到一定 程度时,表面势 使电子从源流向 沟道区 VTH定义为表面电 子浓度等于衬底 多子浓度时的VG

第12页/共61页

阈值电压

0 栅与衬底功函数差

COX

OX

TOX

常通过沟道注入把VTH0调节到合适值 工艺确定后,VTH0就固定了,设计者无法改变

第13页/共61页

I/V特性-沟道随VDS的变化

第3页/共61页

掌握器件物理知识的必要性

• 数字电路设计师一般不需要进入器件内部,只把它当开关用即可 • AIC设计师必须进入器件内部,具备器件物理知识

• MOS管是AIC的基本元件 • MOS管的电特性与器件内部的物理机制密切相关,设计时需将两者结

集成电路原理课件-cmos

集成电路原理与设计

1

微电子学

• 微电子技术是电子计算机和通信的核心技术 • 微电子技术的核心是集成电路(Integrated Circuit, IC) 技术 • 微电子学是电子学的一门分支,主要研究电子或离 子在固体材料中的运动规律及其应用 • 微电子学是以实现电路和系统的集成为目的,研究 如何利用半导体的微观特性以及一些特殊工艺,在 一块半导体芯片上制作大量的器件,从而在一个微 小面积中制造出复杂的电子系统。

I

D

dx

V 0

WC

ox

n [VGS V ( x) VTH ]dV

I/V特性的推导(3)

W 1 2 I D = nCox [(VGS - VTH )VDS - VDS ] (2.8) L 2 W VGS - VTH 称为过驱动电压; 称为宽长比 L 三极管区(线性区)

每条曲线在VDS=VGS-VTH时取最 大值,且大小为:

CGD CGS

WLCOX WCOv 2

CGB可以忽略不计

CSB = CDB =

WE源极Cj (1 VSB /B ) WE漏极Cj (1 VDB /B )

mj mj

源极周长 C jsw (1 VSB /B )

m jsw

漏极周长 C jsw (1 VDB/B )

MOS器件电容

栅源、栅漏、栅衬电容与VGS关系

1) VGS < VTH截止区

CGD CGS WCOv

CGB W 2 L2 COX q si N sub / 4 F WLCOX Cd = 其中Cd=WL q si N sub / 4 F WLCOX Cd WLCOX WL q si N sub / 4 F

1

微电子学

• 微电子技术是电子计算机和通信的核心技术 • 微电子技术的核心是集成电路(Integrated Circuit, IC) 技术 • 微电子学是电子学的一门分支,主要研究电子或离 子在固体材料中的运动规律及其应用 • 微电子学是以实现电路和系统的集成为目的,研究 如何利用半导体的微观特性以及一些特殊工艺,在 一块半导体芯片上制作大量的器件,从而在一个微 小面积中制造出复杂的电子系统。

I

D

dx

V 0

WC

ox

n [VGS V ( x) VTH ]dV

I/V特性的推导(3)

W 1 2 I D = nCox [(VGS - VTH )VDS - VDS ] (2.8) L 2 W VGS - VTH 称为过驱动电压; 称为宽长比 L 三极管区(线性区)

每条曲线在VDS=VGS-VTH时取最 大值,且大小为:

CGD CGS

WLCOX WCOv 2

CGB可以忽略不计

CSB = CDB =

WE源极Cj (1 VSB /B ) WE漏极Cj (1 VDB /B )

mj mj

源极周长 C jsw (1 VSB /B )

m jsw

漏极周长 C jsw (1 VDB/B )

MOS器件电容

栅源、栅漏、栅衬电容与VGS关系

1) VGS < VTH截止区

CGD CGS WCOv

CGB W 2 L2 COX q si N sub / 4 F WLCOX Cd = 其中Cd=WL q si N sub / 4 F WLCOX Cd WLCOX WL q si N sub / 4 F

CMOS集成电路设计基础实用PPT课件

即 UGDP=|Ui-Uo|<|UTHP|

第31页/共76页

3. CD段 当Ui进一步增大, 且满足 Uo+|UTHP|≤Ui≤Uo+UTHN N管和P管的电流相等, 根据电流方程:

I DN

nCox

2

W L

N

(UGSN

UTHN )2

I DP

pCox

2

W L

N

(U

GSP

UTHP )2

第21页/共76页

CMOS传输门的直流传输特性

CMOS传输门的直流传输特性如图 所示, 它不存在阈值损失问题: (1) 当UGN=“0”, UGP=“1”时, N管、 P管均截止, Uo=0。

(2) 当UGN=“1”, UGP=“0”时, Ui由“0”升高到“1”的过程分为以下三个阶段(分析中, 设“1”为UDD=5V, “0”为接地(0 V), UTHN=|UTHP|=0.9 V):

PD1

1 Tc

T1 0

(iDP

UDSP )dt

T2 0

(iDN

U DSN

)dt

iDP iDN

CL

dUo dt

式中Tc为输入信号周期

UDSP UDD Uo

功率延时积

功率延时积(PDP) =E=每操作消耗的能量=Pav×tp

能量延时积

能量延时积(EDP) =门的品质(度量)因子= E×tp

第10页/共76页

功(热)耗对设计的要求: 功耗影响设计:封装、冷却、电源线尺寸、电源容量、集 成度 功耗影响电路的可行性、成本、可靠性。 峰值功耗(确定电源线尺寸)、平均功耗(确定冷却、对 电池要求) 动态功耗(翻转功耗)、静态功耗(漏电功耗) 传播延时与功耗的关系:功耗延时积、能量延时积

第31页/共76页

3. CD段 当Ui进一步增大, 且满足 Uo+|UTHP|≤Ui≤Uo+UTHN N管和P管的电流相等, 根据电流方程:

I DN

nCox

2

W L

N

(UGSN

UTHN )2

I DP

pCox

2

W L

N

(U

GSP

UTHP )2

第21页/共76页

CMOS传输门的直流传输特性

CMOS传输门的直流传输特性如图 所示, 它不存在阈值损失问题: (1) 当UGN=“0”, UGP=“1”时, N管、 P管均截止, Uo=0。

(2) 当UGN=“1”, UGP=“0”时, Ui由“0”升高到“1”的过程分为以下三个阶段(分析中, 设“1”为UDD=5V, “0”为接地(0 V), UTHN=|UTHP|=0.9 V):

PD1

1 Tc

T1 0

(iDP

UDSP )dt

T2 0

(iDN

U DSN

)dt

iDP iDN

CL

dUo dt

式中Tc为输入信号周期

UDSP UDD Uo

功率延时积

功率延时积(PDP) =E=每操作消耗的能量=Pav×tp

能量延时积

能量延时积(EDP) =门的品质(度量)因子= E×tp

第10页/共76页

功(热)耗对设计的要求: 功耗影响设计:封装、冷却、电源线尺寸、电源容量、集 成度 功耗影响电路的可行性、成本、可靠性。 峰值功耗(确定电源线尺寸)、平均功耗(确定冷却、对 电池要求) 动态功耗(翻转功耗)、静态功耗(漏电功耗) 传播延时与功耗的关系:功耗延时积、能量延时积

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

20

开关电容放大器

• 3.1 单位增益采样/缓冲器(续)

速度问题 采样模式下, X处的等效对地电阻

通常,Ron2<<R0,且GmR0>>1,因 此,Rx≈1/Gm 采样模式下的时间常数

16.09.2020

21

开关电容放大器

• 3.1 单位增益采样/缓冲器(续)

速度问题 放大模式下,

▪在开始时,运放的输入会得到一个很大的值(V0),产生转换,按照大信号行为分析,按运放的 转换速率计算。 ▪当放大器进入线性区后,采用线性模型计算。

16.09.2020

9

采样开关

• 2.2 速度问题(续)

采样速度的决定因素

▪开关的导通电阻 输入接近VDD-VTHN时,Ron→∞

Pmos:输入接近|VTHP|时,Ron→∞

16.09.2020

10

采样开关

• 2.2 速度问题(续)

CMOS互补开关

保证同时断开

16.09.2020

16.09.2020

22

开关电容放大器

• 3.1 单位增益采样/缓冲器(续)

速度问题(续) 在线性放大阶段,将CH上的电荷等效为一个电 压源Vs,计算传输函数

并考虑GmR0CH>>CH和Cin简化公式,

如果Cin<<CL及CH,上式简化为CL/Gm

16.09.2020 X点的寄生电容(Cin)会影响速度和精度,因此采样“下极板采样”23

开关电容放大器

• 3.2 同相放大器

采样阶段(b): S1,S2闭合,S3断开 Vout=Vx≈0,电容两端V0=Vin 放大阶段(c): S1,S2断开,S3闭合 Vout=Vin0(C1/C2)

增益:

15

采样开关

• 2.4 电荷注入抵消(续)

方法二:CMOS开关 可以抑制电荷注入,要求:

W 1 L 1 C o( V x C V K i n V T) H W 2 N L 2 C o( V x i n V T) H P

但由于NMOS和PMOS的交叠电容不 相等,只能部分消除时钟馈通

16.09.2020

11

采样开关

• 2.3 精度问题

沟道电荷注入 导通时,沟道中的电荷 Qch会在关断后通过S和D 端流出。

粗略地,假设一半电荷注入到CH上, Vout

再考虑体效应的非线性,沟道电荷注入 将导致三种误差:

增益误差;直流失调;非线性

16.09.2020

12

采样开关

• 2.3 精度问题(续)

时钟馈通 时钟信号通过交叠电容 耦合到采样电容上。

▪可以“跟踪”和“冻结” 信号

(▪“V零in失的调最”高开电关压)等于VDDVTH

线性区

16.09.2020

7

采样开关

• 2.1 MOSFET开关

▪Vin的最高电压等于VDD-VTH 当Vout趋进VDD-VTH时,M1趋于截止。

16.09.2020

8

采样开关

• 2.2 速度问题

采样速度的决定因素 ▪开关的导通电阻 ▪采样电容:小的采样电容可以提高采样速度

S3:S3的沟道电荷来自运放,不会产 生误差。

16.09.2020

19

开关电容放大器

• 3.1 单位增益采样/缓冲器(续)

精度问题 运放的增益和输入电容Cin为有限值 放大模式下,VX不等于0,从CH上抽 取CinVX电荷

V C H (C H V 0 C iV n X )/C H

16.09.2020

CMOS模拟集成电路设计

开关电容电路

16.09.2020

1

提纲

提纲

• 1、概述 • 2、采样开关 • 3、开关电容放大器 • 4、开关电容积分器

16.09.2020

2

概述

1、概述

• CMOS连续时间反馈放大器的问题

CMOS放大器为了有较大增益,需要 有很大的开环输出电阻

闭环增益不精确

16.09.2020

16.09.2020

13

采样开关

• 2.3 精度问题(续)

kT/C噪声

Vn2 kT/C

16.09.2020

14

采样开关

• 2.4 电荷注入抵消

方法一:“虚拟”开关 可以抑制电荷注入,但不精确, 粗略地,假设一半电荷注入到CH上,

得到,W2=0.5W1,L2=L1 此时,也可以抑制时钟馈通

16.09.2020

16

采样电容

• 2.5 采样电容

下极板采样: 放大器的输入接采样电容 的上极板

好处: ▪减小X点对地电容; ▪避免X点注入衬底噪声

上极板

16.09.2020

下极板

17

开关电容放大器

3、开关电容放大器

• 3.1 单位增益采样/缓冲器

采样阶段(a): S1,S2闭合,S3断开 Vout=Vx≈0,电容两端V0=Vin 放大阶段(b): S1,S2断开,S3闭合 Vout=V0=Vin-

放大阶段(b): S1,S2断开,S3闭合,通过C2上的负反 馈,C1上的电荷转到C2上, Vout=VinC1/C2

16.09.2020

负反馈 0

(b)

5

概述

• 开关电容电路

特点: ▪采样 ▪放大阶段仅对采样电压放大器 ▪状态的转换,导致电路的稳定性问题

优点:

▪Vout达到稳定后,通过C2的电流接近0,即稳定后反馈电容不会 降低放大器的开环增益;

3

概述

• CMOS连续时间反馈放大器的问题(续)

采用电容代替反馈电阻

电路呈现高通传输特性,所以不适合 放大宽带信号

Av

RF

1 C2s 1

RFC1s RFC2s 1

C1s

只有当ω>>(RFC2)-1时,AV≈-C1/C2

16.09.2020

4

概述

• 开关电容电路

采样阶段(a): S1,S2闭合,S3断开,C1上存储的电荷 为VinC1

16.09.2020

(a)

(b)

18

开关电容放大器

• 3.1 单位增益采样/缓冲器(续)

沟道电荷注入的影响 从采样到放大模式, S2比S1稍微早断 开一会儿,CH上的电荷为CHV0 S2:引入失调,可以通过差分工 作方式消除

S1:如果S2首先断开(采样时刻), 由于X点“悬空”,采样电容上的电 荷保持不变,因此, S1的电荷不会带 来误差

▪电容更易实现; ▪开关电容放大器在CMOS工艺中更容易实现;CMOS工艺具有 简单开关和高输入阻抗,使得其成为数据采样应用的主要选择。

16.09.2020

6

采样开关

2、采样开关和电容

• 2.1 MOSFET开关

电压传输

▪MOS开关大部分时间工作 在线性区,等效一个电阻

▪MOS开关可以双向传输

t=t0时,饱和区 当Vout≤VDD-VTH时,线性区