什么是硬件乘法器

乘法器工作原理

乘法器工作原理

乘法器是一种电子设备,用于实现两个数字(或模拟)信号的乘法运算。

其工作原理可以简单地描述如下:

1. 输入信号:乘法器通常有两个输入端,分别用于接收待相乘的数字信号A和B。

2. 位展开:乘法器将输入信号A和B进行位展开操作,即将

每一个输入位(或字节)进行分离和独立处理。

这可以通过触发器、逻辑门电路等实现。

3. 部分乘积计算:对每一对输入位进行乘法运算,并将结果存储在部分乘积寄存器中。

这可以通过加法器电路来实现,其中每一个乘积被加到累加器中。

4. 乘积累加:将所有的部分乘积相加得到最终的乘积结果。

这可以通过多级加法器电路来实现。

一般来说,乘法器采用树形结构或布斯-舍乘法算法(Booth's algorithm)来提高计算效率。

5. 结果输出:输出端给出乘法运算的结果。

根据需求,这个结果可以是数字信号,模拟电压或电流等形式。

乘法器的工作原理可以根据底层电路和算法的不同而有所变化。

现代的乘法器采用复杂的电路设计和优化算法,以实现更高的运算速度和精度。

MSP430程序库十三硬件乘法器使用

MSP430程序库<十三>硬件乘法器使用硬件乘法器不占用CPU周期,有硬件实现,速度比软件实现的乘法速度快很多。

msp430f14x、msp430f16x中都含有硬件乘法器模块,方便用户需要速度的时候使用。

硬件介绍:在MSP430系列单片机中,硬件乘法器是外围模块,而不是CPU内核的一部分;所以它的活动与否与CPU的活动与否无关,它的寄存器和其他的外围寄存器一样通过CPU指令读写。

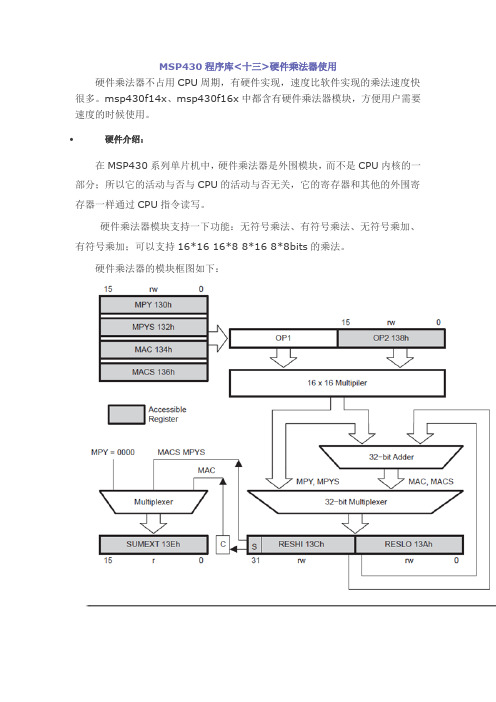

硬件乘法器模块支持一下功能:无符号乘法、有符号乘法、无符号乘加、有符号乘加;可以支持16*16 16*8 8*16 8*8bits的乘法。

硬件乘法器的模块框图如下:硬件乘法器模块的四种操作类型(无符号乘法、有符号乘法、无符号乘加、有符号乘加)是由写入的第一个操作数的位置决定的。

这个模块有两个操作数寄存器:OP1和OP2、三个结果寄存器RESLO, RESHI, 和SUMEXT。

RESLO 寄存器存储结果的低字(低16位);RESHI寄存器存储结果的高字(高16位);SUMEXT寄存器存储结果的有关信息。

结果在3个时钟周期后即可完成;写入OP2后的下一条指令即可读取结果,有一种情况例外:用间接寻址方式访问结果。

用间接寻址方式访问结果时,读取结果之前需要有一条NOP指令。

操作数OP1有四个地址(MPY:0130h MPYS:0132h MAC:0134h MACS:0136h),这四个寄存器用来选择乘法的操作模式。

写入第一个操作数寄存器决定用哪种操作:无符号用符号等,但是不启动相乘操作;写入第二个操作数寄存器启动相乘的操作。

计算完成后结果存入寄存器RESLO,RESHI, 和SUMEXT。

操作数1的四个地址对应的操作:四种操作模式下高位结果寄存器的内容如下:四种操作模式SUMEXT 寄存器的内容:连续乘法运算时,如果操作数1不需改变就可以运算,则可以不需要重新写入和以保存内容相同的数;但OP2必须重新写入以启动乘法运算。

5.4 硬件乘法器

如果执行乘加运算则将用到累加器acc结果保存到硬件乘法器的3个16Байду номын сангаас寄存器中即结果高字寄存器reshi结果低字寄存器reslo及结果扩张寄存器sumext

第5章 MSP430单片机片内外围 章 单片机片内外围 模块

5.4 硬件乘法器

5.4.1 硬件乘法器的结构

硬件乘法器的特性:

能够实现16×16位、8×16位、16×8位或8×8 位运算。 支持无符号乘法(MPY)。 有符号乘法(MPYS)。 无符号乘加(MAC)。 有符号乘加(MACS)。

5.4.4 硬件乘法器的举例

例1:8×8无符号乘法运算,乘积放在R8和R9中。 #include <msp430x44x.h> MOV #0,&RESLO ;清结果寄存器 MOV #0,&RESHI; MOV . B #012h,&0130h ; 第一操作数 MOV . B #034h,&0138h ; 第一操作数 NOP NOP MOV &RESLO,R8;读结果,将结果低字节存入R8 MOV &RESHI,R9;读结果,将结果高字节存入R9 RET

5.4.2 硬件乘法器寄存器

5.4.3 硬件乘法器的操作

硬件乘法寄存器的乘数来源于两个操作数寄存器OP1和OP2,OP1可来源于4 个寄存器MPY、MPYS、MAC及MACS,它们能确定乘法的类型。 乘法运算执行之后,一般需要4个周期数,结果暂存在紧接着的32位乘积寄存 器中。如果执行乘加运算,则将用到累加器ACC, 结果保存到硬件乘法器的3个16位寄存器中,即结果高字寄存器(RESHI)、 结果低字寄存器(RESLO)及结果扩张寄存器(SUMEXT)。

1. 硬件乘法器步骤 第一操作数OP1,来源于寄存器MPY, MPYS, MAC或MACS之一。 写第二操作数OP2,写入完毕,乘法运算立即开始。 读结果,乘法结果存放在RESHI、RESLO及SUMEXT。 2. 硬件乘法器操作时的注意事项 第二个操作数写入完毕,乘法运算就开始。一般在取出结果之前插入 1~2条指令,以保证运算时间的需要。 在一个器件中只有一个硬件乘法器,如果遇到多处使用的情况,必须 在每一次使用完成后再进行下一次使用。 结果扩展寄存器(SUMEXT)内容,与运算类型及结果都有关系。 无论进行何种运算,只要操作数类型为8×8型,操作过程就要使用寄 存器的绝对地址,而不能使用符号形式。但是16×16位运算就可以使 用寄存器符号形式。 在最初两步操作,即传送第一及第二操作数给乘法器之间,不允许接 受中断请求。

fpga中做乘法

fpga中做乘法

FPGA中可以使用各种方法进行乘法,下面列举了几种常用的方法:

1. 逻辑门级乘法器:可以利用AND、OR、XOR等逻辑门实现简单的乘法运算。

例如,使用一系列AND运算将两个输入位相乘,再使用逻辑门将它们相加得到结果。

这种方法的优点是简单易实现,缺点是速度较慢。

2. Booth编码乘法器:Booth编码乘法器是一种基于查找表的乘法器,利用Booth编码对乘数进行编码,根据编码结果进行查表并得到部分积,再将部分积相加得到最终结果。

这种方法的优点是速度较快,缺点是复杂度较高。

3. 数字信号处理(DSP)乘法器:FPGA中通常会包含一些专门设计用于进行高速乘法运算的DSP乘法器。

这些乘法器通常具有高速、低功耗和占用较少逻辑资源等特点,非常适合在FPGA中实现乘法运算。

4. 基于硬件乘法器的乘法:某些FPGA芯片可能包含硬件乘法器,可以直接使用硬件乘法器进行乘法运算。

硬件乘法器通常具有非常高的速度和低的功耗,但会占用较多的资源。

需要根据具体的应用场景和性能要求选择适合的乘法方法。

kk16位硬件乘法器

十六位硬件乘法器一、摘要1、设计要求:位宽十六,输入2个两位十进制相乘,能在数码管上显示积的信息!2、原理说明:十六位硬件乘法器可以分解为由2个8位2进制相乘得到,但要求输入十进制,故可用8421BCD码将2位十进制译成8位2进制即可,本次课设使用的是移位相加法来实现乘法!3、开发板使用说明:sw1到sw8开关是数据输入按键,即一次可同时输入八位数据,对于运算y=a*b,由于加入了辅助程序,总共要输入2次,每次输入的数据分别代表a转换为2进制的八位数,b转换成2进制的八位数,。

每按一次按键s3,即输入当前所设定的八位数据一次,,在数据输入完成后,按s2,进行运算,并由数码管输出用十进制表示的结果。

二、正文1、系统设计方案提出由于是2位的十进制,输入的数据不是很大,转换为二进制也是8位,故想到使用移位相加的方法来实现乘法的功能,同时移位相加是最节省资源的一种方法,其思路是乘法通过逐项移位相加来实现,根据乘数的每一位是否为1,若为1将被乘数移位相加,比较简单,适合本次课程设计。

2,电路划分,电路主要由3部分组成,第一部分是将输入的十进制译成2进制,第二部分是乘法器部分,第三部分是将得到的16位二进制结果译为十进制!第一部分LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY chengshu ISPORT (a: IN STD_LOGIC_VECTOR(3 DOWNTO 0);cq : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) );END chengshu;ARCHITECTURE behav OF chengshu ISBEGINprocess(a)begincase a iswhen "0000" => cq<="00000000";when "0001" => cq<="00001010";when "0010" => cq<="00010100";when "0011" => cq<="00011110";when "0100" => cq<="00101000";when "0101" => cq<="00110010";when "0110" => cq<="00111100";when "0111" => cq<="01000110";when "1000" => cq<="01010000";when "1001" => cq<="01011010";when others =>null;end case ;end process;end ARCHITECTURE behav;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity add8 isport(a:in std_logic_vector(7 downto 0);b:in std_logic_vector(3 downto 0);qout:out std_logic_vector(7 downto 0));end add8;architecture ab of add8 issignal tmp1,tmp2,tmp:std_logic_vector(8 downto 0); begintmp1<='0'&a;tmp2<="00000"&b;tmp<=tmp1+tmp2;qout<=tmp(7 downto 0);end ab;第二部分:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cheng isport ( start : in std_logic;a : in std_logic_vector(7 downto 0);b : in std_logic_vector(7 downto 0);y : out std_logic_vector(15 downto 0)); end cheng;architecture behav of cheng issignal ql : std_logic_vector(7 downto 0);signal qz : std_logic_vector(7 downto 0);signal qy : std_logic_vector(15 downto 0);beginprocess(a,ql,qz,qy,b,start)variable q0 : std_logic_vector(15 downto 0); variable q1 : std_logic_vector(15 downto 0); variable q2 : std_logic_vector(15 downto 0); variable q3 : std_logic_vector(15 downto 0); variable q4 : std_logic_vector(15 downto 0); variable q5 : std_logic_vector(15 downto 0); variable q6 : std_logic_vector(15 downto 0); variable q7 : std_logic_vector(15 downto 0); variable q8 : std_logic_vector(15 downto 0); beginql<=a;qz<=b;q8:="0000000000000000";q7:="00000000"&ql;q0:="00000000"&ql;q7:=q7+q7;q1:=q7;q7:=q7+q7;q2:=q7;q7:=q7+q7;q3:=q7;q7:=q7+q7;q4:=q7;q7:=q7+q7;q5:=q7;q7:=q7+q7;q6:=q7;q7:=q7+q7;if start='1' thenif qz(0)='1' then q8:=q8+q0;end if;if qz(1)='1' then q8:=q8+q1;end if;if qz(2)='1' then q8:=q8+q2;end if;if qz(3)='1' then q8:=q8+q3;end if;if qz(4)='1' then q8:=q8+q4;end if;if qz(5)='1' then q8:=q8+q5;end if;if qz(6)='1' then q8:=q8+q6;end if;if qz(7)='1' then q8:=q8+q7;end if;end if;qy<=q8;end process;y<=qy;end behav;第三部分IBRARY ieee;USE ieee.std_logic_1164.all;USE ieee.std_logic_unsigned.all;USE ieee.std_logic_arith.all;ENTITY jian ISport( a: in std_logic_vector(15 downto 0) ;cnt : OUT std_logic_vector(15 downto 0) ;qout: OUT std_logic_vector(3 downto 0) );END ;ARCHITECTURE hdlarch OF jian ISBEGINprocess(a)beginif a>8999 then cnt<=a-9000;qout<="1001";elsif a>7999 then cnt<=a-8000;qout<="1000";elsif a>6999 then cnt<=a-7000;qout<="0111";elsif a>5999 then cnt<=a-6000;qout<="0110";elsif a>4999 then cnt<=a-5000;qout<="0101";elsif a>3999 then cnt<=a-4000;qout<="0100";elsif a>2999 then cnt<=a-3000;qout<="0011";elsif a>1999 then cnt<=a-2000;qout<="0010";elsif a>999 then cnt<=a-1000;qout<="0001";else cnt<=a ;qout<="0000";end if;end process;end hdlarch;LIBRARY ieee;USE ieee.std_logic_1164.all;USE ieee.std_logic_unsigned.all;USE ieee.std_logic_arith.all;ENTITY jian1 ISport( a: in std_logic_vector(15 downto 0) ;cnt : OUT std_logic_vector(15 downto 0) ;qout: OUT std_logic_vector(3 downto 0) );END ;ARCHITECTURE hdlarch OF jian1 ISBEGINprocess(a)beginif a>899 then cnt<=a-900;qout<="1001";elsif a>799 then cnt<=a-800;qout<="1000";elsif a>699 then cnt<=a-700;qout<="0111";elsif a>599 then cnt<=a-600;qout<="0110";elsif a>499 then cnt<=a-500;qout<="0101";elsif a>399 then cnt<=a-400;qout<="0100";elsif a>299 then cnt<=a-300;qout<="0011";elsif a>199 then cnt<=a-200;qout<="0010";elsif a>99 then cnt<=a-100;qout<="0001";else cnt<=a ;qout<="0000";end if;end process;end hdlarch;LIBRARY ieee;USE ieee.std_logic_1164.all;USE ieee.std_logic_unsigned.all;USE ieee.std_logic_arith.all;ENTITY jian2 ISport( a: in std_logic_vector(15 downto 0) ;cnt : OUT std_logic_vector(15 downto 0) ;qout: OUT std_logic_vector(3 downto 0) );END ;ARCHITECTURE hdlarch OF jian2 ISBEGINprocess(a)beginif a>89 then cnt<=a-90;qout<="1001";elsif a>79 then cnt<=a-80;qout<="1000";elsif a>69 then cnt<=a-70;qout<="0111";elsif a>59 then cnt<=a-60;qout<="0110";elsif a>49 then cnt<=a-50;qout<="0101";elsif a>39 then cnt<=a-40;qout<="0100";elsif a>29 then cnt<=a-30;qout<="0011";elsif a>19 then cnt<=a-20;qout<="0010";elsif a>9 then cnt<=a-10;qout<="0001";else cnt<=a ;qout<="0000";end if;end process;end hdlarch;但是由于2个8位2进制在开发板上不好输入和最后的16位不好译成十进制,故加入几段辅助程序减少其输入次数!library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity test_in isport(test_in: in std_logic_vector(7 downto 0);test_out_ah: out std_logic_vector(3 downto 0);test_out_al: out std_logic_vector(3 downto 0);test_out_bh: out std_logic_vector(3 downto 0);test_out_bl: out std_logic_vector(3 downto 0);clk: in std_logic;led: out std_logic);end entity;architecture one of test_in issignal test_temp: std_logic_vector(7 downto 0);signal cnt: std_logic;begin--process(clk)--begin--if(clk'event and clk='1')then--led<='1';--else--led<='0';--end if;--end process;process(clk)beginif(clk'event and clk='0')thencnt<=not cnt;test_temp<=test_in;end if;end process;process(cnt)begin--if(clk'event and clk='0')thenif(cnt='1')thentest_out_ah<=test_temp(7 downto 4);test_out_al<=test_temp(3 downto 0);elsetest_out_bh<=test_temp(7 downto 4);test_out_bl<=test_temp(3 downto 0);end if;--end if;end process;end architecture;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity de_shake isport(key_in: in std_logic;key_out: out std_logic;clk_1_2hz: in std_logic);end entity;architecture one of de_shake issignal a,b,c: std_logic;beginprocess(clk_1_2hz)variable key_out_temp: std_logic;beginif(clk_1_2hz'event and clk_1_2hz='1')thena<= key_in;b<=a;c<=b;key_out_temp:=(a and b and c );end if;key_out<=key_out_temp;end process;end architecture;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity fre_deshake isport(clk_50m: in std_logic;clk_deshake: out std_logic;clk_50: out std_logic);end entity;architecture one of fre_deshake issignal clk_temp: std_logic_vector(20 downto 0); beginclk_50<=clk_50m;process(clk_50m)beginif(clk_50m'event and clk_50m='1')thenclk_temp<=clk_temp+1;end if;end process;clk_deshake<=clk_temp(20);--clk_deshake(1)<=clk_temp(20);end architecture;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity decode isport(clk_50M: in std_logic;input4: in std_logic_vector(3 downto 0);input3: in std_logic_vector(3 downto 0);input2: in std_logic_vector(3 downto 0);input1: in std_logic_vector(3 downto 0);output: out std_logic_vector(7 downto 0);address: out std_logic_vector(7 downto 0));end entity;architecture one of decode issignal div_clk: std_logic_vector(18 downto 0);signal mode: std_logic_vector(7 downto 0);signal data: std_logic_vector(3 downto 0);begindivclk:process(clk_50M)beginif(clk_50M'event and clk_50M='1')thendiv_clk<=div_clk+1;end if;end process;de_code_01: process(clk_50M,div_clk(18 downto 16))beginif(clk_50M'event and clk_50M='1')thencase div_clk(18 downto 16) iswhen "000"=>mode<="01111111";when "001"=>mode<="10111111";when "010"=>mode<="11011111";when "011"=>mode<="11101111";--when "100"=>--mode<="11110111";--when "101"=>--mode<="11111011";--when "110"=>--mode<="11111101";--when "111"=>--mode<="11111110";when others=>mode<="11111111";end case;end if;end process;de_code_02: process(mode)beginaddress <= mode;case mode iswhen "01111111"=>data<=input4;when "10111111"=>data<=input3;when "11011111"=>data<=input2;when "11101111"=>data<=input1;--when "11110111"=>--data<=input(15 downto 12);--when "11111011"=>--data<=input(11 downto 8);--when "11111101" =>--data<=input(7 downto 4);--when "11111110"=>--data<=input(3 downto 0);when others=>null;end case;end process;decode_03: process(data)begincase data iswhen "0000"=>output<="11000000";when "0001"=>output<="11111001";when"0010"=>output<="10100100";when"0011"=>output<="10110000";when"0100"=>output<="10011001";when"0101"=>output<="10010010";when"0110"=>output<="10000010";when"0111"=>output<="11111000";when"1000"=>output<="10000000";when"1001"=>output<="10010000";--when"1010"=>--output<="10001000";--when"1011"=>--output<="10000011";--when"1100"=>--output<="11000110";--when"1101"=>--output<="10100011";--when"1110"=>--output<="10000110";when others=>output<="10001110";end case;end process;end architecture;第二种方案(无硬件测试)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity mult16_16 isport(clk: in std_logic;start: in std_logic;ina: in std_logic_vector(15 downto 0);inb: in std_logic_vector(15 downto 0);sout: out std_logic_vector(31 downto 0));end entity;architecture one of mult16_16 issignal cout1: std_logic_vector(19 downto 0);signal cout2: std_logic_vector(23 downto 0);signal cout3: std_logic_vector(27 downto 0);signal cout4: std_logic_vector(31 downto 0);signal a4b1: std_logic_vector(19 downto 0);signal a3b1: std_logic_vector(19 downto 0);signal a2b1: std_logic_vector(19 downto 0);signal a1b1: std_logic_vector(19 downto 0);signal a4b2: std_logic_vector(23 downto 0);signal a3b2: std_logic_vector(23 downto 0);signal a2b2: std_logic_vector(23 downto 0);signal a1b2: std_logic_vector(23 downto 0);signal a4b3: std_logic_vector(27 downto 0);signal a3b3: std_logic_vector(27 downto 0);signal a2b3: std_logic_vector(27 downto 0);signal a1b3: std_logic_vector(27 downto 0);signal a4b4: std_logic_vector(31 downto 0);signal a3b4: std_logic_vector(31 downto 0);signal a2b4: std_logic_vector(31 downto 0);signal a1b4: std_logic_vector(31 downto 0);beginprocess(clk)beginif(clk'event and clk='1')thena4b1<=((ina(15 downto 12)*inb(3 downto 0))&"000000000000");a3b1<=("0000"&(ina(11 downto 8)*inb(3 downto 0))&"00000000");a2b1<=("00000000"&(ina(7 downto 4)*inb(3 downto 0))&"0000");a1b1<=("000000000000"&(ina(3 downto 0)*inb(3 downto 0)));a4b2<=((ina(15 downto 12)*inb(7 downto 4))&"0000000000000000");a3b2<=("0000"&(ina(11 downto 8)*inb(7 downto 4))&"000000000000");a2b2<=("00000000"&(ina(7 downto 4)*inb(7 downto 4))&"00000000");a1b2<=("000000000000"&(ina(3 downto 0)*inb(7 downto 4))&"0000");a4b3<=((ina(15 downto 12)*inb(11 downto 8))&"00000000000000000000");a3b3<=("0000"&(ina(11 downto 8)*inb(11 downto 8))&"0000000000000000");a2b3<=("00000000"&(ina(7 downto 4)*inb(11 downto8))&"000000000000");a1b3<=("000000000000"&(ina(3 downto 0)*inb(11 downto 8))&"00000000");a4b4<=((ina(15 downto 12)*inb(15 downto 12))&"000000000000000000000000");a3b4<=("0000"&(ina(11 downto 8)*inb(15 downto 12))&"00000000000000000000");a2b4<=("00000000"&(ina(7 downto 4)*inb(15 downto 12))&"0000000000000000");a1b4<=("000000000000"&(ina(3 downto 0)*inb(15 downto 12))&"000000000000");end if;end process;process(clk)beginif(clk'event and clk='1')thencout1<=a4b1+a3b1+a2b1+a1b1;cout2<=a4b2+a3b2+a2b2+a1b2;cout3<=a4b3+a3b3+a2b3+a1b3;cout4<=a4b4+a3b4+a2b4+a1b4;end if;end process;process(clk,start)beginif(start='1')thensout<="00000000000000000000000000000000";elsesout<=("000000000000"&cout1)+("00000000"&cout2)+("0000"&cout3)+cout4;end if;end process;end architecture;仿真结果三,参考文献资料,EDA技术和VHDL,和同学一起讨论!四,仿真结果,随便输入几个数字后,进行仿真,结果正确,但只能用16进制看结果,因为是译成8421BCD码,是一位十进制数对应4位2进制,最终的结果范围是0~9801,需要16位2进制来对应!五,硬件测试在硬件上进行测试,结果正确!六,实验总结这次课设让我学会了很多东西,刚开始的时候对很多东西不是很理解,后来请教同学,查资料,虽然有些的程序不是自己写的,但跟同学讨论,请教,大概也懂得的那些程序是干什么用的,在最后测试的时候,在仿真阶段,刚开始一直仿真不对,以为是程序错误,但检验后程序并没有错误,由于是8421BCD码故应该用十六进制进行仿真。

乘法器原理

乘法器原理乘法器原理是计算机科学中非常重要的原理,它是实现计算机高效计算的基础。

本文将详细介绍乘法器原理的相关知识,包括乘法器的基本概念、实现原理、应用场景等方面。

一、乘法器的基本概念乘法器是一种用于计算两个数的乘积的计算机硬件。

它是计算机中最常用的算术电路之一,可以用来进行乘法运算,是实现计算机高效计算的关键组件之一。

乘法器通常由多个门电路组成,其中最常用的是AND门、OR门和XOR门。

它的输入是两个二进制数,输出是它们的乘积。

乘法器的输出通常是一个二进制数,它的位数等于输入的两个二进制数的位数之和。

乘法器的输出可以通过一系列的加法器进行加法运算,从而得到最终的结果。

乘法器的性能取决于它的位宽、延迟和功耗等因素。

在实际应用中,乘法器的位宽通常是32位或64位,延迟时间通常在几个时钟周期内,功耗通常在几个瓦特以下。

二、乘法器的实现原理乘法器的实现原理可以分为两种,即基于布斯算法的乘法器和基于蒙哥马利算法的乘法器。

1、布斯算法乘法器布斯算法乘法器是一种基于移位和加法的乘法器。

它通过将一个数分解成多个部分,然后逐位进行计算,最后将它们相加得到最终结果。

布斯算法乘法器的核心是部分积的计算,它可以通过移位和相加操作来实现。

例如,假设要计算两个8位二进制数A和B的乘积,可以将A和B分别分解成4位二进制数A1、A0和B1、B0,然后按照如下方式计算部分积:P1 = A1 × B0P2 = A0 × B1P3 = A0 × B0P4 = A1 × B1最终的结果可以通过将这些部分积相加得到:P = P1 × 2^8 + P2 × 2^4 + P3 + P4 × 2^12布斯算法乘法器的主要优点是简单、易于实现,但它的缺点是速度较慢,需要多次移位和加法操作。

2、蒙哥马利算法乘法器蒙哥马利算法乘法器是一种基于模重复平方和模乘的算法。

它利用模运算的性质,将乘法转化为模运算和加法运算,从而减少了乘法器的复杂度和延迟时间。

MSP430F6638硬件乘法器

硬件乘法器 —— 应用举例(1/6)

◆例1、利用硬件乘法器计算两个16位无符号整数的乘积,

0x1234×0x5678第二个操作数写入完毕,乘法运算就开始。结 果存放在RESLO,RESHI中。ACLK = REFO= 32.768kHz, MCLK = SMCLK = 默认 DCO 。

相关程序如下: #include <msp430f6638.h> void main(void) { WDTCTL = WDTPW+WDTHOLD; // 关闭看门狗定时器 MPY = 0x1234; //载入第一个无符号整型操作数,表明是无符号乘法 OP2 = 0x5678; //载入第二个无符号整型操作数后,开始运算 __bis_SR_register(LPM4_bits); // 进入LPM4 // 调试用,验证结果是否正确,正确结果RESLO == 0x0060 //RESHI == 0x0626 __no_operation(); }

◆ 小数部分

32位乘法器支持定点信号处理功能。在定点信号处理过程中,小数通 常用一个固定的十进制小数来表示。 使用Q格式的表示方法来区分不同范围的小数。不同的Q格式表示不同 的十进制小数点位置。 下图表示有符号Q15数据的16位数据格式。小数点后的每一位,精度 为1/2,最高有效位是符号位。最大的负数为08000h,最大的正数是 07FFFh。因此,16位有符号的Q15格式可以表示从–1.0到 0.999969482≈1.0的数。

▲ 在饱和模式下,乘法器可以防止有符号数操作结果的上溢

生下溢,结果将被设置成负的最大有效值。这可以减少控制系 统在溢出条件下的数学结果。

▲ 如果发生上溢,结果将被设置成正的最大有效值。如果发

▲ 饱和模式只能在需要的时候使能,在使用完之后应禁止。

移位相加8位硬件乘法器电路设计

电子技术课程设计----移位相加8位硬件乘法器电路计学院: 华科学院专业: 通信工程班级:通信052201H姓名: 张茹学号:200522080122指导教师:柴婷婷2007年12月30日一,设计任务与要求--------------------(3)1,内容2,要求二,总体框图---------------------------(3)1,电路的总体框图2,框图的说明3,设计思路4,方案设计三,选择器件与功能模块-----------------(5)1,选择器件各功能模块及功能说明四,功能模块----------------------------(8)1,ADDER8B的模块2,ANDARITH的模块3,ARICTL的模块4,REG16B的模块5,SREG8B的模块五,总体设计电路图----------------------(14)1,总体原理图2,仿真波形图3,管脚分配图4,硬件验证情况六,心得体会--------------------------------------(18)移位相加8位硬件乘法器一.设计任务与要求1.内容: 由8位加法器构成的以时序逻辑方式设计的8位乘法器乘法通过逐向移位加原理来实现,从被乘数的最低位开始,若为1,则乘数左移与上一次和相加;若为0,左移后以全零相加,直至被乘数的最高位。

2.要求: (1) 重点掌握VHDL设计电路模块(2)在掌握8位加法器设计的基础上,进一步掌握8×8位乘法器的设计;(3)进一步学习开发系统,掌握MAX+PLUS II的设计流程。

二.总体框图(电路的总体框图)1,说明:此电路由五部分组成2,它们分别是控制器,锁存器,寄存器,乘法器,加法器。

1控制器是一个乘法器的控制模块,用来接受实验系统上的连续脉冲。

2锁存器起锁存的作用,它可以锁存8位乘数。

3移位寄存器起移位的作用,便于被乘数可以逐位移出。

4乘法器功能类似一个特殊的与非门。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

什么是硬件乘法器

导读:我根据大家的需要整理了一份关于《什么是硬件乘法器》的内容,具体内容:硬件乘法器你听过吗?哈哈,我也是最近才听过这个词的。

下面将由我带大家一起来学习学习下吧,希望对大家有所收获!硬件乘法器,其基础就是加法器结构,它已经是现代计算机中必不...

硬件乘法器你听过吗?哈哈,我也是最近才听过这个词的。

下面将由我带大家一起来学习学习下吧,希望对大家有所收获!

硬件乘法器,其基础就是加法器结构,它已经是现代计算机中必不可少的一部分。

[1] 乘法器的模型就是基于"移位和相加"的算法。

在该算法中,乘法器中每一个比特位都会产生一个局部乘积。

第一个局部乘积由乘法器的LSB产生,第二个乘积由乘法器的第二位产生,以此类推。

如果相应的乘数比特位是1,那么局部乘积就是被乘数的值,如果相应的乘数比特位是0,那么局部乘积全为0。

每次局部乘积都向左移动一位。

乘法器可以用更普遍的方式来表示。

每个输入,局部乘积数,以及结果都被赋予了一个逻辑名称(如A1、A2、B1、B2),而这些名称在电路原理图中就作为了信号名称。

在原理图的乘法例子中比较信号名称,就可以找到乘法电路的行为特性。

在乘法器电路中,乘数中的每一位都要和被乘数的每一位相与,并产生其相应的乘积位。

这些局部乘积要馈入到全加器的阵列中(合适的时候也可以用半加器),同时加法器向左移位并表示出乘法结果。

最后得到的乘积项在CLA电路中相加。

注意,某些全加器电路会将信号带入到进位输入

端(用于替代邻近位的进位)。

这就是一种全加器电路的应用;全加器将其输入端的任何三个比特相加。

随着乘数和被乘数位数的增加,乘法器电路中的加法器位树也要相应的增加。

通过研究CLA电路的特性,也可以在乘法器中开发出更快的加法阵列。

DSP中的专用硬件乘法器

在DSPs中具有硬件连线逻辑的高速"与或"运算器(乘法器和累加器),取两个操作数到乘法器中进行乘法运算,并将乘积累加到累加器中,这些操作都可以在单个周期内完成。

在数字信号处理算法中,乘法和累加是基本的大量的运算。

例如:在卷积运算、数字滤波、FFT、相关计算和矩阵运算等算法中,都有大量的类似于A(k)B(n-k)的运算。

DSPs中设置的硬件乘法器和MAC(乘法并累加)一类的指令,可以使这些运算速度大大提高。

乘法速度越快,DSPs性能就越好。

在通用的微处理器中,乘法指令是由一系列加法来实现的,故需许多个指令周期来完成。

相比而言,DSPs芯片的特征就是有一个专用的硬件乘法器。

硬件乘法器的实现原理

首先,分析一下两个二进制数相乘的过程:

由此可见,硬件乘法器的实现本质是"移位相加"。

对于二进制,乘数和被乘数的每一位非0即1,相当于乘数中的每一位分别和被乘数的每一个体位进行与运算,并产生其相应的乘积位。

这些局部乘积左移一位与上次的和相加。

即从乘数的最低位开始,若其为1,则被乘数左移一位并与上

一次的和相加;若为0,左移后以全零相加,如此循环至乘数的最高位。

硬件乘法器的电路结构

从理论上讲,两个二进制N位操作数相乘,乘积的总宽度为2N,因此需要一个宽度为2N的移位寄存器和加法器。

但在实际执行过程中,一是每个部分积的宽度和移位相加的有效宽度都为N位,从资源的利用率角度考虑,仅需N位宽度的加法器即可;二是按照先移位再相加的原理,两个N 位操作数则需要2N个时钟周期才能完成整个运算,在此考虑将移位和相加两个运算步骤合并,从速度上就可在N个时钟周期内完成。

根据上述分析,8位移位相加型硬件乘法器应包括16位锁存器、8位移位寄存器、8位乘法器、8位加法器等4个组成部分。

具体电路结构如图1所示。

锁存器发挥着锁存的作用,用于锁存部分和。

移位寄存器则具备移位作用,当加载信号有效时乘数将加载于8位右位寄存器,随着时钟上升沿的到来,乘数即由低位开始逐位移出。

乘法器功能类似一个特殊的与门。

有两个输入端口,一个端口用于输入8位并行操作数(被乘数),另一个端口在时钟信号控制下输入由移位寄存逐步移出的串行操作数,并将这两个操作数进行与运算。

加法器用于将本次时钟脉冲控制下得到的8位部分积与锁存于锁存器高8位的前一个时钟脉冲下得到的部分和相加。