arm中断处理流程

arm中断处理过程

Arm的中断处理流程1:芯片输入管脚,按照中断的配置发生变化,(比如产生上升沿),arm芯片内部就会检测到中断。

2:ARM要求中断向量表必须放置在从0开始、连续8×4字节的空间内。

所以地址空间“0x00000000-0x00000032”就是所谓的中断向量表。

3:arm检测到中断后,会根据中断的类型强行设置PC寄存器的值。

把当前cpsr的内容保存到spsr_mode . 然后改变cpsr得内容。

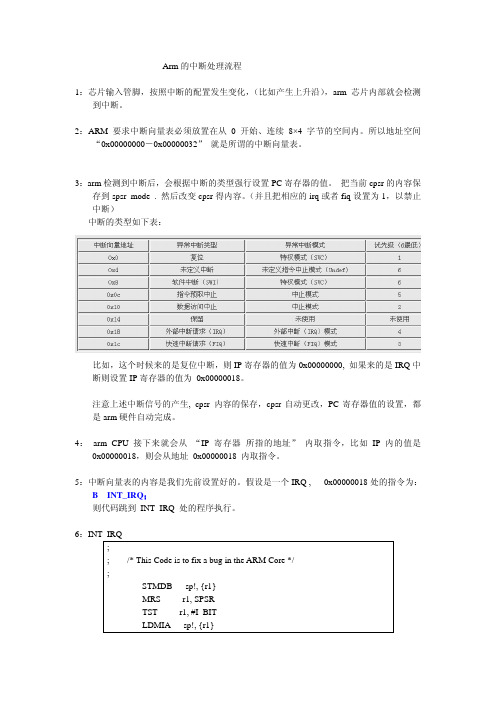

(并且把相应的irq或者fiq设置为1,以禁止中断)中断的类型如下表:比如,这个时候来的是复位中断,则IP寄存器的值为0x00000000, 如果来的是IRQ中断则设置IP寄存器的值为 0x00000018。

注意上述中断信号的产生, cpsr 内容的保存,cpsr自动更改,PC寄存器值的设置,都是arm硬件自动完成。

4: arm CPU接下来就会从“IP寄存器所指的地址”内取指令,比如IP内的值是0x00000018,则会从地址 0x00000018 内取指令。

5:中断向量表的内容是我们先前设置好的。

假设是一个IRQ , 0x00000018处的指令为:B INT_IRQ;则代码跳到 INT_IRQ 处的程序执行。

6:INT_IRQ;; /* This Code is to fix a bug in the ARM Core */;STMDB sp!, {r1}MRS r1, SPSRTST r1, #I_BITLDMIA sp!, {r1}SUBNES pc,lr,#4; //保存环境; /* End ARM Core Fix */STMDB sp!, {a1 - v7, fp, ip, lr} ; Save context…… //里面会进行某些状态位判断,以确定具体是哪个中断,然后调用相应处理程序//恢复环境INT_IRQ_EXITLDMIA sp!, {a1 - v7, fp, ip, lr} ; Restore contextSUBS pc, lr, #4 ; Return to interrupted codeEND ; end file7:What happens if an interrupt occurs as it is being disabled?Applies to:If an interrupt is received by the core during execution of an instruction that disables interrupts, the ARM7 family will still take the interrupt. This occurs for both IRQ and FIQ interrupts.For example, consider the follow instruction sequence:MRS r0, cpsrORR r0, r0, #I_Bit:OR:F_Bit ;disable IRQ and FIQ interruptsMSR cpsr_c, r0If an IRQ interrupt is received during execution of the MSR instruction, then the behavior will be as follows:The IRQ interrupt is latchedThe MSR cpsr, r0 executes to completion setting both the I bit and the F bit in the CPSRThe IRQ interrupt is taken because the core was committed to taking the interrupt exception before the I bit was set in the CPSR. The CPSR (with the I bit and F bit set) is moved to the SPSR_irq上面是arm的一个bug。

中断异常处理流程

计算机体系结构中,异常或者中断是处理系统中突发事件的一种机制,几乎所有的处理器都提供这种机制。

异常主要是从处理器被动接受的角度出发的一种描述,指意外操作引起的异常。

而中断则带有向处理器主动申请的意味。

但这两种情况具有一定的共性,都是请求处理器打断正常的程序执行流程,进入特定程序的一种机制。

若无特别说明,对“异常”和“中断”都不作严格的区分。

本文结合经过实际验证的代码对ARM9中断处理流程进行分析,并设计出基于S3C2410芯片的外部中断处理程序。

1.异常中断响应和返回系统运行时,异常可能会随时发生。

当一个异常出现以后,ARM微处理器会执行以下几步操作:1) 将下一条指令的地址存入相应连接寄存器LR,以便程序在处理异常返回时能从正确的位置重新开始执行。

2)将CPSR复制到相应的SPSR中。

3)根据异常类型,强制设置CPSR的运行模式位。

4) 强制PC从相关的异常向量地址取下一条指令执行,从而跳转到相应的异常处理程序处。

这些工作是由ARM内核完成的,不需要用户程序参与。

异常处理完毕之后,ARM微处理器会执行以下几步操作从异常返回:1)将连接寄存器LR的值减去相应的偏移量后送到PC中。

2)将SPSR复制回CPSR中。

3) 若在进入异常处理时设置了中断禁止位,要在此清除。

这些工作必须由用户在中断处理函数中实现。

为保证在ARM处理器发生异常时不至于处于未知状态,在应用程序的设计中,首先要进行异常处理。

采用的方式是在异常向量表中的特定位置放置一条跳转指令,跳转到异常处理程序。

当ARM处理器发生异常时,程序计数器PC会被强制设置为对应的异常向量,从而跳转到异常处理程序。

当异常处理完成以后,返回到主程序继续执行。

可以认为应用程序总是从复位异常处理程序开始执行的,因此复位异常处理程序不需要返回。

2.异常处理程序设计2.1 异常响应流程由于向量表的限制,只能有一条指令B完成32MB范围内的跳转,并不能保证所有的异常处理函数都位于32MB范围内。

ARM系统中触摸屏的中断处理方法.

ARM系统中触摸屏的中断处理方法摘要:实现了一种全集成可变带宽中频宽带低通滤波器,讨论分析了跨导放大器-电容(OTA—C)连续时间型滤波器的结构、设计和具体实现,使用外部可编程电路对所设计滤波器带宽进行控制,并利用ADS软件进行电路设计和仿真验证。

仿真结果表明,该滤波器带宽的可调范围为1~26 MHz,阻带抑制率大于35 dB,带内波纹小于0.5 dB,采用1.8 V电源,TSMC 0.18μm CMOS工艺库仿真,功耗小于21 mW,频响曲线接近理想状态。

关键词:Butte随着嵌入式微处理器性能的提高,集成的外围接口设备越来越多,而外围设备与处理器之间多采用中断方式进行通信,即使在没有操作系统的情况下,也常需要对多个外围设备的中断处理例程进行动态加载,从而实现对多个外围设备的集中动态管理。

同时,中断功能可以解决CPU内部运行速度远远快于外部总线速度而产生的等待延时问题。

因此,嵌入式微处理器的应用设计中,中断处理通常是系统的核心任务之一。

1 触摸屏(1)触摸屏简介随着多媒体信息查询的与日俱增,人们越来越关注触摸屏。

触摸屏具有坚固耐用、反应速度快、节省空间、易于交流等许多优点,作为一种最新的电脑输入设备,它是目前最简单、方便、自然的人机交互方式。

它赋予多媒体崭新的面貌,是极富吸引力的全新多媒体交互设备。

触摸屏由触摸检测部件和触摸屏控制器组成。

触摸检测部件安装在显示器屏幕前面,用于检测用户触摸位置,接收信息后送至触摸屏控制器;触摸屏控制器的主要作用是从触摸点检测装置上接收触摸信息,并将它转换成触点坐标后送给CPU,同时能接收CPU发来的命令并加以执行。

按照触摸屏的工作原理和传输信息的介质,触摸屏可以分为4种,即电阻式、电容感应式、红外线式以及表面声波式。

这里采用的是四线电阻屏。

(2)S3C2410A触摸屏控制器S3C2410A触摸屏的外接电路主要是控制上下两层导电层的通断情况以及取电压,取电压之后还需要将这个模拟量转换成数字量,这部分工作主要是靠S3C2410A芯片中的模数转换器来实现的。

cortex-r 中断处理

cortex-r 中断处理

Cortex-R系列处理器是ARM公司设计的一系列实时处理器,主要用于需要高可靠性和实时响应的应用,如汽车和工业控制。

在Cortex-R系列处理器中,中断处理是一个重要的部分,用于处理异步事件,如硬件故障、外部信号等。

中断处理在Cortex-R系列中主要涉及到以下几个组件:

1. NVIC (Nested Vectored Interrupt Controller): 嵌套向量中断控制器是ARM Cortex-R核的一部分,用于管理中断。

它能够配置优先级、子优先级、向量地址等。

2. 中断向量表: 在Cortex-R核中,中断向量表是一个固定的内存区域,用于存放中断处理程序的地址。

当一个中断发生时,Cortex-R 核会跳转到这个表中对应的地址开始执行。

3. 中断处理程序: 中断处理程序是用于处理特定中断的代码。

它通常会快速检查中断源,然后根据需要执行相应的操作。

在Cortex-R系列中,中断处理的基本流程如下:

1. 当一个中断发生时,Cortex-R核的NVIC会接收这个中断请求,并检查是否允许该中断。

2. 如果允许,NVIC会保存当前执行上下文(如程序计数器、寄存器等),然后跳转到中断向量表中的对应地址开始执行中断处理程序。

3. 中断处理程序执行完毕后,NVIC会恢复之前保存的执行上下

文,然后返回到被中断的程序继续执行。

需要注意的是,由于Cortex-R系列是实时处理器,因此中断处理需要尽可能快地完成,以避免影响实时任务的执行。

同时,由于中断可能会在任何时候发生,因此中断处理程序的设计也需要特别小心,以避免出现意外的行为。

ARM中断向量表与响应流程

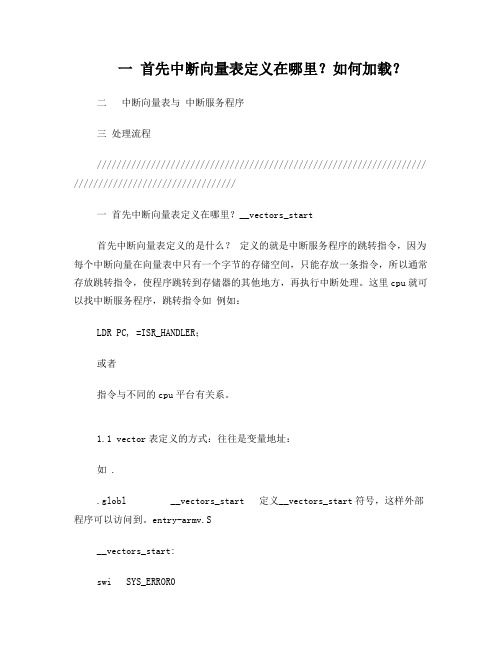

一首先中断向量表定义在哪里?如何加载?二中断向量表与中断服务程序三处理流程/////////////////////////////////////////////////////////////////// /////////////////////////////////一首先中断向量表定义在哪里?__vectors_start首先中断向量表定义的是什么?定义的就是中断服务程序的跳转指令,因为每个中断向量在向量表中只有一个字节的存储空间,只能存放一条指令,所以通常存放跳转指令,使程序跳转到存储器的其他地方,再执行中断处理。

这里cpu就可以找中断服务程序,跳转指令如例如:LDR PC, =ISR_HANDLER;或者指令与不同的cpu平台有关系。

1.1 vector表定义的方式:往往是变量地址:如 ..globl __vectors_start 定义__vectors_start符号,这样外部程序可以访问到。

entry-armv.S__vectors_start:swi SYS_ERROR0b vector_und + stubs_offsetldr pc, .LCvswi + stubs_offsetb vector_pabt + stubs_offsetb vector_dabt + stubs_offsetb vector_addrexcptn + stubs_offsetb vector_irq + stubs_offsetb vector_fiq + stubs_offsetARM的异常处理向量表在entry-armv.S文件中:1.2 中断向量表类型From ARM.globl __vectors_start 定义__vectors_start符号,这样外部程序可以访问到。

__vectors_start:定义异常(地址逻辑自上而下0x00----0x1c) 跟具体的cpu 特性有关ARM( swi SYS_ERROR0 )向量0:reset,但是这里被修改了,如果是cpu跑到了0地址,用软件中断SYS_ERROR0来处理.THUMB( svc #0)向量1THUMB( nop)向量2W(b) vector_und + stubs_offset 向量3 #未定义指令异常W(ldr) pc, .LCvswi + stubs_offset 向量4#软中断W(b) vector_pabt + stubs_offset #向量5指令预取异常中断(Prefetch Abort )W(b) vector_dabt + stubs_offset #向量6数据中止W(b) vector_addrexcptn + stubs_offset #向量7地址异常These aren't too critical.W(b) vector_irq + stubs_offset #向量8.IRQ(一般中断)W(b) vector_fiq + stubs_offset #向量9 FIQ(快速中断)/*关于.globl指令:.global/.globl 命令.global symbol.global 使得连接程序(ld)能够识别 symbl声明symbol是全局可见的。

ARM中断程序的原理和实现

ARM中断程序的原理和实现引言:中断是计算机系统中一种特殊的事件,它可以打断当前正在执行的程序,并执行一段特定的代码。

在ARM架构中,中断主要由两部分组成:中断处理程序和中断控制器。

本文将介绍ARM中断程序的原理和实现,包括中断的基本概念、中断的分类、中断的处理过程以及中断控制器的实现方式。

一、中断的基本概念中断可以看作是外部设备向CPU发送一个请求的一种方法。

当外部设备发生一些特定的事件时(如按键、时钟周期等),它会产生一个中断请求信号,通知CPU去处理相应的事件。

CPU收到中断请求信号后,会暂停当前的任务,保存现场并跳转到中断处理程序来处理中断。

二、中断的分类1.外部中断:外部中断是由外设产生的中断信号,如GPIO、串口等。

当外设产生中断请求信号时,中断控制器会将信号传递给CPU,触发相应的中断处理程序。

2.软件中断:软件中断是由软件主动触发的中断,通过软件指令可以触发中断控制器发送中断请求信号给CPU。

软件中断可以用于实现系统调用、任务切换等功能。

三、中断的处理过程1.中断请求:外部设备发生特定事件,产生中断请求信号。

中断请求信号会被中断控制器接收并传递给CPU。

2.中断响应:CPU收到中断请求信号后,会立即响应中断,并执行中断处理程序。

在响应中断之前,CPU需要保存当前的现场(包括程序计数器PC、寄存器等)。

3.中断处理:CPU跳转到中断处理程序的入口地址,开始执行中断处理程序。

中断处理程序通常用来处理中断事件,并根据需要进行中断服务例程的调用。

4.中断返回:中断处理程序执行完毕后,CPU会根据中断处理程序的返回指令返回到原来的程序中,并恢复之前保存的现场。

同时,中断控制器会清除中断请求信号,使其能够接受新的中断请求。

四、中断控制器的实现方式ARM架构中,中断控制器常用的实现方式包括级联式中断控制器和向量式中断控制器。

1.级联式中断控制器:级联式中断控制器是一种层级结构的中断控制器。

它包含多个级别的中断控制器,每个级别对应一组中断请求。

异常及中断处理

一.ARM异常中断处理概述1、中断的概念中断是一个过程,是CPU在执行当前程序的过程中因硬件或软件的原因插入了另一段程序运行的过程。

因硬件原因引起的中断过程的出现是不可预测的,即随机的,而软中断是事先安排的。

2、中断源的概念我们把可以引起中断的信号源称之为中断源。

3、中断优先级的概念ARM处理器中有7种类型的异常,按优先级从高到低的排列如下:复位异常(Reset)、数据异常(Data Abort)、快速中断异常(FIQ)、外部中断异常(IRQ)、预取异常(Prefetch Abort)、软件中断(SWI)和未定义指令异常(Undefined instruction)二.ARM体系异常种类下面是ARM的7种异常当异常发生时,处理器会把PC设置为一个特定的存储器地址。

这一地址放在被称为向量表(vector table)的特定地址范围内。

向量表的入口是一些跳转指令,跳转到专门处理某个异常或中断的子程序。

当异常产生时, ARM core:拷贝CPSR 到SPSR_<mode>设置适当的CPSR 位:改变处理器状态进入ARM 状态改变处理器模式进入相应的异常模式设置中断禁止位禁止相应中断(如果需要)保存返回地址到LR_<mode>设置PC 为相应的异常向量返回时, 异常处理需要:从SPSR_<mode>恢复CPSR从LR_<mode>恢复PCNote:这些操作只能在ARM 态执行.当异常发生时,分组寄存器r14和SPSR用于保存处理器状态,操作伪指令如下。

R14_<exception_mode> = return linkSPSR_<exception_mode> = CPSRCPSR[4∶0] = exception mode numberCPSR[5] = 0 /*进入ARM状态*/If <exception_mode> = = reset or FIQ thenCPSR[6] = 1 /*屏蔽快速中断FIQ*/CPSR[7] = 1 /*屏蔽外部中断IRQ*/PC = exception vector address异常返回时,SPSR内容恢复到CPSR,连接寄存器r14的内容恢复到程序计数器PC。

arm cortex-m中断处理流程

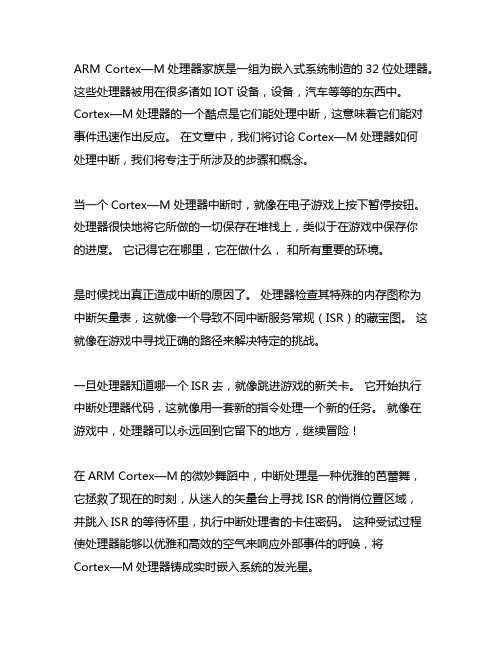

ARM Cortex—M处理器家族是一组为嵌入式系统制造的32位处理器。

这些处理器被用在很多诸如IOT设备,设备,汽车等等的东西中。

Cortex—M处理器的一个酷点是它们能处理中断,这意味着它们能对事件迅速作出反应。

在文章中,我们将讨论Cortex—M处理器如何

处理中断,我们将专注于所涉及的步骤和概念。

当一个Cortex—M处理器中断时,就像在电子游戏上按下暂停按钮。

处理器很快地将它所做的一切保存在堆栈上,类似于在游戏中保存你

的进度。

它记得它在哪里,它在做什么,和所有重要的环境。

是时候找出真正造成中断的原因了。

处理器检查其特殊的内存图称为

中断矢量表,这就像一个导致不同中断服务常规(ISR)的藏宝图。

这就像在游戏中寻找正确的路径来解决特定的挑战。

一旦处理器知道哪一个ISR去,就像跳进游戏的新关卡。

它开始执行

中断处理器代码,这就像用一套新的指令处理一个新的任务。

就像在

游戏中,处理器可以永远回到它留下的地方,继续冒险!

在ARM Cortex—M的微妙舞蹈中,中断处理是一种优雅的芭蕾舞,

它拯救了现在的时刻,从迷人的矢量台上寻找ISR的悄悄位置区域,

并跳入ISR的等待怀里,执行中断处理者的卡住密码。

这种受试过程

使处理器能够以优雅和高效的空气来响应外部事件的呼唤,将Cortex—M处理器铸成实时嵌入系统的发光星。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ARM编程特别是系统初始化代码的编写中通常需要实现中断的响应、解析跳转和返回等操作,以便支持上层应用程序的开发,而这往往是困扰初学者的一个难题。

中断处理的编程实现需要深入了解ARM内核和处理器本身的中断特征,从而设计一种快速简便的中断处理机制。

需要说明的是,具体的上层高级语言编写的中断服务函数不在本文的讨论范围之内。

ARM处理器异常中断处理概述

当异常中断发生时,系统执行完当前指令后,将跳转到相应的异常中断处理程序处执行。

当异常中断处理程序执行完成后,程序返回到发生中断的指令的下一条指令处执行。

在进入异常中断处理程序时,要保存被中断的程序的执行现场。

从异常中断处理程序退出时,要恢复被中断的程序的执行现场。

ARM体系中通常在存储地址的低端固化了一个32字节的硬件中断向量表,用来指定各异常中断及其处理程序的对应关系。

当一个异常出现以后,ARM微处理器会执行以下几步操作:

1)保存处理器当前状态、中断屏蔽位以及各条件标志位;

2)设置当前程序状态寄存器CPSR中相应的位;

3)将寄存器lr_mode设置成返回地址;

4)将程序计数器(PC)值设置成该异常中断的中断向量地址,从而跳转到相应的异常中断处理程序处执行。

在接收到中断请求以后, ARM处理器内核会自动执行以上四步,程序计数器PC总是跳转到相应的固定地址。

从异常中断处理程序中返回包括下面两个基本操作:

1)恢复被屏蔽的程序的处理器状态;

2)返回到发生异常中断的指令的下一条指令处继续执行。

当异常中断发生时,程序计数器PC所指的位置对于各种不同的异常中断是不同的,同样,返回地址对于各种不同的异常中断也是不同的。

例外的是,复位异常中断处理程序不需要返回,因为整个应用系统是从复位异常中断处理程序开始执行的。

支持中断跳转的解析程序

解析程序的概念和作用

如前所述,ARM处理器响应中断的时候,总是从固定的地址开始的,而在高级语言环境下开发中断服务程序时,无法控制固定地址开始的跳转流程。

为了使得上层应用程序与硬件中断跳转联系起来,需要编写一段中间的服务程序来进行连接。

这样的服务程序常被称作中断解析程序。

每个异常中断对应一个4字节的空间,正好放置一条跳转指令或者向PC寄存器赋值的数据访问指令。

理论上可以通过这两种指令直接使得程序跳转到对应的中断处理程序中去。

但实际上由于函数地址值为未知和其它一些问题,并不这么做。

这里给出一种常用的中断跳转流程:

图1中断跳转流程图

这个流程中的关键部分是中断向量表,为了让解析程序能找到向量表,应该将向量表的地址固定化(编程者自定义)。

这样,整个跳转流程的所有程序地址都是固定的,当中断触发后,就可以自动运行。

其中,只有向量表的内容是可变的,编程者只要在向量表中填入正确的目标地址值就可以了。

这使得上层中断处理程序和底层硬件跳转有机地联系起来。

解析过程示例

以一次IRQ跳转为例,假定中断向量表定义在0x00400000开始的外部RAM空间:

图2 中断解析示例流程

图2中实线表示的流程都用ARM汇编语言编写,一般作为boot代码的一部分放在系统的底层模块中。

填写向量表的操作可以在上层应用程序中方便地实现,比如在C语言中: *( int *(0x00400018)) = (int) ISR_IRQ;这样就将IRQ中断的服务程序入口地址(0x00300260)填写到中断向量表中的固定地址0x00400018开始的4字节空间了。

如此一来,就可避免在应用程序中计算中断的跳转地址,并且可以很方便的选择不同的函数作为指定中断的服务程序。

当然,在程序开发时要合理开辟好向量表,避免对向量表地址空间不必要的写操作。

解析程序的扩展

众所周知,在ARM处理器中会包含很多中断源,通常会在ARM内核外面扩展一个中断控制器来管理各种原因产生的中断。

比如,三星公司的S3C4510B处理器中的IRQ/FIQ类型的中断源可以有21个,S3C44B0X 有26个。

这时候中断处理的原理还是一样的,无非是向量表更长,并且当一个中断触发以后,需要在解析程序里查询中断控制器的状态来确定具体的中断源,再根据中断源来读取向量表中的对应地址内容。

其处理流程可用图3表示。

图3 中断解析的扩展

相比图2,图3中多了一级的跳转,也就是在第一次解析跳转到IRQ/FIQ服务程序中后,再进行第二次的解析_中断源的识别。

向量中断的处理

一些处理器在设计外扩的中断控制器时提供了一种叫做“向量中断”的中断跳转机制。

这与前文叙述的扩展解析跳转流程有所不同,它不需要软件来识别具体的中断源,也就是不需要添加图3中的IRQ/FIQ 服务程序,而完全由硬件自动跳转到对应的中断地址。

其它跳转流程的原理都是一样的。

这相当于扩展了ARM内核的硬件中断向量表,减小了中断响应延时。

以S3C44B0X处理器的外部中断0为例,需要在其对应的硬件固定跳转地址0x00000020处添加指令:ldr pc,=HandlerEINT,使得程序跳转到其服务程序HandlerEINT0处执行。

图4 向量中断解析流程示例

结语

本文介绍的中断处理机制是嵌入式编程中常常采用的方法,其原理是通用的。

当然,在实际开发中,需要根据系统处理器ARM内核的中断特征和处理器自身的中断控制器特点具体细化流程图中的各个步骤和改写参考代码。

arm 中断处理

1. 首先就是知道ARM状态下37个寄存器包括通用寄存器、程序计数器、状态寄存器。

绿颜色的就是相应模式下的私有寄存器。

就是说程序一般运行在系统和用户模式下,使用的是系统和用户模式下的通用寄存器,当有异常发生时,比如FIQ,那么系统将切换到FIQ模式下,相应的就会采用FIQ模式下的寄存器,其中绿颜色的就是只在FIQ模式下才会用到的寄存器。

2. 在模式切换的过程中,要保护系统和用户模式下的通用寄存器状态,以便在异常处理完成之后程序能正常返回。

因为FIQ模式下R8-R14为其私有寄存器,所以切换到FIQ模式的过程中,系统和用户模式下的通用寄存器的R8-R14就不用保护了,所以减少了对寄存器存取的需要,从而可以快速的进行FIQ处理,故称为FIQ。

这就是FIQ的私有寄存器比其它模式多的原因。

切到FIQ模式需要保护的寄存器为R0~R7,切到SVC,IRQ,ABORT.和未定义模式需要保护的寄存器为R0~R12

3. 异常处理的动作。

当然这都是CPU内核自己干的。

以FIQ为例。

当CPU切入FIQ模式时,

第一,将原来执行程序的下一条指令地址保存到LR中,就是将R14保存到R14_fiq里面。

第二,拷贝CPSR到SPSR_fiq。

第三,改变CPSR模式位的值,改到FIQ模式。

第四,改变PC值,将其指向异常处理向量所指的下一条指令。

离开异常处理的时候,

第一,将LR(R14_fiq)赋给PC。

第二,将SPSR(SPSR_fiq)拷贝到CPSR。

第三,清除中断禁止标志(如果开始时置位了)。

4.异常中断向量

异常中断的向量地址

地址异常中断类型入口时处理器的操作模式

0x00000000 复位超级用户

0x00000004 未定义指令未定义

0x00000008 软件中断超级用户

0x0000000c 中止(预取指)中止

0x00000010 中止(数据)中止

0x00000014 保留保留

0x00000018 IRQ IRQ

0x0000001c FIQ FIQ

异常中断优先级

中断优先级

复位最高

数据异常

FIQ

IRQ

预取指异常中断

未定义指令和软件中断最低

5.当发生IRQ中断时

第一,模式进入到IRQ里面。

第二,PC跳到0x00000018处运行。

因为这是IRQ的中断入口。

第三,通过0x00000018:LDR PC, IRQ_ADDR。

跳转到相应的中断服务程序。

这个里面就有个确定哪个中断源的问题了。

那就有优先级的问题了。

每个中断源会有自己的中断服务程序。

第四,得到中断源有硬件实现和软件处理两种方式。

比如LPC21XX的就是利用硬件方式,为了利用向量中断控制器的优点,IRQ中断向量入口处代码做了修改,变成

0x00000018:LDR PC, [PC, #-0xff0]。

这条指令从内存映射地址0xfffff030处获得数据装载到PC,这样就能够直接从硬件中获得中断源。

这样就减少了中断延迟。

记得,三星的S3C44B0

好象采用的是用软件确定中断源,因此要建立中断向量表。

好久不用了,记不清了。

第五,得到中断源,就知道要跳到哪个中断服务程序去了。

一般都是这么定义的。

Timer0_Handler HANDLER Timer0 。

这种格式是调用一种宏定义,目的是保护现场,跳到中断服务程序。