ARM中的中断

arm中断处理过程

Arm的中断处理流程1:芯片输入管脚,按照中断的配置发生变化,(比如产生上升沿),arm芯片内部就会检测到中断。

2:ARM要求中断向量表必须放置在从0开始、连续8×4字节的空间内。

所以地址空间“0x00000000-0x00000032”就是所谓的中断向量表。

3:arm检测到中断后,会根据中断的类型强行设置PC寄存器的值。

把当前cpsr的内容保存到spsr_mode . 然后改变cpsr得内容。

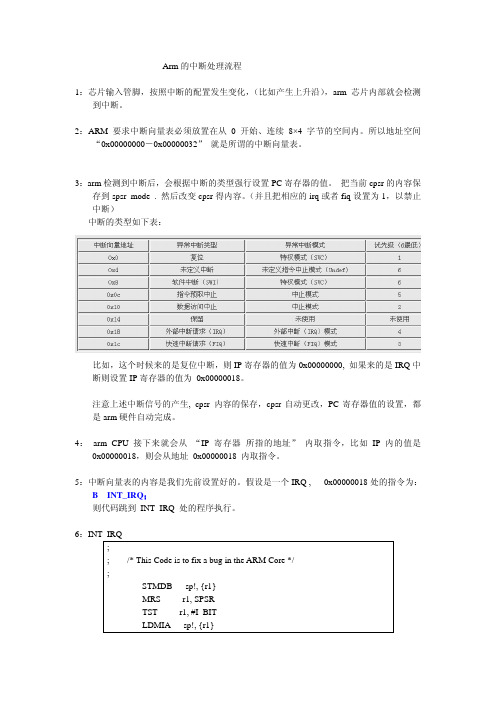

(并且把相应的irq或者fiq设置为1,以禁止中断)中断的类型如下表:比如,这个时候来的是复位中断,则IP寄存器的值为0x00000000, 如果来的是IRQ中断则设置IP寄存器的值为 0x00000018。

注意上述中断信号的产生, cpsr 内容的保存,cpsr自动更改,PC寄存器值的设置,都是arm硬件自动完成。

4: arm CPU接下来就会从“IP寄存器所指的地址”内取指令,比如IP内的值是0x00000018,则会从地址 0x00000018 内取指令。

5:中断向量表的内容是我们先前设置好的。

假设是一个IRQ , 0x00000018处的指令为:B INT_IRQ;则代码跳到 INT_IRQ 处的程序执行。

6:INT_IRQ;; /* This Code is to fix a bug in the ARM Core */;STMDB sp!, {r1}MRS r1, SPSRTST r1, #I_BITLDMIA sp!, {r1}SUBNES pc,lr,#4; //保存环境; /* End ARM Core Fix */STMDB sp!, {a1 - v7, fp, ip, lr} ; Save context…… //里面会进行某些状态位判断,以确定具体是哪个中断,然后调用相应处理程序//恢复环境INT_IRQ_EXITLDMIA sp!, {a1 - v7, fp, ip, lr} ; Restore contextSUBS pc, lr, #4 ; Return to interrupted codeEND ; end file7:What happens if an interrupt occurs as it is being disabled?Applies to:If an interrupt is received by the core during execution of an instruction that disables interrupts, the ARM7 family will still take the interrupt. This occurs for both IRQ and FIQ interrupts.For example, consider the follow instruction sequence:MRS r0, cpsrORR r0, r0, #I_Bit:OR:F_Bit ;disable IRQ and FIQ interruptsMSR cpsr_c, r0If an IRQ interrupt is received during execution of the MSR instruction, then the behavior will be as follows:The IRQ interrupt is latchedThe MSR cpsr, r0 executes to completion setting both the I bit and the F bit in the CPSRThe IRQ interrupt is taken because the core was committed to taking the interrupt exception before the I bit was set in the CPSR. The CPSR (with the I bit and F bit set) is moved to the SPSR_irq上面是arm的一个bug。

arm中断嵌套的原理

arm中断嵌套的原理摘要:1.引言2.arm 中断嵌套的原理2.1 arm 的中断向量表2.2 中断嵌套的实现2.3 中断嵌套的优点和应用3.arm 中断嵌套的实现3.1 硬件方面的支持3.2 软件方面的支持4.arm 中断嵌套的注意事项4.1 中断处理时间的考虑4.2 中断优先级的处理5.总结正文:在嵌入式系统中,中断处理是一个常见的功能。

ARM 处理器提供了丰富的中断处理功能,使得开发者可以灵活地处理各种中断事件。

中断嵌套是ARM 中断处理的一个重要特性,可以提高系统的响应速度和处理效率。

本文将详细介绍ARM 中断嵌套的原理、实现以及注意事项。

首先,我们需要了解ARM 中断嵌套的原理。

ARM 的中断向量表是一个关键概念。

中断向量表是一个存储中断向量地址的数组,用于快速定位和处理各种中断事件。

当有中断请求时,处理器会根据中断类型号在中断向量表中查找对应的中断向量地址,然后跳转到该地址执行中断处理程序。

中断嵌套的实现主要依赖于中断向量表的布局和中断处理程序的设计。

在一个系统中,可能会有多个中断源,它们的中断向量地址可能会相互重叠。

为了实现中断嵌套,我们需要保证中断向量表中的下一个中断向量地址在当前中断处理程序执行完毕之前可以被访问到。

这样,当一个中断请求到来时,处理器可以在当前中断处理程序执行完毕后,快速跳转到下一个中断向量地址,执行下一个中断处理程序。

中断嵌套的优点主要体现在可以提高系统的响应速度和处理效率。

例如,当一个外部中断请求到来时,处理器可以在执行当前中断处理程序的同时,响应外部中断请求,这样可以减少中断处理的时间。

此外,中断嵌套还可以实现中断优先级的功能,使得高优先级的中断请求能够更快地被处理。

要实现ARM 中断嵌套,需要硬件和软件两方面的支持。

在硬件方面,处理器需要支持中断嵌套,这通常需要处理器具有中断控制器,可以实现中断请求的排队和嵌套处理。

在软件方面,需要编写适当的中断处理程序,确保在当前中断处理程序执行完毕之前可以跳转到下一个中断向量地址。

ARM微处理器的七种运行模式

ARM微处理器的七种运⾏模式

ARM微处理器的七种运⾏模式:

1. ⽤户模式(usr):正常的程序执⾏状态

2. 快速中断模式(fiq):⽤于处理快速中断,对⾼速数据传输或通道处理。

3. 中断模式(irq):对⼀般情况下的中断进⾏处理。

4. 管理模式(svc):操作系统使⽤的保护模式,处理软件中断swi reset。

5. 系统模式(sys):运⾏具有特权的操作系统任务

6. 数据访问终⽌模式(abt):数据或指令预取终⽌时进⼊该模式,可⽤于处理存储器故障、实现虚拟存储器和存储器保护。

7. 未定义指令终⽌模式(und):未定义的指令执⾏时进⼊该模式,处理未定义的指令陷阱,当未定义的指令执⾏时进⼊该模式,可⽤于

⽀持硬件协处理器的软件仿真。

特别说明

运⾏模式可以通过软件来进⾏模式切换,或者发⽣各类中断、异常时CPU⾃动进⼊相应的模式。

除⽤户模式外,其余6种⼯作模式都属于特权模式。

特权模式中除了系统模式以外的其余5种模式称为异常模式。

⼤多数程序运⾏于⽤户模式。

进⼊特权模式是为了处理中断、异常、或者访问被保护的系统资源。

arm中断实验的实验报告

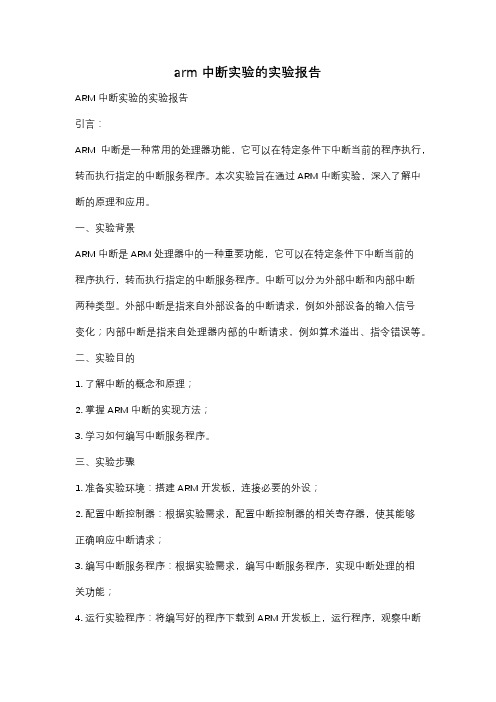

arm中断实验的实验报告ARM中断实验的实验报告引言:ARM中断是一种常用的处理器功能,它可以在特定条件下中断当前的程序执行,转而执行指定的中断服务程序。

本次实验旨在通过ARM中断实验,深入了解中断的原理和应用。

一、实验背景ARM中断是ARM处理器中的一种重要功能,它可以在特定条件下中断当前的程序执行,转而执行指定的中断服务程序。

中断可以分为外部中断和内部中断两种类型。

外部中断是指来自外部设备的中断请求,例如外部设备的输入信号变化;内部中断是指来自处理器内部的中断请求,例如算术溢出、指令错误等。

二、实验目的1. 了解中断的概念和原理;2. 掌握ARM中断的实现方法;3. 学习如何编写中断服务程序。

三、实验步骤1. 准备实验环境:搭建ARM开发板,连接必要的外设;2. 配置中断控制器:根据实验需求,配置中断控制器的相关寄存器,使其能够正确响应中断请求;3. 编写中断服务程序:根据实验需求,编写中断服务程序,实现中断处理的相关功能;4. 运行实验程序:将编写好的程序下载到ARM开发板上,运行程序,观察中断的触发和响应情况;5. 实验结果分析:根据实验结果,分析中断的触发条件、中断服务程序的执行情况等。

四、实验结果与分析通过实验,我们成功实现了ARM中断的功能。

在实验过程中,我们配置了外部设备的中断引脚,当引脚状态发生变化时,中断控制器会产生中断请求,处理器则会立即中断当前的程序执行,转而执行中断服务程序。

在中断服务程序中,我们可以完成一些特定的操作,例如读取外设数据、更新系统状态等。

实验结果表明,中断服务程序能够正确地响应中断请求,并完成相应的操作。

五、实验总结本次实验通过ARM中断的实验,我们深入了解了中断的原理和应用。

中断是一种重要的处理器功能,它可以在特定条件下中断当前的程序执行,转而执行指定的中断服务程序。

掌握了中断的实现方法和编写中断服务程序的技巧,我们可以在实际应用中更好地利用中断功能,提高系统的响应速度和稳定性。

arm的内部函数

arm的内部函数ARM的内部函数是指在ARM架构下实现的一些特定功能的函数。

这些函数在ARM处理器中运行,并且可以直接访问处理器的内部寄存器和功能模块,以提供更高效的操作和更好的性能。

本文将介绍一些常见的ARM内部函数,并对它们的功能和用法进行详细解释。

1. __disable_irq()函数:该函数用于禁用中断。

在ARM处理器中,中断是一种常见的硬件机制,用于处理外部事件或异常情况。

通过调用__disable_irq()函数,可以在需要的时候临时禁用中断,以确保特定的代码段可以在不被中断干扰的情况下执行。

一旦禁用了中断,除非显式地调用__enable_irq()函数,否则中断将一直被禁用。

2. __enable_irq()函数:该函数用于启用中断。

与__disable_irq()函数相对应,__enable_irq()函数可以在需要的时候重新启用中断。

一旦中断被启用,处理器将可以响应外部事件和异常情况,并按照相应的中断处理程序执行相应的操作。

3. __nop()函数:该函数用于插入一个空操作。

在某些情况下,为了实现精确的时间延迟或调整代码的执行顺序,我们可能需要在代码中插入一些不执行任何操作的语句。

__nop()函数可以实现这个目的,它会在执行期间执行一个空操作,不会对处理器的状态或寄存器产生任何影响。

4. __wfi()函数:该函数用于使处理器进入等待模式。

等待模式是一种低功耗状态,在该状态下,处理器会暂停执行并进入休眠状态,以降低功耗。

通过调用__wfi()函数,我们可以将处理器置于等待模式,直到外部事件或中断唤醒处理器。

5. __dmb()函数:该函数用于实现数据屏障操作。

在多核或多线程的系统中,为了保证数据的一致性和可见性,我们需要使用数据屏障操作。

__dmb()函数可以在代码中插入数据屏障指令,以确保特定的内存访问顺序和数据同步。

6. __rev()函数:该函数用于反转字节顺序。

在某些应用场景下,我们需要将数据的字节顺序进行反转,以满足特定的数据格式要求。

ARM中断控制器

VIC是处于芯片外设和ARM内核之间的一个模块,对芯片所有外设中断进行管理,决定哪些中断源可以产生中断、产生哪种类型的中断以及中断后执行哪段服务程序。

ARM处理器内核具有两个中断输入:向量中断请求(IRQ)和快速中断请求(FIQ)。

向量中断控制器使用32个中断请求输入,可将其编程分配为FIQ或向量IRQ类型。

可编程分配机制意味着外设中断的优先级可动态分配和调整。

中断向量控制器的作用?答:ARM处理器内核本身只有FIQ和IRQ这2条中断输入信号线,只能接受2个中断源,而向量中断控制器就使LPC2000系列ARM具有正确快速处理多个外部中断事件的能力的模块。

快速中断请求具有最高优先级。

向量IRQ具有可编程的中断优先级。

特性:*ARM PrimeCell向量中断控制器 *映射到AHB地址空间以高速访问*支持32个向量IRQ *16个可编程的中断优先级*在每个可编程优先级内的硬件优先级固定 *硬件优先级屏蔽*任何中断都可分配为FIQ *软件中断功能中断源分配表向量中断控制器(VIC)具有32个中断请求输入,可将其编程分为3类:FIQ,向量IRQ和非向量IRQ。

可编程分配机制意味着不同外设的中断优先级可以动态分配并调整。

快速中断请求:具有最高优先级。

如果分配给FIQ的请求多余1个,VIC将中断请求“相或”后向ARM处理器产生FIQ信号,当只有一个中断被分配为FIQ时可实现FIQ的最短等待时间,因为FIQ服务程序只要简单的启动器件的处理就可以产生了。

但如果分配给FIQ级的中断多于一个,FIQ服务程序需要读取FIQ状态寄存器来识别产生中断请求的FIQ中断源。

向量IRQ具有中等优先级。

该级别可分配32个请求中的16个。

32个请求中的任意一个中断都可分配到16个向量IRQsolt中的任意一个,其中slot0具有最高优先级,而solt15则为最低优先级。

非向量IRQ中断的优先级最低VIC将所有的中断向量和非向量IRQ相或,向ARM处理器产生IRQ信号。

ARM的启动和中断向量表

ARM的启动和中断向量表启动的⽅式对于S3C2440⽽⾔,启动的⽅式有两种,⼀是Nor Flash⽅式启动,⼆是Nand Flash⽅式启动。

使⽤Nor Flash⽅式启动Nor Flash的地址范围如下0x0000.0000—0x0800.0000 (2M Nor Flash)⽚内的BootSRAM地址被置为0x4000.0000—0x4000.DFFF (4K BootSRAM)由于可以在Nor Flash直接运⾏代码,因此BootSRAM被映射到别的地址上去,可作为其他⽤途。

程序映像直接存放到NOR FLASH⾥⾯,中断向量表存放在0x0000.0000开始的8×4⼤⼩的空间中。

中断产⽣时,PC被置为相对应的向量地址。

如上电或者按Reset键时,PC直接置为0x00,从NOR FLASH的0x00处开始执⾏。

使⽤NAND Flash⽅式启动此时,⽚内的BootSRAM地址被置为0x0000.0000—0x0800.0000 (4K BootSRAM)NAND Flash地址接NFCE由于NAND Flash中不能运⾏代码,因此必须复制到内存之中再运⾏。

程序映像存放在NAND FLASH中,中断向量表位置在程序映像的最前⾯。

由于NAND FLASH不能运⾏代码,系统上电或者Reset的时候,内置的NAND FLASH 将访问控制接⼝,并将中断向量表和引导代码⾃动加载到内部SRAM(此时该SRAM 定位于起始地址空间0x00000000,容量为4KB),并且置PC值为0x00运⾏程序(这⼀切是有芯⽚内部的硬件逻辑完成的)。

之后,SRAM 中的引导程序将操作系统镜像加载到SDRAM 中,操作系统就能够在SDRAM 中运⾏。

启动完毕,4KB 的启动SRAM 就可以⽤于其他⽤途。

中断向量表的设置ARM中的异常与中断总共有7种按响应优先级从⾼到低按中断向量表顺序复位复位数据中⽌未定义指令中断FIQ SWIIRQ预取指令中⽌预取指令中⽌数据中⽌异常未定义指令、SWI IRQFIQARM要求中断向量表必须放置在从0地址开始,连续8×4字节的空间内(ARM720T和ARM9、ARM10也⽀持从0xFFFF0000开始的⾼地址向量表),各异常和中断向量在向量表中的位置如下地址中断0x00Reset0x04Undef0x08SWI0x0C Prefetch Abort0x10Data Abort0x14(Reserved)0x18IRQ0x2C FIQ0x2C FIQ当中断产⽣时ARM处理器强制把PC指针置为中断向量表中相对应的向量地址。

新手必看 ARM里中IRQ与FIQ的不同

新手必看ARM里中IRQ与FIQ的不同

熟悉ARM学习的朋友一定知道,ARM运行时有着非常多的模式,中断模式(IRQ)和快速中断模式(FIQ)就是其中两种。

之所以特别提及到这两种模式,是因为在入门阶段,很多人对这两种模式的区别并不了解。

所以经常会造成两种模式混淆的情况,本文将为大家介绍这两种模式的区别,并简单的进行比较。

在进行比较之前,首先对这两种模式的概念进行介绍。

IRQ (InterruptRequest)指中断模式。

FIQ(FastInterrupt Request)指快速中断模式。

IRQ与FIQ是ARM处理器的两种不同编程模式(ARM有7种处理模式)。

两者的不同

1、在FIQ中,开发者必须进快处理中断请求,并离开这个模式。

2、IRQ可以被FIQ所中断,但FIQ不能被IRQ所中断,在处理FIQ时必须要关闭中断。

3、FIQ的优先级比IRQ高。

4、FIQ模式下,比IRQ模式多了几个独立的寄存器。

不要小看这几个寄存器,ARM在编译的时候,如果FIQ中断处理程序足够用这几个独立的寄存器来运作,它就不会进行通用寄存器的压栈,这样也省了一些时间。

5、FIQ的中断向量地址在0x0000001C,而IRQ的在0x00000018。

(也有的在FFFF001C以及FFFF0018)写过完整汇编系统的都比较明白这点的差别,18只能放一条指令,为了不与1C处的FIQ冲突,这个地方只能跳转,而FIQ不一样,1C以后没有任何中断向量表了,这样可以直接在1C处放FIQ的中断处理程序,由于跳转的范围限制,至少减少一条跳转指令。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一、S5PV210中中断的特点1、特点• Supports 93 vectored IRQ interrupts• Fixed hardware interrupts priority levels• Programmable interrupt priority levels• Supports Hardware interrupt priority level masking• Programmable interrupt priority level masking• Generates IRQ and FIQ• Generates Software interrupt2、FIQ与IRQ的区别1)FIQ和IRQ并不是中断源,而是中断的类型,我们可以将一个中断源设置成FIQ也可以设置成IRQ。

2)FIQ是快速中断,IRQ是一般中断,FIQ的响应时间比IRQ短。

3)FIQ的优先级高于IRQ。

4)FIQ的分组寄存器(R8~R14)比IRQ(R13~R14)多。

当在FIQ产生的时候,R8~R14不需要保存,响应的速度会快。

3、S5PV210的中断源二、原理图分析三、如何以中断的方式来检测按键:GPH2_2(EINT18) 、GPH2_3(EINT19) 按键的检测:轮询:将GPIO配置成输入…….中断:将GPIO配置成外部中断…….1、GPIO的配置,将一个GPIO配置成外部中断2、外部中断的触发方式(高电平、低电平、上升沿、下降沿)3、外部中断的开关寄存器0 = Enables Interrupt 打开中断1 = Masked 关闭中断4、外部中断判断寄存器0 = Not occur 外部中断没有发生1 = Occur interrupt 触发了中断该寄存器的作用:1)读该寄存器,可以知道对应的中断源是否触发。

2)写该寄存器,可以实现清除中断,如果一个中断不清除,CPU就会认为该中断还是存在的,就会再次触发该中断,形成循环。

所以我们在中断处理程序中,需要清除中断。

清中断的方法:如果一个中断已经触发,该寄存器的相应位会自动置1,我们需要向该位写个“1”,就可以将该位清0,写“0”无效。

这是PEND寄存器的特点例如:清EINT18EXT_INT_2_PEND |= (1<<2);5、IRQ的状态寄存器通过该寄存器,可以得到某个IRQ类型中断源是否发生的状态。

6、中断类型设置寄存器7、打开中断的寄存器例:打开EINT18和EINT19VIC0INTENABLE |= (1<<16);EXT_INT_2_MASK &= ~(0x3<<2);8、关闭中断的寄存器例:关闭EINT18和EINT19VIC0INTENCLEAR |= (1<<16);EXT_INT_2_MASK |= (0x3<<2);9、VIC向量地址寄存器ISR ----- Interrupt Service Routine 中断处理程序该寄存器的内容是当前正在响应的中断服务程序的入口地址,我们可以通过该地址去调用中断服务程序。

向该寄存器写任何值,都可以清除中断,一般情况下,中断的清除都是在ISR的结束位置。

10、每个中断源的向量地址寄存器注意:该每个VIC(共有4个)有32个这样的寄存器,当我们在做中断初始化的时候,需要安装中断,安装中断的时候,要将中断服务程序的入口地址,写到对应的向量地址寄存器中。

例:void eint18_19_isr(void){//点灯//清中断}如何实现中断向量的安装???VIC0VECTADDR16 = (unsigned int)eint18_19_isr;EINT16~EINT31的向量地址寄存器= 中断服务程序的入口地址四、中断的响应过程。

以外部中断EINT18为例,分析中断的响应过程。

1、start.S_start:ldr sp, =0x40000000 //初始化管理模式的stack,stack在DDR2中mov r0, #0x53msr CPSR, r0 //对CPSR[7:0] = 010 10011,管理模式,arm状态、关闭FIQ、IRQ打开b main //进入C环境2、当一个IRQ中断发生的时候,首先进入IRQ中断的入口地址:PC = 0x00000018, 分析0x18地址上是什么内容???0x18地址是s5pv210内容iROM中的BL0,samsung固化。

3、在iRom的0x18地址有一个跳转指令,跳转到iRAM中异常中断向量表中。

PC = 0xD0037418 ???4、异常中断向量的安装int_init(void) //中断初始化的时候调用{//vector table of exception initializepExceptionUNDEF = (unsigned long)exceptionundef;//undefinepExceptionSWI = (unsigned long)exceptionswi;//software interruptpExceptionPABORT = (unsigned long)exceptionpabort;//pabortpExceptionDABORT = (unsigned long)exceptiondabort;//data abort pExceptionIRQ = (unsigned long)IRQ_handle;//IRQpExceptionFIQ = (unsigned long)FIQ_handle;//FIQ………………………………………….}分析异常中断向量表的安装:1)pExceptionIRQ#define pExceptionIRQ ( *((volatile unsigned long *)(_Exception_Vector + 0x18)) )#define _Exception_Vector 0xD0037400总结:pExceptionIRQ是0xD0037418地址下的内容,该地址是IRQ异常中断映射后的入口地址2)(unsigned long)IRQ_handle;IRQ_handle: @CPSR会由硬件自动保存到SPSR_irqldr sp, =0xD0037F80 //初始化IRQ模式的stacksub lr, lr, #4 //返回地址的修正,原因:IRQ中断的返回地址是LR-4,与流水线相关stmfd sp!, {r0-r12, lr} //将R0~R12及LR入栈保存,相当于保护现场bl Irq_Isrldmfd sp!, {r0-r12, pc}^ @将SPSR_irq恢复给CPSRLR的值为什么要修正:总结:IRQ_handle子程序的入口地址PC = IRQ_handle5、执行IRQ_handle子程序IRQ_handle: @CPSR会由硬件自动保存到SPSR_irqldr sp, =0xD0037F80sub lr, lr, #4stmfd sp!, {r0-r12, lr}bl Irq_Isrldmfd sp!, {r0-r12, pc}^ @将SPSR_irq恢复给CPSR6、现场保护后,执行Irq_Isrvoid Irq_Isr(void){int i;//VIC的向量地址寄存器unsigned long vicaddr[4] = {VIC0ADDRESS,VIC1ADDRESS,VIC2ADDRESS,VIC3ADDRESS};void (*isr)(void) = (void *)0; //定义一个函数指针,指向0地址for(i=0; i<4; i++){if(intc_getvicirqstatus(i) != 0){isr = (void (*)(void)) vicaddr[i]; //i = 0; isr=((void)(*)(void)) VIC0ADDRESSbreak;}}(*isr)(); //调用前面定义的函数}//查看中断的状态,当某个中断发生,VICIRQSTA TUS的相应的位就会为1,例:EINT18有效:VIC0IRQSTA TUS[16] =1unsigned long intc_getvicirqstatus(unsigned long ucontroller){if(ucontroller == 0)return VIC0IRQSTA TUS;else if(ucontroller == 1)return VIC1IRQSTA TUS;else if(ucontroller == 2)return VIC2IRQSTA TUS;else if(ucontroller == 3)return VIC3IRQSTA TUS;else{}return 0;}分析:isr=((void)(*)(void)) VIC0ADDRESS1)isr 函数指针2)((void)(*)(void)) VIC0ADDRESS当EINT18有效的时候,EINT18对应向量地址寄存器(VIC0VECTADDR16)中的内容会由硬件自动的拷贝到VIC0ADDRESS寄存器中。

总结:isr函数指令,是指向VIC0ADDRESS的内容,在这个位置又是一个isr函数的调用。

PC=VIC0ADDRESS= VIC0VECTADDR16,CPU就开始执行VIC0ADDRESS下的内容。

7、ARM开始执行VIC0VECTADDR16地址下的函数在中断初始化的时候://initialize vector interrupt address with num of init and isr.//中断的安装NUM_EINT16_31---中断号:16// EINT16_31_ISR---中断处理程序//将EINT16_31_ISR的入口地址写入到VEC0VECTADDR16intc_setvectaddr(NUM_EINT16_31, EINT16_31_ISR);分析://the address resigster of vector interrupt initialize//num of int, isr of int//intc_setvectaddr(NUM_EINT16_31, EINT16_31_ISR);该函数的作用:将一个中断服务程序的入口地址,写到该中断对应的向量地址寄存器中。

void intc_setvectaddr(unsigned long intnum, void (*handler)(void)){//VIC0if(intnum<32){//*( (volatile unsigned long *)(0xF2000000+0x100+0x40)=(unsigned int)EINT16_31_ISR得到EINT16_31_ISR的入口地址//VIC0VECTADDR16=EINT16_31_ISR的入口地址*( (volatile unsigned long *)(VIC0VECTADDR + 4*intnum) ) = (unsigned)handler;}//VIC1else if(intnum<64){*( (volatile unsigned long *)(VIC1VECTADDR + 4*(intnum-32)) ) = (unsigned)handler;}//VIC2else if(intnum<96){*( (volatile unsigned long *)(VIC2VECTADDR + 4*(intnum-64)) ) = (unsigned)handler;}//VIC3else{*( (volatile unsigned long *)(VIC3VECTADDR + 4*(intnum-96)) ) = (unsigned)handler;}return;}总结:PC= VIC0VECTADDR16 = (unsigned int ) EINT16_31_ISR;8、执行中断服务程序EINT16_31_ISR外部中断EINT16_31的中断服务程序,在该中断服务中,在去判断子中断EINT18、EINT19void EINT16_31_ISR(void) //EINT18/EINT19{if(EXT_INT_2_PEND & (1<<2))//EINT18发生{GPJ2DAT ^= (1<<0); //toggle D1// clear pending bitEXT_INT_2_PEND = 1<<2;// clear VIC0ADDRESS//VIC0ADDRESS = 0;intc_clearvectaddr();}if(EXT_INT_2_PEND & (1<<3))//EINT19反生{GPJ2DAT ^= (1<<1); //toggle D2// clear pending bitEXT_INT_2_PEND = 1<<3;// clear VIC0ADDRESSintc_clearvectaddr();}}9、中断返回IRQ_handle: @CPSR会由硬件自动保存到SPSR_irq ldr sp, =0xD0037F80sub lr, lr, #4stmfd sp!, {r0-r12, lr}bl Irq_Isrldmfd sp!, {r0-r12, pc}^ @将SPSR_irq恢复给CPSRldmfd sp!, {r0-r12, pc}^分析:1)将R0~R12出栈2)将LR出栈给PC,中断的返回3)将SPSR_irq恢复给CPSR。