arm外部中断笔记

ARM7(sc44b0)外部中断笔记

ARM7(sc44b0)外部中断笔记对于sc44b0它也是一种单片机,一种比较高级的单片机而已,所以他也跟51单片机一样有外部中断,不同51单片机的是,他有8个外部中断源,对应的是8个管脚,(51只有两个,int0和int1,P3.3和P3.4),分别是Port G八个管脚。

而对于外部中断4 \5\6\7很多都是共用寄存器,他们是通过或逻辑公用一个中断请求线。

下面就具体来说说使用外部中断的一些必要的配置。

一,对管脚的配置,因为Port G有三种功能用法,要通过对rPCONG(端口G配置寄存器)的配置来选用Port G的外部中断的功能。

其配置表如下所以应该将其配置为11(设置为中断功能状态);二,中断模式的选择,中断模式有两种,FIQ(快速中断模式)和 IRQ(中断模式)两种,一般没有特殊要求都用IRQ模式即可。

可以通过对中断模式寄存器rINTMOD配置获得。

如表下三,是否允许中断,即中断使能位。

通过对中断控制寄存器INTCON的配置即可,如表下通过对中断控制寄存器的配置即可,可以看出只要让intcon的【1】位置零即可使中断使能。

四,外部中断方式的选择,低电平或上升沿触发呢,还是别的,这就要对外部中断方式寄存器(EXTINT)的配置,其表如下由上表可知,如果要用下降沿触发,就可将EXTINT 的值给0x22222222;将所有的外部中断都设置为下降沿触发。

五,当中断捕抓到以后,要引起什么变化呢?或者说用什么来捕抓呢?在sc44b0中用了两个寄存器来捕抓,一个中断挂起寄存器(INTPND),和外部中断挂起寄存器(EXINTPND),一开始不明白挂起是什么意思,后来才懂,差不多就相当与51单片机的标志位一样,当中断发生后,就将挂起寄存器的对应的某一位置一或置零,外部中断挂起寄存器如表下中断挂起寄存器:当中断产生后,是将INTPND的【21】位置一的;所以,判断有无外部中断,就可以通过读取挂起寄存器对应的为,即可知道是否有无中断。

ARM体系中异常中断种类及处理办法

ARM 体系中异常中断种类及处理办法在ARM 体系中,通常有以下3 种方式控制程序的执行流程:

•在正常程序执行过程中,每执行一条ARM 指令,程序计数器寄存器(PC)的值加4 个字节;每执行一条Thumb 指令,程序计数器寄存器(PC)的值加2 个字节。

整个过程是顺序执行。

•通过跳转指令,程序可以跳转到特定的地址标号处执行,或者跳转到特定的子程序处执行。

其中,B 指令用于执行跳转操作;BL 指令在执行跳转操作的同时,保存子程序的返回地址;BX 指令在执行跳转操作的同时,根据目标地址的最低位可以将程序状态切换到Thumb 状态;BLX 指令执行3 个操作:跳转到目标地址处执行,保存了子程序的返回地址,根据目标地址的最低位可以将程序状态切换到Thumb 状态。

•当异常中断发生时,系统执行完当前指令后,将跳转到相应的异常中断处理程序处执行。

在当异常中断处理程序执行完成后,程序返回到发生中断的指令的下一条指令处执行。

在进入异常中断处理程序时,要保存被中断的程序的执行现场,在从异常中断处理程序退出时,要恢复被中断的程序的执行现场。

ARM的异常处理学习笔记转贴

ARM 的异常处理学习笔记转贴ARM的异常处理这部分比较不好理解。

当异常中断发生时,系统执行完当前指令后,将跳转到相应的异常中断处理程序处执行。

当异常中断处理程序执行完成后,程序返回到发生中断指令的下条指令处执行。

在进入异常中断处理程序时,要保存被中断程序的执行现场,从异常中断处理程序退出时,要恢复被中断程序的执行现场。

1、引起异常的原因(1)、指令执行引起的异常软件中断、未定义指令(包括所要求的协处理器不存在是的协处理器指令)、预取址中止(存储器故障)、数据中止。

(2)、外部产生的中断复位、FIQ、IRQ。

2、ARM中异常中断的种类(1)、复位(RESET)a、当处理器复位引脚有效时,系统产生复位异常中断,程序跳转到复位异常中断处理程序处执行,包括系统加电和系统复位。

b、通过设置PC跳转到复位中断向量处执行称为软复位。

(2)、未定义的指令当ARM处理器或者是系统中的协处理器认为当前指令未定义时,产生未定义的指令异常中断,可以通过改异常中断机制仿真浮点向量运算。

(3)、软件中断这是一个由用户定义的中断指令(SWI)。

可用于用户模式下的程序调用特权操作指令。

在实时操作系统中可以通过该机制实现系统功能调用。

(4)、指令与取终止(Prefech Abort)如果处理器预取的指令的地址不存在,或者该地址不允许当前指令访问,当被预取的指令执行时,处理器产生指令预取终止异常中断。

(5)、数据访问终止(DATAABORT)如果数据访问指令的目标地址不存在,或者该地址不允许当前指令访问,处理器产生数据访问终止异常中断。

(6)、外部中断请求(IRQ)当处理器的外部中断请求引脚有效,而且CPSR的寄存器的I控制位被清除时,处理器产生外部中断请求异常中断。

系统中个外设通过该异常中断请求处7)、快速中断请求(FIQ) 理服务。

(当处理器的外部快速中断请求引脚有效,而且CPSR的F控制位被清除时,处理器产生外部中断请求异常中断。

不同CPU中断技术对比

不同CPU中断技术对比摘要:本文大体论述了80x86,80c51,和ARM在中断源,中断申请方式、中断优先级管理方式、中断的处理过程、中断向量等方面比较。

关键词:CPU,80x86,80c51,,ARM,中断申请方式,中断优先级管理方式,中断的处理过程,中断向量。

正文:一、X86 CPU,80C51,ARM中断源:X86 CPU支持256个中断向量,中断号00H--0FFH 。

0~19是系统预定义的异常和NMI,20~31被Intel保留,如表1。

所以,外部中断从32开始。

CPU处理的流程都一样,在执行完当前指令后,根据中断源提供的中断向量,在IDT中找到并调用相应的服务例程。

X86 CPU中断分为内部中断和外部中断。

内部中断分为:软中断,内部中断和异常,异常分为3种:Fault:可以被更正的错误,异常处理程序的返回地址是产生fault的指令。

Trap:执行trap指令(例如INT 3)后被报告的异常,异常处理程序的返回地址是产生trap指令的后一条指令。

Abort:严重错误,无法继续执行。

外部中断分为:不可屏蔽硬件中断和可屏蔽硬件中断。

不可屏蔽硬件中断(02H):由NMI端引入的中断请求,中断请求不可被屏蔽;可屏蔽硬件中断请求:由INTR端引入,中断请求可由IF=0进行屏蔽,使中断请求不进入。

表180C51的中断系统包括中断源、中断允许寄存器IE、中断优先级寄存器IP、中断矢量等。

在80C51中,只有两级中断优先级。

图1是80C51的中断系统结构示意图。

80C51有5个中断源分别为:两个外部中断源INT0、INT1和三个内部中断源T0、T1定时/计数谥出中断源和串行口发送或接收中断源。

外部中断是由外部信号引起的,它们的中断请求信号分别从引脚INT0和INT1上引入图1ARM 7TDMI具有常规中断(IRQ)、快中断(FIQ)和软件中断(SoftWare Interrupt)三种中方式。

常规中断和快中断都是硬件中断。

外部中断详解

7.1EXTI外部按键中断实验前面我们学习了,LED灯和按键。

实际上对于STM32来说,我们是学习了它的外设GPIO。

这一节我们前面学习的内容,学习STM32的EXTI (External interrupt),即外部中断。

前面的按键章节中,我们检测按键是否被按下的方式是轮询检测的方式,这里我们改为使用中断检测的方式,提高CPU的效率。

7.1.1什么是中断单片机中断系统的概念:什么是中断,我们从一个生活中的例程引入。

比如说你在做A 事,但是突然间来了你想起来了更重要的B事,所以你马上去做B事了,做完之后再回来继续做A事,这个就是中断。

7.1.2什么是单片机的中断?当CPU正在执行一个任务,但突然又发生了一个更高级的任务,CPU必须立即去执行的任务,所以CPU必须中断当前的任务,并保存该任务已经执行的状态和相关信息,然后转而去执行那个更加高级的任务,因此就引入了“中断”这个概念。

中断是指计算机在执行程序的过程中,当出现异常情况或特殊请求时,计算机停止现行程序的运行,转向对这些异常情况或特殊请求的处理,处理结束后再返回现行程序的间断处,继续执行原程序。

中断是单片机实时地处理内部或外部事件的一种内部机制。

当某种内部或外部事件发生时,单片机的中断系统将迫使CPU暂停正在执行的程序,转而去进行中断事件的处理,中断处理完毕后,又返回被中断的程序处,继续执行下去。

在程序里面也是一样的。

举个例子可能会容易懂点,定时中断:比如你定时1ms,主程序在运行,每当1ms时间到后,就跑到定时中断子程序里面执行,执行完后再回到主程序(中断程序是1ms中断一次)。

那对于整个系统来说中断能实现什么好处呢?下面我们给以说明:1)提高了CPU的效率CPU是计算机的指挥中心,它与外围设备(如按键、显示器等)通讯的方法有查询和中断2种:查询的方法是无论外围IO是否需要服务,CPU每隔一段时间都要依次查询一遍,这种方法CPU需要花费一些时间在做查询服务工作。

Stm32中断优先级相关概念与使用笔记

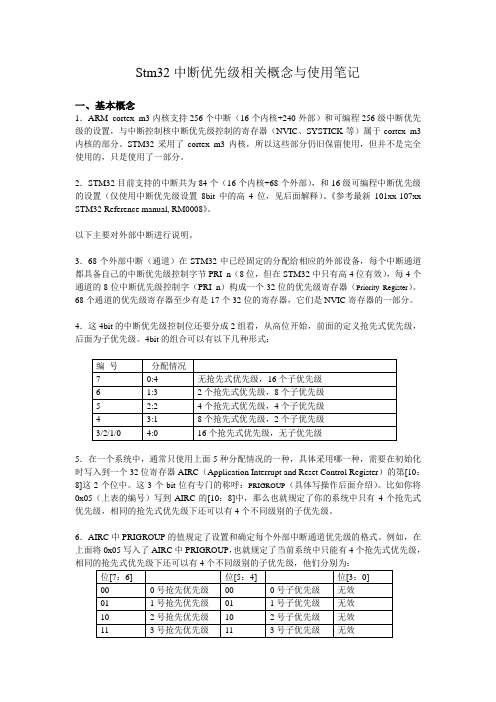

Stm32中断优先级相关概念与使用笔记一、基本概念1.ARM cortex_m3内核支持256个中断(16个内核+240外部)和可编程256级中断优先级的设置,与中断控制核中断优先级控制的寄存器(NVIC、SYSTICK等)属于cortex_m3内核的部分。

STM32采用了cortex_m3内核,所以这些部分仍旧保留使用,但并不是完全使用的,只是使用了一部分。

2.STM32目前支持的中断共为84个(16个内核+68个外部),和16级可编程中断优先级的设置(仅使用中断优先级设置8bit中的高4位,见后面解释)。

《参考最新101xx-107xx STM32 Reference manual, RM0008》。

以下主要对外部中断进行说明。

3.68个外部中断(通道)在STM32中已经固定的分配给相应的外部设备,每个中断通道都具备自己的中断优先级控制字节PRI_n(8位,但在STM32中只有高4位有效),每4个通道的8位中断优先级控制字(PRI_n)构成一个32位的优先级寄存器(Priority Register)。

68个通道的优先级寄存器至少有是17个32位的寄存器,它们是NVIC寄存器的一部分。

4.这4bit的中断优先级控制位还要分成2组看,从高位开始,前面的定义抢先式优先级,后面为子优先级。

4bit的组合可以有以下几种形式:5.在一个系统中,通常只使用上面5种分配情况的一种,具体采用哪一种,需要在初始化时写入到一个32位寄存器AIRC(Application Interrupt and Reset Control Register)的第[10:8]这2个位中。

这3个bit位有专门的称呼:PRIGROUP(具体写操作后面介绍)。

比如你将0x05(上表的编号)写到AIRC的[10:8]中,那么也就规定了你的系统中只有4个抢先式优先级,相同的抢先式优先级下还可以有4个不同级别的子优先级。

6.AIRC中PRIGROUP的值规定了设置和确定每个外部中断通道优先级的格式。

计算机原理实验-外部中断实验

计算机原理与应用实验实验名称:外部中断实验学院:信息与通信工程学院班级:2017211113姓名:***学号:**********同组成员姓名:李凝同组成员学号:**********一、实验目的1. 掌握NVIC 中断优先级配置。

2. 学会外部中断配置。

二、实验原理及内容(一)实验原理电路结构如图3.1 所示1. NVIC 中断优先级NVIC 是嵌套向量中断控制器,控制着整个芯片中断相关的功能,它跟内核紧密耦合,是内核里面的一个外设。

但是各个芯片厂商在设计芯片的时候会对Cortex-M4 内核里面的NVIC 进行裁剪,把不需要的部分去掉,所以说STM32 的NVIC 是Cortex-M4 的NVIC 的一个子集。

CM4 内核可以支持256个中断,包括16个内核中断和240个外部中断,256 级的可编程中断设置。

对于STM32F4 没有用到CM4 内核的所有东西,只是用到了一部分,对于STM32F40 和41 系列共有92个中断,其中有10个内核中断和82个可屏蔽中断,常用的为82个可屏蔽中断。

ISER[8]—中断使能寄存器组,用来使能中断,每一位控制一个中断,由于上面已经说明了控制82 个可屏蔽的中断,因此利用ISER[0~2]这三个32 位寄存器就够了。

一下的几个寄存器同理。

ICER[8]—中断除能寄存器组,用来消除中断。

ISPR[8]—中断挂起控制寄存器组,用来挂起中断。

ICPR[8]—中断解挂控制寄存器组,用来解除挂起。

IABR[8]—中断激活标志寄存器组,对应位如果为1 则表示中断正在被执行。

IP[240]—中断优先级控制寄存器组,它是用来设置中断优先级的。

我们只用到了IP[0]~IP[81],每个寄存器只用到了高4 位,这4 位又用来设置抢占优先级和响应优先级(有关抢占优先级和响应优先级后面会介绍到),而对于抢占优先级和响应优先级各占多少位则由AIRCR 寄存器控制,相关设置如表 3.1 所示。

学习小结--ARM7中断原理

2

3 向量地址寄存器 0-15(VICVectAddr0-15 - 0xFFFFF100-13C,读/写)

一般(以 Slot0 为例):VICVectAddr0 = (uint32)IRQ_TIME0 ;

4 向量地址寄存器(VICVectAddr - 0xFFFFF030,读/写) VICVectAddr = 0x00; // 通知 VIC 中断处理结束

二 ,VIC 寄存器 1,中断选择寄存器(VICIntSelect - 0xFFFFF00C,读/写)

该寄存器将 32 个中断请求分别分配为 FIQ 或 IRQ。

一般选 IRQ 时:VICIntSelect = 0x00;

1

2,向量控制寄存器 0-15(VICVectCnt l0-15 - 0xFFFFF200-23C,读/写)

PINSEL0 = 0x00000000; // 设置管脚连接 GPIO IO1DIR = LED1|LED2; // 设置 I/O 为输出 IO1SET = LED1|LED2; Time1Init(); // 初始化定时器及使能中断 Time0Init(); VICIntSelect = 0x00; // 所有中断通道设置为 IRQ 中断 VICDefVectAddr = (uint32)nIRQ_TIME; VICIntEnable = time0|time1; while(1); // 等待定时器中断或定时器匹配输出 return(0); }

}

} /**************************************************************************** * 名 称:Time0Init() * 功 能:初始化定时器,定时时间为 S,并使能中断。 * 入口参数:无 * 出口参数:无 ****************************************************************************/ void Time1Init(void) {

ARM异常中断以及对ARM异常返回地址的分析

返回地址:SUBS PC,R14,#8 返回地址分析: 当进入异常时,R14_abt = address of the aborted instruction + 8

所以要返回到有问题的指令处重新执行,所以返回的地址为 R14-8 IRQ 中断异常:

产生原因: 当处理器的外部中断请求引脚有效,且 CPSR 寄存器的 I 控制位被清除 时,处理器产生外部中断 IRQ 异常。

是因为当前指令即引起软件异常中断的指令执行后所引起的,说明当前指令已近执行,当从

中断返回时,执行的指令应该是当前指令的下一条指令,即待执行指令的地址应该是 0x3004, 而 R14 中存放的即为 0x3004,所以返回时使用将 R14 的值直接赋给 PC 即可。

指令预期中止异常: 发生原因:若在指令预取阶段遇到无效指令时,系统存储器将该预取的指令标记为无

效指令,当处理器试图去执行这一条被标记为预取无效的指令时,将产生指令预取中止异常, 注意若处理器没有执行无效指令时将不会产生异常中断(在流水线中存在一条分支指令,导 致该非法指令没有执行,将不会产生该异常)。

处理器动作: R14_abt = address of the aborted instruction + 4 SPSR_abt = CPSR ….. …..

2、各异常分析

举个小例子,下面是一段 ARM 汇编代码: (后面的返回地址分析中将会用到此图)

ARM七种异常类型详解(精华版)

ARM7支持六种操作模式:(1)用户模式(usr):正常的程序执行状态(2)FIQ模式(fiq):支持数据传送或通道处理(3)IRQ模式(irq):用于通用的中断处理(4)管理模式(svc):用于操作系统的保护模式(5)异常模式(abt):数据或者指令预取异常时进入(6)无定义模式(und):当无定义指令被执行时进入(7)软件控制,外部中断,异常处理都可以改变操作模式。

大部分的应用程序在用户模式下执行。

其他模式,比如管理模式,在中断、异常服务、或者访问被保护资源时进入。

ARM 的中央寄存器集是16 个用户寄存器R0 – R15。

这些寄存器均是32 位宽度,R0 – R12 没有其他特殊功能,寄存器R13 – R15在CPU中有特殊功能。

R13被用作栈指针(stack pointer,SP)。

R14被称为链接寄存器(link register, LR),当调用一个函数时返回地址被自动保存到链接寄存器,在函数返回时有效。

这使得快速进入和返回“叶”函数(不调用其他函数的函数)成为可能。

如果函数是分支的一部分(即该函数将调用另一个函数),链接寄存器必须入栈(R13)。

R15 是程序计数器(program counter, PC)。

有趣的是,许多指令也可以在R13 – R15中执行,就像它们是标准的用户寄存器。

ARM中断的问题ARM的七种异常类型---------1> 复位异常2> 数据访问中止异常3> 快速中断请求异常4> 一般中断请求5> 预取指令异常6> 软件中断异常7> 未定义异常-------------------------问题:1> 为什么除了进入复位异常模式外,在别的异常处理模式中都允许FIQ中断?2> 数据访问中止异常的优先级大于 FIQ异常,为什么在数据访问异常处理模式中,还允许 FIQ中断?这样不就成了:在高优先级异常处理中允许低优先级的中断发生?即使这样,因为FIQ中断的优先级 < 数据异常中断优先级,也不会进入 FIQ中断处理程序啊,这样不就更没有用处了??ARM体系的各种异常的分析(学习日记)- [ARM7TDMI]版权声明:转载时请以超链接形式标明文章原始出处和作者信息及本声明/logs/10669519.html1.复位异常(1)当内核的nRESET信号被拉低时,ARM处理器放弃正在执行的指令,当nRESET信号再次变高时,ARM处理器进行复位操作;(2)系统复位后,进入管理模式对系统进行初始化,复位后,只有PC(0x00000000)和CPSR (nzcvqIFt_SVC)的值是固定的,另外寄存器的值是随机的。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1、ARM中断有两种类型FIQ和IRQ

FIQ---快速中断

IRQ---一般中断

我们是可以将一个中断源设置为FIQ也可以设置成IRQ,一般我们都是使用IRQ,在嵌入式linux是不支持FIQ。中断源默认的也是IRQ。

2、IRQ总的开关

通过CPSR中的I位控制IRQ的开关。

一般我们只能将一个中断源设置成FIQ,这个中断源是最紧急需要处理的。

EXT_INT_0_MASK

EXT_INT_1_MASK

EXT_INT_2_MASK

EXT_INT_3_MASK

5、中断判断及清除寄存器

EXT_INT_0_PEND

EXT_INT_1_PEND

EXT_INT_2_PEND

EXT_INT_3_PEND

五、中断控制器的寄存器

1、中断状态寄存器

可以通过该寄存器知道中断是否发生。

VIC0VECTADDR16=(unsigned int )eint16_31_isr;

2、当EINT16有效,则开始响应EINT16,这时硬件会自动将VIC0VECTADDR16的内容copy到VIC0ADDRESS寄存器中。

3、在将VIC0ADDRESS的值给PC,这样就跳到eint16_31_isr()处理该中断。

}

七、分析中断的响应过程

八、总结

九、作业

1、KEY2~KEY5四个按键控制D1~D4的翻转,采用中断方式做。

{

if(EXT_INT_2_PEND & (1<<0))//EINT16

{

GPJ2DAT ^= (1<<0);//toggle

// clear pending bit

EXT_INT_2_PEND = 1<<0;

// clear VIC0ADDRESS

intc_clearvectaddr();

}

#if 0

2、中断类型选择寄存器

3、中断开关寄存器

4、中断向量地址寄存器

分析:

1、VIC0VECTADDR0~VIC0VECTADDR31是VIC0的32个中断源的向量地址寄存器,该寄存器中存放的是对应中断源ISR的入口地址。在中断初始化的时候,需要对该寄存器赋值。

例如:EINT16的中断处理程序void eint16_31_isr(void),则初始化过程如下:

if(EXT_INT_2_PEND & (1<<1))//EINT17

{

GPJ2DAT ^= (1<<1);//toggle

// clear pending bit

EXT_INT_2_PEND = 1<<1;

// clear VIC0ADDRESS

intc_clearvectaddr();

}

#endif

intc_setvectaddr(NUM_EINT16_31, isr_key);

//unmasked EINT16

EXT_INT_2_MASK &= ~(1<<0);

//enable EINT16_31

intc_enable(NUM_EINT16_31);

while (1);

}

2、中断处理程序

void isr_key(void)

// GPH2_0 --> EXT_INT[16]

GPH2CON |= 0xF;

//EXT_INT[16]: Falling edge triggered

EXT_INT_2_CON &= ~(7<0);

EXT_INT_2_CON |= (2<<0);

//initialize vector interrupt address with num of init and isr.

六、实验程序

EINT16(key2)控制D1等翻转1、主ຫໍສະໝຸດ 序int main(void)

{

//GPJ2CON[3:0] = 0001;GPJ2_0--->output

GPJ2CON &= ~(0xf<<0);

GPJ2CON |= (1<<0);

//interrupt controller init

int_init();

二、s5p210的中断源

1、有四个中断控制VIC0~VIC3

三、GEC210平台的原理图

四、外部中断的初始化设置

如果将一个GPIO设置成EINT,并且设置该EINT的触发方式。

1、设置GPIO为EINT功能

2、设置EINT的触发方式

我们可以将外部中断设置为下降沿触发。

3、EINT自带滤波器设置

4、EINT中断开关(屏蔽)寄存器