Allegro16.6约束规则设置详解

allegro差分线分组约束规则设置

allegro差分线分组约束规则设置(最新版)目录1.allegro 差分线分组约束规则的概念2.allegro 差分线分组约束规则的设置方法3.allegro 差分线分组约束规则的应用实例4.allegro 差分线分组约束规则的优缺点正文一、allegro 差分线分组约束规则的概念Allegro 是一种用于印刷电路板(PCB)设计的专业软件,它能够帮助设计人员快速高效地完成电路板的布局和设计。

在 Allegro 中,差分线分组约束规则是一种用于控制差分线(differential pair)布局的规则,能够有效地提高电路板的信号完整性。

二、allegro 差分线分组约束规则的设置方法在 Allegro 中,设置差分线分组约束规则的方法如下:1.打开 Allegro 软件,点击菜单栏的“工具”选项,选择“约束管理器”。

2.在弹出的“约束管理器”窗口中,选择“新建”选项,创建一个新的约束。

3.在“新建约束”对话框中,选择“差分线分组”选项,然后输入差分线的名称和描述。

4.在“差分线分组”对话框中,设置差分线的属性,包括线宽、间距、层数等。

5.确认设置后,点击“确定”按钮,完成差分线分组约束规则的设置。

三、allegro 差分线分组约束规则的应用实例在实际的电路板设计中,差分线分组约束规则可以应用于各种需要差分线布局的场景,例如高速信号传输、模拟信号处理等。

下面是一个应用实例:假设我们需要设计一个用于高速数据传输的电路板,其中涉及到一对差分线。

我们可以通过设置差分线分组约束规则,控制这对差分线的布局,以确保信号的完整性。

四、allegro 差分线分组约束规则的优缺点差分线分组约束规则在提高电路板信号完整性方面具有显著的优势,但也存在一些不足之处:优点:1.有效提高信号完整性,减少信号干扰和噪声。

2.便于设计和修改,提高设计效率。

缺点:1.需要对差分线进行专门的设置和管理,增加了设计复杂度。

2.对于复杂的电路板设计,差分线分组约束规则的设置可能会变得繁琐。

Allegro16.6约束管理器及使用示例

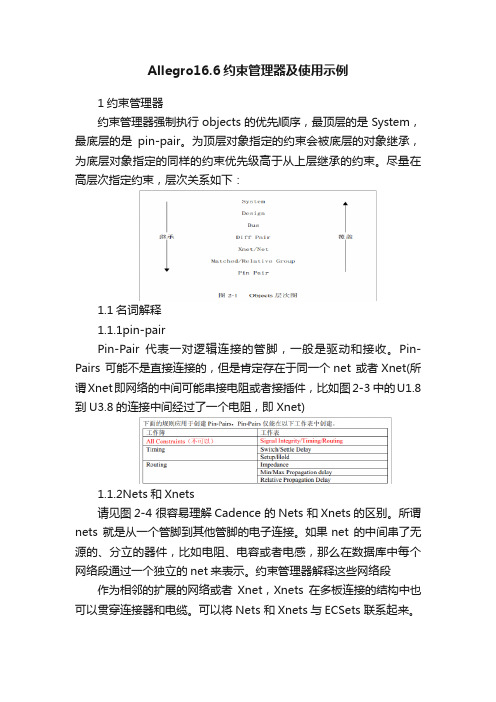

Allegro16.6约束管理器及使用示例1约束管理器约束管理器强制执行objects的优先顺序,最顶层的是System,最底层的是pin-pair。

为顶层对象指定的约束会被底层的对象继承,为底层对象指定的同样的约束优先级高于从上层继承的约束。

尽量在高层次指定约束,层次关系如下:1.1名词解释1.1.1pin-pairPin-Pair代表一对逻辑连接的管脚,一般是驱动和接收。

Pin-Pairs 可能不是直接连接的,但是肯定存在于同一个net 或者Xnet(所谓Xnet即网络的中间可能串接电阻或者接插件,比如图2-3 中的U1.8到U3.8的连接中间经过了一个电阻,即Xnet)1.1.2Nets和Xnets请见图2-4 很容易理解Cadence 的Nets 和Xnets的区别。

所谓nets 就是从一个管脚到其他管脚的电子连接。

如果net 的中间串了无源的、分立的器件,比如电阻、电容或者电感,那么在数据库中每个网络段通过一个独立的net来表示。

约束管理器解释这些网络段作为相邻的扩展的网络或者Xnet,Xnets在多板连接的结构中也可以贯穿连接器和电缆。

可以将Nets 和Xnets与ECSets 联系起来。

1.1.3Match GroupsMatch Group 是nets,Xnets或者pin-pairs 的集合,此集合一定要都匹配(delay 或者length)或者相对于组内的一个明确的目标。

如果delta 值没有定义,组内的所有成员都将是绝对匹配的,并允许有一定的偏差。

如果定义了delta 值,那么组内所有成员将相对匹配于明确的目标网络。

1.2在线检查设置首先在约束管理器中需要进行以下设置Analyze -> Analysis Modes这样在布线后,在相应的地方都会显示线长或约束相差值;如下图1.3示例通过一个实例来理解约束管理器U1看作是MCU,U2为DDR,ADDR0-3为地址线,需要作等长处理;CLK为时钟线,差分处理;U3,U4为连接同一个MCU的DDR;地址线是复用的,设置通过T型网络连接;需要作等长处理U5为DDR,DDR_DQ0-3为数据线,需要作等长处理1.3.1差分对约束即上图中的DDR_CLKP,DDR_CLKN设置Electrical ->Electrical Constraint Set -> Differential Pair 在Object的Name下方Project右键Create -> Electrical CSet;并输入参数差分对约束参数主要有以下几个:Min line spacing:内间距最小线距,若实际走线内间距小于这个值,DRC就会出错。

Allegro16.6约束规则设置详解_SCC

Allegro16.6约束规则设置详解前言:本文主要讲解Allegro16.6约束管理器的使用,从基本约束规则到高级约束规则的设置。

目录:一、基本约束规则设置1、线间距设置2、线宽设置3、设置过孔4、区域约束规则设置5、设置阻抗6、设置走线的长度范围7、设置等长7.1、不过电阻的NET等长7.2、过电阻的XNET等长7.3、T型等长8、设置通用属性9、差分规则设置9.1、创建差分对9.2、设置差分约束10、Pin Delay二、高级约束规则设置11、单个网络长度约束12、a+b类长度约束13、a+b-c类长度约束14、a+b-c在最大和最小传播延迟中的应用1、线间距设置(1)、设置默认间距规则点击CM图标,如下图所示,打开约束管理器。

单击Spacing,再点击All Layers,如下图所示。

右边有一个DEFAULT就是默认规则,我们可以修改其值。

按住Shift键,点击第一个和最后一个即可选中所示,然后输入一个值,这样就都修改了,如下图所示(2)、定义特殊的间距约束点选Default按鼠标右键,执行Create-Spacing CSet加入新规则。

取一个有意义点的名字,如下图所示,单击OK。

其值是从默认规则拷贝的,先修改其值。

按住Shift键选中所有,输入12,回车。

然后为所需要设置的网络分配规则单击左边的Net-All Layers,在右边工作簿中,为GND网络设置12MIL_SPACE规则,在Referenced Spacing CSet下选中12MIL_SPACE,如下图所示(3)、设置Class-Class规则若针对不同的信号群组有不同的间距规则,则需要设置Class-Class选到Net Class-Class后,在右边CLOCK(2)上右键选择Ctreat-Class-Class...,如下图所示选择2个不同的Net Classes,如下图所示,单击OK如下图所示。

在右边的Referenced Spacing CSet栏可以修改其值。

高速PCB设计软件allegro16.6版本约束管理界面讲解

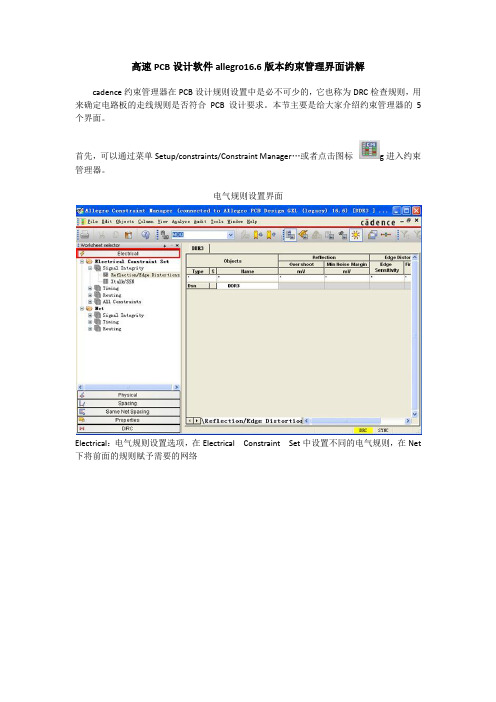

高速PCB设计软件allegro16.6版本约束管理界面讲解cadence约束管理器在PCB设计规则设置中是必不可少的,它也称为DRC检查规则,用来确定电路板的走线规则是否符合PCB设计要求。

本节主要是给大家介绍约束管理器的5个界面。

首先,可以通过菜单Setup/constraints/Constraint Manager…或者点击图标g进入约束管理器。

电气规则设置界面Electrical:电气规则设置选项,在Electrical Constraint Set中设置不同的电气规则,在Net 下将前面的规则赋予需要的网络物理规则设置界面Physical:物理规则设置选项,在Physical Constraint Set中设置不同的物理规则,在net 下将前面的规则赋予需要的网络;其中Region 是区域规则,主要针对BGA、引脚间距小、出线密度高的器件,需绘制一个区域框并赋予区域规则,区域内线宽和间距都可能小于区域外,物理规则下能够赋予物理规则。

间距规则设置界面Spacing:间距规则设置选项,在Spacing Constraint Set中设置不同的物理规则,在net 下将前面的规则赋予需要的网络,Net Class-Class是设置网络类之间的间距,补充网络间距之间的不足。

Region中可以赋予区域间距规则。

同名网络间距规则设置界面Same Net Spacing:同名网络间距设置选项,即一个网络本身之间的间距,主要是在需要绕线时运用。

属性设置界面DRC界面DRC:DRC错位查看选项,能够查看不同规则下错误的数量和位置,以及和错误相关的规则约束条件。

对高速PCB设计软件cadence16.6版本约束管理器界面进行介绍完毕后,下期继续为大家介绍与网络有关的约束与规则的讲解。

allegro差分线分组约束规则设置

allegro差分线分组约束规则设置【最新版】目录1.Allegro 软件概述2.差分线分组约束规则的概念3.差分线分组约束规则的设置方法4.差分线分组约束规则的应用实例5.总结正文一、Allegro 软件概述Allegro 是一款专业的 EDA(电子设计自动化)软件,广泛应用于 PCB (印刷电路板)设计领域。

通过 Allegro 软件,设计人员可以轻松实现电路原理图的绘制、PCB 布局布线以及各种设计规则的检查等功能。

在PCB 设计过程中,设计规则的合理设置是保证电路板性能和可靠性的关键。

二、差分线分组约束规则的概念差分线分组约束规则是 Allegro 软件中一种用于控制差分线(Differential Pair)布局布线的设计规则。

差分线是指在高速信号传输过程中,通过两条走线进行数据传输,以降低外部干扰和信号衰减的影响。

在实际应用中,为了保证差分线的传输性能,需要对差分线的布局布线进行分组约束。

三、差分线分组约束规则的设置方法在 Allegro 软件中,设置差分线分组约束规则的方法如下:1.打开 Allegro 软件,载入需要设置差分线分组约束规则的 PCB 设计文件。

2.在顶部菜单栏中,依次点击“规则”(Rules)→“约束规则”(Constraints)→“新建”(New),打开“新建约束规则”对话框。

3.在“新建约束规则”对话框中,设置差分线分组约束规则的名称、描述等信息,然后点击“添加”(Add)按钮。

4.在弹出的“添加约束规则”对话框中,设置差分线分组约束规则的具体参数,包括差分线分组名称、走线宽度、间距等,点击“确定”(OK)按钮。

5.在“新建约束规则”对话框中,点击“确定”(OK)按钮,完成差分线分组约束规则的设置。

四、差分线分组约束规则的应用实例在实际的 PCB 设计过程中,我们可以通过以下实例应用差分线分组约束规则:假设某高速信号传输系统,需要设计两条差分线,分别为 A 和 B。

allegro中的约束规则

Allegro中的约束规则1. 引言Allegro是一种强大的软件系统,用于在逻辑和数学约束下解决复杂的问题。

约束规则在Allegro中扮演着重要的角色,它们定义了问题的约束条件和限制,以确保问题的解满足特定的要求。

在本文中,我们将深入探讨Allegro中的约束规则,包括其定义、类型、应用和最佳实践。

2. 约束规则的定义约束规则是一种形式化的表达方式,用于描述问题的约束条件和限制。

它们通常由逻辑和数学公式组成,用于限制问题的解空间。

在Allegro中,约束规则是由谓词逻辑和约束语言组成的,它们定义了问题的约束条件和限制。

3. 约束规则的类型在Allegro中,约束规则可以分为以下几种类型:3.1 等式约束等式约束是最常见的约束规则类型之一。

它定义了两个表达式之间的相等关系。

例如,“x = y”表示变量x和y具有相同的值。

在Allegro中,等式约束通常用于限制变量之间的关系。

3.2 不等式约束不等式约束定义了两个表达式之间的不等关系。

例如,“x < y”表示变量x的值小于变量y的值。

在Allegro中,不等式约束用于限制变量的取值范围。

3.3 逻辑约束逻辑约束定义了变量之间的逻辑关系,如AND、OR和NOT等。

例如,“x > 0 AND y < 10”表示变量x大于0且变量y小于10。

在Allegro中,逻辑约束用于限制变量之间的关系。

3.4 全局约束全局约束是一种特殊类型的约束规则,它可以同时限制多个变量的取值。

例如,“AllDifferent(x, y, z)”表示变量x、y和z的取值不能相同。

在Allegro中,全局约束用于限制多个变量之间的关系。

4. 约束规则的应用约束规则在Allegro中具有广泛的应用。

以下是一些常见的应用场景:4.1 排课问题在学校或大学中,排课是一个复杂的问题。

通过使用约束规则,可以限制每个教室在每个时间段只能安排一门课程,并确保每个学生在每个时间段只能上一门课程。

ALLEGRO16.6软件操作技巧

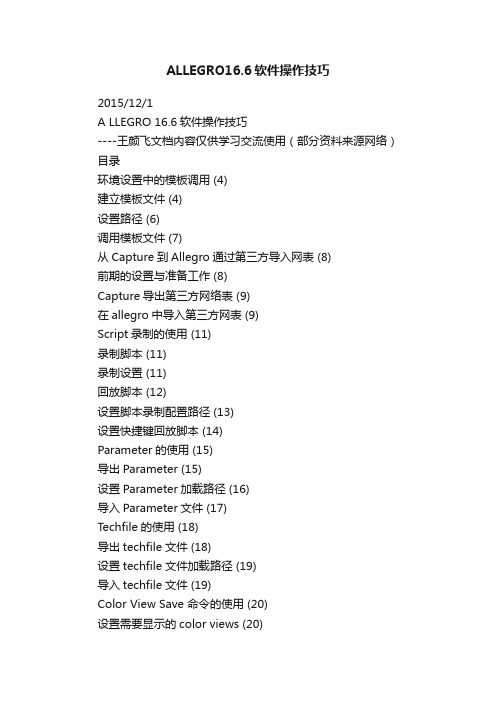

ALLEGRO16.6软件操作技巧2015/12/1A LLEGRO 16.6软件操作技巧----王颜飞文档内容仅供学习交流使用(部分资料来源网络)目录环境设置中的模板调用 (4)建立模板文件 (4)设置路径 (6)调用模板文件 (7)从Capture到Allegro通过第三方导入网表 (8)前期的设置与准备工作 (8)Capture导出第三方网络表 (9)在allegro中导入第三方网表 (9)Script录制的使用 (11)录制脚本 (11)录制设置 (11)回放脚本 (12)设置脚本录制配置路径 (13)设置快捷键回放脚本 (14)Parameter的使用 (15)导出Parameter (15)设置Parameter加载路径 (16)导入Parameter文件 (17)Techfile的使用 (18)导出techfile文件 (18)设置techfile文件加载路径 (19)导入techfile文件 (19)Color View Save 命令的使用 (20)设置需要显示的color views (20)保存color views (20)设置环境参数中color views配置路径 (21)如何使用color views (21)布局之Swap 命令(器件交换) (22)激活菜单命令 (22)交换对象 (22)右键菜单交换器件 (22)Swap Pin用法 (23)在原理图中设置Pin Group属性 (23) Allegro环境中交换引脚 (23)Swap Pin回注 (25)布局之模板复用 (27)布局布线其中一个模块; (27)创建复用模块 (27)调用模块 (29)模块复用完成 (31)Module Reuse用法 (32)原理图工程文件创建Module Reuse模块 (32) Allegro中创建Module Reuse模块 (33)设置软件的路径配置信息 (34)原理图工程中调用Module Reuse模块 (35) PCB 工程中调用Module Reuse模块 (36) Sub-Drawing用法 (38)导出Sub-Drawing (38)设置配置路径 (40)导入Sub-Drawing (40)如何在allegro中增加元件 (42)设置软件配置信息,允许logic编辑 (42)添加元件 (42)放置元件 (45)添加网络 (46)布局布线操作 (46)极坐标布局(来源阿杜) (48)环境设置中的模板调用实际应用中,为了节省设置环境的时间,我们就会根据需要建立的文件类型和实际情况制作模板。

Allegro16.6约束规则设置详解2

7.2、过电阻的XNET 等长这里关键是设置XNET。

假设有一排过电阻的线需要等长。

首先创建电阻模型。

单击Signal Model 图标,如下图所示点击电阻,如下图所示,单击RN0603 10所有这种模型的电阻都高亮了,如下图所示单击Create Model。

按钮。

默认,单击OK默认单击OK。

如下图所示。

再单击OK 结束命令。

假设我们要将DR_MD49 到DR_MD53网络等长。

打开约束管理器,选择相对延迟,这里可以看到我们刚才设置的XNET。

我们在DR_MD49 网络上右键创建PIN PAIR选择2 个端点,如上图所示,单击OK。

同理,其他需要设置等长的网络,也创建PIN PAIR。

然后按住Ctrl 键选择这些PIN PAIR,右键创建MATCH GROUP 如下图所示设定约束值,及目标网络,方法同不过电阻网络等长设置。

7.3、T 型等长T 型等长设置,比如两个D DR 之间的等长就属于T 型等长,设置方法如下(以text_drr 举例)。

首先添加T 型连接点。

点击Logic-Net Schedule,单击你要设置网络的一个pin。

如下图。

在中间右键Insert T,加入T 型连接点,如下图所示然后去点击第二个pin,再回到T 型连接点,然后去点击第三个pin,右键done 即可。

创建的T 型连接点如下图所示这只是创建了一个网络的T 型连接点,如果需要创建多个,可点击进入约束管理器设置。

在N et-Routing——Wiring 下面,刚才设置的网络拓扑便会显示成UserDefined。

如下图所示选中那个网络,右键创建Creat-Electrical CSet,如下图然后将你需要设置T 型结构的网络选择刚才设置的ECSet 作为参考,Verify Schedule 选择yes 即打开验证,如下图所示。

然后打开检查模式,在约束管理器Analyze-Analysis Modes弹出的对话框中,将Stub length/Net 的检查模式选择为on 如下如所示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Allegro16.6约束规则设置详解前言:本文主要讲解Allegro16.6约束管理器的使用,从基本约束规则到高级约束规则的设置。

目录:一、基本约束规则设置1、线间距设置2、线宽设置3、设置过孔4、区域约束规则设置5、设置阻抗6、设置走线的长度范围7、设置等长7.1、不过电阻的NET等长7.2、过电阻的XNET等长7.3、T型等长8、设置通用属性9、差分规则设置9.1、创建差分对9.2、设置差分约束10、Pin Delay二、高级约束规则设置11、单个网络长度约束12、a+b类长度约束13、a+b-c类长度约束14、a+b-c在最大和最小传播延迟中的应用1、线间距设置(1)、设置默认间距规则点击CM图标,如下图所示,打开约束管理器。

单击Spacing,再点击All Layers,如下图所示。

右边有一个DEFAULT就是默认规则,我们可以修改其值。

按住Shift键,点击第一个和最后一个即可选中所示,然后输入一个值,这样就都修改了,如下图所示(2)、定义特殊的间距约束点选Default按鼠标右键,执行Create-Spacing CSet加入新规则。

取一个有意义点的名字,如下图所示,单击OK。

其值是从默认规则拷贝的,先修改其值。

按住Shift键选中所有,输入12,回车。

然后为所需要设置的网络分配规则单击左边的Net-All Layers,在右边工作簿中,为GND网络设置12MIL_SPACE规则,在Referenced Spacing CSet下选中12MIL_SPACE,如下图所示(3)、设置Class-Class规则若针对不同的信号群组有不同的间距规则,则需要设置Class-Class选到Net Class-Class后,在右边CLOCK(2)上右键选择Ctreat-Class-Class...,如下图所示选择2个不同的Net Classes,如下图所示,单击OK如下图所示。

在右边的Referenced Spacing CSet栏可以修改其值。

执行Analyze-Analysis Modes...,如下图所示可以看到Spacing Mode的检查模式2、线宽设置(1)、设置默认约束点选Physical Constraint Set即可出现Default的Physical相关设定值,如Line Width、Neck width..等(2)、设置特殊物理规则点选Default按鼠标右键,执行Create Physical CSet加入新规则修改其值,如下图所示然后在分配网络,左边点击Net-All Layers,右边为所需设置的网络分配规则,如下图所示3、设置过孔物理规则设置里面有一栏是Vias,点击即可设置,如下图所示点击默认规则的Vias,如下图所示Remove可以移除过孔。

在左边的过孔列表中双击即可添加过孔。

同理,可设置其他物理规则的过孔,如下图所示。

4、区域约束规则设置在物理规则下,左边点击Region,在右边cds_2右键并选择Create-Region...,如下图所示输入其约束值。

然后执行Shape> Polygon/Rectangular/Circular设定范围,一般BGA比较常用。

类选择为Constraint Region,子类为All。

Assign to Region分配的区域设置为刚才创建的RGN1.5、设置阻抗(1)、通过Edit Property方式设置语法说明:IMPEDANCE_RULE=A:B:C:DA:起点PINB:终点PINC:阻抗的数值大小D:阻抗的误差大小例如:(1).IMPEDANCE_RULE=ALL:ALL:50ohm:10ohm设定走线的阻抗是50ohm,误差值是正负10ohm (2).IMPEDANCE_RULE=U1.1:R1.1:50ohm:20%设定走线在U1.1到R1.1之间的阻抗是50ohm,误差是正负20%执行Edit/Properties,点击一个网络,假设点击D0网络在过滤器里面输入im*,点击Apply输入数值all:all:60:5,单击Apply,如下图所示单击OK,结束命令。

然后打开检查模式,在Setup-Constraints-Modes... 如下图所示在弹出的窗口中,将电气模式下的阻抗检查打开,如下图所示违反规则,就会出现一个DRC,如下图所示(2)、在约束管理器中设置在约束管理器中,点选Impedance,如下图所示在cds_2上,右键Create-Electrical CSet,如下图所示输入名称60ohm单击OK,回到工作簿,设置其值,如下图所示然后为所需要设置的网络分配规则,如下图所示然后再打开检查模式,如下图所示6、设置走线的长度范围语法说明:PROPAGATION_DELAY=A:B:C:DA:起点PINB:终点PIN如果是整条NET只有2个PIN时,在A处写入L,在B处写入SC:最小线长D:最大线长例如:PROPAGATION_DELAY=U1.4:U2.8:1000mil:1500mil设定U1.4到U2.8的走线长度为1000MIL到1500MIL之间PROPAGATION_DELAY=L:S:1000mil:1500mil设定整条NET的走线长度为1000MIL到1500MIL之间(1)、通过Edit Property设置执行Edit /Porperties命令,单击一个网络,选择PROGATION_DELAY并输入其数值,如下图所示。

然后再开启检查模式,Setup-Constraints-Modes...(2)、在约束管理器中设置在Electrical Constraint Set 点选Min/Max Propagation Delays在cds_2上右键选择Create-Electrical CSet设定其值为网络分配约束,如下图所示再打开检查模式,Analyze-Analysis Modes...将电气规则下的,Propagation delay检查模式打开。

走线模式时,即可辅助线束走线状态。

(3)、在原理图中设置进入Capture中的Property Edit,选Cadence-Allegro及Flat Net执行Edit/Invoke UI对PROPAGATION_DELAY设定其值输出Netlist到Allegro。

进入Allegro后即可看到Properties再开启检查模式。

走线模式时,即可辅助显示走线状态7、设置等长语法说明:RELATIVE_PROPAGATION_DELAY=A:B:C:D:E:FA:组名。

不用和BUS_NAME 名相同,在设定MATCH_GROUP 时注意这一点。

B:是GLOBAL,在B位写入G 即可C:起点PIND:终点PIN如果NET只有2个PIN时,C处写L,D处写S。

E:写入要比参照线(Target)长或短的数值F:长度的误差(也可以用百分比表示)7.1、不过电阻的NET等长打开约束管理器,选择一组NET,右键创建MATCH_GROUP,如下图所示。

然后设定其值然后设置一个网络为目标网络,在网络Delta :Tolerance 栏处右键选择Set as target,如下图所示再打开检查模式。

如下图所示7.2、过电阻的XNET等长这里关键是设置XNET。

假设有一排过电阻的线需要等长。

首先创建电阻模型。

单击Signal Model图标,如下图所示点击电阻,如下图所示,单击RN0603 10所有这种模型的电阻都高亮了,如下图所示单击Create Model。

按钮。

默认,单击OK默认单击OK。

如下图所示。

再单击OK结束命令。

假设我们要将DR_MD49到DR_MD53网络等长。

打开约束管理器,选择相对延迟,这里可以看到我们刚才设置的XNET。

我们在DR_MD49网络上右键创建PIN PAIR选择2个端点,如上图所示,单击OK。

同理,其他需要设置等长的网络,也创建PIN PAIR。

然后按住Ctrl键选择这些PIN PAIR,右键创建MATCH GROUP 如下图所示设定约束值,及目标网络,方法同不过电阻网络等长设置。

7.3、T型等长这里为节约时间,直接引用现成的文档,基于15.7版本。

16.6设置方法类似。

T型等长设置,比如两个DDR之间的等长就属于T型等长,设置方法如下(以text_drr举例)。

首先添加T型连接点。

点击Logic-Net Schedule,单击你要设置网络的一个pin。

如下图。

在中间右键Insert T,加入T型连接点,如下图所示然后去点击第二个pin,再回到T型连接点,然后去点击第三个pin,右键done即可。

创建的T型连接点如下图所示这只是创建了一个网络的T型连接点,如果需要创建多个,可点击进入约束管理器设置。

在Net-Routing——Wiring下面,刚才设置的网络拓扑便会显示成UserDefined。

如下图所示选中那个网络,右键创建Creat-Electrical CSet,如下图然后将你需要设置T型结构的网络选择刚才设置的ECSet作为参考,Verify Schedule选择yes即打开验证,如下图所示。

然后打开检查模式,在约束管理器Analyze-Analysis Modes弹出的对话框中,将Stub length/Net的检查模式选择为on 如下如所示。

然后选中你设置的网络右键Analyze,看看是否通过,为绿色pass即可,如下图所示。

再回到pcb,打开飞线,看看是否都有了T型连接点,如下图所示。

然后在回到约束管理器,将刚才设置的T型结构的网络选中,右键Creat-Bus,如下图所示。

选中所创建的Bus,右键SigXplorer,如下图所示这里可以看到刚才设置的拓扑结构,单击Set菜单下Constraints子菜单,如下图所示,选择Rel Prop Delay面板创建两个约束,注意这里设置的是从T1到U2和T1到U3,即U2和U3之间T型等长,约束名称是一样的,范围Scope 选择Local,如下图所示设置好之后,单击Update Cm图标更新回约束管理器,如下图所示。

再回到约束管理器下Net-Routing-Relative Propagation Delay 就可以看到刚才设置的约束BUS2_M1了,如下图所示。

然后再打开检查模式,在Analyze下Analysis Modes,如下图所示,将Relative propagation检查模式设置为on,如下图8、设置通用属性若以NET常用的property为例#MIN_LINE_WIDTH 最小线宽#BUS_NAME BUS名称#NO_RAT 隐藏鼠线#FIXED 将器件固定(1)、通过Edit /Porperties命令设置执行Edit /Porperties,点击你要设置属性的网络(右键Temp Group可以选择多个网络),在弹出的属性编辑对话框中选择相应的Porperties并设定Value 即可(2)、在约束管理器中设置执行Edit /Net Porperties命令,进入约束管理器的General Properties选项,选择栏位并设定其值即可,如下图所示(3)、BUS_NAME等属性也可以通过原理图设置好,然后在Allegro中导入网表的方式来设置。