计算机组成原理实验1-5(2017-2018-1)

计算机组成原理实验

计算机组成原理实验一、实验目的本实验旨在通过实际操作,加深对计算机组成原理的理解,掌握计算机硬件的基本原理和工作方式。

二、实验设备和材料1. 计算机主机:型号为XXX,配置了XXX处理器、XXX内存、XXX硬盘等。

2. 显示器:型号为XXX,分辨率为XXX。

3. 键盘和鼠标:标准配置。

4. 实验板:包括CPU、内存、存储器、输入输出接口等模块。

5. 逻辑分析仪:用于分析和调试电路信号。

6. 示波器:用于观测电路信号的波形。

三、实验内容1. 实验一:CPU的工作原理a. 将实验板上的CPU模块插入计算机主机的CPU插槽中。

b. 连接逻辑分析仪和示波器,用于观测和分析CPU的工作信号和波形。

c. 打开计算机主机,启动操作系统。

d. 运行一段简单的程序,观察CPU的工作状态和指令执行过程。

e. 通过逻辑分析仪和示波器的数据分析,了解CPU的时钟信号、数据总线、地址总线等工作原理。

2. 实验二:内存的存储和读写a. 将实验板上的内存模块插入计算机主机的内存插槽中。

b. 打开计算机主机,启动操作系统。

c. 编写一个简单的程序,将数据存储到内存中。

d. 通过逻辑分析仪和示波器的数据分析,观察内存的写入和读取过程,了解内存的存储原理和读写速度。

3. 实验三:存储器的工作原理a. 将实验板上的存储器模块插入计算机主机的存储器插槽中。

b. 打开计算机主机,启动操作系统。

c. 编写一个简单的程序,读取存储器中的数据。

d. 通过逻辑分析仪和示波器的数据分析,观察存储器的读取过程,了解存储器的工作原理和数据传输速度。

4. 实验四:输入输出接口的工作原理a. 将实验板上的输入输出接口模块插入计算机主机的扩展插槽中。

b. 打开计算机主机,启动操作系统。

c. 编写一个简单的程序,通过输入输出接口实现数据的输入和输出。

d. 通过逻辑分析仪和示波器的数据分析,观察输入输出接口的工作过程,了解数据的传输和控制原理。

四、实验结果分析1. 实验一:通过观察CPU的工作状态和指令执行过程,可以验证CPU的时钟信号、数据总线、地址总线等工作原理是否正确。

计算机组成原理实验(接线、实验步骤)

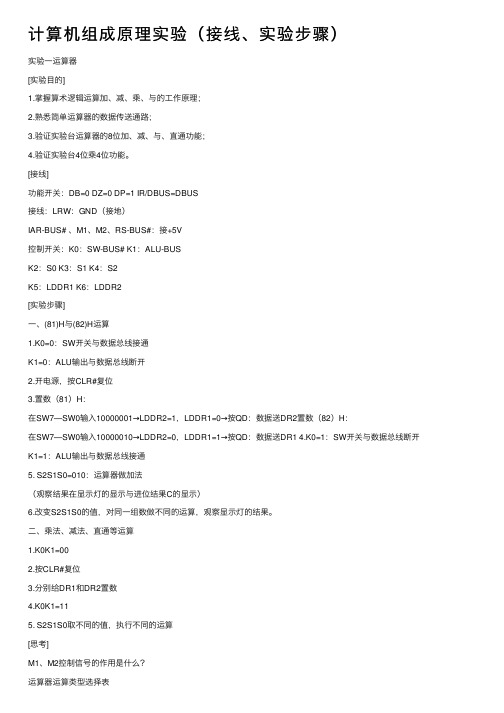

计算机组成原理实验(接线、实验步骤)实验⼀运算器[实验⽬的]1.掌握算术逻辑运算加、减、乘、与的⼯作原理;2.熟悉简单运算器的数据传送通路;3.验证实验台运算器的8位加、减、与、直通功能;4.验证实验台4位乘4位功能。

[接线]功能开关:DB=0 DZ=0 DP=1 IR/DBUS=DBUS接线:LRW:GND(接地)IAR-BUS# 、M1、M2、RS-BUS#:接+5V控制开关:K0:SW-BUS# K1:ALU-BUSK2:S0 K3:S1 K4:S2K5:LDDR1 K6:LDDR2[实验步骤]⼀、(81)H与(82)H运算1.K0=0:SW开关与数据总线接通K1=0:ALU输出与数据总线断开2.开电源,按CLR#复位3.置数(81)H:在SW7—SW0输⼊10000001→LDDR2=1,LDDR1=0→按QD:数据送DR2置数(82)H:在SW7—SW0输⼊10000010→LDDR2=0,LDDR1=1→按QD:数据送DR1 4.K0=1:SW开关与数据总线断开K1=1:ALU输出与数据总线接通5. S2S1S0=010:运算器做加法(观察结果在显⽰灯的显⽰与进位结果C的显⽰)6.改变S2S1S0的值,对同⼀组数做不同的运算,观察显⽰灯的结果。

⼆、乘法、减法、直通等运算1.K0K1=002.按CLR#复位3.分别给DR1和DR2置数4.K0K1=115. S2S1S0取不同的值,执⾏不同的运算[思考]M1、M2控制信号的作⽤是什么?运算器运算类型选择表选择操作S2 S1 S00 0 0 A&B0 0 1 A&A(直通)0 1 0 A+B0 1 1 A-B1 0 0 A(低位)ΧB(低位)完成以下表格ALU-BUS SW-BUS# 存储器内容S2S1S0 DBUS C输⼊时:计算时:DR1:01100011DR2:10110100(与)DR1:10110100DR2:01100011(直通)DR1:01100011DR2:01100011(加)DR1:01001100DR2:10110011(减)DR1:11111111DR2:11111111(乘)实验⼆双端⼝存储器[实验⽬的]1.了解双端⼝存储器的读写;2.了解双端⼝存储器的读写并⾏读写及产⽣冲突的情况。

计算机组成原理实验报告

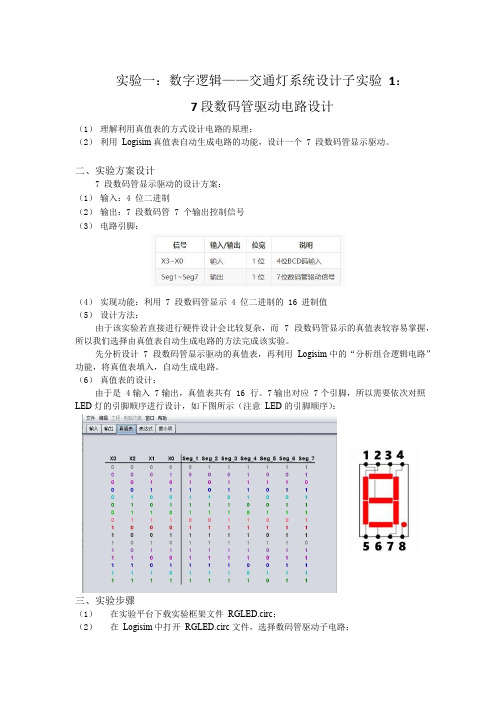

实验一:数字逻辑——交通灯系统设计子实验1:7 段数码管驱动电路设计(1)理解利用真值表的方式设计电路的原理;(2)利用Logisim 真值表自动生成电路的功能,设计一个 7 段数码管显示驱动。

二、实验方案设计7 段数码管显示驱动的设计方案:(1)输入:4 位二进制(2)输出:7 段数码管 7 个输出控制信号(3)电路引脚:(4)实现功能:利用 7 段数码管显示 4 位二进制的 16 进制值(5)设计方法:由于该实验若直接进行硬件设计会比较复杂,而7 段数码管显示的真值表较容易掌握,所以我们选择由真值表自动生成电路的方法完成该实验。

先分析设计 7 段数码管显示驱动的真值表,再利用Logisim 中的“分析组合逻辑电路”功能,将真值表填入,自动生成电路。

(6)真值表的设计:由于是 4输入 7输出,真值表共有 16 行。

7输出对应 7个引脚,所以需要依次对照LED 灯的引脚顺序进行设计,如下图所示(注意LED 的引脚顺序):三、实验步骤(1)在实验平台下载实验框架文件RGLED.circ;(2)在Logisim 中打开RGLED.circ 文件,选择数码管驱动子电路;(3)点击“工程”中的“分析组合逻辑电路”功能,先构建4输入和7输出,再在“真值表”中,将已设计好的真值表的所有数值仔细对照着填入表格中,确认无误后点击“生成电路”,自动生成的电路如下图所示:(4)将子电路封装为如下形式:(5)进行电路测试:·自动测试在数码管驱动测试子电路中进行测试;·平台评测自动测试结果满足实验要求后,再利用记事本打开RGLED.circ 文件,将所有文字信息复制粘贴到Educoder 平台代码区域,点击评测按钮进行测试。

四、实验结果测试与分析(1)自动测试的部分结果如下:(2)平台测试结果如下:综上,本实验测试结果为通过,无故障显示。

本实验的关键点在于:在设计时需要格外注重LED 灯的引脚顺序,保证0-9 数字显示的正确性,设计出正确的真值表。

计算机组成原理实验1_脱机运算器

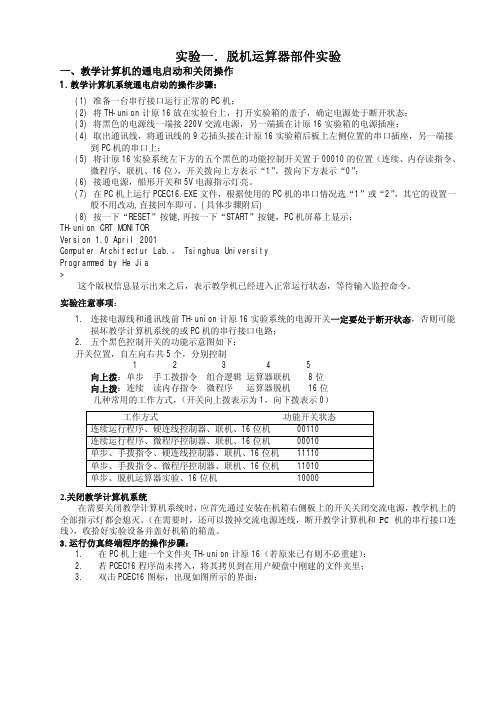

实验一.脱机运算器部件实验一、教学计算机的通电启动和关闭操作1.教学计算机系统通电启动的操作步骤:(1) 准备一台串行接口运行正常的PC机;(2) 将TH-union计原16放在实验台上,打开实验箱的盖子,确定电源处于断开状态;(3) 将黑色的电源线一端接220V交流电源,另一端插在计原16实验箱的电源插座;(4) 取出通讯线,将通讯线的9芯插头接在计原16实验箱后板上左侧位置的串口插座,另一端接到PC机的串口上;(5) 将计原16实验系统左下方的五个黑色的功能控制开关置于00010的位置(连续、内存读指令、微程序、联机、16位),开关拨向上方表示“1”,拨向下方表示“0”;(6) 接通电源,船形开关和5V电源指示灯亮。

(7) 在PC机上运行PCEC16.EXE文件,根据使用的PC机的串口情况选“1”或“2”,其它的设置一般不用改动,直接回车即可。

(具体步骤附后)(8) 按一下“RESET”按键,再按一下“START”按键,PC机屏幕上显示:TH-union CRT MONITORVersion 1.0 April 2001Computer Architectur Lab., Tsinghua UniversityProgrammed by He Jia>这个版权信息显示出来之后,表示教学机已经进入正常运行状态,等待输入监控命令。

实验注意事项:1.连接电源线和通讯线前TH-union计原16实验系统的电源开关一定要处于断开状态,否则可能损坏教学计算机系统的或PC机的串行接口电路;2.五个黑色控制开关的功能示意图如下:开关位置,自左向右共5个,分别控制1 2 3 4 5向上拨:单步手工拨指令组合逻辑运算器联机 8位向上拨:连续读内存指令微程序运算器脱机 16位几种常用的工作方式,(开关向上拨表示为1,向下拨表示0)工作方式功能开关状态连续运行程序、硬连线控制器、联机、16位机 00110连续运行程序、微程序控制器、联机、16位机 00010单步、手拨指令、硬连线控制器、联机、16位机 11110单步、手拨指令、微程序控制器、联机、16位机 11010单步、脱机运算器实验、16位机 100002.关闭教学计算机系统在需要关闭教学计算机系统时,应首先通过安装在机箱右侧板上的开关关闭交流电源,教学机上的全部指示灯都会熄灭。

计算机组成原理实验课 实验报告

3设置TH-union+实验机工作方式:将6个拨动开关置于正确位置,实现“分立电路CPU的16位联机工作、使用微程序控制其并从内存读指令”的状态。

4在pc机上启动PECE16.EXE

5练习TH-union+实验机各条指令的使用,掌握其功能。

6编写汇编程序段,实现任务要求的功能。

三、实验结果

三、实验过程

这是一个完成整数排序功能的程序,要求首先输入5个参加排序的整数数值,接下来完成对这5个整数的排序操作,并输出最终的排序结果。

<1>在命令行提示符:下输入下面程序:

10 for i=1 to 5

20 input a(i)

30 next i

40 for i=1 to 4

50 for j=i+1 to 5

2.7实验机存储器使用和扩展实验

一、实验目的

1.理解计算机主存储器芯片的读写和控制方法,学习ROM存储器和RAM存储器的使用

2.熟悉计算机主存储器的组成方法,掌握存储器扩展技术.地址分配

二、实验环境介绍

1.扩展芯片连接

TH-union+教学实验计算机机箱上,供实验中进行存储器扩展空间的只有2个芯片插槽,可插入2片8K*8位的58C65芯片,进行EEPROM存储空间的扩展。

2.58C65芯片应用

58C65芯片是电可擦除可编程的ROM器件,它既可以通过专用的编程软件和设备向芯片写入相应内容,也可以通过写内存的指令,向芯片的指定单元写入数据。

三、实验步骤

用EEPROM芯片58C65扩展主存实验

(1)将扩展的AT58C65芯片插入标有“EXTROMH”和“EXTROML”的自锁紧插座,要注意芯片插入的方向。

计算机组成原理实验

IN ADD OUT JMP – 通过串口连接实验系统和PC机 – 运行CMPP联机软件,装载程序文件 – 调用“复杂模型机”通路图,注意观察单步 微指令和单步机器指令的运行过程

实验一 系统认识实验

实验报告要点:

– 数字计算机结构原理图

– 本系统的四条指令

IN ADD OUT JMP – 实验思考题 – 实验小结

– 74LS245三态门,控制输入输出操作 ALU-B置低电平:输出运算结果 SW-B置低电平:输入数据进入总线 – 74LS273实现两个操作数的数据锁存 LDDR1/LDDR2置高电平 脉冲触发-T4 – 总线灯(LED)显示总线上的数据

245芯片 181芯片 273芯片 181芯片 273芯片 总线灯

实验三 控制器实验

微命令(微信号)

– 直接作用于控制电路的控制命令

微操作

– CPU在执行指令中,由微命令控制实现的最

基本操作

送指令地址、取指、读指令、译码、送操作数地 址、取操作数、运算、写回结果等 微操作是指令执行部件接受微命令后进行的操作

微周期

– 读取一条微指令并完成相应微操作所用时间,

C字段

9 0 0 0 0 1 1 1 8 0 0 1 1 0 0 1 7 0 1 0 1 0 1 0 P(1) P(2) P(3) P(4) AR LDPC 选择

实验三 控制器实验

A字段

15 0 0 0 0 1 1 1 14 0 0 1 1 0 0 1 13 0 1 0 1 0 1 0 LDRi LDDR1 LDDR2 LDIR LOAD LDAR 选择

实验二 运算器实验

集成逻辑芯片74LS181 – 4位ALU单元 逻辑功能表

计算机组成原理 实验报告

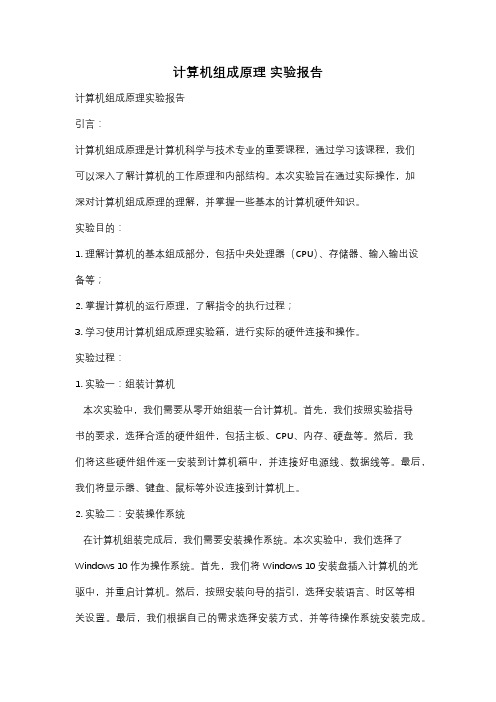

计算机组成原理实验报告计算机组成原理实验报告引言:计算机组成原理是计算机科学与技术专业的重要课程,通过学习该课程,我们可以深入了解计算机的工作原理和内部结构。

本次实验旨在通过实际操作,加深对计算机组成原理的理解,并掌握一些基本的计算机硬件知识。

实验目的:1. 理解计算机的基本组成部分,包括中央处理器(CPU)、存储器、输入输出设备等;2. 掌握计算机的运行原理,了解指令的执行过程;3. 学习使用计算机组成原理实验箱,进行实际的硬件连接和操作。

实验过程:1. 实验一:组装计算机本次实验中,我们需要从零开始组装一台计算机。

首先,我们按照实验指导书的要求,选择合适的硬件组件,包括主板、CPU、内存、硬盘等。

然后,我们将这些硬件组件逐一安装到计算机箱中,并连接好电源线、数据线等。

最后,我们将显示器、键盘、鼠标等外设连接到计算机上。

2. 实验二:安装操作系统在计算机组装完成后,我们需要安装操作系统。

本次实验中,我们选择了Windows 10作为操作系统。

首先,我们将Windows 10安装盘插入计算机的光驱中,并重启计算机。

然后,按照安装向导的指引,选择安装语言、时区等相关设置。

最后,我们根据自己的需求选择安装方式,并等待操作系统安装完成。

3. 实验三:编写并执行简单的汇编程序在计算机组装和操作系统安装完成后,我们需要进行一些简单的编程实验。

本次实验中,我们选择了汇编语言作为编程工具。

首先,我们编写了一个简单的汇编程序,实现两个数相加的功能。

然后,我们使用汇编器将程序翻译成机器码,并将其加载到计算机的内存中。

最后,我们通过调试器来执行这个程序,并观察程序的执行结果。

实验结果与分析:通过本次实验,我们成功地组装了一台计算机,并安装了操作系统。

在编写并执行汇编程序的实验中,我们也成功地实现了两个数相加的功能。

通过观察程序的执行结果,我们发现计算机能够按照指令的顺序逐条执行,并得到正确的结果。

这进一步加深了我们对计算机的工作原理的理解。

计算机组成原理实验

计算机组成原理实验计算机组成原理实验报告1. 引言计算机组成原理实验是计算机类专业学生进行的重要实践课程之一。

通过实验,学生可以深入了解计算机系统的各个组成部分以及它们的功能和工作原理。

2. 实验目的本次实验的主要目的是探究计算机中的主要组成部分,包括中央处理器(CPU)、内存、输入输出设备以及硬盘等,并了解它们的相互连接与调度方式。

3. 实验装置和材料本实验使用了一台计算机,配备有Intel Core i7处理器、8GB 内存和500GB硬盘。

实验中还使用了键盘、鼠标和显示器等输入输出设备。

4. 实验过程及结果4.1 CPU实验在这个实验中,我们通过编写汇编语言程序来实现简单的数值运算。

实验结果显示,CPU能够根据程序逐条执行指令,并正确计算出结果。

4.2 内存实验通过编写C语言程序,我们对内存进行读写操作。

实验结果显示,内存可以正确存储和读取数据,并且能够保持数据的一致性。

4.3 输入输出设备实验在这个实验中,我们测试了键盘和鼠标的输入功能以及显示器的输出功能。

实验结果显示,输入设备能够正确识别用户的输入,而输出设备能够正确显示结果。

4.4 硬盘实验通过读写文件的操作,我们测试了硬盘的存储和检索功能。

实验结果显示,硬盘能够正确存储和读取文件,并且能够在短时间内进行大量的数据传输。

5. 结论通过本次实验,我们深入了解了计算机系统的各个组成部分以及它们的功能和工作原理。

实验结果表明,计算机的各个组件能够正常工作,并且能够协同工作以完成复杂的任务。

6. 参考文献[1] 《计算机组成原理实验指导书》[2] Smith, J.E., & Jones, P. 《Computer Organization and Design: The Hardware/Software Interface》. Morgan Kaufmann, 2014.。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验电路结构图

NO.0

实验电路结构图

HEX

PIO2PIO3PIO4PIO5PIO7PIO6D1

D2

D3

D4

D5

D6

D7

D8

D16

D15

D14

D13

D12

D11

数码1

数码2

数码3

数码4

数码5

数码6

数码7

数码8

S P E A K E R

扬声器

译码器译码器译码器译码器译码器译码器译码器译码器

FPGA/CPLD PIO15-PIO12

PIO11-PIO8PIO7--PIO2HEX 键1

键2

键3键4键5键6键7键8PIO47-PIO44

PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16目标芯片

附图2 实验电路结构图NO.0

附图3 实验电路结构图NO.1

ʵÑéµç·½á¹¹Í¼

NO.3

ÒëÂëÆ÷

ÒëÂëÆ÷ÒëÂëÆ÷ÒëÂëÆ÷ÒëÂëÆ÷ÒëÂëÆ÷ÒëÂëÆ÷ÒëÂëÆ÷D9

D16D15D14D13D12D11D10

D8D7D6D5D4D3D2D1PIO8

PIO9

PIO10

PIO11

PIO12

PIO13

PIO14

PIO15

S P E A K E R

ÑïÉùÆ÷

1

2345678Ä¿±êоƬFPGA/CPLD PIO0

PIO1PIO2PIO3PIO4PIO5PIO6PIO7¼ü1

¼ü2¼ü3¼ü4¼ü5¼ü6¼ü7¼ü8PIO15-PIO8PIO47-PIO44

PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16

附图4 实验电路结构图NO.2 附图5 实验电路结构图NO.3

D16D15D14D13D12D11D9D8PIO47

D7PIO46

D6PIO45

D5PIO44

D4PIO43

D3PIO42

D2PIO41

PIO40

D1NO.7

实验电路结构图

S P E A K E R

扬声器

FPGA/CPLD 目标芯片1

2

3

4

5

6

7

8

PIO0

PIO2PIO3PIO4PIO5PIO6PIO7单脉冲

单脉冲单脉冲键1

键2

键3

键4

键5

键6

键7

键8

PIO47-PIO40PIO39-PIO36

PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16

译码器译码器译码器译码器译码器

译码器

附图6 实验电路结构图NO.4 附图9 实验电路结构图NO.7

拨码开关

滤波1A /D 使能比较器5t h 使能R O M 使能

ON

8

7

6

5

4

3

2

1转换结束D S 8使能

拨码1:ROM/RAM 使能,即它们的CS1接地拨码8:DAC0832输出滤波使能

拨码7:ADC0809使能,默认关闭,见左图拨码6:ADC0809转换结束使能,见左图拨码5:应用LM311使能,见下图

拨码4:8数码管显示开关,默认打开拨码2:默认关闭 向上拨,由厂家通知升级VS (PIO65)

HS (PIO64)B (PIO63)

G (PIO61)R (PIO60)

105487

6

3

21 视频接口

VGA J6R78 200

R77 200R76 200

14

13

PIO77

PIO76PS/2下接口

PS/2上接口

VCC

GND

PIO45

PIO46513

J7

4VCC

GND

513

4PIN31->A15 )

PIN29->WE ,

29C040(PIN31->WE,PIN1->A18,

P29->A14)

27010(PIN30->VCC,PIN3->A15,PIN29->A14)27020(PIN30->A17,PIN3->A15,PIN3->A15,PIN29->A14)27040(PIN31->A18,PIN30->A17,

PIN30->A17,PIN3->A15,PIN29->A14)

注意,PIO62 同时是键11的信号线

PIO62RAM/ROM 使能

A I N 1VCC

10K VR1

拨码7拨码6

A I N 0P I O 8

(23)(24)1216272610C L O C K 750K H Z A 021+5V r e f (-)r e f (+)I N -1I N -06

9

22

25

7

17

1415818192021E U 1A D C 0809P I O 16

P I O 17P I O 18P I O 19P I O 20P I O 21P I O 22P I O 23P I O 32

P I O 33P I O 35P I O 34

m s b 2-12-22-32-42-52-62-7l s b 2-8E O C A D D -A A D D -B A D D -C A L E E N A B L E S T A R T

(拨码1:“ROM 使能 ON”即将CS1接地)

628128(PIN30->VCC,PIN3->A14,(拨码8:“滤波1 ON”即连接滤波电容)

滤波1

103

连接PIO37与COMP )

(拨码5:“比较器ON”即7.2K PIO31

PIO29PIO30PIO28PIO27PIO26PIO25PIO2413

1415164D7

D6D5D4D35D26D1D07PIO37

+5

51pFC27

COMP

LM311VCC

10K -12

+1248

23TL082/1

AIN0

AOUT

5.1K

R72765

TL082/2

8

4

1

+12

-12

COMM

EU2DAC0832

1181710

32WR1

FB

9

3

211IOUT1IOUT2

12/CS WR2XFER A GND D GND

VREF

8

VCC 20VCC

D1PIO8

D2D3D4D5D6D7D8PIO9

PIO10

PIO11

PIO12

PIO15

PIO14

PIO13

实验电路结构图

NO.5

S P E A K E R

扬声器

FPGA/CPLD 目标芯片1

2345678D16D15D14D13D12D11D10D9

PIO47-PIO44

PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16译码器译码器译码器译码器译码器译码器译码器

译码器PIO15-PIO8PIO0

PIO1PIO2PIO3PIO4PIO5PIO6PIO7键1

键2键3键4键5键6键7键8GND

VCC

PIO49RAM/ROM

A18/A19A18/A15/WE PIO26PIO25PIO24PIO32PIO33PIO34PIO35PIO36PIO37PIO38PIO39PIO14PIO47PIO10PIO48PIO9PIO46PIO45PIO11PIO12PIO13PIO15PIO31PIO30PIO29PIO28PIO27

32

313029282726252423222120191817

16

151413121110987654321VCC GND

2708027040270202701027512272562764628128622566264VCC

A17/VCC WR/A14

A13A8A9A11OE A10CS1D7D6D5

D4D3GND

D2D1D0A0A1A2A3A4A5A6A7A12A14(A15)A16

附图7 实验电路结构图NO.5

附图8 实验电路结构图NO.6

附图10 实验电路结构图NO.8 附图11 实验电路结构图NO.9。