实验1 1位全加器设计

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验1 一位全加器设计

【实验目的】

1.掌握数字电路的两种设计方法

2.掌握在Cadence中绘制原理图的方法

3.掌握芯片外围特性与实现硬件电路

4.掌握Verilog HDL设计电路的方法。

【实验内容】

1.设计1位全加器

2.绘制1位全加器原理图

3.在面包板上实现1位全加器设计

4.用Verilog HDL行为描述法设计实现1位全加器并仿真

【实验器件】

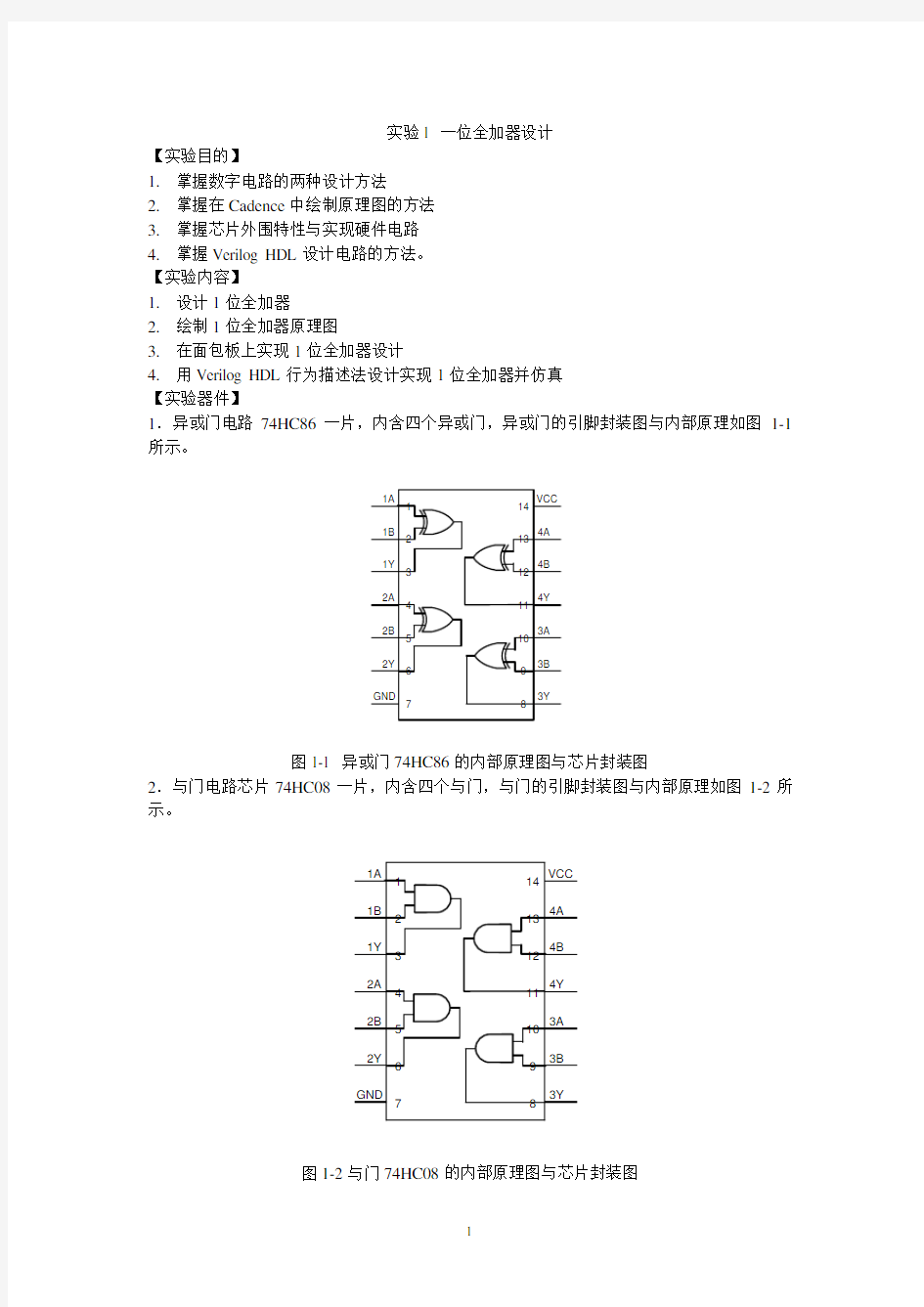

1.异或门电路74HC86一片,内含四个异或门,异或门的引脚封装图与内部原理如图1-1所示。

图1-1 异或门74HC86的内部原理图与芯片封装图

2.与门电路芯片74HC08一片,内含四个与门,与门的引脚封装图与内部原理如图1-2所示。

图1-2与门74HC08的内部原理图与芯片封装图

3.或门电路芯片74HC32一片,内含四个或门,或门的引脚封装图与内部原理如图1-3所示。

图1-3或门74HC32的内部原理图与芯片封装图

4.3个1k的电阻和两个发光二极管,一个8路开关,5v电源,面包板一块,导线若干条。【实验步骤】

1.设计1位全加器

1)设1位全加器的输入为被加数为A,加数B,低位进位Cin;输出为本位和Sum,对高位的进位为Cout。

2)根据1位加法器的运算{Cout,Sum}=A+B+Cin列真值表如表吗-1所示。

表1-1 1位加法器真值表

3)根据真值表列出逻辑表达式

Cin

B

A

Cin

B

A

Cin

B

A

Cin

B

A

B

A

Cin

AB

B

A

ABCin

Cin

B

A

Cin

B

A

Cin

B

A

Sum

⊕

⊕

=

⊕

+

⊕

=

+

+

+

=

+

+

+

=

)

(

)

(

)

(

)

(

AB

Cin

B

A

ABCin

Cin

AB

Cin

B

A

BCin

A

Cout+

⊕

=

+

+

+

=)

(

4)手动绘制该原理图,为电路加上开关控制数据输入,用发光二极管显示输出,电路图如图1-4所示。

图1-4 1位全加器原理图

2.在实验板上连接实现该电路并分析电路元件构成

3.在protel软件中绘制原理图

1)绘制元件符号

2)绘制原理图

4. .在protel软件中绘制pcb

1)封装绘制

2)pcb绘制