数字电子基础组合逻辑电路

《数字电子技术基础》第五版:第四章 组合逻辑电路

74HC42

二-十进制译码器74LS42的真值表

序号 输入

输出

A3 A2 A2 A0 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 Y8 Y9

0 0 000 0 111111111

1 0 001 1 011111111

2 0 010 1 101111111

3 0 011 1 110111111

4 0 100 1 111011111

A6 A4 A2

A0

A15 A13 A11 A9

A7 A5 A3

A1

I7 I6 I5 I4 I3 I2 I1 I00

S

74LS 148(1)

YS

YEE Y2 Y1

Y0

XX

I7 I6 I5 I4 I3 I2 I1 I0

S

74LS 148(2)

YS

YE Y2 Y1

Y0

X

&

G3

&

G2

&

G3

Z3

Z2

Z1

&

G3

0时1部分电路工作在d0a1a0d7d6d5d4d3d2d1d074ls153d22d20d12d10d23d21s2d13d11s1y2y1a1a0在d4a0a1a2集成电路数据选择器集成电路数据选择器74ls15174ls151路数据输入端个地址输入端输入端2个互补输出端74ls151的逻辑图a2a1a02274ls15174ls151的功能表的功能表a2a1a0a将函数变换成最小项表达式b将使能端s接低电平c地址a2a1a0作为函数的输入变量d数据输入d作为控制信号?实现逻辑函数的一般步骤cpcp000001010011100101110111八选一数据选择器三位二进制计数器33数据选择器数据选择器74ls15174ls151的应用的应用加法器是cpu中算术运算部件的基本单元

数字电子技术基础组合逻辑电路(半加器`全加器及逻辑运算)

一、实验目的

1. 掌握组合逻辑电路的功能测试。

2. 验证半加器和全加器的逻辑功能。

3. 学会二进制数的运算规律。

二、实验原理及其实验元件

实验原理:参照指导书对应内容结合自己理解写

实验箱、芯片(74LS00、74LS10、74LS54、74LS86)、导线。

三、实验内容及其步骤

数字电子技术基础

组合逻辑电路(半加器、全加器及逻辑运算)

[班级] [姓名] [学号]

[日期]

2.测试用异或门(74LS86)和与非门组成的半加器的逻辑功能。

用一片(74LS86)和(74LS00)组成半加器。

3.测试用异或门、与或门和非门组成的全加

器的逻辑功能。

S

CO

设计性实验

设计一个“三个一至电路”。

电路有三个输入端,一个输出端。

当三个输入端变量A、B、C状态一致时,输出F为“1”;当三个变量状态不一致时,输出F为“0”。

(要求:用与非门组成电路。

)

步骤:

1)列真值表:

2)写出逻辑表达式:

()()

ABC

C

B

A

F⋅

=

3)画逻辑电路图:

A

B

C

F

4)验证:

所得实验结论与理论值相等,说明实验成功。

5)按下图连接实验电路。

A

B。

数字电子技术基础 第4章

在将两个多位二进制数相加时,除了最低位以外,每一 位都应该考虑来自低位的进位,即将两个对应位的加数 和来自低位的进位3个数相加。这种运算称为全加,所用 的电路称为全加器。

图4.3.26

全加器的卡诺图

图4.3.27 双全加器74LS183 (a)1/2逻辑图 (b)图形符号

二、多位加法器

1、串行进位加法器(速度慢)

数字电子技术基础 第四章 组合逻辑电路

Pan Hongbing VLSI Design Institute of Nanjing University

4.1 概述

数字电路分两类:一类为组合逻辑电路,另一类 为时序逻辑电路。 一、组合逻辑电路的特点

任何时刻的输出仅仅取决于该时刻的输入,与电路原 来的状态无关。 电路中不能包含存储单元。

例4.2.1 P162

图4.2.1

例3.2.1的电路

4.2.2 组合逻辑电路的设计方法

最简单逻辑电路:器件数最少,器件种类最少, 器件之间的连线最少。 步骤:

1、进行逻辑抽象 2、写出逻辑函数式 3、选定器件的类型 4、将逻辑函数化简或变换成适当的形式 5、根据化简或变换后的逻辑函数式,画出逻辑电路 的连接图 6、工艺设计

通常仅在大规模集成电 路内部采用这种结构。 图4.3.7 用二极管与门阵列组成的3线-8线译码器

最小项译码器。

图4.3.8

用与非门组成的3线-8线译码器74LS138

例4.3.2 P177

图4.3.10

用两片74LS138接成的4线-16线译码器

二、二-十进制译码器

拒绝伪码功能。

图4.3.11

4.2.2 组合逻辑电路的设计方法

数字电子技术基础实验二 组合逻辑电路设计

数字电子技术基础实验报告题目:实验二组合电路设计小组成员:小组成员:1.掌握全加器和全减器的逻辑功能;2.熟悉集成加法器的使用方法;3.了解算术运算电路的结构;4.通过实验的方法学习数据选择器的结构特点、逻辑功能和基本应用。

二、实验设备1.数字电路实验箱;2.Quartus II 软件。

三、实验要求要求1:参照参考内容,调用MAXPLUSⅡ库中的组合逻辑器件74153双四数据选择器和7400与非门电路,用原理图输入方法实现一一位全加器。

(1)用 Quartus II波形仿真验证;(2)下载到 DE0 开发板验证。

要求2:参照参考内容,调用MAXPLUSⅡ库中的组合逻辑器件74138三线八线译码器和门电路,用原理图输入方法实现一位全减器。

(1)用 Quartus II 波形仿真验证;(2)下载到 DE0 开发板验证。

要求3:参照参考内容,调用MAXPLUSⅡ库中的组合逻辑器件74138三线八线译码器和门电路,用原理图输入方法实现一个两位二进制数值比较器。

(MULTISM仿真和FPGA仿真)。

1、74138三线八线译码器原理2、74153双四数据选择器原理3、全加器原理全加器能进行加数、被加数和低位来的进位信号相加,并根据求和的结果给出该位的进位信号。

图一图一是全加器的符号,如果用i A,i B表示A,B两个数的第i位,1i C 表示为相邻低位来的进位数,i S表示为本位和数(称为全加和),i C表示为向相邻高位的进位数,则根据全加器运算规则可列出全加器的真值表如表一所示。

表一可以很容易地求出S 、C 的化简函数表达式。

i i i-1i i i-1i i ()i i S A B C C A B C A B =⊕⊕=⊕+用一位全加器可以构成多位加法电路。

由于每一位相加的结果必须等到低一位的进位产生后才能产生(这种结构称为串行进位加法器),因而运算速度很慢。

为了提高运算速度,制成了超前进位加法器。

这种电路各进位信号的产生只需经历以及与非门和一级或非门的延迟时间,比串行进位的全加器大大缩短了时间。

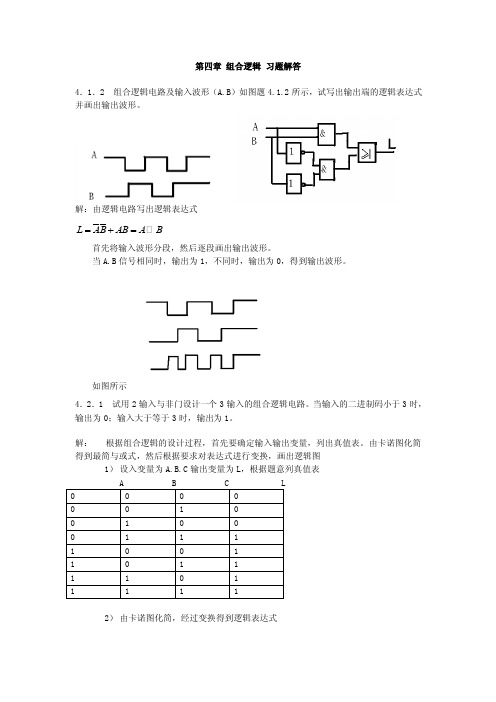

数字电子基础部分答案(康华光)第04章_组合逻辑习题解答

第四章组合逻辑习题解答4.1.2 组合逻辑电路及输入波形(A.B)如图题4.1.2所示,试写出输出端的逻辑表达式并画出输出波形。

解:由逻辑电路写出逻辑表达式=+=L AB AB A B首先将输入波形分段,然后逐段画出输出波形。

当A.B信号相同时,输出为1,不同时,输出为0,得到输出波形。

如图所示4.2.1 试用2输入与非门设计一个3输入的组合逻辑电路。

当输入的二进制码小于3时,输出为0;输入大于等于3时,输出为1。

解:根据组合逻辑的设计过程,首先要确定输入输出变量,列出真值表。

由卡诺图化简得到最简与或式,然后根据要求对表达式进行变换,画出逻辑图1)设入变量为A.B.C输出变量为L,根据题意列真值表2)由卡诺图化简,经过变换得到逻辑表达式L A BC A BC=+=*3)用2输入与非门实现上述逻辑表达式4.2.7 某足球评委会由一位教练和三位球迷组成,对裁判员的判罚进行表决。

当满足以下条件时表示同意;有三人或三人以上同意,或者有两人同意,但其中一人是叫教练。

试用2输入与非门设计该表决电路。

解: 1)设一位教练和三位球迷分别用A和B.C.D表示,并且这些输入变量为1时表示同意,为0时表示不同意,输出L表示表决结果。

L为1时表示同意判罚,为0时表示不同意。

由此列出真值表输入输出A B C D L2)由真值表画卡诺图由卡诺图化简得L=AB+AC+AD+BCD由于规定只能用2输入与非门,将上式变换为两变量的与非——与非运算式 *******L AB AC AD BCD AB AC AD B CD ==3)根据L 的逻辑表达式画出由2输入与非门组成的逻辑电路4.3.3 判断图所示电路在什么条件下产生竞争冒险,怎样修改电路能消除竞争冒险?解: 根据电路图写出逻辑表达式并化简得*L A B BC =+当A=0,C=1时,L B B =+ 有可能产生竞争冒险,为消除可能产生的竞争冒险,增加乘积项使AC ,使 *L A B BC A C =++ ,修改后的电路如图4.4.4 试用74HC147设计键盘编码电路,十个按键分别对应十进制数0~9,编码器的输出为8421BCD码。

《数字电子技术基础》复习指导(第四章)

《数字电⼦技术基础》复习指导(第四章)第四章组合逻辑电路⼀、本章知识点(⼀)概念1.组合电路:电路在任⼀时刻输出仅取决于该时刻的输⼊,⽽与电路原来的状态⽆关。

电路结构特点:只有门电路,不含存储(记忆)单元。

2.编码器的逻辑功能:把输⼊的每⼀个⾼、低电平信号编成⼀个对应的⼆进制代码。

优先编码器:⼏个输⼊信号同时出现时,只对其中优先权最⾼的⼀个进⾏编码。

3.译码器的逻辑功能:输⼊⼆进制代码,输出⾼、低电平信号。

显⽰译码器:半导体数码管(LED数码管)、液晶显⽰器(LCD)4.数据选择器:从⼀组输⼊数据中选出某⼀个输出的电路,也称为多路开关。

5.加法器半加器:不考虑来⾃低位的进位的两个1位⼆进制数相加的电路。

全加器:带低位进位的两个 1 位⼆进制数相加的电路。

超前进位加法器与串⾏进位加法器相⽐虽然电路⽐较复杂,但其速度快。

6.数值⽐较器:⽐较两个数字⼤⼩的各种逻辑电路。

7.组合逻辑电路中的竞争⼀冒险现象竞争:门电路两个输⼊信号同时向相反跳变(⼀个从1变0,另⼀个从0变1)的现象。

竞争-冒险:由于竞争⽽在电路输出端可能产⽣尖峰脉冲的现象。

消除竞争⼀冒险现象的⽅法:接⼊滤波电容、引⼊选通脉冲、修改逻辑设计(⼆)组合逻辑电路的分析⽅法分析步骤:1.由图写出逻辑函数式,并作适当化简;注意:写逻辑函数式时从输⼊到输出逐级写出。

2.由函数式列出真值表;3.根据真值表说明电路功能。

(三)组合逻辑电路的设计⽅法设计步骤:1.逻辑抽象:设计要求----⽂字描述的具有⼀定因果关系的事件。

逻辑要求---真值表(1) 设定变量--根据因果关系确定输⼊、输出变量;(2)状态赋值:定义逻辑状态的含意输⼊、输出变量的两种不同状态分别⽤0、1代表。

(3)列出真值表2.由真值表写出逻辑函数式真值表→函数式,有时可省略。

3.选定器件的类型可选⽤⼩规模门电路,中规模常⽤组合逻辑器件或可编程逻辑器件。

4.函数化简或变换式(1)⽤门电路进⾏设计:从真值表----卡诺图/公式法化简。

电子技术 数字电路 第3章 组合逻辑电路

是F,多数赞成时是“1”, 否则是“0”。

0111 1000 1011

2. 根据题意列出真值表。

1101 1111

(3-13)

真值表

ABCF 0000 0010 0100 0111 1000 1011 1101 1111

3. 画出卡诺图,并用卡 诺图化简:

BC A 00

00

BC 01 11 10

010

3.4.1 编码器

所谓编码就是赋予选定的一系列二进制代码以 固定的含义。

一、二进制编码器

二进制编码器的作用:将一系列信号状态编制成 二进制代码。

n个二进制代码(n位二进制数)有2n种 不同的组合,可以表示2n个信号。

(3-17)

例:用与非门组成三位二进制编码器。 ---八线-三线编码器 设八个输入端为I1I8,八种状态,

全加器SN74LS183的管脚图

14 Ucc 2an 2bn2cn-1 2cn

2sn

SN74LS183

1 1an 1bn 1cn-11cn 1sn GND

(3-39)

例:用一片SN74LS183构成两位串行进位全加器。

D2

C

D1

串行进位

sn

cn

全加器

an bn cn-1

sn

cn

全加器

an bn cn-1

1 0 1 1 1 AB

AC

F AB BC CA

(3-14)

4. 根据逻辑表达式画出逻辑图。 (1) 若用与或门实现

F AB BC CA

A

&

B

C

&

1 F

&

(3-15)

(2) 若用与非门实现

数字电路基础-组合逻辑电路和时序逻辑电路考试试卷

数字电路基础-组合逻辑电路和时序逻辑电路考试试卷(答案见尾页)一、选择题1. 数字电路中的基本逻辑门有哪些?A. 或门B. 与门C. 非门D. 异或门E. 同或门2. 下列哪种逻辑电路可以实现时序控制?A. 组合逻辑电路B. 时序逻辑电路C. 计数器D. 编码器3. 在组合逻辑电路中,输出与输入的关系是怎样的?A. 输出总是与输入保持相同的逻辑状态B. 输出仅在输入发生变化时改变C. 输出与输入没有直接关系D. 输出在输入未知时保持不变4. 时序逻辑电路中的时钟信号有何作用?A. 提供时间信息B. 控制电路的工作顺序C. 改变电路的工作频率D. 用于解码5. 下列哪种器件是时序逻辑电路中常见的时序元件?A. 计数器B. 编码器C. 解码器D. 触发器6. 组合逻辑电路和时序逻辑电路的主要区别是什么?A. 组合逻辑电路的输出与输入存在一对一的逻辑关系;时序逻辑电路的输出与输入之间存在时间上的依赖关系。

B. 组合逻辑电路只能处理数字信号;时序逻辑电路可以处理模拟信号。

C. 组合逻辑电路中没有存储单元;时序逻辑电路中存在存储单元(如触发器)。

D. 组合逻辑电路的响应速度较快;时序逻辑电路的响应速度较慢。

7. 在组合逻辑电路中,如果输入信号A和B都为,则输出F将是:A. 0B. 1C. 取决于其他输入信号D. 无法确定8. 在时序逻辑电路中,触发器的时钟信号来自哪里?A. 外部时钟源B. 内部时钟源C. 控制器D. 数据输入端9. 时序逻辑电路的设计通常涉及哪些步骤?A. 确定逻辑功能需求B. 选择合适的触发器C. 设计状态转移方程D. 将设计转换为实际电路E. 对电路进行仿真和验证二、问答题1. 什么是组合逻辑电路?请列举几种常见的组合逻辑电路,并简述其工作原理。

2. 时序逻辑电路与组合逻辑电路有何不同?请举例说明。

3. 组合逻辑电路中的基本逻辑门有哪些?它们各自的功能是什么?4. 什么是触发器?它在时序逻辑电路中的作用是什么?5. 组合逻辑电路设计的基本步骤是什么?请简要说明。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

本章内容□ 组合逻辑电路的分析与设计□常用中规模集成电路南京大学金陵学院一肇莹组合逻辑电路•输入逻辑变量输出逻辑变量■ Output = Function (Input)Y?二DC • DBA 二DC + DBAK = DCB • DCB • DC A = DCB + DCB + DC AY° 二DC・DB 二DC + DB设计一个3位奇偶校验电路,当输入变量中有奇数个“1”时,输出为“1”,否则,输岀为“0” •用与非门来实现。

F = ABC + ABC + ABC + ABCF = ABC + ABC + ABC + ABC =ABC • ABC • ABC • ABCABFC&正常工作状态OO・RAGRAGZ0 0 0 10 0 1 00 1 0 00 1 1 1 Z = RAG + RAG + RAG + RAG + RAG1 0 0 0 1 0 1 1 1 1 0 11111态• o ・| !••• RAG RAG•oo oeo RAG RAG故障状• •o| I RAG RAGZ = RAG + RA + RG + AGRAz GgjZ = RAG^RA^RG^AGRAGf =3V, v/L=ov -AoAA2Vcc丁 Ay7YeYs丫4了3丫2Y1yA B cE EW-Q03-to-8 译码器— 匕=G • (J + J)・ A • B ・ U Z)—^2——.■*3_2 ---- ---------------- -----------------------Yy =G X ・(G2A +G2B )・A ・B ・CD —/---表示低电平有效74x138Pin-8 isGND Pin-16 is V ccY0Y1Y2Y3Y4Y5Y6Y7匕=d ・(。

2占 +°2B)・N E XA BO4线6线译码器D 2 D.Zo Zi Z 2 Z3 乙 Z 5 Z5 Z7 Z& Z9 Z10Zu Z12Z13 Z]4=>用译码器来实现逻辑函数。

当译码器在工作状态下= G^B=°,Y oY} = N・E・UY7= A・B・CF(X#,Z)= m(0,3,5,6)F(X,Y,Z)= b»E 匕74x138------D—9——ABC& D ----------yo_yly2y3一人y5y6y7y8ys 74LS42D. P(a)BS201A7 10 98 5 4 2 3D. Pl公共阴极(b)1,6d74x48BI/ RBORBIA2 Y eA1 AO丫&灯测试端 LT : if LT = 0, then Y a 〜笛=1.灭零输入端 RBI, if RBI = 0 & 4/^4观=0000, then 匕〜兀=0. 灭灯输入/灭零输出BI/RBO : if BI =0, then Y a 〜/ = 0・1 0 0 0 0 0 1 0adRBO = A3A2A i A Q• LT • RBIA 3 V CCA]AoLTBl/RBO RBIY bYeY d Y eY f GND 丫呂lkQX7cc3 2 10• A A A AREQ1 ——REQ2 ——REQ3 •REQN RequestEncoderRequestor J snumber优先权编码器74x14874x1484 3 . 2 1E IOI7 O I6 C I5 C1-^-C1-^Q 7 I4 I3I211IA2A1A0GSEOInput OutputEI I0 11 I2 I3 I4 I5 I6 I7 A2 A1 AO GS EO1 X X X X X X X X 1 1 1 1 10 X X X X X X X 0 0 0 0 0 10 X X X X X X 0 1 0 0 1 0 10 X X X X X 0 1 1 0 1 0 0 10 X X X X 0 1 1 1 0 1 1 0 10 X X X 0 1 1 1 1 1 0 0 0 10 X X 0 1 1 1 1 1 1 0 1 0 10 X 0 1 1 1 1 1 1 1 1 0 0 10 0 1 1 1 1 1 1 1 1 1 1 0 10 1 1 1 1 1 1 1 1 1 1 1 1 0D EI-—E nable□ GS…表示编码器工作,并且有编码信号输入(Got Someting) □ EO…表示编码器工作,但是没有编码信号输入。

74x14816线・4线编码器LRequest 15Request 14Request 13Request 12Request 11Request 10Request 9Request 8c El4Cl713I6 I5 I4 I3 I2 11 IOA2A1AOGSEOA3A2A1Request 7Request 6Request 5Request 4Request 3Request 2Request 1Request 0I71-2-C1-2-011I6I5I4 I3 I211IOA2A1AOGSEOAOLD?3(AA)^13(AA))X 74x15374x151in—921 15 14 13 12 ENABCDOD1D2D3D4D5D6D7Y = ^ABC)D0+^ABC)D} +A(ABC)D7^NO 扩展位数Y0ENA BC= 用数据选择器来实现逻辑函数L = A J BC+ABC + ABL = ABC + ABC + AB(C + C)=ABC + ABC + ABC + ABC=(ABC + ABC + ABC + 1+(ABC + ABC + ABC + ABC^ 0=> D3 = D5 = Z)7 = Z)6 = 1, D o = D x = = Z)4 = O74x1515f 6试用4选1数据选择器来实现数值比较器1位数值比较器厶(A >B)=A B乙3(A =占)=AJB + ~AB =乙2(A V 占)=~AB如何比较A3A2A1A0A3 & B3—> A2 &厶(A > B) 厶(AM) 乙2 (A vB)二AB + AB& B3B2B{B Q—A] & By--yAg & JB Q数值比较跖:74x85)L\(A > B)= A3 B3 + (冬。

^ )企B2 + (A3QB3 )(A2©B2B x +(A3©B3)(A2©B2X A O B.)A)瓦+ (43^^占3 )(42(^)厶2 )(A]G)Q )(企>^^占0 )*(A>B)©B3X A2©B2X A 0B\L3(A = B)=(A3X A)©B0)•/(・乙2 (A V B)= A3B3+ (^3©^3 )^2^2 + (^3©^3 X A>O^2 )A ^1+(4 ©B3)( A2©B2X A OQ )石%+(4 ©B3 X 企32 XA G〉Q)(竝 3。

”(z)数值比较對74x85)74x85数值比较器(74x85)[注意]:当只比较两个四位二进制数时,例:Compare X,A X Q <x o YO X1 Y1 X2 Y2 X374x85攵骂AY Q74x85L QA<.B) L(A=B) L(A A B)X <YX = Y X >YX4 Y4 X5 Y5 X6 Y6 X7 Y4 AO BO A1 B1 A2 B2 A3 B3数值比较器(CC14585)/<A<B)/<A=B)1 0 --------&—y(A<B)& >数值比较器(CC14585)Y(A <B)= A3B. +(A3 OS3)A2B2 +(A3 OB3 )(A2©82)A1B1+ (AO d )(9 昱)(AQ 马)石凤+ (AOd X^O^2 X A 0^1 XA)©^0 ”(AVB) Y(4 = B)=(A3 o^3 )(A2 o^2 )(A QB\ XA) OB0)e/D3c3—D2 c2—D\—n0 Co —Y(A<B>Y(A =B)D7c7—D.G—D5C5—D AC4—sssyooY(A<B>Y(A=B)Y(C<D)Y(C=D)I(AVB)A= B)I<A<B)I<A = B>I<A>B>Y(A>B)y <C>D>(AM)半加器X Y 'out s0 0 000 1 0 11 0 0 11 1 10outc in 是进位输入信号 c out 是进位输出信号Cout、\BC in A \ 00 01 11 10I 1 I1m [i ?C = AB + (A ® B)C in ?A B C in c t s out 0 0 0 0 0 0 0 1 0 1 0 1 0 0 1 0 1 1 1 0 1 0 0 0 1 1 0 1 1 0 1 1 0 1 0 1 1 11 1全加器的真值表S = 4 ㊉ B在C = AB +(A㊉中, AB称作进位产生信号A㊉B称作进位传输信号进位产生信号A Bc0FA G“进位传输信号全加器逻辑符号u>如何设计4・bit全加器?* 人2人2S S超前进位加法器0+ = A B t + (A ® Bj)0, =q + pg对于四位二进制数的加法,O] = +(A)① BoWo = G o + 7%Uo<S2 = +(A] ® d )0] = q + P x c x+ 年G°+马C73 = A?占 2 + (人2 B?)C 2 = U 2 + P?U 2=0^2 + 卩2^\ + 尸2.尺G^O + 尺只)U。

O4 —A3B3 +(A3 包>£3)^3 = G^3 +=0^3 + 卩3^^2 + ^3 ^2 ^-^2 + 卩3卩2卩\0\ + ^3 ^2^1 ^0^*074x283 x2AS2 B\力0ABoB3Bzco。