数字电子技术基础答案

数字电子技术基础试题及答案

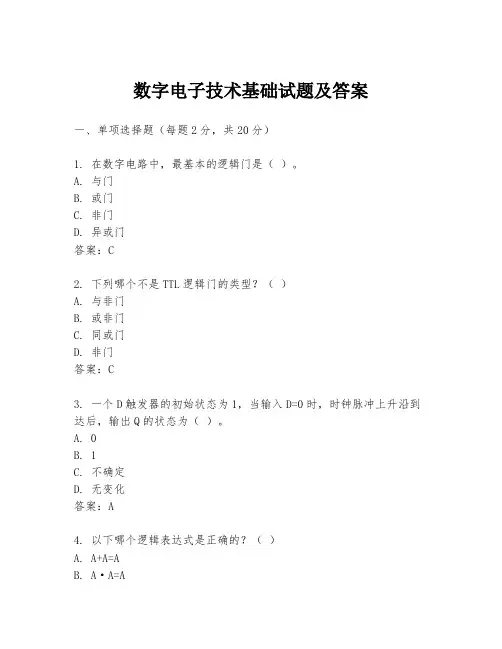

数字电子技术基础试题及答案一、单项选择题(每题2分,共20分)1. 在数字电路中,最基本的逻辑门是()。

A. 与门B. 或门C. 非门D. 异或门答案:C2. 下列哪个不是TTL逻辑门的类型?()A. 与非门B. 或非门C. 同或门D. 非门答案:C3. 一个D触发器的初始状态为1,当输入D=0时,时钟脉冲上升沿到达后,输出Q的状态为()。

A. 0B. 1C. 不确定D. 无变化答案:A4. 以下哪个逻辑表达式是正确的?()A. A+A=AB. A·A=AC. A+A=0D. A·A=0答案:B5. 一个4位二进制计数器,从0000开始计数,当计数到1111时,下一个状态是()。

A. 0000B. 1000C. 10000D. 0111答案:A6. 在数字电路中,若要实现一个逻辑函数,下列哪种方法最为经济?()A. 使用与非门B. 使用或非门C. 使用与门D. 使用或门答案:A7. 一个三态输出门,当控制端为高电平时,输出状态为()。

A. 高阻态B. 低电平C. 高电平D. 低阻态答案:C8. 以下哪个是BCD码的特点?()A. 每个十进制数字对应一个唯一的二进制代码B. 每个二进制数字对应一个唯一的十进制数字C. 每个二进制数字对应一个唯一的十六进制数字D. 每个十进制数字对应多个二进制代码答案:A9. 在数字电路中,一个反相器的逻辑功能是()。

A. 与B. 或C. 非D. 异或答案:C10. 一个JK触发器在时钟脉冲上升沿到达时,如果J=1,K=0,则触发器的状态()。

A. 保持不变B. 翻转C. 置0D. 置1答案:D二、填空题(每题2分,共20分)1. 一个2输入的与门,当两个输入都为1时,输出为______。

答案:12. 在数字电路中,一个D触发器的D端输入为0,时钟脉冲上升沿到达后,输出Q的状态为______。

答案:03. 一个4位二进制计数器,如果初始状态为0101,下一个状态为______。

《数字电子技术基础》试题及参考答案_shijuan1

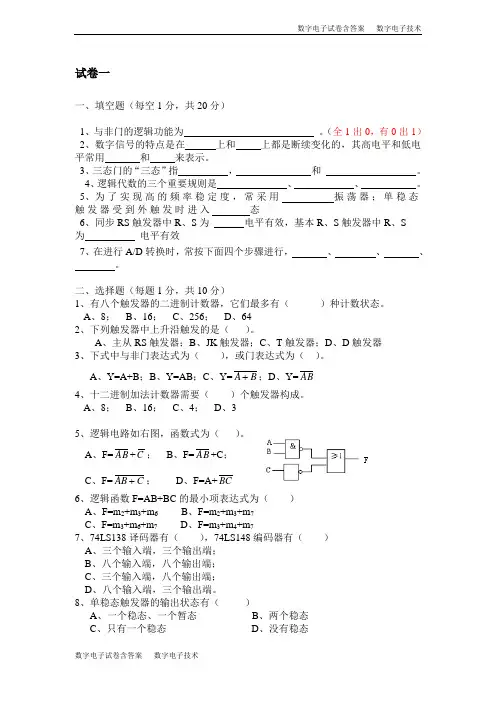

试卷一一、填空题(每空1分,共20分)1、与非门的逻辑功能为。

(全1出0,有0出1)2、数字信号的特点是在上和上都是断续变化的,其高电平和低电平常用和来表示。

3、三态门的“三态”指,和。

4、逻辑代数的三个重要规则是、、。

5、为了实现高的频率稳定度,常采用振荡器;单稳态触发器受到外触发时进入态6、同步RS触发器中R、S为电平有效,基本R、S触发器中R、S为电平有效7、在进行A/D转换时,常按下面四个步骤进行,、、、。

二、选择题(每题1分,共10分)1、有八个触发器的二进制计数器,它们最多有()种计数状态。

A、8;B、16;C、256;D、642、下列触发器中上升沿触发的是()。

A、主从RS触发器;B、JK触发器;C、T触发器;D、D触发器3、下式中与非门表达式为(),或门表达式为()。

A、Y=A+B;B、Y=AB;C、Y=BA+;D、Y=AB4、十二进制加法计数器需要()个触发器构成。

A、8;B、16;C、4;D、35、逻辑电路如右图,函数式为()。

A、F=AB+C;B、F=AB+C;AB+;D、F=A+BCC、F=C6、逻辑函数F=AB+BC的最小项表达式为()A、F=m2+m3+m6B、F=m2+m3+m7C、F=m3+m6+m7D、F=m3+m4+m77、74LS138译码器有(),74LS148编码器有()A、三个输入端,三个输出端;B、八个输入端,八个输出端;C、三个输入端,八个输出端;D、八个输入端,三个输出端。

8、单稳态触发器的输出状态有()A、一个稳态、一个暂态B、两个稳态C、只有一个稳态D、没有稳态三、判断(每题1分,共10分):1、逻辑变量的取值,1比0大。

(×)2、对于MOS门电路多余端可以悬空。

(×)3、计数器的模是指对输入的计数脉冲的个数。

(×)4、JK触发器的输入端J 悬空,则相当于J = 0。

(×)5、时序电路的输出状态仅与此刻输入变量有关。

《数字电子技术基础》试题及参考答案_shijuan1

试卷一一、填空题(每空1分,共20分)1、与非门的逻辑功能为。

(全1出0,有0出1)2、数字信号的特点是在上和上都是断续变化的,其高电平和低电平常用和来表示。

3、三态门的“三态”指,和。

4、逻辑代数的三个重要规则是、、。

5、为了实现高的频率稳定度,常采用振荡器;单稳态触发器受到外触发时进入态6、同步RS触发器中R、S为电平有效,基本R、S触发器中R、S为电平有效7、在进行A/D转换时,常按下面四个步骤进行,、、、。

二、选择题(每题1分,共10分)1、有八个触发器的二进制计数器,它们最多有()种计数状态。

A、8;B、16;C、256;D、642、下列触发器中上升沿触发的是()。

A、主从RS触发器;B、JK触发器;C、T触发器;D、D触发器3、下式中与非门表达式为(),或门表达式为()。

A、Y=A+B;B、Y=AB;C、Y=BA+;D、Y=AB4、十二进制加法计数器需要()个触发器构成。

A、8;B、16;C、4;D、35、逻辑电路如右图,函数式为()。

A、F=AB+C;B、F=AB+C;AB+;D、F=A+BCC、F=C6、逻辑函数F=AB+BC的最小项表达式为()A、F=m2+m3+m6B、F=m2+m3+m7C、F=m3+m6+m7D、F=m3+m4+m77、74LS138译码器有(),74LS148编码器有()A、三个输入端,三个输出端;B、八个输入端,八个输出端;C、三个输入端,八个输出端;D、八个输入端,三个输出端。

8、单稳态触发器的输出状态有()A、一个稳态、一个暂态B、两个稳态C、只有一个稳态D、没有稳态三、判断(每题1分,共10分):1、逻辑变量的取值,1比0大。

(×)2、对于MOS门电路多余端可以悬空。

(×)3、计数器的模是指对输入的计数脉冲的个数。

(×)4、JK触发器的输入端J 悬空,则相当于J = 0。

(×)5、时序电路的输出状态仅与此刻输入变量有关。

数字电子技术课后答案

数字电子技术基础答案第1章自测题 1.1填空题1. 100011.11 00110101.01110101 11110.01 1E.42. 43. n 24. 逻辑代数 卡诺图5.)(D C B A F )(D C B A F +='6.))((C B D C B A F7. 代数法 卡诺图8. 1 1.2判断题1. √2.√3. × 1.3选择题 1.B 2.C 3.C1.4 A F =1⊙B AB F 2 B A F +=3 1.51.6 C L =1.7 AB C B A BC Y 习题1.1 当000012 A A A ,7A 到3A 有1个不为0时,就可以被十进制8整除 1.2 (a)AC BC AB F ++=1 (b )B A AB F +=2(c)C B A S ⊕⊕= AC BC AB C 0 1.3略1.4 (1) )(B A D C F )(1 ))((1B A D C F ++='(2) )(B A B A F )(2 ))((2B A B A F ++='(3) E D C B A F 3 DE C AB F ='3(4) )()(4D A B A C E A F )())()((4D A C AB E A F +++='1.5 C B A F ⊕⊕=1.6 (1) B A C B C A L (2) D B C B D C A L (3) AD L (4) E ABCD L (5) 0 L 1.7 C B A BC A C AB ABC C B A L ),,( 1.8(1) ABD D A C F 1 (2) BC AB AC F 2(3) C A B A B A F 3 (有多个答案) (4) C B D C AB C A CD F +++=4 (5) C B A ABD C B A D B A F 5 (6) 16 F 1.9 (1) AD D C B B A F 1 (2) B A AC F 2(3) D A D B C B F 3 (4) B C F 4 1.10 (1) C A B F 1 (2) B C F 2(3) D A B C F 3 (4) C B A D B D C F 4 1.11 C A B A D F1.12 (1) D B A D C A D C B F 1(多种答案) (2) C B BCD D C D B F 2 (3) C B C A D C F 3 (4) A B F 4 (5) BD D B F 5 (6) C B D A D C A F 6(多种答案) (7) C A D B F 7(多种答案) (8) BC D B F 8(多种答案) (9) B D C F 9 1.13 略第2章自测题 2.1 判断题1. √2. √3. ×4. √5. √6. √7. ×8. √9. × 10√ 2.2 选择题1.A B 2.C D 3.A 4.B 5.B 6.A B D 7.C 8.A C D 9.A C D 10.B 习题2.1解:ABC Y =12.2解:(a)mA 234.0503.012=-=-=C CES CC BS R U V I βBS mA 1.0537.06I I B <=-=∴三极管处于放大状态,)V (711.05012=⨯⨯-=-=C B CC O R I V u β。

《数字电子技术基础》课后习题及参考答案

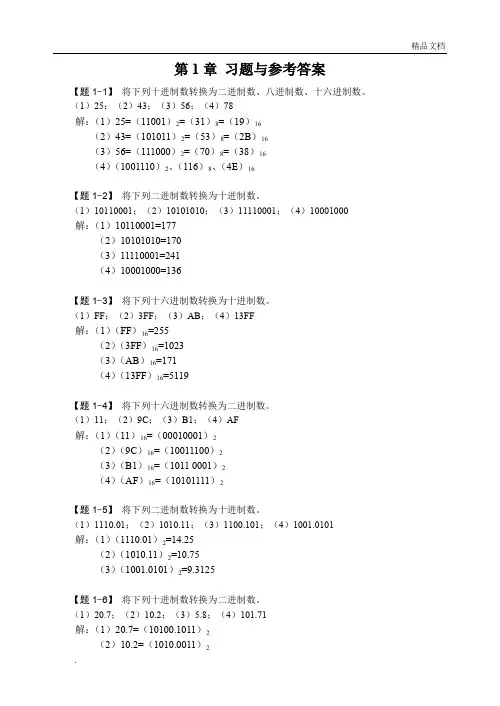

第1章习题与参考答案【题1-1】将下列十进制数转换为二进制数、八进制数、十六进制数。

(1)25;(2)43;(3)56;(4)78解:(1)25=(11001)2=(31)8=(19)16(2)43=(101011)2=(53)8=(2B)16(3)56=(111000)2=(70)8=(38)16(4)(1001110)2、(116)8、(4E)16【题1-2】将下列二进制数转换为十进制数。

(1)10110001;(2)10101010;(3)11110001;(4)10001000 解:(1)10110001=177(2)10101010=170(3)11110001=241(4)10001000=136【题1-3】将下列十六进制数转换为十进制数。

(1)FF;(2)3FF;(3)AB;(4)13FF解:(1)(FF)16=255(2)(3FF)16=1023(3)(AB)16=171(4)(13FF)16=5119【题1-4】将下列十六进制数转换为二进制数。

(1)11;(2)9C;(3)B1;(4)AF解:(1)(11)16=(00010001)2(2)(9C)16=(10011100)2(3)(B1)16=(1011 0001)2(4)(AF)16=(10101111)2【题1-5】将下列二进制数转换为十进制数。

(1)1110.01;(2)1010.11;(3)1100.101;(4)1001.0101解:(1)(1110.01)2=14.25(2)(1010.11)2=10.75(3)(1001.0101)2=9.3125【题1-6】将下列十进制数转换为二进制数。

(1)20.7;(2)10.2;(3)5.8;(4)101.71解:(1)20.7=(10100.1011)2(2)10.2=(1010.0011)2(3)5.8=(101.1100)2(4)101.71=(1100101.1011)2【题1-7】写出下列二进制数的反码与补码(最高位为符号位)。

数字电子技术基础第一章练习题及参考答案

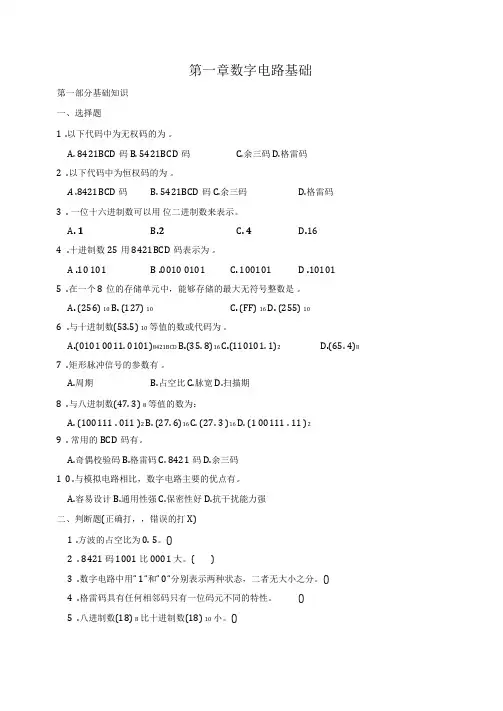

第一章数字电路基础第一部分基础知识一、选择题1.以下代码中为无权码的为。

A. 8421BCD码B. 5421BCD码C.余三码D.格雷码2.以下代码中为恒权码的为。

A .8421BCD码B. 5421BCD码C.余三码D.格雷码3. 一位十六进制数可以用位二进制数来表示。

A. 1B.2C. 4D.164.十进制数25用8421BCD码表示为。

A .10 101B .0010 0101 C. 100101 D .101015.在一个8位的存储单元中,能够存储的最大无符号整数是。

A. (256) 10B. (127) 10C. (FF) 16D. (255) 106.与十进制数(53.5) 10等值的数或代码为。

A.(0101 0011. 0101)8421BCDB.(35. 8)16C.(110101. 1)2D.(65. 4)87.矩形脉冲信号的参数有。

A.周期B.占空比C.脉宽D.扫描期8.与八进制数(47. 3) 8等值的数为:A. (100111 . 011 )2B. (27. 6)16C. (27. 3 )16D. (1 00111 . 11 )29. 常用的BCD码有。

A.奇偶校验码B.格雷码C. 8421码D.余三码10 .与模拟电路相比,数字电路主要的优点有。

A.容易设计B.通用性强C.保密性好D.抗干扰能力强二、判断题(正确打,,错误的打X)1.方波的占空比为0. 5。

()2. 8421 码1001 比0001 大。

( )3.数字电路中用“ 1”和“ 0”分别表示两种状态,二者无大小之分。

()4.格雷码具有任何相邻码只有一位码元不同的特性。

()5.八进制数(18) 8比十进制数(18) 10小。

()6.当传送十进制数5时,在8421奇校验码的校验位上值应为1。

( )7.在时间和幅度上都断续变化的信号是数字信号,语音信号不是数字信号。

()8.占空比的公式为:q = t w / T,则周期T越大占空比q越小。

数字电子技术基础课后答案(李雪飞)

(1)

(2)

[题2.11]

(1)

(2)

[题2.12]

Y1为高电平,Y2为低电平,Y3为低电平,Y4为高阻态,Y5为低电平,Y6为高阻态,Y7为低电平,Y8为低电平,Y9为高电平,Y10为低电平

[题2.13]

Y1为低电平,Y2为低电平,Y3为低电平,Y4为低电平

[题2.14]

这种扩展输入端的方法不能用于TTL门电路。CMOS门电路的内部结构决定了其输入端的个数不能太多,由于其输入信号的范围较宽(0~VDD),因此,可以采用本题的扩展方式。而TTL门的输入输出信号的高低电平分别为3.6V和0.3V。

对于Y3和Y4来说,采用此连接方式后,不能满足TTL电路输出电平的要求,无法驱动后级TTL门工作。

[题2.15]

(a)错。TTL门电路不能直接驱动晶体管,否则在与非门输出高电平3.6V时,会将晶体管和门电路损坏。应在晶体管基极接一个电阻Rb,电路如图(a)所示。

(b)错。集电极开路门应用中必须在电源与其输出端之间加一个外接电阻,正确的电路如图(b)所示。

[题3.18]

电路如下图

当M=0时,

当M=1时,

[题3.19]

[题3.20]

解:设两个5位二进制数分别为A( )和B( )。依据题意,将两个5位二进制数的高4位,即 和 分别接入比较器的数据输入端,将 和 比较的结果 , 和 分别接入级联输入的 , 和 端,其函数表达式为

[题3.21]

解:由电路写出输出Y的逻辑函数式为

[题1.4]

(1)(2942)D(2)(10010010.01110101)BCD

[题1.5]

(1)原码和补码都是01001(2)原码是11101,补码是10011

《数字电子技术基础》课后习题及参考答案#(精选.)

第1章习题与参考答案【题1-1】将下列十进制数转换为二进制数、八进制数、十六进制数。

(1)25;(2)43;(3)56;(4)78解:(1)25=(11001)2=(31)8=(19)16(2)43=(101011)2=(53)8=(2B)16(3)56=(111000)2=(70)8=(38)16(4)(1001110)2、(116)8、(4E)16【题1-2】将下列二进制数转换为十进制数。

(1)10110001;(2)10101010;(3)11110001;(4)10001000 解:(1)10110001=177(2)10101010=170(3)11110001=241(4)10001000=136【题1-3】将下列十六进制数转换为十进制数。

(1)FF;(2)3FF;(3)AB;(4)13FF解:(1)(FF)16=255(2)(3FF)16=1023(3)(AB)16=171(4)(13FF)16=5119【题1-4】将下列十六进制数转换为二进制数。

(1)11;(2)9C;(3)B1;(4)AF解:(1)(11)16=(00010001)2(2)(9C)16=(10011100)2(3)(B1)16=(1011 0001)2(4)(AF)16=(10101111)2【题1-5】将下列二进制数转换为十进制数。

(1)1110.01;(2)1010.11;(3)1100.101;(4)1001.0101解:(1)(1110.01)2=14.25(2)(1010.11)2=10.75(3)(1001.0101)2=9.3125【题1-6】将下列十进制数转换为二进制数。

(1)20.7;(2)10.2;(3)5.8;(4)101.71解:(1)20.7=(10100.1011)2(2)10.2=(1010.0011)2(3)5.8=(101.1100)2(4)101.71=(1100101.1011)2【题1-7】写出下列二进制数的反码与补码(最高位为符号位)。

数字电子技术基础(数电)课后习题解答

解: ① (0011101)2 =1×24+ 1×23+ 1×22+ 1×20=(29)10

(0011101)2 =(0 011 101)2= (35)8 (0011101)2 =(0001 1101)2= (1D)16 同理:② (27.75)10,(33.6)8,(1B.C)16; ③ (439)10,(667)8,(1B7)16;

(1) Y=AB+BC+A'C'

=B+A'C'

BC

A

00 01 11 10

0

1

11

1

11

(2) Y=AB'C'+A'B'+A'D+C+BD =B’+C+D (或用圈0法)

CD 00 01 11 10

AB

00 1

1

1

1

01

1

1

1

11

1

1

1

10 1

1

1

1

(3) Y=A' (B'C+B(CD'+D))+ABC'D

1

010

1

011

1

100

1

101

1

110

1

111

0

题1.9 在举重比赛中,有甲、乙、丙三名裁判,其中甲为主裁判,乙、丙为副裁判,当主裁判 和一名以上(包括一名)副裁判认为运动员上举合格后,才可发出合格信号。列出该函数的 真值表。

数字电子技术基础课后习题及答案

第1章习题与参考答案【题1-1】将以下十进制数转换为二进制数、八进制数、十六进制数。

〔1〕25;〔2〕43;〔3〕56;〔4〕78解:〔1〕25=〔11001〕2=〔31〕8=〔19〕16〔2〕43=〔101011〕2=〔53〕8=〔2B〕16〔3〕56=〔111000〕2=〔70〕8=〔38〕16〔4〕〔1001110〕2、〔116〕8、〔4E〕16【题1-2】将以下二进制数转换为十进制数。

〔1〕10110001;〔2〕10101010;〔3〕11110001;〔4〕10001000解:〔1〕10110001=177〔2〕10101010=170〔3〕11110001=241〔4〕10001000=136【题1-3】将以下十六进制数转换为十进制数。

〔1〕FF;〔2〕3FF;〔3〕AB;〔4〕13FF解:〔1〕〔FF〕16=255〔2〕〔3FF〕16=1023〔3〕〔AB〕16=171〔4〕〔13FF〕16=5119【题1-4】将以下十六进制数转换为二进制数。

〔1〕11;〔2〕9C;〔3〕B1;〔4〕AF解:〔1〕〔11〕16=〔00010001〕2〔2〕〔9C〕16=〔10011100〕2〔3〕〔B1〕16=〔1011 0001〕2〔4〕〔AF〕16=〔10101111〕2【题1-5】将以下二进制数转换为十进制数。

〔1〕1110.01;〔2〕1010.11;〔3〕1100.101;〔4〕1001.0101解:〔1〕〔1110.01〕2=14.25〔2〕〔1010.11〕2=10.75〔3〕〔1001.0101〕2=9.3125【题1-6】将以下十进制数转换为二进制数。

〔1〕20.7;〔2〕10.2;〔3〕5.8;〔4〕101.71解:〔1〕20.7=〔10100.1011〕2〔2〕10.2=〔1010.0011〕2〔3〕5.8=〔101.1100〕2〔4〕101.71=〔1100101.1011〕2【题1-7】写出以下二进制数的反码与补码〔最高位为符号位〕。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Q 1

CP

Q 1

Q 0

&&D 1D 0第一组:

计算题

一、(本题20分)

试写出图示逻辑电路的逻辑表达式,并化为最简与或式。

解:C B A B A F ++=C B A B A F ++=

二、(本题25分)

时序逻辑电路如图所示,已知初始状态Q 1Q 0=00。

(1)试写出各触发器的驱动方程; (2)列出状态转换顺序表; (3)说明电路的功能;

解:(1)100Q Q D =,101Q Q D =; (2)00→10→01 (3)三进制移位计数器

三、(本题30分)

由集成定时器555组成的电路如图所示,已知:R 1=R 2=10 k

Ω,C =5μF 。

(1)说明电路的功能; (2)计算电路的周期和频率。

解:(1)多谐振荡器电路 (2)T 1=7s , T 2=3.5s

四、(本题25分)

用二进制计算器74LS161和8选1数据选择器连接的电路如图所示, (1)试列出74LS161的状态表; (2)指出是几进制计数器; (3)写出输出Z 的序列。

"1"

解:

(1)状态表如图所示 (2)十进制计数器

C

R R CC

u o

(3)输出Z的序列是0010001100

第二组:

计算题

一、(本题20分)

逻辑电路如图所示,试答:1、写出逻辑式并转换为最简与或表达式,2、画出用“与”门及“或”门实现的逻辑图。

B

二、(本题25分)

试用与非门设计一个三人表决组合逻辑电路(输入为A、B、C,输出为F),要求在A有一票决定权的前提下遵照少数服从多数原则,即满足:1、A=1时,F一定等于1,2、A、B、C中有两2个以上等于1,则输出F=1。

试:(1)写出表决电路的真值表;

(2)写出表决电路的逻辑表达式并化简;

(3)画出用与非门设计的逻辑电路图。

解:

(1)真值表

(2) 表达式:A BC A BC A F +=+=

(3)BC A A BC F •=+=

逻辑电路图

F

A

B

三 、(本题30分)

已知逻辑电路图及C 脉冲波形, 试:(1)写出各触发器的驱动方程;(2)列出逻辑状态表;(3)画出输出 Q 0,Q 1 的波形(设Q 0,Q 1 的初始状态均为“0”)。

答:

状 态 表 波 形 图

Q 1

Q 0

Q 0Q 1020010113

00

C

C

四、(本题25分)

由555集成定时器组成的电路如图1 所示。

已知电容C =100 F ,输入I u 和输出O u 的波形如图2 所示。

试 (1) 说明由555 集成定时器和R 、C 组成的是何种触发器(单稳态、 双稳 态、 无稳态),(2) 对应输入I u 和输出 O u 的波形画出电容C 的电压波形图 ,(3)求电阻R 的值。

图2答:

s)

O

Ω

=

⨯

⨯

-

=

=

-

K

5.

54

10

100

1.1

5

11

1.16

C

t

R W

第三组:

计算题

一、(本题20分)

逻辑电路如图所示,写出逻辑式 并化简成最简与或表达式,画出逻辑电路图。

1

&

≥1

&

&

≥1

B

A C

D

F

解:F=CD BC )B A (++=D BC 逻辑图如下

二、(本题25分)

试用与非门设计一个三人表决组合逻辑电路(输入为A 、B 、C ,输出为F),要求在A 有一票否决权的前提下遵照少数服从多数原则,即满足:1、A=0时,F 一定等于0,2、A 、B 、C 中有2个以上等于1,则输出F=1。

试:(1)写出表决电路的真值表;(2)写出表决电路的逻辑表达式;(3)画出用与非门设计的逻辑电路图。

解:真值表如下 A B C F 0 0 0 0

0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 1 1 1 0 1 1 1 1 1

F=AB AC AB AC ABC C AB C B A •=+=++ 逻辑图如下

三、(本题30分)

已知逻辑电路图及C 脉冲波形, 试:(1)写出各触发器的驱动方程;(2)列出逻辑状态表;(3)画出输出 Q 0,Q 1 的波形(设Q 0,Q 1 的初始状态均为“0”)。

解:J0=1Q ,K0=1,J1=Q0,K1=1

Q1 Q0 1n 1Q + 1n 0Q +

0 0 0 1

0 1 1 0

1 0 0 0

1 1 0 0

波形图如下方所示

四、(本题25分)

由555 集成定时器组成的电路如图1 所示。

已知电容C=10μF,电阻R=100KΩ,输入

u的波形如图2 所示。

试:(1)说明由555集成定时器和R、C组成的是何种触发器(单1

稳态、双稳态、无稳态);(2)求输出脉冲的宽度的值;(3)画出电容电压

u和输出电压

C

u的波形。

O

+

-

+

∞+

-

+

∞Q

Q

D

S R D

C A

C B

+U CC

3

7

1

6

5

84

2

R

t (s)

5k Ω

5k Ω

5k Ω

u I

u O

u

I

u C

t (s)

O

O

C

图2

图1

S D u

O

t (s)

O

解:

构成单稳态触发器,输出脉冲宽度tw=1.1RC=1.1S

uc 的波形如上图所示。