软硬件协同设计_功能边界划分准则

SOC设计领域的核心技术——软硬件协同设计

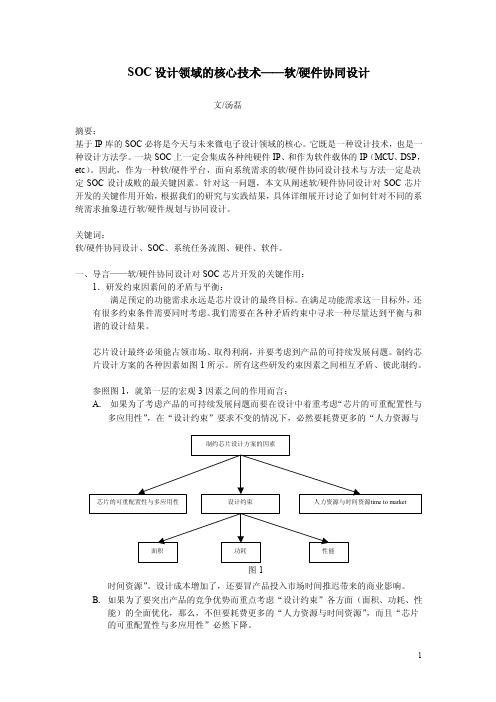

芯片的可重配置性与多应用性

设计约束

人力资源与时间资源time to market

面积

功耗

性能

图1 时间资源” 。设计成本增加了,还要冒产品投入市场时间推迟带来的商业影响。 B. 如果为了要突出产品的竞争优势而重点考虑“设计约束”各方面(面积、功耗、性 能)的全面优化,那么,不但要耗费更多的“人力资源与时间资源” ,而且“芯片 的可重配置性与多应用性”必然下降。

3

列。 如果要在实际设计中强调某一款专用芯片的可重配置性与多应用性,一个最有效的方 法,就是尽可能考虑到各个应用的大体功能需求,即每个单应用的单任务流图形式,然 后将各个单任务流图看作一个彼此互斥的多分支总系统任务流图来进行系统架构规划。 简单举例: TD-SCDMA、GSM、可视电话 3 模合一应用下(下行链路)的多分支系统 任务流图粗框架如图 2 所示: 多分支系统任务流图软/硬件划分原则如下: A. 首先采用算法将不同分支间功能相似的子任务节点尽可能进行一一自动对应。 B. 各个分支间,完全对应相同的子任务节点由硬件完成。 (比如,假设如果 3 个应用模 式下的语音解码协议完全相同,则完全可将语音解码部分做成纯硬件。 ) C. 各个分支间任务有差别的相对应节点由软件完成。 (如:3 种应用下彼此不同的协议 栈处理工作) D. 各个分支间任务不同, 但不适宜由软件完成的工作, 由不同硬件各自单独完成。 (比 如: 对于芯片的 3 模应用, 架构中一定要有 TD-RFIO、 GSM-RFIO、 可视电话 UART 3 个各自独立的对外接口模块,这里暂不讨论软件无线电的可实现性。 ) E. 软件载体(MCU、DSP)的最大处理能力应该由已被划分为软件任务的、各个分支 间任务相似的相对应节点对软件性能需求的最大值来决定。 (如图: 假设可视电话和 TD 的信源解码都要求有语音及图象解码能力,而 GSM 的信源解码只要求有语音解 码能力。则芯片中 DSP 的性能必须具备语音及图象解码能力。 ) 根据研究,对多分支系统任务流图,由于不同分支间的互斥性与分时性,可以将各个分 支进行基于对应节点功能相似度的图形合并,由此生成一张复合任务流图[3,4]。复合 任务流图中的每一个复合节点子任务,由生成该复合节点的原各个分支间相对应节点的 功能集之合集组成。 例如,上述 TD-SCDMA、GSM、可视电话 3 模式应用下的多分支系统任务流图的复合 任务流图粗框架形式如图 2 右所示。也就是说,对于多分支系统任务流图,我们可以通 过图论的方法将各个分支进行任务合并生成一张复合任务流图,当且仅当系统架构能够 胜任复合任务流图的功能及性能需求时,芯片设计能够满足所预定的可重配置性与多应 用性的需要。 (关于“基于节点任务相似度的多图自动化合并算法”可参考[3,4]。 ) 六、并行系统任务流图的软/硬件协同设计方法: 多并行与多分支系统任务的最大区别是各单任务流图在时间上并行因此不能进行合并。 比如对于手机基带芯片的应用而言,通话过程的上行与下行任务之间就可视为并行任 务。而对于手机大多数的其它功能需求,如:发短信、记事本、打游戏、上网、MP3, 等等,它们通常不可能与通话过程同时进行,并且它们彼此之间并行的可能性也不高。 我们可将其相互之间视为多分支系统任务[1]。各个分支任务的多样性适宜由软件来完 成,而软件载体(MCU、DSP)的最大处理能力则由各个分支间相对应各节点对软件性 能需求的最大值来决定。

嵌入式系统设计中的硬件与软件协同开发指南

嵌入式系统设计中的硬件与软件协同开发指南嵌入式系统设计是将计算机系统嵌入到设备或产品中,以完成特定的功能。

在嵌入式系统设计过程中,硬件与软件之间的协同开发是至关重要的。

本文将介绍硬件与软件协同开发的指南,包括硬件与软件设计的基本原则、协同开发的方法以及常见的开发工具和技术。

一、硬件与软件设计的基本原则1. 设计目标明确:在开始硬件与软件协同开发之前,明确设计的目标和功能,确保开发过程能够有针对性地进行。

2. 硬件与软件的分工合作:确定硬件与软件之间的功能划分和接口定义,确保两者能够有效地协同工作。

3. 通信性能和可靠性:在设计过程中,应该重视硬件与软件之间的通信性能和可靠性,包括数据传输速度、数据完整性、时序控制等。

4. 硬件的可扩展性和适应性:设计时应该考虑硬件的可扩展性和适应性,即在未来需求变化时能够方便地进行升级和改进。

5. 可测试性和可维护性:在设计硬件和软件时,应考虑到测试和维护的需求,提供相应的调试和故障排除的接口和手段。

二、硬件与软件协同开发的方法1. 并行开发:硬件与软件的开发应该并行进行,而不是线性顺序。

这样可以加快开发进度,减少后期修改的工作量。

2. 接口协议的定义:硬件与软件之间的接口应该事先定义清楚,包括接口电气特性、协议和通信方式等,并对接口进行一定的验证和测试。

3. 嵌入式系统仿真:使用嵌入式系统仿真工具,如ModelSim和QEMU等,可以加速硬件和软件的调试过程,并提前发现问题。

4. 封装与集成:硬件和软件的封装与集成应该在整个开发过程中密切协作,确保硬件和软件能够无缝地集成到最终产品中。

5. 迭代开发:在硬件和软件的设计过程中,应该采用多次迭代的方式,进行逐步优化和改进,以达到更好的性能和功能。

三、常见的开发工具和技术1. 软件开发工具:常用的软件开发工具包括编译器、调试器、性能分析工具等。

例如,对于嵌入式系统的软件开发,常用的工具有Keil、IAR Embedded Workbench和Eclipse等。

自动化系统中的软硬件一体化设计

自动化系统中的软硬件一体化设计随着科技的不断发展和进步,自动化系统在各个领域的应用越来越广泛。

而其中的软硬件一体化设计则成为了实现自动化系统高效运行的关键。

本文将对自动化系统中的软硬件一体化设计进行探讨,并介绍其重要性、设计原则以及实施方法等方面的内容。

一、软硬件一体化设计的重要性软硬件一体化设计是指在自动化系统的开发和设计过程中,将软件和硬件两个方面的元素紧密结合起来,相互配合,共同实现系统的功能。

它的重要性主要体现在以下几个方面:1. 提高系统性能:软硬件一体化设计可以充分发挥软硬件的优势,从而更好地满足系统的需求。

软件可以通过算法和控制策略来优化系统的运行效果,而硬件则提供了更加稳定和可靠的物理支持。

2. 简化系统结构:软硬件一体化设计能够将系统的各个部分进行统一整合,减少了不必要的接口和连接。

这样可以降低系统的复杂度,提高系统的可维护性和可扩展性。

3. 提高系统的可靠性:软硬件一体化设计能够通过相互配合和协同工作的方式,提高系统的稳定性和可靠性。

比如,硬件可以提供实时的数据输入和输出,而软件则可以对这些数据进行实时分析和处理。

二、软硬件一体化设计的原则在进行软硬件一体化设计时,需要遵循一定的原则,以确保设计的有效性和实施的顺利进行。

以下是一些常见的软硬件一体化设计原则:1. 确定系统需求:在进行软硬件一体化设计之前,首先需要明确系统的需求和目标。

这包括功能需求、性能需求、接口需求等。

只有明确了需求,才能有针对性地进行软硬件设计。

2. 确定软硬件分工:软硬件一体化设计并不是对软件和硬件进行简单的整合,而是需要根据各自的特点和优势,进行合理的划分和分工。

软件负责算法和控制策略的实现,而硬件负责数据采集和物理控制等方面的功能。

3. 考虑系统的可扩展性:软硬件一体化设计应该考虑到系统的未来发展和扩展。

这意味着设计的时候需要采用模块化和可拓展的结构,以便于后续的功能扩展和升级。

4. 进行系统级测试:软硬件一体化设计完成后,需要进行系统级测试,以验证系统的性能和功能是否达到要求。

电子产品研发中的软硬件协同设计技术

电子产品研发中的软硬件协同设计技术一、引言软硬件协同设计是指对系统中的软硬件部分使用统一的描述和工具进行集成开发,可完成全系统的设计验证并跨越软硬件界面进行系统优化。

软硬件协同设计所涉及到的内容有:HW-SW 协同设计流程、HW-SW 划分、HW-SW 并行综合、HW-SW 并行仿真。

软件硬件协同设计的设计流程:第一步,用HDL语言和C语言进行系统描述并进行模拟仿真和系统功能验证;第二步,对软硬件实现进行功能划分,分别用语言进行设计并将其综合起来进行功能验证和性能预测等仿真确认(协调模拟仿真);第三步,如无问题则进行软件和硬件详细设计;第四步,最后进行系统测试。

大规模集成电路的复杂度依照摩尔定律即每18个月单位元件数增加一倍的速度迅速发展,现在已经能够在单一硅芯片上集成MCU、MPU、DSP等模拟与数字混合电路,从而构成一个完整的系统,这就是片上系统(SOC)。

下面以SOC为例电子产品研发中的软硬件协同设计技术。

SOC是21世纪集成电路发展的必然趋势,SOC系统将原来由许多芯片完成的功能,集中到一块芯片中完成。

但SOC不是各个芯片功能的简单叠加,而是从整个系统的功能和性能出发,用软硬结合的设计和验证方法,利用IP 复用及深亚微米技术,在一个芯片上实现复杂的功能。

二、正文1、软硬件协同设计理论SOC是微电子设计领域的一场革命,SOC主要有3个关键的支持技术:①软、硬件的协同设计技术, 面向不同系统的软件和硬件的功能划分理论(Functional Partition Theory);②IP模块库问题;③模块界面间的综合分析技术。

其中软硬件协同设计技术不仅是SOC的重要特点,也是21世纪IT业发展的一大趋势。

HW-SW Co-design目的是为hardware 和software的协同描述、验证和综合提供一种集成环境。

SOC与IC的设计原理是不同的,但它的设计不可能一切从头开始,要将设计建立在较高的基础之上,利用已有的芯核进行设计重用,设计方法从传统的电路设计转向系统设计,设计的重心也从逻辑综合、布局布线转向系统的设计、软硬结合的设计以及仿真。

体系工程师的软硬件协同设计

体系工程师的软硬件协同设计体系工程师在软硬件协同设计中起着至关重要的作用。

软硬件协同设计是指在设计阶段中,软件和硬件工程师相互协作,通过有效的沟通和协调,达到整体系统设计的一致性和协调性。

本文将从软件和硬件两个方面探讨体系工程师在软硬件协同设计中的角色和任务。

一、软件方面的协同设计在软件方面,体系工程师需要与软件工程师密切合作,共同完成软件设计的任务。

软件设计是指在体系结构设计的基础上,对软件系统的具体功能进行设计和实现。

软件工程师根据需求分析的结果,设计出相应的软件模块,并编写出代码。

而体系工程师在软件方面的任务主要包括以下几个方面:1.需求分析和规格定义:体系工程师需要了解系统的需求,并将其转化为软件工程师可以理解的规格,以确保软件设计与整体系统设计的一致性。

2.软件模块设计:体系工程师需要与软件工程师共同确定软件模块的划分,并定义模块间的接口和通信方式,以便实现不同模块间的协同工作。

3.软件验证和测试:体系工程师需要协助软件工程师进行软件验证和测试,确保软件的功能和性能符合设计要求。

二、硬件方面的协同设计在硬件方面,体系工程师需要与硬件工程师密切合作,共同完成硬件设计的任务。

硬件设计是指在体系结构设计的基础上,对硬件系统的具体功能进行设计和实现。

硬件工程师负责设计出可实现功能的硬件电路和布局,而体系工程师在硬件方面的任务主要包括以下几个方面:1.硬件架构设计:体系工程师需要与硬件工程师共同确定硬件架构,包括选择适当的处理器、存储器等硬件组件,并定义它们之间的连接和通信方式。

2.硬件设计验证:体系工程师需要参与硬件设计的验证工作,包括功能验证、性能验证和可靠性验证等,以确保硬件设计符合系统的需求和规格。

3.硬件与软件的接口设计:体系工程师需要与软件工程师协商并确定硬件与软件之间的接口,包括数据传输格式、通信协议等,以确保硬件与软件的协同工作。

三、软硬件协同设计的挑战和解决方案软硬件协同设计面临着一些挑战,如需求变更、设计复杂度和设计周期压力等。

软硬件协同开发

软硬件协同开发软硬件协同设计的定义:软硬件协同设计是指对系统中的软硬件部分使用统一的描述和工具进行集成开发,可完成全系统的设计验证并跨越软硬件界面进行系统优化。

嵌入式系统设计早期,主要有两种方式:一是针对一个特定的硬件进行软件开发;二是根据一个已有的软件实现其具体的硬件结构。

前者是一个软件开发问题;后者是一个软件固化的问题。

早期的这种设计没有统一的软硬件协同表示方法;没有设计空间搜索,从而不能自动地进行不同的软硬件划分,并对不同的划分进行评估;不能从系统级进行验证,不容易发现软硬件边界的兼容问题;上市周期较长。

因此,早期的设计存在各种缺陷和不足。

使用软硬件协同设计后,从系统功能描述开始,将软硬件完成的功能作全盘考虑并均衡,在设计空间搜索技术的支持下,设计出不同的软硬件体系结构并进行评估,最终找到较理想的目标系统的软硬件体系结构,然后使用软硬件划分理论进行软硬件划分并设计实现。

在设计实现时,始终保持软件和硬件设计的并行进行,并提供互相通信的支持。

在设计后期对整个系统进行验证,最终设计出满足条件限制的目标系统。

由于软硬件协同设计是电子系统复杂化后的一种设计新趋势,现在嵌入式设计尽量依靠对软硬件的同时设计,用一种能对软硬件同时设计的系统描述来进行设计,其中SoC和SoPC是这一趋势的典型代表。

SoC设计技术始于20世纪90年代中期,它是一种系统级的设计技术。

如今,电子系统的设计已不再是利用各种通用集成电路IC(Integrated Circuit)进行印刷电路板PCB(Printed Circuit Board)板级的设计和调试,而是转向以大规模现场可编程逻辑阵列FPGA (Field Programmable Gate Array)或专用集成电路ASIC (Application Specific Integrated Circuit)为物理载体的系统级的芯片设计。

使用ASIC为物理载体进行芯片设计的技术称为片上系统技术,即SoC;使用FPGA作为物理载体进行芯片设计的技术称为可编程片上系统技术,即SoPC(System on Programmable Chip)。

软硬件协同设计

知识创造未来

软硬件协同设计

软硬件协同设计是指软件和硬件之间的设计过程中的密切合作和协

同工作。

软硬件协同设计旨在优化软硬件系统的整体性能、功耗、

可靠性、可维护性等方面。

在软硬件协同设计过程中,软件和硬件工程师需要密切合作,共同

定义系统需求、功能和接口。

软件工程师可以通过与硬件工程师讨

论和了解硬件设计的限制和约束,来优化软件设计并提升系统性能。

硬件工程师则可以通过了解软件设计的需求和特点,来优化硬件设

计并提高系统的可靠性和维护性。

软硬件协同设计还包括了软硬件的联合验证和调试。

通过联合验证,软硬件工程师可以同时测试软件和硬件的功能和性能,从而及早发

现和解决可能存在的问题。

同时,在调试阶段,软硬件工程师可以

共同分析和解决可能出现的软硬件集成问题。

软硬件协同设计在提高系统性能、降低开发成本和加快产品上市时

间方面具有重要的意义。

通过软硬件协同设计,可以减少软硬件集

成问题带来的延迟和成本,提高软硬件开发效率,从而更好地满足

用户的需求。

1。

软件设计中模块划分应遵循的准则

软件设计中模块划分应遵循的准则

模块划分是软件设计的重要环节之一,正确的模块划分可以增强软件的可维护性、可扩展性和可重用性。

下面是软件设计中模块划分应遵循的准则:

1.单一职责原则(SRP)

每个模块只负责一个功能,不允许一个模块负责多个功能。

这样可以让模块的职责清晰明确,便于维护和重用。

2.接口隔离原则(ISP)

如果一个模块对外提供多个接口,而客户端只需要使用其中部分接口,那么这些接口就应该被分成更小的接口,以避免客户端依赖不必要的接口。

3.依赖倒置原则(DIP)

高层模块不应该依赖底层模块,它们应该都依赖于抽象接口。

这样可以实现松耦合,提高软件的可维护性和可扩展性。

4.开闭原则(OCP)

模块应该对扩展开放,对修改关闭。

一旦模块完成了它的工作,就不应该频繁地修改它,而是应该通过扩展来改变它的行为。

5.里氏替换原则(LSP)

子类应该能够替换它的父类,而且程序仍然能够正确地运行。

这样可以保证扩展性和灵活性,提高软件的可维护性。

6.迪米特法则(LoD)

每个模块只应该与它的直接朋友进行交互,而不应该与陌生人进行交互。

这样可以降低模块之间的耦合度,提高软件的可维护性、可扩展性和可重用性。

7.缺陷注重原则

需要将缺陷注重在较小的区域,以便更容易修正和维护。

在模块划分过程中,需要结合实际情况,合理分配模块的职责,避免模块之间互相依赖,这样可以有效地降低系统的复杂度。

通信电子的软硬件协同设计

通信电子的软硬件协同设计软硬件协同设计是一种先进的设计方法,它通过把软件和硬件的设计过程无缝地结合起来,来提高产品设计的效率和质量。

在通信电子行业中,软硬件协同设计已经成为一种必不可少的设计方法。

本文就从不同角度探讨通信电子的软硬件协同设计。

一、软硬件协同设计的概念软硬件协同设计是指在某一产品开发的过程中,软件和硬件设计人员共同参与设计,协作完成产品设计的过程。

软硬件协同设计的核心是“一次设计,多次复用”,它充分利用不同领域工程师的专业知识和技能,把产品设计从单一的软硬件领域拓展到整个系统层面上。

在通信电子领域,软硬件协同设计的重要性越来越被关注。

它能够加速产品开发周期,降低产品成本,并且提高产品质量保证。

因此,软硬件协同设计已经成为各大通信电子企业必须掌握的关键技术之一。

二、软硬件协同设计的优势软硬件协同设计的优势主要体现在以下几个方面:1、加速产品设计周期。

传统的软硬件设计工作是分开进行的,两个设计团队独立完成各自的任务。

但是,软硬件协同设计把软硬件设计团队有机地融合在一起,形成一个有力的设计团队,这样可以避免资源的浪费和重复的设计,从而加速产品设计周期。

2、降低产品成本。

软硬件协同设计可以有效降低产品的成本。

软硬件团队合作完成的设计能够减少硬件设计中的器件数量,减少板子的呆板,同时可以提高软件的可重用性,从而降低生产成本。

3、提高产品质量保证。

软硬件协同设计可以大大提高产品的质量保证。

它的主要原因是对于整个系统的设计考虑更加全面和深入,并且从软硬件的共同点入手,从而解决了单一领域专业设计的短板,提高了整个系统设计的可靠性和稳定性。

三、软硬件协同设计的实现方法软硬件协同设计的实现方法多种多样。

下面列举几种常见的实现方法。

1、软件仿真软件仿真是软硬件协同设计中应用最广泛的一种方法。

可以使用仿真工具对软件和硬件进行准确的建模和仿真,并且能够提前发现设计缺陷和问题,从而将问题解决在实际制造过程之前。

计算机系统与组织结构计算机硬件与软件的协同设计

计算机系统与组织结构计算机硬件与软件的协同设计计算机硬件与软件的协同设计是计算机系统与组织结构中一个非常重要的环节。

在计算机科学和工程领域,硬件和软件的结合是创造出高性能、高可靠性以及高效能计算机系统的基础。

本文将探讨计算机系统与组织结构中硬件和软件间的协同设计,尤其是在现代计算机系统中的关键技术与方法。

一、硬件与软件的协同设计的概念协同设计是指计算机系统的硬件和软件之间的相互配合和协同工作。

它要求硬件和软件在各自的设计过程中相互考虑对方的需求,以实现整个系统的高性能和高可靠性。

硬件和软件的协同设计不仅仅是硬件工程师和软件工程师之间的合作,更是整个系统设计的一种全面的思想与方法。

二、硬件与软件的协同设计的重要性硬件与软件的协同设计在计算机系统与组织结构中具有重要的作用。

首先,硬件和软件的协同设计能够提高计算机系统的性能。

硬件和软件相辅相成,相互配合,能够更好地发挥各自的优势,提高系统的运行效率和响应速度。

其次,协同设计还能够提高系统的可靠性和稳定性。

在设计过程中,硬件和软件可以相互排查和纠正错误,避免系统出现故障和崩溃。

最后,协同设计还能够降低系统的成本。

通过充分考虑硬件和软件之间的兼容性,避免资源的浪费,可以降低系统的开发和维护成本。

三、现代计算机系统中硬件与软件的协同设计的关键技术与方法1. 硬件和软件接口设计:在计算机系统中,硬件和软件之间通过接口进行通信和交互。

因此,设计合理的硬件和软件接口是协同设计的基础。

在接口设计中,需要考虑接口的稳定性、扩展性和兼容性,以便适应未来系统的升级和扩展需求。

2. 硬件资源配置与优化:硬件资源的配置和优化对系统的性能和能效具有重要影响。

在协同设计中,需要根据软件的需求合理配置硬件资源,并通过优化算法和策略提高资源利用率。

同时,硬件资源的配置也需要考虑功耗和散热等问题,以保证系统的稳定和可靠性。

3. 软件算法和程序优化:软件算法和程序的优化对系统的性能和效能也具有重要作用。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Functional: Partition function, then implement

– Enables better size/performance tradeoffs – Uses fewer objects, better for algorithms/humans – Permits hardware/software solutions – But, it’s harder than graph partitioning

12

Basic Partitioning Issues

Specification-abstraction level: input definition

– Executable languages becoming a requirement • Although natural languages common in practice. – Just indicating the language is insufficient – Abstraction-level indicates amount of design already done • e.g. task DFG, tasks, CDFG, FSMD

An important advantage of functional partitioning is that it allows hardware/software solutions

10

Binding Software to Hardware

Binding: assigning software to hardware components After parallel implementation of assigned modules, all design threads are joined for system integration

Two design tasks:

– Allocate system components or ASIC constraints – Partition functionality among components

Constraints

– Cost, performance, size, power

Partitioning Methods

1

Outline

Introduction to Hardware-Software Codesign Models, Architectures, Languages Partitioning Methods Design Quality Estimation Specification Refinement Co-synthesis Techniques Function-Architecture Codesign Paradigm Codesign Case Studies

functions in G for a given partition {H,S}

– Set of performance constraints, Cons = (C1, ... Cm), where Cj =

{G, timecon}, indicates the maximum execu in group G and G O

– ATM Virtual Private Network – Digital Camera with JPEG

2

System Partitioning

System functionality is implemented on system components

– ASICs, processors, memories, buses

• Utilize high-level synthesis algorithms to generate a register transfer implementation from a behavior description

Partitioning algorithms are closely related to the process scheduling model used for the software side of the implementation

8

Partitioning Approaches

Start with all functionality in software and move portions into hardware which are time-critical and can not be allocated to software (software-oriented

This is a multivariate optimization problem that when automated, is an NP-hard problem

4

HW/SW Partitioning Formal Definition

A hardware/software partition is defined using two sets H and S, where H O, S O, H S = O, H S =f Associated metrics:

– Early binding commits a design process to a certain course – Late binding, on the other hand, provides greater flexibility

for last minute changes

11

high-volume production)

– Incurs high cost of developing and maintaining (complex)

software

7

Structural vs. Functional Partitioning

Structural: Implement structure, then partition

– The system’s functionality is described as collection of

indivisible functional objects

– Each system component’s functionality is implemented in

either hardware or software

Granularity: specification size in each object

– Fine granularity yields more possible designs – Coarse granularity better for computation, designer

partitioning)

Start with all functionality in hardware and move portions into software implementation (hardware-oriented

partitioning)

9

System Partitioning (Functional Partitioning)

Hardware/Software System Architecture Trends

Some operations in special-purpose hardware

– Generally take the form of a coprocessor communicating

with the CPU over its bus

– Good for the hardware (size & pin) estimation. – Size/performance tradeoffs are difficult. – Suffer for large possible number of objects. – Difficult for HW/SW tradeoff.

• Computation must be long enough to compensate for the communication overhead

– May be implemented totally in hardware to avoid instruction

interpretation overhead

5

Performance Satisfying Partition

A performance satisfying partition is one for which performance(Cj.G) Cj.timecon, for all j=1…m Given O and Cons, the hardware/software partitioning problem is to find a performance satisfying partition {H,S} such that Hsize(H) is minimized The all-hardware size of O is defined as the size of an all hardware partition (i.e., Hsize(O))

System partitioning in the context of hardware/software codesign is also referred to as functional partitioning Partitioning functional objects among system components is done as follows