CPLD低频数字相位测量仪的设计

基于CPLD的低频数字相位测量仪

・

测控技术 ・

电 子 工 皇 师

20 0 6年 1 0月

3 软件实现

软件 主要 是 实 现 P WM 的 占空 比的 测量 , 基 本 其 原理 是利 用 85 单 片机 内部 的计数 器 来 测量 。具 0 l 体过 程是 : 过对 85 通 0 l的 P . 11口进行 实 时查询 , 当检 测 到 P . 脚 的信 号为 高 电平 时 , 11 开 中断计 数 , 然后 继续 查 询 P . 1 1的状 态 。 当检 测 到 P . 脚 的信号 为低 11

同步平均 时 间的 门控 信 号 , 生 满 周 期 的控 制 门 。同 产 时 , 电路还 完成 了相 位超前 和滞 后 的判 断 。 该

收 稿 日期 : 05 1-5 修 回 日 : 0 6 2 2 0 —12 ; 期 2 0 3 。 图 2 系统 框 图

2 硬件电路 的设计与分析

T 中断程 序 O

读T 计数值为 O

i!

读T 计数值为 T: O o 关T 中断 O

电平 时, 录 计数器 当前的数信号为高电 11 11 平时 , 录 计数器 的计数值 作为一个 P 记 WM 周 期 ,WM 的 占空 比 D=( 。r 0 % , 电源 或 负 P / 0)X10 而

相、 门控 、 同步、 计数 、 锁存、 数据选择等逻辑功能 ; 片机部分对数据进行处理 , 单 完成数据 的读取、 运 算、 数据类型转化 、 循环扫描显示控制等功能 , 并将待测信号的相位差显示在八段数码管上。 关键词 : 相位测量仪 ;P D 单片机; CL ; 鉴相

中图 分类 号 : M 3 . T 9 33

维普资讯

第3 2卷第 l 0期 20 0 6年 l 0月

基于CPLD的低频相位测量仪的设计与实现PPT资料优秀版

鉴相器原理图和仿真波形

系统模块设计,包括信号整形模块,CPLD数据采集模块, 单片机数据运算控制及数据显示模块

单片机模块的程序设计流程图

等精度频率/相位计实物图

CPLD模块的软件设计与仿真

在图中可以看到,计数结果是,对TCLK的计数值是5,对BCLK的计数值是64(十六进制)。 由于系统将CPLD和单片机相结合,综合其优点,具有集成度高、稳定性好、设计灵活和设计效率高等优点。 本系统采用Altera公司CPLD芯片EPM240T100C5N和单片机AT89S52构成测控主体。 包括硬件设计和软件设计两大部分。 由仿真波形可知,该脉冲信号的占空比与这两路信号 在图中,取SPUL=0时,系统被允许进行脉宽测试。 由仿真波形可知,该脉冲信号的占空比与这两路信号 包括硬件设计和软件设计两大部分。 单片机模块的程序设计流程图 为了便于观察,图中仿真波形中的TCLK和BCLK的周期分别设置为75us和500ns。 通过控制SEL就能按照8个8位将计数器中的32位数读入单片机中进行计算, 由此,不难算出,TCLK的高电平脉宽应该等于4BH乘以BCLK的周期。 这时,CLR一个正脉冲后,系统被初始化。 相位测量:将两路被测正弦波信号整成方波信号,通过鉴相器,输出一路具有不同占空比的脉冲波形。 CPLD模块的软件设计与仿真 单片机模块的程序设计流程图 仿真波形中TCLK和BCLK的周期分别设置为10us和500ns。

仿真波形中TCLK和BCLK的周期分别设置为10us和500ns。在图中可以看到, 计数结果是,对TCLK的计数值是5,对BCLK的计数值是64(十六进制)。通 过控制SEL就能按照8个8位将计数器中的32位数读入单片机中进行计算,

在图中,取SPUL=0时,系统被允许进行脉宽测试。为了便于观察,图中 仿真波形中的TCLK和BCLK的周期分别设置为75us和500ns。此时,CL和 CLR的功能都能发生变化,前者为1时测信号高电平的脉宽,为0时测低电 平的脉宽;而后者CLR变为1时作系统初始化,由1变为0后启动电路系统 的标准信号计数器BZQ准备对标准频率进行计数。而允许计数的条件是 此后出现的第一个脉宽。由图11可见,当CL= 1,TCLK的高电平脉冲到来 时,即启动了BZQ进行计数,而在TCLK的低电平到来时停止计数,状态 信号EEND则由低电平变为高电平,告诉单片机计数结束。计数值可以通 过SEL读出,这里是4BH.

低频数字式相位测量仪设计报告

低频数字式相位测量仪摘要本低频数字式相位测量仪由数字式移相信号发生器、模拟移相网络、数字相位测量部分以及人机接口等模块组成。

数字式移相信号发生器采用双路时统DDS技术,基于FPGA实现。

相位测量部分采用基于相位—时间变换的等精度测量技术,由单片机控制CPLD实现。

本系统硬件设计应用了EDA技术,软件设计采用基于C51的模块化设计技术,总体上较好地完成了题目基本和发挥部分的要求。

并增加了扫频、扫相、扫幅及相位打印功能,扩展了模拟移相器移相范围及相位显示形式。

关键词:时统DDS数字移相等精度数字测相 FPGA/CPLD一.方案论证与选择根据题目要求本系统可分解为数字式移相信号发生器、模拟移相网络及相位测量部分等三个模块。

模拟移相网络已由题目给出,以下对另两部分实现方案进行论证。

(一)数字式移相信号发生器方案论证方案一:用PLL 频率合成技术产生正弦波信号,将其通过FFT 变换到频域,再乘以一定的旋转因子,即相当于时域的时延(移相)。

不同的旋转因子对应不同的移相,但对不同频率的输入信号进行移相时,需要调整滤波器参数或改变滤波器采样率。

前者运算量较大,后者需要用到PLL 技术,硬件繁琐。

方案二:应用单片机产生移相信号。

将正弦波信号数字化,形成数据表存入FLASH 或EPROM 等非易失性存储芯片中,单片机交叉读出该数据表中的数据,形成两路波形信号,送往两路D/A ,得到两路具有一定相位差的正弦波。

这种处理方式的实质是将数据地址的偏移量映射为信号间的相位差。

但受单片机速度限制,这种方法难以产生较高频率的信号。

方案三: 采用DDS 技术产生移相信号。

1、DDS 频率合成DDS 频率合成的基本原理是使用稳定的参考时钟源作为抽样时钟,通过地址累加来寻址波形查找表得到波形的幅度抽样值,然后将抽样值经D/A 转换和低通滤波输出平滑的波形。

图1.1给出了DDS 的工作原理框图。

相位累加器波形查找表DAC低通滤波器系统时钟K频率控制字NN Hf0图1.1 DDS 基本原理框图图1.1中相位累加器(N 为位数)以频率控制字K 为间隔对地址进行累加,将累加结果的最大有效位数H 作为ROM 查找表的地址(ROM 中存储波形数据),通过D/A 转换将所查地址单元的波形数据转化为模拟量,再由低通滤波器滤出其基波成分。

低频数字相位(频率)测量的CPLD实现

低频数字相位(频率)测量的CPLD实现在电子测量技术中,测频测相是最基本的测量之一。

相位测量仪是电子领域的常用仪器,当前测频测相主要是运用等精度测频、PLL 锁相环测相的方法。

研究发现,等精度测频法具有在整个测频范围内保持恒定的高精度的特点,但是该原理不能用于测量相位。

PLL 锁相环测相可以实现等精度测相,但电路调试较复杂。

因此,选择直接测相法作为低频测相仪的测试方法[1、2、3、4]。

设计的低频测相仪,满足以下的技术指标:a .频率20-20KHz;b .输入阻抗≥100KΩ;c.相位测量绝对误差≤1 度; d.具有频率测量和数字显示功能;e.显示相位读数为0 度--359 度。

1 系统工作原理系统工作原理如单片机和CPLD 的数据采用独立接口方式,这样设计比较灵活,可以不受单片机总线时序的影响。

由ADD[0..2]进行控制,分别读取测频测相计数器中的19 位数据,并存于单片机中,进行后续的计算。

单片机完成数据的运算后,将所得数据转化为10 进制,送到显示板进行显示。

显示板共有8 个数码管,其中,前5 位用于显示频率(最大为20000Hz),后三位显示相位(最大为359 度)。

在CPLD 设计中,根据计算,选取测频、测相计数器长度均为19 位,在标频信号为10MHz 时,相位测量精度小于1 度。

若只用89C51,其自带的计数器只有16 位,且不易同时实现测频测相的功能。

故选用CPLD 实现其测频测相的计数功能,并设计了独立的数据接口,以便与单片机交换数据[5、6]。

2 CPLD 测频测相模块工作原理。

【电子设计】低频数字式相位测量仪制作报告

低频数字式相位测量仪制作报告摘要本系统由低频数字相位频率测量仪,输入移相网络和数字式移相信号发生器组成。

利用CPLD,单片机控制模块实现了高精度的频率相位测量。

数字式移相信号发生器采用直接数字频率合成(DDFS)技术,输出频率范围宽,控制精度高。

由于在DDFS系统中采用了双D/A输出形式,信号幅度采用数字调节方式,输出信号幅度稳定。

移相网络的输入采用了自动增益控制(AGC),实现了高达48dB的宽范围输入,实现信号的自动稳幅输出。

此外,本系统友好的人机界面,合理实用的功能扩展,使整个系统更利于实际使用。

一.方案设计与论证1.相位频率测量部分方案一:对输入的两路正弦信号分别进行过零比较,并对生成的两路方波信号进行异或运算,得到占空比与相位差成正比的脉冲信号。

将该正弦送入单片机系统,对信号的脉宽进行测量,经计算得到输入的两路正弦信号的相位差。

单片机系统直接对过零比较后的方波信号计数,得到输入信号频率。

经单片机系统处理后,显示测量结果。

此方案电路相对简单,容易实现,但是受到单片机工作速度的限制,精度不高。

方案二:对输入的两路正弦信号分别进行过零比较,并对生成的两路方波信号进行异或运算,得到占空比与相位差成正比的脉冲信号。

由CPLD对相位差脉冲信号和频率信号进行计数,将计数结果送入单片机,单片机经过简单计算后显示测量结果。

此方案可以提高系统的测量精度,单片机要实现的功能相对简单,可以实现友好的人机界面。

缺点是电路相对复杂,成本较高。

系统框图详见图2-1。

综合考虑,这里采用了方案二。

2.移相网络部分方案一:直接采用题目中提供的参考电路。

此电路实现简单,但对于不同幅度的输入信号,不能做到自动稳幅输出。

对于小信号输入,无法满足题目输出峰-峰值0.3~5V的要求,除非采用可变增益放大器,在没有单片机控制的情况下,显然带来诸多不便。

方案二:以题目中提供的参考电路为基础,在信号输入前端加入自动增益控制电路(AGC),以适应各种幅度的信号输入。

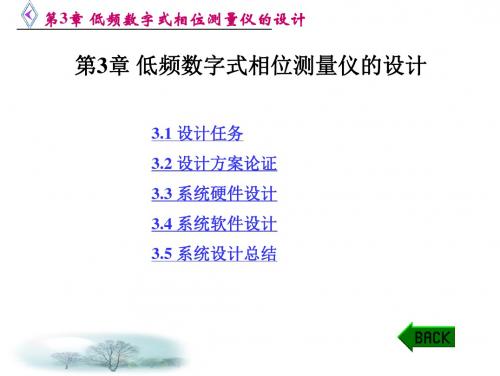

第3章+低频数字式相位测量仪的设计

图3.3 用测周期的方法获得信号频率

第3章 低频数字式相位测量仪的设计

2) 鉴相器就是异或门,在鉴相器的输出波形IV中, 正脉冲宽度就是要测量的I和V 相位差所对应的时间差 Tθ ,如图3.4所示。

第3章 低频数字式相位测量仪的设计

I V

IV

图3.4 鉴相器的输入、输出波形图

第3章 低频数字式相位测量仪的设计

F INT1(P 3.3)

图3.6 MCU测量时间差、周期的电路图

第3章 低频数字式相位测量仪的设计

(2) 时序图如图3.7所示。需要说明的是,由软 件创建一标志位2FH.1,当输入引脚P3.6=0时,CPU置 位标志位2FH.1,而当P3.6=1时,CPU在读取时间差数 据后清零标志位2FH.1。

第3章 低频数字式相位测量仪的设计

2) (1)电路图如图3.6所示,该电路由单片机、整 形电路、门电路等组成。由定时器/计数器T0、T1分别 测量周期、时间差。

第3章 低频数字式相位测量仪的设计

待测信号 1 待测信号 2

A

D

整形 电路

2分 频

=1 C

&

整形 电路 B

MCU -51 INT0(P 3.2) ≥1 E P3.6

SUB1入 口 R4=4(R4是计 数器 )

P3.6= 1?

N

Y

2FH.1= 1?

N

Y

R4= 4?

Y

N

保存 周期 TH0、TL0 保存 时间 差 TH1、TL1

SETB 2FH.1

清零 定时 器 T0、T1 清0标志 位 2FH.1

R4- 1送 R4

N

R4= 0?

Y SUB1出 口

低频数字式相位测量仪

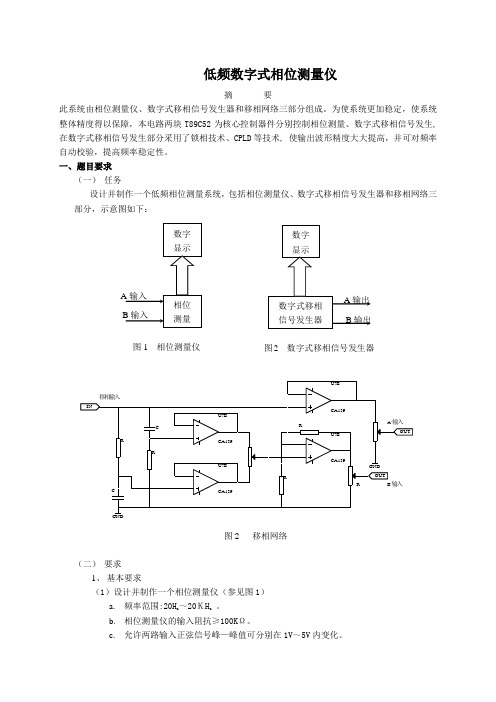

低频数字式相位测量仪摘 要此系统由相位测量仪、数字式移相信号发生器和移相网络三部分组成。

为使系统更加稳定,使系统整体精度得以保障,本电路两块T89C52为核心控制器件分别控制相位测量、数字式移相信号发生,在数字式移相信号发生部分采用了锁相技术、CPLD 等技术, 使输出波形精度大大提高,并可对频率自动校验,提高频率稳定性。

一、题目要求(一) 任务设计并制作一个低频相位测量系统,包括相位测量仪、数字式移相信号发生器和移相网络三部分,示意图如下:图2 移相网络(二) 要求1、 基本要求(1)设计并制作一个相位测量仪(参见图1)a. 频率范围:20H z ~20KH z 。

b. 相位测量仪的输入阻抗≥100K Ω。

c. 允许两路输入正弦信号峰—峰值可分别在1V ~5V 内变化。

图1 相位测量仪图2 数字式移相信号发生器d.相位测量绝对误差≤2°e.具有频率测量及数字显示功能.f.相位差数字显示:相位读数为0°~359.9°,分辨率为0.1°。

(2)参考图2制作一个移相网络a.输入信号频率:100H z、1KH z、10KH z。

b.连续相移范围:—45°~+45°。

c.A¹、B¹输出的正弦信号峰—峰值可分别在0.3V~5V内变化。

2、发挥部分(1)设计并制作一个数字式移相信号发生器(图3),用以产生相位测量仪所需的输入正弦信号,要求:a.频率范围:20H z~20KH z,频率步进为20H z,输出频率可预置。

b.A、B输出正弦信号峰—峰值可分别在0.3V~5V内变化。

c.相位差范围0°~359°,相位差步进为1°,相位差可预置。

d.数字显示预置的频率、相位差值。

(2)在保持相位测量仪测量误差和频率范围不变的条件下,扩展相位测量仪输入正弦信号峰—峰值至0.3V~5V范围。

(3)用数字移相信号发生器校验相位测量仪,自选几个频点、相位差值和不同幅度进行校验。

毕业设计论文《低频数字式相位测量仪》

毕业设计论文《低频数字式相位测量仪》摘要该数字式相位测量仪以单片机 (89c52) 为核心 , 通过高速计数器 CD4040 为计数器计算脉冲个数从 , 而达到计算相位的要求 , 通过 8279 驱动数码管显示正弦波的频率,不采用一般的模拟的振动器产生 , 而是采用单片机产生 , 从而实现了产生到显示的数字化 . 具有产生的频率精确 , 稳定的特点 . 相移部分采用一般的 RC 移相电路 , 节省了成本。

一方案论证与比较 :1 常见正弦信号的测量方法 :方案一:采用模拟分离元件如二极管,三极管等非线性元件,实现频率的测量,检相的功能,使用起来方便,价格便宜,但采用分离元件由于分散性太大,不便于集成及数字化,而且测量误差大。

方案二:采用集成的检相器,检频器实现频率及相位的测量。

这种方法的实现框图如下:这种方法虽然可实现比较精确的测量,但由于模拟信号易受外界的干扰,不易调节,无法实现智能化,数字化的缺点,一般在要求较低的情况下使用。

方案三:此方案采用高速信号发生器产生 20MHz 的高频信号,其主要特点是采用 CD4040 高频计数器结合单片机,利用计数脉冲实现测量相位与频率的目标。

这种方法克服了模拟电路的缺点,实现了数字化与集成化。

本设计采用了这种方法。

这种方案的组成框图:二系统总体设计按照题目要求,我们设计的相位测量系统包括三部分:正弦波产生系统(包括频率调整电路),移相电路和相位显视系统,其总体框图如下:三各部分硬件电路设计及参数计算1、正弦波产生电路•方案一:利用 8038 芯片或 MAX038 可以实现压控的函数发生器通过改变少量的外围元件,可实现正弦波,方波,三角波,并可实现频率调节,但采用模拟器件由于元件分散性太大,即使使用单片函数发生器,参数也与外部元件有关,外接的电阻,电容对参数影响很大,因而产生的频率稳定度差,精度低,抗干扰能力差,调节困难,成本也高。

而且灵活性差,不能实现智能化。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

包括数字移相信 号发生 器和相位 测量仪 2 部分 , 分别 完成移相信号的发生 、 频率 与相位差 的预置、 数字显示、 号的移相 以 信

及移相后信 号相位差和频率 的测量 与相识 等功能。 中数字 式移 相信号发生 器可 以产 生预置频率 的差值 ; 其 相位 测量仪可

以测量和显 示相位信 号的频率 、 位 差。 相

厂一

后, 将波形整形电路的2 0 ] 厂 厂 厂 厂 ] ]

图 1 波形变换 示意 图

的功能, 用以产生相位测量仪所需的输入正弦信号 。 其

技术 要 求 指标 : 率 范 围2 Hz~ 0 Hz 频 率 步进 为 频 0 2k ,

2H , 0 z 输出频率可预置; 相位差范围为0 3 9 , ~ 5 。相位差

( 具有设定保存功能。 5)

实现相位 、 频率的测量, 并且具有独 自的控制功能和数

字显示 功能。

11系统硬件 结构 .

首 先 将 被 测 2列 正

弦 信号 A 、 B经平 滑 滤 波

后 , 入 过 零 比较 电路 , 输

A

1系统硬件设计

总体要求 : ( ) 有相 位 测量 功 能 , 1具 即相 位 测量 仪 的 功 能 。 其

传 感 及 检 测 仪 表

C L 低频 数 字 相 位 测 量 仪 的设 计 PD

朱 红梅 , 美 君 潘

( 海西部矿 业铅业 摘

要: 绍 了一种基 于复杂的可编程逻辑 器件( L 和 高速 单片机s c8 c 8 介 CP D) T 9 5 的低频数字 相位 测量仪 。 该测量仪

京航 天航 空 大 学 出版 社 【] 白英 彩 . 型 计 算 机 常 用 芯 片 手 册 【 . 海 : 海科 学 3 微 M】 上 上

技 术 出版 社

2软件部分设计

系统采用硬件描述语言VH L D 和MC 一1 S5 单片机汇

编语言, 采用 模块 化 程 序设 计 , 要 由数 字 式移 相 信 号 主 发 生 器 波 形 产 生 程 序 、 形 发生 幅 度 控 制 子 程 序 、 波 键

参 考 文 献

器 的 自动 扫描 , 别 闭合 建 的 建号 , 成 显示 器 的 动态 识 完 显 示 , 以节 省 CP 可 U处 理 键盘 和 显示 器 的 时 间 , 高 提 C U的工 作效率 。 P

() 3键盘设置: ~ 数字键; 一 0 9 A 频率输入; 一 B频率步进;

而通过D 0 3 的置数控制波形输出的幅度, 1 0 AC 8 2 MC 4 3 为基准源, 为DA 0 3 提供基准电压。 C 82 这样可以提高信

号 幅 度 的 稳 定性 。 形 发 生结 构 图 如 图4 示 。 波 所

N P ; IC D H 判断指针的高位字节R 是 1 否为1若是, P 加1 , 则D H 取出正弦波D C A 数据

I

0RG 8 0 H 10

S TART: M OV

S ,6 H P# 0

MO R 加 ; V 定义指 向正弦波D c A 数据 的指针, 因为 有3 6 个数 据, 1 所以用 了R和R 。 两个寄存器 。

M 0V R1 0 L OOP M OV A, : R0 M OV DVI , S N- R # I DAT A CJ NE R1 # , f Ⅳ_ T , 1 I0、 AB

Z UH n- i A H og , NMej meP in - u (edn ut Bac oQnhi s rMi n C . t, unzog 160C i ) 1a I sy r h f i aWetn n g o Ld H aghn 8 10 , h a d r n g e i , . n

c ng n r t i a ewi p e o c  ̄ x fe ue c ndt a e eaeasnw v h t rc n e lrq n ya wowa e v swi pe o c re haedfee c .t a o t u u l h n in l h s - h t rc n e tdp s i rn e I c nc ni o syc a gsg a p a e n

自动化应用 2 1 9期 00

6 3

[ 谢 宜仁. 片机实用技术 问答【 . 4 】 单 M] 北京: 民邮 电出版社 人 [】 刘必 虎 . 小 规模 集 成 电路 的 原 理 与应 用 【 . 海 : 5 中 M】 上 上

海科 技 出版 社

【] 付 家 才 .DA原 理 与应 用 【 . 京 : 学 工 业 出版 社 6 E M]北 化

作者简介: 朱红梅 1 , 事工厂 电气 <9 ) 8 从 维修工作。

收稿日期:0 0 80 2 1- —3 0

12单 元电路设 计 .

() 1 数字移相原理: 将所需 的正弦波量化存人高速

6 、 ̄ ^f uo a pyc m 2 、 ^a t —p l o i自动化应用 ^. .

A sr ̄ T e a e it d c s l wf q e c h s me s rn ty tm whc ae n L e h oo ya dSn l C i bl a h p p r n r u e a o r u n yp ae a ue  ̄n s s o e e ihb sdo CP Dt n lg n ige hpMirc mp tr c co o ue S C8 C5 .hss s m i ma eu fwop r ,n s in l e ea r dteo e i p a e a u me t d l. h g a g n rtr d l T 9 8T i t s d po t ye at o ei s a g n rt a h t r s h s me s r n mo ue T es n l e eao mo ue s g on h i

传 感 及 检 测 仪 表

盘/ 显示处理子程序 、 位测量仪 子程序 、 相 中断服务 子 程序 、 运算控制子程序 和主程序组成 。 波形发生器程序

流程 图如 图5 示 。 所

CLKl

CL K 2

74 6 F8

LK 。

—

A

2

7 4F7 4

B

3

图 2 波形变换 电路 图

各个领域, 对相位测量的要求也逐步向高精度、 高智能 化方向发展。 在低频范围内, 相位测量在电力机械等部

门有 着尤其重要 的意义, 通过采 用P O E 、 X+ I S R T L MA PU

I等工具, I 完成 了系统相位测量仪 、 数字移相信号 发生

2 部分 的功 能 , 其 能 够 自动 产 生 正 弦信 号 , 使 同时 可 以

K y rs p aemesrme trq e c— a ue n;ige hpmi o o ue; LD e wod : h s- aue n;e un ymesrmets lc i c c mp t , f n r r CP

U 引 吾 随着 相 位 测量 技 术广 泛 应 用于 国 防 、 研 、 科 生产 等

表, 显然不能够满足所需的精度要求。 随着 电子技术 以 及微机技术 的发展 , 字式仪 表因其高精度 的分辨率 数

以及高度 的智能化 、 观化 的特 点得 到越来越广 泛的 直

应用 。 本方 案基 于复杂 的C L P D和高速 单片机S C 9 5 , T 8C 8 与 常用 的方法 相 比, 好地 解 决 了在 高 频 时精 度 低 、 较 易 受干扰 的问题 。

3 结语

对 于 低频 相位 的 测量 , 传统 的模 拟指 针式 仪 用

图 4 波 形 发 生 结 构 图 ( 数 字 移相 信 号 发生器 键盘 显示 电路 : 用键盘 2) 通 显 示 电路 采用 I tl 司生 产 的通 用 可编 程 键盘 和显 示 ne公

电路 的接 口电路芯 片 8 9 , 2 7 以实 现对 键盘 和显示 2 789 可

关键词 : ga 量 ; , 频率测量 ; l 单片机; L CP D

D sg f o F e u n y Ph s a u e n y t m a e nCPL e ino L w r q e c a e Me s r me t se B s d o a S D

2 所示 。 为了判断输 出的 2 方波 波形超前 或滞 列 路输 出方 波送人D触发

器 进 行 极 性 判 别 , 后 然

广] 厂]

厂]

显示, 相位读数为0 3 9 。分辨率为01 。 ~5 . , 9 .。

( 具 有 信号 发 生功 能 , 2) 即数 字 式移 相信 号 发生 器

CPLD

89 C51

单 片 机

图 5 波 形 发 生 器 程 序 流 程

频 率 相 位

显 示

波 形 产 生部 分 程 序 如 下 :

A 54 E U 6 0H D72 Q 00

0RG 8 0 H 00

基 准频 率

I

图 3 系 统 硬 件 结构 S C 9 5 单 片机 , T 8C 8 然后访 问存 储器地 址 , 用时 间差产 利 生2 列具 有 相 位差 的阶梯 波 , 经D/ 换 后滤 波 整 形 再 A转 输 出 。 A 0 3 的输 出电压 为A 4 2 D C 82 D7 5 提供基 准 电压 , 从

si hf tAn h h s me s rme t d l h s efn t no me s r ga dd s l igtes n l h s n p aedfee c o t os g a . dtep a e a u e n mo ue a t u ci f a u n n ipa n h g a p aea d h s i rn e f h o i y i w n n l i s