应用8051单片机IP设计相位测量仪

数字式相位差测量系统(基于51单片机)

数字相差检测仪的制作专业:电气班级:XX班学号:XXXXXXXXXX 学生姓名:XXX指导教师:XX目录摘要: ............................................................................................................... 错误!未定义书签。

Abstract: ............................................................................................................. 错误!未定义书签。

第一章绪论. (5)1.1 测量相位差的作用和意义 (5)1.2 相位差测量的研究现状 (5)1.3本课题研究的主要内容 (7)第一章:最小二乘法以及快速傅里叶变换简介 (8)1.1:最小二乘法简介 (8)2.1 主程序流程图 (12)2.2位倒序算法实现 (12)2.4 FFT算法的实现 (13)2.5 AD采样的使用 (14)2.6 定时器的使用 (15)第三章:硬件电路设计 (17)3.1 移相电路的设计 (17)3.2 电压跟随器模块 (17)3.4 电源电路 (18)3.4.1 变压器简介 (18)3.4.2 单相全桥整流电路 (19)结论 (20)致谢 ................................................................................................................... 错误!未定义书签。

参考文献(Reference).. (21)附录: (22)基于最小二乘法的低频数字相位差检测仪的研究摘要:常见的相位差检测方法一般是过零法,通过外部硬件电路对正弦信号的零点进行检测,产生的脉冲信号出发MCU的外部中断,通过MCU的定时器计算出信号的频率以及相位差。

基于8051单片机IP软核的优化设计及应用研究

speed,the program flow concept is

introduced and

instructions

applied.This refer to arithmetic

and log沁instructions,data

transfer

and

bit addressable instructions,To prove the possibility simulator. into FPGA

专用集成电路asicapplicationspecificintegratedcircuit的设计成本不断降低在功能上现代的集成电路已能实现单片电子系统socsystemonachip的功能810edaelectronicdesignautomation技术作为现代电子设计技术的核心它依赖功能强大的计算机在eda工具软件平台上对以硬件描述语言hdlhardwaredescriptionlanguage为系统逻辑描述手段完成的设计文件自动地完成逻辑编译逻辑化简逻辑分割逻辑综合结构综合布局布线以及逻辑优化和仿真测试直到实现既定的电子线路系统功能

and

SoC

based

on

8 bit

MCU

Key words:MCS一8051,SOC,FPGA,IP core

JV

西华大学硕七学位论文

申明

本人申明所呈交的学术论文是本人在导师指导下进行的研究工作及取得 的研究成果。除了文中特别加以标注和致谢的地方外,论文中不包含其他人已 经发表或撰写过的研究成果,也不包含为获得西华大学或其他教育机构的学位 或证书而使用过的材料。与我一同工作的同志对本研究所做的任何贡献均已在 论文中作了明确的说明并表示谢意。 本学位论文成果是本人在西华大学读书期问在导师指导下取得的,论文成 果归西华大学所有,特此申明。

基于FPGA和8051单片机IP核的多功能频率计的设计与实现

基于FPGA和8051单片机IP核的多功能频率计的

设计与实现

频率是电信号中重要的物理量,在电子、通信系统中,信号的频率稳定度决定了整个系统的性能,准确测量信号的频率是系统设计的重要内容。

单片机广泛地应用于电子系统设计,其性价比高,大量的外围接口电路,使基于单片机的电子系统设计方便,周期缩短。

然而,单片机的串行工作特点决定了它的低速性和程序跑飞,另外还存在抗干扰能力不强等缺点。

EDA(Electronic Design AutomaTIon)技术以计算机为工具,在Quartus II软件平台上,对以硬件描述语言Verilog HDL/VHDL为系统逻辑描述手段完成的设计文件,自动地完成逻辑编译、化简、综合及优化、逻辑仿真,直至对特定目标芯片的适配、编译、逻辑映射和编程下载等工作,FPGA是纯硬件结构,具有较强的抗干扰能力。

文中在FPGA芯片中嵌入MC8051 IP Core,作为控制核心,利用Verilog HDL语言进行编程,设计了以MC8051 IPCore为核心的控制模块、计数模块、锁存模块和LCD显示模块等模块电路,采用等精度测量法,实现了频率的自动测量,测量范围为0.1 Hz~50 MHz,测量误差小于0.01%。

基于单片机的相位测量仪电路设计(完整版)

相位测量仪是电力部门、工厂和矿山、石油化工、冶金系统进行二次回路检查的理想的高精度仪表。尤其适用于电能计量、用电检查、继电保护、差动检测、电力建设和变送电工程等。是电力系统各部门的必备仪器之一。

1.1

在电子测量技术中,相位测量时最基本的测量手段之一,相位测量仪式电子领域的常用仪器。随着相位测量技术广泛应用于科学研究、实验、生产实践等各个领域,对相位测量技术的要求也向高精度高智能化方向发展,在低频范围内,相位测量在电力、机械等部门具有非常重要的意义。

矢量法:任何一个正弦函数都可以用矢量来表示,如各个正弦信号幅度相等、频率相同,运算器运用减法器合成得到矢量的模 .矢量法用于测量小角度范围时,灵敏度较好,可行度也较高;但在180°附近灵敏度降低,读数困难且不准确.由于系统输出为一余弦或正弦函数,因此这种方法适用于较宽的频带范围。

上述3种测量相位的方法各有优势,从测量范围、灵敏度、准确度、频率特性和谐波的敏感性等技术指标来看,过零检测法的输出正比于相位差的脉冲数,且易于实现数字化和自动化,故本研究采用过零检测法。

XTAL1:反向振荡放大器的输入及内部时钟工作电路的输入。

XTAL2:来自反向振荡器的输出。

振荡器特性:XTAL1和XTAL2分别为反向放大器的输入和输出。该反向放大器可以配置为片内振荡器。石晶振荡和陶瓷振荡均可采用。如采用外部时钟源驱动器件,XTAL2应不接。有余输入至内部时钟信号要通过一个二分频触发器,因此对外部时钟信号的脉宽无任何要求,但必须保证脉冲的高低电平要求的宽度。

第

本设计中,相位测量仪主要是对被测网络的输入、输出信号的相位差进行测量。这样的两路待测信号为同频不同相的正弦交流信号,频率范围为20Hz-20kHz,幅度为0V~500V。相位差测量的基本原理为:对信号波形的变换、比较及相关数学运算。即对于被测信号是同频不同相的两路正弦交流信号,为了准确地测量出该相位差,需要对输入信号的波形进行整形,本设计利用LM339组成整形电路,使输入信号变成矩形波信号,再经异或门组成的鉴相器电路,输出即为相位差信号,再结合单片机的数据处理功能,最后通过液晶即可显示出该相位差。由于单片机的工作电压在5V左右,所以在进行相位测量前,还需将被测信号进行分档降压处理。

基于8051IP核的便携式超声波测厚仪设计

基于8051IP核的便携式超声波测厚仪设计牟光臣;石新峰【摘要】介绍了超声波测厚仪的应用场合,分析了超声波测厚仪的基本原理和工作过程,并提出了利用8051IP核,在FPGA芯片上实现超声波测厚控制电路的方法.文中阐述了该系统的工作原理、硬件电路构成和软件系统设计,实现了一教高集成化、低功耗的便携武超声波测厚仪的设计.【期刊名称】《河南机电高等专科学校学报》【年(卷),期】2012(020)006【总页数】3页(P14-16)【关键词】超声波测厚仪;8051IP核;FPGA;便携式【作者】牟光臣;石新峰【作者单位】河南机电高等专科学校电子通信工程系,河南新乡453000【正文语种】中文【中图分类】TP332超声波测厚仪携带方便,操作简单,精度较高,可以快捷而准确地测量各种结构均匀的金属材料和非金属材料的厚度。

尤其对于锅炉、压力容器和管道等只有一个侧面可以接触的测量对象,具有更大优越性。

利用超声波测厚仪构成的集总式检测系统,对工业企业的锅炉、压力容器和各种管道的厚度进行在线实时检测,了解其局部腐蚀、锈蚀的情况,并及时发出警报信息,对设备安全运行有着极大作用。

1 超声测厚仪工作原理超声波测厚仪有脉冲式、共振式、兰姆波式等多种类型。

目前广泛采用的是脉冲反射式。

脉冲反射式超声测厚仪的工作原理及工作过程如下:1)由微处理器触发超声脉冲发生器开始工作,产生超声脉冲,脉冲频率一般应该在40KHz以上,并激发超声探头产生(一般采用一体化探头)超声波,即时开始超声发射。

控制脉冲发生器的工作时间,保证每次发射8~15个周期。

2)超声波通过被测介质传输至材料分界面。

3)超声波脉冲在分界面处被反射。

回波被一体化探头接收到。

4)接收电路对回波信号进行多次滤波及放大,并截取第一次回波信号的峰值,变成数字信号传输至高速计数器。

5)周期固定的高速计数器自发出超声脉冲序列时开始进行高速计数,当接收到回波有效信号时结束计数。

即可得到超声波在介质中的渡越时间。

应用8051单片机IP设计相位测量仪

70科技资讯 SC I EN C E & TE C HN O LO G Y I NF O R MA T IO N工 业 技 术相位差测量技术发展至今已深入到电子技术、工业自动化、智能控制及通信等众多领域。

因此,设计一个高精度的相位差测量仪显得十分重要。

当前国内的一般的解决方案是单片机+F P G A 方案,其中F P G A 完成高速的脉冲计数功能,而单片机则进行脉冲计数后的有关计算和LC D显示等的控制。

此方案中的FPGA内部资源往往利用不足,造成比较大的浪费。

本设计应用SOPC和8051单片机IP技术,通过在FPGA中嵌入8051单片机IP来取代单片机+FPGA方案中的实际的单片机。

既少用一个实际的单片机又充分利用FPGA内部资源,大大节省了硬件的成本。

1 8051单片机IP核简介常见的8051单片机IP有开源免费的和工业级收费的两类,一般都具有以下特点。

(1)指令系统与8051单片机完全兼容,硬件部分也基本相同,时钟频率可比传统的8051单片机要高。

(2)8051单片机IP core一般无内部ROM 和R A M ,所有程序R O M 和内部R A M 都必须外接。

用F P G A 实现时,可使用F P G A 片内R O M 、R A M 资源实现。

(3)输出与输入(I/O)口是分开的。

如果需要使用双向口功能,必须外接一些电路才能实现。

(4)单片机程序可使用普通8051单片机程序编译器生成单片机HE X程序代码,再在F P G A 的E D A 开发平台下下载到充当程序R O M 的F P G A 片内R O M 以供使用。

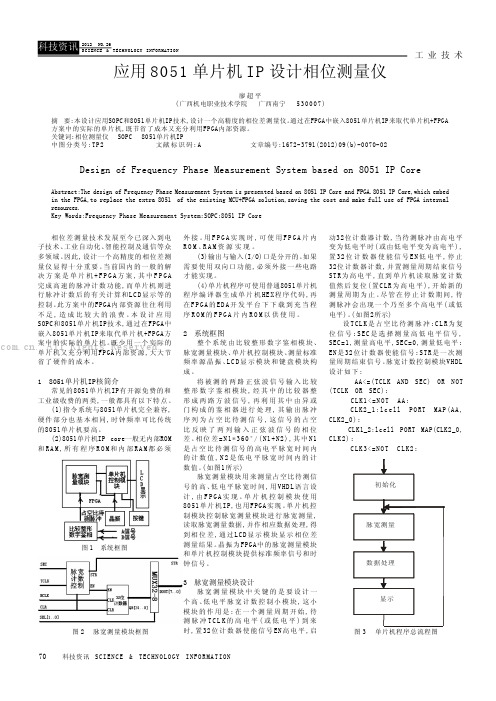

2 系统框图整个系统由比较整形数字鉴相模块、脉宽测量模块、单片机控制模块、测量标准频率源晶振、L C D 显示模块和键盘模块构成。

将被测的两路正弦波信号输入比较整形数字鉴相模块,经其中的比较器整形成两路方波信号,再利用其中由异或门构成的鉴相器进行处理,其输出脉冲序列为占空比待测信号,这信号的占空比反映了两列输入正弦波信号的相位差。

基于8051单片机的相位差测试仪的研究设计

基于8051单片机的相位差测试仪的研究设计摘要提出了一种基于8051 单片机开发的低频数字相位差测量仪的设计。

系统以单片机8051 及计数器,显示管为核心, 构成完备的测量系统。

可以对1Hz~1000Hz 频率范围的信号进行频率、相位等参数的精确测量, 测相绝对误差不大于1°采用数码管显示被测信号的频率、相位差。

硬件结构简单, 程序简单可读写性强,软件采用汇编语言实现, 效率高。

与传统的电路系统相比, 其有处理速度快、稳定性高、性价比高的优点。

关键词: 相位差;单片机;计数器;数码显示管Designs of Low frequency Digital Phase Measurement Based on Single ChipAbstractA new kind of low - frequency digital phase measurement instrument is residented which is based on 8051.This is a complete system whose core is based on single chip 8051 and arithmometer and charactron. It may measure the frequency and phase of the signal which begin from 1 Hz to 1000Hz, absolute error is not more than 1° The data are displayed on numeral displayer. Hardware structure is simple and software is realized by compiling language. Compared with traditional circuit, it has many advantages of faster processing speed, good stability and high ratio between property and price.Keyword: phase difference; single-chip computer;. Arithmometer;charactron tube目录第一章绪论 (3)1.1背景介绍 (3)1.2本设计的内容要求及方法 (4)第二章小信号处理的构成及基本原理 (4)2.1信号处理模块 (5)2.2.1数字式相位测量仪 (5)2.2.2.移相网络 (6)2.2.3信号发生器 (7)2.3方案细化 (8)2.3.1、数字式相位测量仪 (8)2.3.2信号发生器 (9)2.4原理图分析及各参数设置 (10)第三章计数部分的构成和原理 (11)3.1测相部分 (11)3.1.1测相原理 (11)3.1.2电路结构 (12)3.2测频部分 (12)3.2.1测频原理 (12)3.2.2电路结构 (13)3.3程序编写 (16)3.4输出显示部分 (18)第四章模拟仿真及结论 (20)4.1仿真工具的选择 (20)4.2电路仿真操作步骤 (20)4.3仿真波形分析 (21)第五章原理误差分析235.1小信号部分的误差 (23)5.2频率测量模块的误差 (23)5.3相位测量模块的误差 (23)附录 (25)设计回顾,收获及心得体会 (30)感谢辞 (31)参考文献 (32)第一章绪论1.1背景介绍在实际工作中,经常会遇到需要检测两个信号之间的相位差,这也是研究网络相频特性中不可缺少的重要方面。

基于FPGA的低频数字相位测量仪的设计

1引言关于低频数字相位测量系统的设计与实现方法,提出了以单片机最小系统和复杂可编程逻辑芯片为核心的电路设计模型。

相位的数字测量方法基本分为硬件电路测量与A/D采样后利用软件计算两种。

硬件法测量由于电路结构比较复杂,易受外界干扰影响以及准确度较差的缺点,限制了其作用进一步发挥。

近年来,随着计算机硬件及其外围设备的日益发展,以数字信号处理为核心的软件法测量技术在相位差的测量中得到了越来越多关注,并且得到了较快发展。

同频率正弦信号间的相位差测量在电工技术、工业自动化、智能控制及通讯、电子等许多领域都有广泛的应用,如电工领域中的电机功角测试,介质材料的损耗角的确定等。

因此相位差测量有着广泛的实用价值。

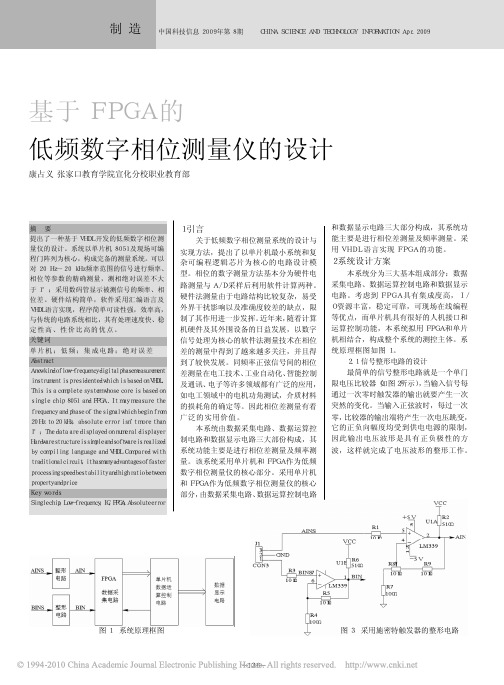

本系统由数据采集电路、数据运算控制电路和数据显示电路三大部份构成,其系统功能主要是进行相位差测量及频率测量。

该系统采用单片机和FPGA作为低频数字相位测量仪的核心部分。

采用单片机和FPGA作为低频数字相位测量仪的核心部分,由数据采集电路、数据运算控制电路基于FPGA的低频数字相位测量仪的设计康占义 张家口教育学院宣化分校职业教育部图1 系统原理框图图3 采用施密特触发器的整形电路和数据显示电路三大部分构成,其系统功能主要是进行相位差测量及频率测量。

采用VHDL语言实现FPGA的功能。

2系统设计方案本系统分为三大基本组成部分:数据采集电路、数据运算控制电路和数据显示电路。

考虑到FPGA具有集成度高,I/O资源丰富,稳定可靠,可现场在线编程等优点,而单片机具有很好的人机接口和运算控制功能,本系统拟用FPGA和单片机相结合,构成整个系统的测控主体。

系统原理框图如图1。

2.1 信号整形电路的设计最简单的信号整形电路就是一个单门限电压比较器(如图2所示),当输入信号每通过一次零时触发器的输出就要产生一次突然的变化。

当输入正弦波时,每过一次零,比较器的输出端将产生一次电压跳变,它的正负向幅度均受到供电电源的限制,因此输出电压波形是具有正负极性的方波,这样就完成了电压波形的整形工作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

应用8051单片机IP设计相位测量仪

摘要:本设计应用SOPC和8051单片机IP技术,设计一个高精度的相位差测量仪。

通过在FPGA中嵌入8051单片机IP来取代单片机+FPGA方案中的实际的单片机,既节省了成本又充分利用FPGA内部资源。

关键词:相位测量仪SOPC 8051单片机IP

Abstract:The design of Frequency Phase Measurement System is presented based on 8051 IP Core and FPGA.8051 IP Core,which embed in the FPGA,to replace the extra 8051 of the existing MCU+FPGA solution,saving the cost and make full use of FPGA internal resources.

Key Words:Frequency Phase Measurement System;SOPC;8051 IP Core

相位差测量技术发展至今已深入到电子技术、工业自动化、智能控制及通信等众多领域。

因此,设计一个高精度的相位差测量仪显得十分重要。

当前国内的一般的解决方案是单片机+FPGA方案,其中FPGA完成高速的脉冲计数功能,而单片机则进行脉冲计数后的有关计算和LCD显示等的控制。

此方案中的FPGA内部资源往往利用不足,造成比较大的浪费。

本设计应用SOPC和8051单片机IP技术,通过在FPGA中嵌入8051单片机IP来取代单片机+FPGA方案中的实际的单片机。

既少用一个实际的单片机又充分利用FPGA内部资源,

大大节省了硬件的成本。

1 8051单片机IP核简介

常见的8051单片机IP有开源免费的和工业级收费的两类,一般都具有以下特点。

脉宽测量模块用来测量占空比待测信号的高、低电平脉宽时间,用VHDL语言设计,由FPGA实现。

单片机控制模块使用8051单片机IP,也用FPGA实现。

单片机控制模块控制脉宽测量模块进行脉宽测量,读取脉宽测量数据,并作相应数据处理,得到相位差,通过LCD显示模块显示相位差测量结果。

晶振为FPGA中的脉宽测量模块和单片机控制模块提供标准频率信号和时钟信号。

3 脉宽测量模块设计

脉宽测量模块中关键的是要设计一个高、低电平脉宽计数控制小模块,这小模块的作用是:在一个测量周期开始,待测脉冲TCLK的高电平(或低电平)到来时,置32位计数器使能信号EN高电平,启动32位计数器计数,当待测脉冲由高电平变为低电平时(或由低电平变为高电平),置32位计数器使能信号EN低电平,停止32位计数器计数,并置测量周期结束信号STR为高电平,直到单片机读取脉宽计数值然后复位(置CLR为高电平),开始新的测量周期为止。

尽管在停止计数期间,待

测脉冲会出现一个乃至多个高电平(或低电平)。

(如图2所示)

设TCLK是占空比待测脉冲;CLR为复位信号;SEC是选择测量高低电平信号,SEC=1,测量高电平,SEC=0,测量低电平;EN是32位计数器使能信号;STR是一次测量周期结束信号。

脉宽计数控制模块VHDL 设计如下:

AA<=(TCLK AND SEC) OR NOT(TCLK OR SEC);

CLK1<=NOT AA;

CLK2_1:lcell PORT MAP(AA, CLK2_0);

CLK1_2:lcell PORT MAP(CLK2_0, CLK2);

CLK3<=NOT CLK2;

Q1<=Q10;

Q2<=Q20;

BB<=Q2&Q3;

LL1:PROCESS(CLK1,CLR)

BEGIN

Q10<=&acute;0&acute;;

ELSIF CLK1&acute;EVENT AND CLK1=&acute;1&acute;THEN

Q10<=&acute;1&acute;;

END IF;

END PROCESS;

LL2:PROCESS(CLK2,CLR)

BEGIN

IF CLR=&acute;1&acute;THEN Q20<=&acute;0&acute;;

ELSIF CLK2&acute;EVENT AND CLK2=&acute;1&acute;THEN Q20<=Q10;

END IF;

END PROCESS;

LL3:PROCESS(CLK3,CLR)

BEGIN

<=&acute;0&acute;;

ELSIF CLK3&acute;EVENT AND CLK3=&acute;1&acute;THEN Q3<=Q20;

END IF;

END PROCESS;

MG :

PROCESS(BB)

BEGIN

CASE BB IS

WHEN”10”=>

EN<=&acute;1&acute;;

WHEN OTHERS=>

EN<=&acute;0&acute;;

END CASE;

CASE BB IS

WHEN”11”=>

STR<=&acute;1&acute;;

WHEN OTHERS =>

STR<=&acute;0&acute;;

END CASE;

END PROCESS;

脉宽测量模块中还有用于脉宽计数的32位计数器和计数值输出多路选择器,它们的设计这里从略。

4 单片机程序设计

本系统单片机程序总流程图如图3,其中脉宽测量子程序流程图如图4。

本相位差测量仪在以ALTERA Cyclo neII EP2C5T144为核心的

FPGA开发板中实现并通过验证。

参考文献

[1] 田秀丰.低频数字式相位测量仪的设计[J].无线通信技术,2008(2).

[2] 姚晖.基于单片机和CPLD的数字相位测量仪设计[J].工业控制计算机,2010(1).

[3] 廖超平.基于8051单片机IP设计等精度频率测量系统[J].科技资讯,2011(22).。