第3章TMS320F2812中断系统

采用 TMS320F2812 的CAN 系统解决方案

根据具体情况,下列的系统解决方案供参考选用:

1.开发平台:

z 仿真调试器 选用 SDI 公司的仿真调试器,可对 Code Composer Studio 生成的调试文件进 行仿真调试并下载。与 PC 机连接端,有 USB 口、并口等多种选择。

can@

第2页

更新时间:2006.8

有了好的 CAN 开发工具,应当可以顺利完成各个独立的 CAN 单片机节 点的开发,但这并不意味着整套系统的顺利完成。由于 CAN 协议只规 定到数据链路层,用户通常要自行定义应用层协议以完成各个 CAN 节 点之间的通信,必须要进行大量的测试才能保证确保用户自定义协议的 完整和有效。为了解决协议测试阶段遇到的大量问题,可以采用各类基 于 PC 的测试硬件及软件,以 PC 和各类 PC-CAN 接口板卡来模拟一个 系统中运行的节点、收发信息,并对系统总线上的信息监视并分析。通 过应用各种 CAN 测试工具,可以使系统在实际应用前得到充分的检验, 尽可能地到达最优的状态。

中国单片机公共实验室

CAN-bus 客户咨询报告之十二

z 应用实验板套件 选用 SDI 的 eZdps F2812 模块& eZdps F2812 CCS。eZdps F2812 是一个独立 的模块,可以让仿真器检查 TMS320F2812 DSP 的特点,以决定这款 DSP 是否满足用户的应用需求。配上 eZdps F2812 CCS,它便成为基于 TMS320F2812 开发、演示和运行软件的极好平台。

2.测试平台:

z 智能型 CAN/LIN 模块—USB-to-CAN II 该智能接口模块有两个 CAN 通道和一个 LIN 通道(汽车型)。它采用 16 位微

控制器,具有强大、高效的功能,支持即插即用。板上 16 位微控制器能够高效 地控制 CAN 控制器的发送和接收任务,即使在总线负载较重的情况下,仍可有 效支持带有时间标志的 CAN 报文的过滤、预处理和存储以及 CAN 报文的实时 传输等功能。

2812中断使用程序

TMS320F2812学习笔记中断系统及其应用2812的中断是3级中断机制,分别是外设级,PIE级以及CPU级,对于某一个具体的外设中断请求,任意一级的不许可,CPU最终都不会执行该外设中断。

(1)外设级外设产生中断时,该中断事件相关的中断标志位(IF)置1。

此时,如果该中断相应的中断使能寄存器(IE)也置为1,外设就会向PIE控制器发出一个中断请求。

如果外设级中断没有被使能(相应的使能位为0),那么外设就不会向PIE发出中断请求,相应的中断标志位会一直保持置位状态,除非用软件清除。

当然,在中断标志位保持在1的时候,一旦该中断被使能了,那么外设立马会向PIE发出中断申请。

注:不管在什么情况下,外设寄存器中的中断标志位必须采用软件进行清除。

小结:外设中断的屏蔽,需要将与该中断相关的外设寄存中的中断使能位置0;外设中断标志位的清除,需要将与该中断相关的外设寄存中的中断标志位置1;(2)PIE级当外设产生中断事件,相关中断标志位置位,中断使能位使能之后,外设就会把中断请求提交给我们的PIE模块。

PIE模块将96个外设和外部引脚的中断进行了分组,分为12组,每组8个中断,分别是PIE1-PIE12。

每个组的中断被多路汇集进入1个CPU中断,例如P DPINDA,PDPINDB,XINT1,XINT2,ADCINT,TINT0,WAKEINT这7个中断都在PIE1组内,这些中断都汇集到CPU中断的INT1。

和外设级类似的,PIE控制器中的每个组都会有一个中断标志寄存器PIEIFRx和和中断使能寄存器PIEIERx,当然x=1.....12。

每个寄存器的低8位对应于8个外设中断,高8位保留。

小结:PIE中断的使能。

就得将其相应组的使能寄存器PIEIERx的相应位进行置位;PIE中断的屏蔽。

这是和使能相反的操作;PIE应答寄存器PIEACK相关位的清除,以使得CPU能够响应同组的其他中断。

PIE级的中断和外设级的中断比较外设中断的中断标志位是需要软件清除的,而PIE级的中断标志位都是自动置位或者清除的。

TMS320F2812系统控制和中断

表3.10 低功耗模式控制寄存器1功能定义

位

名称

描述

0

XINT1

1

XNMI

2

WDINT

3

T1CTRIP

4

T2CTRIP

5

T3CTRIP

6

T4CTRIP

7

TRIP

8

C2TRIP

如果相应的控制位设置为1,将使能对应的信号将器件从低功耗模式唤醒, 进入到正常工作模式。如果设置为0,则相应的信号没有影响

(系统复位的默认值)。 WDENINT=0,看门狗复位信号 WDRST 被使能,看门狗中断信号 WDINT 屏蔽。 如果WDOVERRIDE位置1,允许用户改变看门狗控制寄存器(WDCR)的看门狗屏 蔽位(WDDIS);如果通过向WDOVERRIDE位写1将其清除,用户则不能够改变 WDDIS位的设置,写0没有影响。如果该位被清除,只有系统复位该位才会改变状 态。用户随时可以读取该状态为。

0110

CLKIN = (OSCCLK * 6.0)/2

0111

CLKIN = (OSCCLK * 7.0)/2

1000

CLKIN = (OSCCLK * 8.0)/2

1001

CLKIN = (OSCCLK * 9.0)/2

1010

CLKIN = (OSCCLK * 10.0)/2

1011

保留

1100 1101

外设 寄存器

低速外设

高速预定标器

外设 寄存器

高速外设

ADC 寄存器

功耗模 式控制

图3.1 F2810和F2812内部的各种时钟和复位电路

在F2812/F2810数字信号处理器上,所有的时钟、锁相环、看门狗以及低功耗模式等都 是通过相应的控制寄存器配置的,各控制寄存器如表3.1所示。

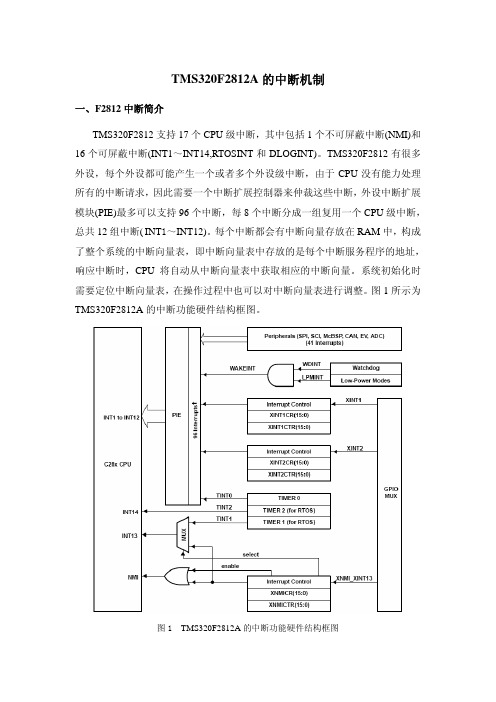

TMS320F2812A的中断机制

(EV-B)

(EV-B)

(EV-B)

(EV-B)

(EV-B)

reserved

INT6

SPIRXINTA SPITXINTA

(SPI)

(SPI)

reserved

reserved

MRINT (McBSP)

MXINT (McBSP)

reserved

reserved

INT7

reserved reserved reserved reserved reserved reserved reserved reserved

图 2 中断扩展模块图 图 2 中断响应流程图

对于复用的 12 组中断,在 PIE 模块内每组中断都有相应的中断标志位 (PIEIFRx.y)和使能位(PIEIERx.y)。除此之外,每组 PIE 中断(INT1~INT12)都有 一个响应标志位(PIEACK)。PIEIFR 和 PIEIER 不同的设置时,硬件操作如图 2 所示。

当 PIE 控制器中有中断产生时,相应的中断标志位(PIEIFRx.y)将被置 1,如 果相应的中断使能位也被置 1,PIE 将检查相应的 PIEACKx,确定 CPU 是否准 备响应该中断,如果相应的 PIEACKx 被清零,PIE 将向 CPU 申请中断;如果 PIEACKx 被置 1,PIE 将等待,直到相应的 PIEACKx 被清零时才向 CPU 申请中 断。

在 TMS320F2812 中,中断向量表可以映射到 5 个不同的存储空间,实际使 用中 F2812 只使用了 PIE 中断向量表的存储器映射,中断向量的映射主要有以下 位/信号来控制。

WMAP:状态寄存器 1(ST1)的位 3,复位后值为 1。 M0M1MAP:状态寄存器 1(ST1)的位 11,复位后值为 1。 MP/MC:该位在 XINTCNF2 寄存器的位 8,复位时 MP/MC 引脚上的值为该 寄存器的相应位的值。 ENPIE:该位为 PIECTRL 寄存器的位 0,复位后默认为 0(PIE 被屏蔽)。 依据上述位的不同的设置,中断向量表有不同的映射方式。如表 2 所示。

第3章TMS320F2812驱动程序设计学习要点

第3章 TMS320F2812驱动程序设计【本章要点】了解TMS320F2812驱动程序的特点了解TMS320F2812位字段的描述方法掌握TMS320F2812驱动程序的框架结构掌握CCS集成开发环境的应用1.驱动程序的概念:TMS320F2812处理器的驱动程序在这里实际上就是指一段能让CPU控制片内各种功能模块正常工作的程序代码。

如果我们不对片内的功能模块进行编程驱动,那么时钟系统、定时器、片内外设等硬件就无法工作,这个芯片就不能发挥其特有的功效了。

换言之,TMS320F2812处理器驱动程序的开发就是通过设置片内的各功能模块,将其本身的功能激发出来,从而保证芯片能正常地工作。

2.TI公司C28x DSPs常用代码库文件(了解)库 名 文档编号 说 明C281xC/C++头文件和外设示例SPRC097外设API驱动程序TMS320F2812闪存API SPRC125对Flash进行操作的APIC28x 定点数学函数库SPRC085包含常用的基本数学函数C28x IQMath库(虚拟浮点引擎)SPRC087将浮点算法无缝地连接到定点代码中 C28x 快速傅立叶变换程序库SPRC081提供可供调用的FFT函数C28x 滤波器库SPRC082提供FIR及IIR模块C28x 软件测试台库SPRC084提供基于实时应用的密集计算模块C28x 通信驱动程序库SPRC183虚拟的IIC总线及SPI总线驱动C28x 信号发生器库SPRC083包含正弦波、锯齿波、梯形脉冲发生器 F281x 数字电机控制程序库SPRC080帮助开发数字电机控制,比如空间矢量发生器PFC Software SPRC307帮助开发数字控制电源S V2.2版本开发环境下的TMS320F2812处理器驱动程序开发包,这个开发包的名称是“C281x C/C++ 头文件及片内外设应用示例(C281x C/C++ Header Files and Peripheral Examples)”,安装后的文件结构如图所示。

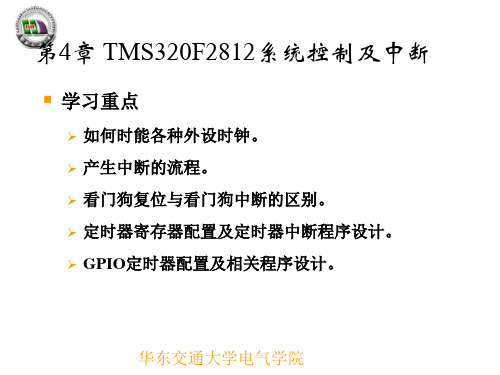

第4章_TMS320F2812系统控制及中断

4.2 时钟及系统控制

华东交通大学电气学院

4.3 振荡器及锁相环模块

2812 基于 PLL 的时钟模块可以采用两种模式,一种是 PLL 未被禁止的情况下(旁路 或使能), 使用外部晶振给 2812 提供时钟信号,使用 X1/CLKIN 引脚和 X2 引脚;另外 一种 PLL 被禁止的情况下,旁 路片内振荡器,由外部时钟源提供时钟信号,即将外部振

PIEIERx。每个寄存器的低 8 位对应于 8 个外设中断,高 8 位保留。例如 T1PINT对应于PIEIFR2 的第 4 位和 PIEIER2 的第 4 位。

因为 PIE 模块是多路复用的,那么每一组同一时间应该只能是一个中断被响应,

PIE 是怎么做到的呢?PIE 除了每组具有 刚才的 PIEIERx,PIEIFRx 寄存器 之外,还有一个 PIEACK 寄存器,它的低 12 位分别对应着 12 个组,即 INT1INT12,高位保留。假如 T1 的周期中断被响应了,则 PIEACK 寄存器的第 2 位(对应于 INT2)就会被置位,并且一直保持直到手动清除这个标志位。当 CPU 在响应 T1PNT 的时候,PIEACK 的第 2 位一直是 1, 这时候如果 PIE2 组内发生其他的外设中断,则暂时不会被 PIE 响应送给 CPU,必须等到 PIEACK 的第 2 位被复位之后,如果该中断请求还存在,那么立马由 PIE 控制 块将中断请求送至 CPU。所以,每个外设中断被响应之后,一定要对 PIEACK 的相关位进行手动服务,否则同组内的其他中断都不会被响应。

时钟频率具体的计算如下面所示。 晶振为 30M,

PLLCR 的 DIV 位被设置成 1010 时的时钟频率

CLKIN=(OSCLKIN*10)/2=(XCLKIN*10)/2=(30M*10)/2=150M Hz

第3章TMS320F2812中断系统

3.1 TMS320F2812中断的基本原理与结构

TMS320F2812的中断管理分为三级:

外设级中断管理 PIE(Peripheral Interrupt Expansion, PIE, 外设中断扩展)级中断管理 CPU级中断管理

4

3.1 TMS320F2812中断的基本原理与结构

TMS320F2812支持32个CPU级中断源,并支持软 件和硬件两种中断。 软件中断:由INTR、ORIFR或TRAP指令激发。 硬件中断: 外部中断——由外部中断引脚上的信号触发。 内部中断——由片内外设的信号触发。

5

3.1 TMS320F2812中断的基本原理与结构

TMS320F2812外设级中断管理主要负责外设内

部的中断源的屏蔽与使能。 PIE级中断管理主要负责将各种已使能的外设 中断进行分组管理并形成最终的CPU中断请求。 CPU级中断管理主要负责处理直接向CPU申请 的中断请求,这些中断请求分别来自PIE外设中 断模块、外部中断引脚和片内32位的CPU定时 器。 操作顺序: 首先由某个事件引起外设产生中断 请求并传送到PIE模块。

17

3.2 PIE中断扩展

TMS320F2812中断处理模式 在标准中断处理模式下,不使用调试中断使能寄存 器(DBGIER);只有在使用F2812实时调试模式 (Real-time Debug)且CPU被停止时,才使用调试中 断使能寄存器(DBGIER),这种情况下中断总开关 INTM不起作用。 特别地,若F2812采用实时调试模式而CPU仍然正 常运行时,则采用标准的中断处理模式。

10

3.1 TMS320F2812中断的基本原理与结构

TMS320F2812对于中断的处理主要分为下列4个步骤: ⑴硬件中断或软件中断提出中断请求。 ⑵F2812在能够响应中断的情况下响应中断请求。 ⑶保存现场,为执行中断服务程序作好准备。 ⑷执行中断服务子程序

第三章F2812的系统控制与中断

1

DSP技术与应用

3.1 F2812的存储器

F2812的存储空间: Flash 128kX16b OTP存储器 只能一次编程,不能擦除 表4.1 flash和OTP配置寄存器寄存器受EALLOW位保护 (保护寄存器) 执行EALLOW指令后,可将数据写入寄存器 执行EDIS指令后,写操作禁止

3

DSP技术与应用

4

F2810和F2812内部的各种时钟和复位电路 DSP技术与应用

3.2.2 锁相环电路

锁相环是一种控制晶振使其相对于参考信号保持 恒定相位的电路,在数字通信系统中使用比较广泛。

目前微处理器或DSP集成的片上锁相环,主要作用 则是通过软件实时地配置片上外设时钟,提高系统的 灵活性和可靠性。此外,由于采用软件可编程锁相环 ,所设计的系统处理器外部允许较低的工作频率,而 片内经过锁相环微处理器提供较高的系统时钟。 好处:可以有效地降低系统对外部时钟的依赖和 电磁干扰,提高系统启动和运行的可靠性,降低系统 对硬件的设计要求 。

27

DSP技术与应用

3.3 看门狗

看门狗主要用来检测软件和硬件的运行状态,当内部 计数器溢出时,将产生一个复位信号。 为了避免产生不必要的复位,要求用户定期对看门狗 定时器进行复位。 如果不明的原因使CPU中断程序,看门狗将产生一个复 位信号,使CPU复位,程序从系统软件的开始执行。 看门狗有效地提高了系统的可靠性。

18

DSP技术与应用

位10 SCIAENCLK 如置1,使能SCI-A外设模块的低速时钟(LSPCLK),要让器件 进入低功耗工作模式,用户可以将该位清零或复位。 位9 Reserved 保留位 位8 SPIAENCLK 如置1,使能串行外设接口的低速时钟(LSPCLK),要让器件 进入低功耗工作模式,用户可以将该位清零或复位。 位7~4Reserved 保留位

DSP芯片TMS320f2812的外中断(精)

DSP芯片TMS320f2812的外中断一.实验目的1.通过实验熟悉F2812A的中断响应过程。

2.学会C语言中断程序设计,以及运用中断程序控制程序流程。

二.实验原理1.中断及中断处理过程(1)中断简介中断是一种由硬件或软件驱动的信号,DSP在接到此信号时,将当前程序悬挂起来,转向去执行另外一个任务,称为中断服务程序(ISR)。

TMS320f28xDSP可支持32个ISR,可由硬件或软件触发。

所有的C28x 中断,可以分成可屏蔽中断和不可屏蔽中断两种,软件中断是不可屏蔽的。

(2)DSP一.实验目的1.通过实验熟悉F2812A的中断响应过程。

2.学会C语言中断程序设计,以及运用中断程序控制程序流程。

二.实验原理1.中断及中断处理过程(1)中断简介中断是一种由硬件或软件驱动的信号,DSP在接到此信号时,将当前程序悬挂起来,转向去执行另外一个任务,称为中断服务程序(ISR)。

TMS320f28x DSP可支持32 个ISR,可由硬件或软件触发。

所有的C28x 中断,可以分成可屏蔽中断和不可屏蔽中断两种,软件中断是不可屏蔽的。

(2)DSP处理中断的步骤①接收中断请求。

请求由软件或硬件发出。

②响应中断请求。

对于可屏蔽中断,需要满足若干条件,才发生响应;而对于不可屏蔽中断,则立即响应。

③准备执行中断服务程序。

-完成当前正在执行的指令;将进入流水线但还未解码的指令清除。

-自动保存若干寄存器的值到数据堆栈和系统堆栈。

-取得用户定义的中断向量表中当前中断向量,中断向量指向中断服务程序入口。

④执行中断服务程序。

中断服务程序包含中断返回指令,这样返回时可以出栈以前保存的关键寄存器数据,从而恢复中断服务程序执行前的现场。

(4)外中断TMS320f2812 可以响应两个外中断。

2.ICETEK-CTR板的键盘接口显示/控制模块ICETEK-CTR通过接口P8连接小键盘,接收小键盘传送的扫描码,并在每个扫描码结束后保存,同时向DSP的XINT2 发送中断信号;当DSP读键盘时将扫描码送到数据总线上。

2812外部中断

2010-05-21 23:03:48| 分类:默认分类|字号订阅1. 要使用外部中断要从两方面进行准备:首先,在硬件上必须将中断信号引到DSP的外部中断引脚上。

比如:FPGA的一个output发出中断请求信号那么就将这个管脚与DSP的XINT1相连,XINT1可以通过一个4.7k的电阻上拉到3.3v, 也可以不拉。

其次是在软件上的配置:1.初始外部中断寄存器void Xint1_init(void){EALLOW;XIntruptRegs.XINT1CR.bit.ENABLE=1;//使能外部中断XIntruptRegs.XINT1CR.bit.POLARITY=1;//中断产生在上升沿,若为0中断产生在下降沿 DISE;}由于这是一个函数,所以也要有函数声明,函数调用,函数定义。

2使能cpu INT1中断PieCtrlRegs.PIEIER1.bit.INTx4 = 1; //Enable all XINT1 interruptIER |= 0x100; // Enable CPU INTIER |= 0x0001; // enable PIEIER1, and INT13.编写中断服务程序,interrupt void Xint1_ISR(void){.......PieCtrlRegs.PIEACK.all|=0x0001;}4将中断服务程序入口地址赋给中断向量表PieVectTable.XINT1=&Xint1_ISR;总结起来使用外部中断的步骤如下:1声明外部中断服务程序和外部中断初始化函数void Xint1_init(void);interrupt void Xint1_ISR(void);2将中断服务程序入口地址赋给中断向量表PieVectTable.XINT1=&Xint1_ISR;3使能cpu INT1中断IER |= 0x0001; // enable PIEIER1, and INT1PieCtrlRegs.PIEIER1.bit.INTx4 = 1; //Enable all XINT1 interrupt4. 在主函数体外定义专断初始化函数和中断服务程序不好意思这几天加班、单位聚餐,一直没时间回复。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

IFR(11:0) . . . . . .

IER(11:0) . . . . . . MUX 1 0 CPU

全局使能 (标志) (使能) INTx.1 INTx.2 INTx.3 INTx.4 INTx.5 INTx.6 INTx.7 INTx.8 (使能) PIEIERx(7:0) (标志) PIEIFRx(7:0)

外部中断源

XINT1 XINT2 PDPINTx RS XNMI_XINT13

3.1 TMS320F2812中断的基本原理与结构

TMS320F2812外设级中断管理主要负责外设内

部的中断源的屏蔽与使能。 PIE级中断管理主要负责将各种已使能的外设 中断进行分组管理并形成最终的CPU中断请求。 CPU级中断管理主要负责处理直接向CPU申请 的中断请求,这些中断请求分别来自PIE外设中 断模块、外部中断引脚和片内32位的CPU定时 器。 操作顺序: 首先由某个事件引起外设产生中断 请求并传送到PIE模块。

第3章 TMS320F2812中断系统

第3章 TMS320F2812中断系统

中断是CPU对系统发生的某个事件作出一种反应, CPU暂时终止正在执行的程序,保留现场后自动转去 执行相应事件的处理程序,处理完成后返回断点,继 续执行被打断的原程序,中断请求信号是由硬件或软 件驱动的信号。

2

第3章 TMS320F2812中断系统

INTx MUX

来自外设 或外部中 断源

PIEACKx

3.2 PIE中断扩展

在PIE模块中,外设可屏蔽中断被分为12组,每 组占用一个CPU级中断,如PIE第1组占用INT1, PIE第2组占用INT2,…PIE第12组占用INT12,其 中直接连接到CPU上的中断不复用,直接将中断请 求传递至CPU。 对于复用的中断源,在PIE模块内每组PIE中断 有相应的中断标志位(PIEIFRx,y)、中断使能位 (PIEIERx,y)和一个中断响应标志位(PIEACK)。

第3章 TMS320F2812中断系统

中断系统是系统输入/输出部分中非常重要的 一个部分,通常需要由软硬件构成的中断系统 模块对系统中的多个中断源进行管理和控制。 其中硬件部分主要负责接收中断源发出的各种 中断请求,并按照某种方式响应其请求,然后 将系统控制权交给特定的中断服务程序;软件 部分主要负责识别中断源的类型并按其类型处 理特定的中断请求。

北京化工大学BUCT 本科课程教学

信息科学与技术学院 EEE32501T

DSP原理与应用

Principles and Applications of DSP

主讲教师: 韩阳 Michael

2013-4-12

VERSION EEE32501T201001-0302 COPYRIGHT© 2010CEEE&MIC 2013.2.25 ALL RIGHTS RESERVED.

16

3.2 PIE中断扩展

1)外设向PIE控制器提出中断请求

当外设向PIE控制器提出中断请求,相应的PIE中 断标志位(PIEIFRx,y)将被置1,如果相应的中断使 能位(PIEIERx,y)也置为1有效,则PIE将检查相应的 中断响应标志位(PIEACKx)以确定CPU是否准备好 响应该中断请求。如果中断响应标志位(PIEACKx) 被清零,PIE将向CPU发出中断请求,如果中断响 应标志位(PIEACKx)被置1,PIE将持续等待直到中 断响应标志位(PIEACKx)被清零后才向CPU发出中 断请求。

18

3.2 PIE中断扩展

TMS320F2812中断处理模式 在标准中断处理模式下,不使用调试中断使能寄存 器(DBGIER)ห้องสมุดไป่ตู้只有在使用F2812实时调试模式 (Real-time Debug)且CPU被停止时,才使用调试中 断使能寄存器(DBGIER),这种情况下中断总开关 INTM不起作用。 特别地,若F2812采用实时调试模式而CPU仍然正 常运行时,则采用标准的中断处理模式。

INT14

1

IFR中断标志寄存器 中断使能寄存器(INTM以及IER被使能了才能响应)

3.1 TMS320F2812中断的基本原理与结构

TMS320F2812支持32个CPU级中断源,并支持软件和 硬件两种中断。 软件中断:由INTR、ORIFR或TRAP指令激发。 硬件中断: 外部中断——由外部中断引脚上的信号触 发。 内部中断——由片内外设的信号触发。

3.4 可屏蔽中断

TMS320F2812中断系统中的可屏蔽中断可以 用软件设置使它们禁止(屏蔽)或允许(使能), 主要包括: 14个通用中断(INT1~INT14) CPU数据标志中断(DLOGINT) CPU实时操作系统中断(RTOSINT)

其中INT1~INT14是通用GPIO中断,CPU数据标志中断 (DLOGINT)和CPU实时操作系统中断(RTOSINT)只用于实 时仿真。

中断处理模式 标准中断处理模式 实时调试模式且CPU停机 相应标志 INTM=0且IER对应位为1 IER对应位为1且DBGIER为1

19

3.3 中断向量表

3.3.1 中断向量的分配

TMS320F2812中断向量表

TMS320F2812支持包括复位在内的32位的中断向量, 每一个中断向量是一个22位的地址,这个地址是对应 的中断服务程序ISR的入口地址。 每一个32位的中断向量存放在一个连续的地址空间中, 其中中断向量的低16位(LSB)存放在该地址的低16位, 中断向量的高16位(MSB)存放在该地址的高16位。当 一个中断被确定后,它所对应的22位的中断向量将被 取出,而该地址所对应的高10位被忽略。

11

3.1 TMS320F2812中断的基本原理与结构

TMS320F2812对于中断的处理主要分为下列4个步骤: ⑴硬件中断或软件中断提出中断请求。 ⑵F2812在能够响应中断的情况下响应中断请求。 ⑶保存现场,为执行中断服务程序作好准备。 ⑷执行中断服务子程序

12

3.2 PIE中断扩展

TMS320F2812片内含有丰富的外设,各个外设根据不 同的事件可以产生一个或多个不同优先级的外设级中断 请求. F2812 CPU级管理的中断数量是有限的,它支持17个 CPU级中断请求,1个非屏蔽中断(NMI)和16个可屏蔽 中断(INT1~INT14,RTOSINT及DLOGINT)。 如果多个外设事件触发中断请求,仅仅依靠F2812 CPU 是很难处理的,因此在TMS320F2812系统中通过一个 专门的外设中断扩展控制器模块PIE (Peripheral Interrupt Expansion)来实现这些外设多路中断的管理。

XINT2

GPIO MUX

MUX

选择 使能 NMI 中断控制 XNMICR(15:0) XNMICTR(15:0) XNMI_XINT13

INT13 INT14 DLOGINT RTOSINT INT1 INT2 . . . INT11 INT12

IFR(15:12)

IER(15:12) INTM

7

外设(SPI,SCI,McBSP,CAN,EV,ADC) (41个中断源) WAKEINT WDINT LPMINT 看门狗 低功耗模式 XINT1

†

中断控制 INT1~INT12 PIE s t p u r 6 r 9 e t n I C28×CPU TINT0 INT14 INT13

MUX

XINT1CR(15:0) XINT1CTR(15:0) 中断控制 XINT2CR(15:0) XINT2CTR(15:0) CPU定时器0 CPU定时器2(用于RTOS) CPU定时器1(用于RTOS) GPIO MUX XINT2

17

3.2 PIE中断扩展

2)PIE模块向CPU发出中断请求

如果PIE模块向CPU发出中断请求,相应的CPU 级中断标志寄存器(IFR)中对应位将置1,中断标志 位锁存到标志寄存器后,当CPU中断使能寄存器 (IER)或中断调试使能寄存器(DBGIER)相应的使能 位和全局中断屏蔽位(INTM)被使能时,CPU将最终 接收到来自外设经PIE发来的中断请求,进入中断响 应流程,执行相应的中断服务程序。

13

外设(SPI,SCI,McBSP,CAN,EV,ADC) (41个中断源) WAKEINT WDINT LPMINT 看门狗 低功耗模式 XINT1

†

中断控制 INT1~INT12 PIE s t p u r 6 r 9 e t n I C28×CPU TINT0 INT14 INT13 TINT2 TINT1 XINT1CR(15:0) XINT1CTR(15:0) 中断控制 XINT2CR(15:0) XINT2CTR(15:0) CPU定时器0 CPU定时器2(用于RTOS) CPU定时器1(用于RTOS)

10

3.1 TMS320F2812中断的基本原理与结构 硬件中断和软件中断从CPU管理的角度又分为可 屏蔽中断和不可屏蔽中断两类: 可屏蔽中断:均为硬件中断,可以用软件设置使 它们禁止(屏蔽)或允许(不屏蔽或使能)。当硬 件设备或外部引脚成功地请求了可屏蔽中断时,与 其相应的一个或几个标志被激活,无论处理器此后 是否响应此中断,这些标志都被设置为1。 不可屏蔽中断:不能被软件禁止,包括所有的软 件中断和非法指令中断ILLIGAL、硬件复位中断和 硬件中断。 对于此类中断,F2812总是要响应并从 主程序转移到中断服务程序。

20

3.3 中断向量表

3.3.2 中断向量表的映射

TMS320F2812中断向量表

F2812采用PIE扩展外部中断,其实质是将中断向量表 范围扩展,使得96个可能产生的中断都有各自独立的 32位中断入口地址。在F2812中,中断向量表可以映 射到5个不同的存储空间,而在实际应用中F2812只使 用PIE中断向量表映射部分(VMAP=1且ENPIE=1)。 F2812中断向量表映射主要由映射模式控制位/信号控 制。 21