五邑大学 数字电路与逻辑设计2004~2005(一)(答案)

2005-2006数字电路与逻辑设计II试题(A卷)

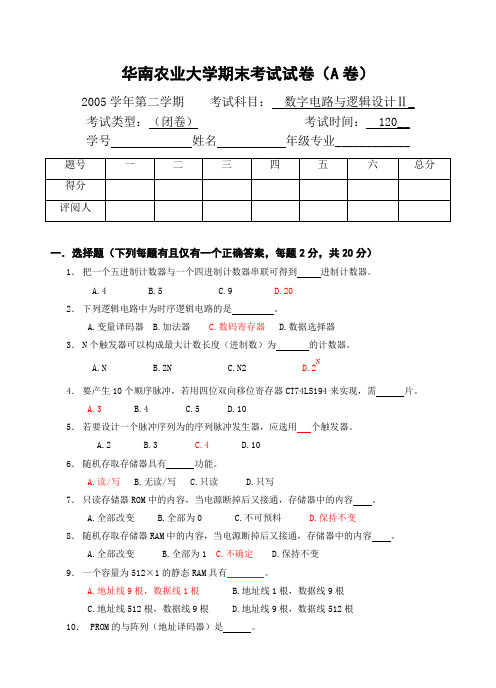

华南农业大学期末考试试卷(A卷)2005学年第二学期考试科目:数字电路与逻辑设计Ⅱ_考试类型:(闭卷)考试时间: 120__学号姓名年级专业____________一.选择题(下列每题有且仅有一个正确答案,每题2分,共20分)1.把一个五进制计数器与一个四进制计数器串联可得到进制计数器。

A.4B.5C.9D.202.下列逻辑电路中为时序逻辑电路的是。

A.变量译码器B.加法器C.数码寄存器D.数据选择器3.N个触发器可以构成最大计数长度(进制数)为的计数器。

NA.NB.2NC.N2D.24.要产生10个顺序脉冲,若用四位双向移位寄存器CT74LS194来实现,需片。

A.3B.4C.5D.105.若要设计一个脉冲序列为的序列脉冲发生器,应选用个触发器。

A.2B.3C.4D.106.随机存取存储器具有功能。

A.读/写B.无读/写C.只读D.只写7.只读存储器ROM中的内容,当电源断掉后又接通,存储器中的内容。

A.全部改变B.全部为0C.不可预料D.保持不变8.随机存取存储器RAM中的内容,当电源断掉后又接通,存储器中的内容。

A.全部改变B.全部为1C.不确定D.保持不变9.一个容量为512×1的静态RAM具有。

A.地址线9根,数据线1根B.地址线1根,数据线9根C.地址线512根,数据线9根D.地址线9根,数据线512根10.PROM的与阵列(地址译码器)是。

A.可编程阵列B.不可编程阵列C.可编程阵列D.不可编程阵列二.分析题(共2小题,共20分)1、 如图一由JK 触发器构成的时序逻辑电路,回答如下几个问题?(共14分)(1) 这是同步电路还是异步电路,是moore 型电路还是mealy 型电路?(3分) (2) 分析电路的功能,画出完整的状态转换图和逻辑表达式?(9分) (3) 该电路具备自启动功能吗?(2分)2、 如图二由D 触发器构成的时序逻辑电路,回答如下问题?(共6分)(1) 分析电路功能,画出电路的时序图?(4分)(2) 根据电路中触发器所具有的功能以及触发脉冲级连的特点,总结这类电路的组成与级连规律? (2分)三. 解答题(共2小题,共15分)1. 化简下表的原始状态图。

数字电路与逻辑设计试卷(A)(04级计算机、网络工程、软件工程专业)

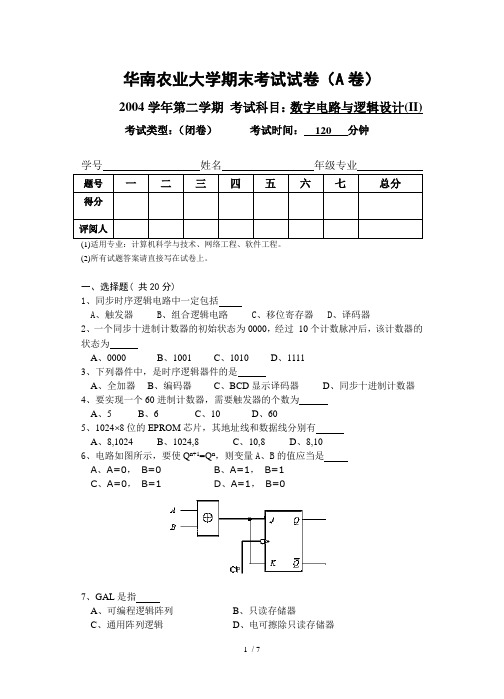

华南农业大学期末考试试卷(A卷)2004学年第二学期考试科目:数字电路与逻辑设计(II)考试类型:(闭卷)考试时间:120 分钟学号姓名年级专业(1)适用专业:计算机科学与技术、网络工程、软件工程。

(2)所有试题答案请直接写在试卷上。

一、选择题( 共20分)1、同步时序逻辑电路中一定包括A、触发器B、组合逻辑电路C、移位寄存器D、译码器2、一个同步十进制计数器的初始状态为0000,经过10个计数脉冲后,该计数器的状态为A、0000B、1001C、1010D、11113、下列器件中,是时序逻辑器件的是A、全加器B、编码器C、BCD显示译码器D、同步十进制计数器4、要实现一个60进制计数器,需要触发器的个数为A、5B、6C、10D、605、1024 8位的EPROM芯片,其地址线和数据线分别有A、8,1024B、1024,8C、10,8D、8,106、电路如图所示,要使Q n+1=Q n,则变量A、B的值应当是A、A=0,B=0B、A=1,B=1C、A=0,B=1D、A=1,B=07、GAL是指A、可编程逻辑阵列B、只读存储器C、通用阵列逻辑D、电可擦除只读存储器8、PAL的与阵列与或阵列A、与阵列固定,或阵列可编程B、与阵列可编程,或阵列固定C、与阵列和或阵列都固定D、与阵列和或阵列都可编程9、74LS138是一个A、译码器B、同步十进制计数器C、同步十六进制计数器D、优先级编码器10、在系统可编程ISP器件的特点是A、可反复编程B、成为成品后不可再改变C、必须通过紫外线擦除D、数据在掉电后会丢失二、(12分)下图是由同步十进制加法计数器74LS160组成的可变进制计数器电路,试分析当控制变量M分别为1和0时电路各为几进制计数器,并说明理由。

三、(121.该电路需用几个触发器? 为什么?2.设电路的起始状态为A,输入序列为,11010101,电路的响应和输出序列应当如何?3.经过第(2)步的电路变化,电路将停止在什么状态?五、(18分)分析下面的VHDL语言实现的功能,并回答问题LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY mux4 ISPORT (Z : IN STD_LOGIC_VECTOR( 3 DOWNTO 0) ;S : IN STD_LOGIC_VECTOR( 1 DOWNTO 0) ;A, B, C, D : OUT STD_LOGIC_VECTOR( 3 DOWNTO 0 ) ) ;END mux4;ARCHITECTURE demux4_behave OF mux4 ISBEGINPROCESS (Z, S)BEGINA <= "0000" ;B <= "0000" ;C <= "0000" ;D <= "0000" ;CASE S ISWHEN "00" => A <= Z ;WHEN "01" => B <= Z ;WHEN "10" => C <= Z ;WHEN OTHERS => D <= Z ;END CASE ;END PROCESS ;END demux4_behave ;1.在程序相应的画线部分请对此行作出解释。

五邑大学专插本参考数字电路与逻辑设计教学内容

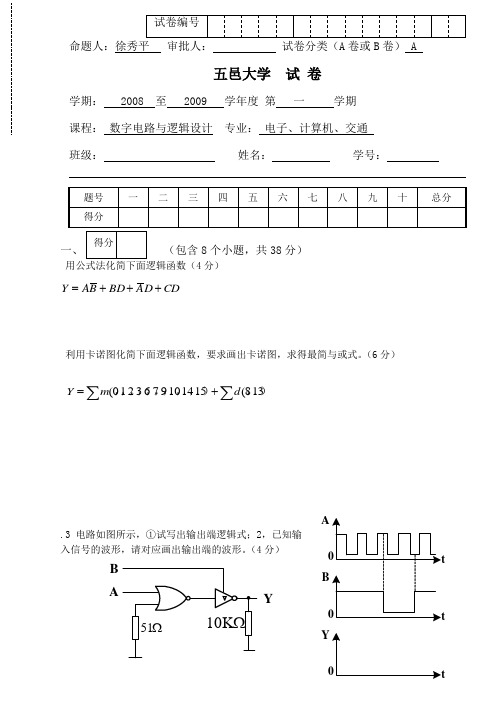

命题人:徐秀平 审批人: 试卷分类(A 卷或B 卷) A五邑大学 试 卷学期: 2008 至 2009 学年度 第 一 学期 课程: 数字电路与逻辑设计 专业: 电子、计算机、交通 班级:姓名: 学号:一、 (包含8个小题,共38分)1.1 4分)CD D A BD B A Y +++=1.2 利用卡诺图化简下面逻辑函数,要求画出卡诺图,求得最简与或式。

(6分) ∑∑+=),),,,,,,,,,138(1514109763210(d m Y.3电路如图所示,①试写出输出端逻辑式;2,已知输入信号的波形,请对应画出输出端的波形。

(4分)A B Y BA Y1.4电路如图所示,其中所有的门均为TTL 门。

若已知各门的参数为I OH =0.25mA ,I OL =14mA ,I IH =0.05mA ,I IL =1.6mA ,试求能带多少个同类门?(4分)1.5电路如图所示,请写出输出Q 的特性方程,并画出对应时钟脉冲CLK 的输出Q 的波形(4分)1. 6电路如图所示,①说明它的容量是多少?②写出各片的地址范围(十六进制表示)。

(6分)QQSETCLRDA B CLKQDR 'TTL }N Y 00000tttttCLKDR 'A B1.7 CB555定时器接成的电路如图所示,若V CC =12V ,①试问CB555接成的是什么电路?②若输入电压v I 波形如图所示,试画出输出电压v 0的波形。

(6分)1.8 如图所示电路为4位倒T 型电阻网络D/A 转换器。

已知R=10K Ω,V REF =12V 。

当某位数字量d i =1时,开关接S i 接运算放大器的反相输入端,;当d i =0时,开关接S i 接地。

试求:①输出模拟电压v o 的范围;②求d 3d 2d 1d 0=1011时,对应的输出的模拟电压v o 值。

(4分)Ivov 0tt10V 5V二、 分析题(包含三道题,共32分)2.1由3线-8线译码器74HC138构成的逻辑电路如图所示,分析电路的逻辑功能,要求写出输出端逻辑式和真值表,说明电路有什么作用。

五邑大学《数字电路与逻辑设计》 第2章 逻辑门电路.

Junction Transistor)构成的逻辑门电路。

输入端的负载特性 TTL输入端负载特性

A B TTL & Y1 A B TTL & Y2 A B

100 K

TTL & 1 Y3

100

(a)

100 K

(b)

(c)

一般对于TTL门电路,悬空和接逻辑高电平等效。

若输入端通过电阻接地,一般当RP≤0.9KΩ时,构 成低电平输入方式;当RP≥2.9KΩ时,构成高电平 输入方式。

I CS = VCC / RC

若v1 = VIL = 5V

BJT饱和

iB

VCC

RC

饱和导 通状态

vCE = 0.2 ~ 0.3V

12/11/2ห้องสมุดไป่ตู้1

3.3 TTL TTL反相器(非门) 门电路

TTL—Transistor-Transistor Logic(三

极管-三极管逻辑),TTL逻辑门就是由 双极型晶体三极管(BJT, Bipolar

OC门上拉电阻的计算 OC门上拉电阻的计算

m’-负载管输入端的个数 IOL-一个OC门T5管导通 时的电流; IIL-负载门每个输入端的 低电平输入电流 VOL(max) -驱动管输出低电 平的最小电压。 IOL VOL IIL

RL (min) ( I OL mI IL ) VCC VOL (max)

输入端的负载特性 CMOS输入端负载特性

A B COMS & Y1 A B COMS &

12/11/201

课前学习内容

2-3 TTL集成门电路 2-3-4集电极开路的TTL门电路(OC门) 2-3-5 OC门上拉电阻的计算 2-3-6 TTL三态门电路

五邑大学专插本参考数字电路与逻辑设计

命题人:徐秀平 审批人: 试卷分类(A 卷或B 卷) A五邑大学 试 卷学期: 2008 至 2009 学年度 第 一 学期 课程: 数字电路与逻辑设计 专业: 电子、计算机、交通 班级:姓名: 学号:一、(包含8个小题,共38分)4分)CD D A BD B A Y +++=利用卡诺图化简下面逻辑函数,要求画出卡诺图,求得最简与或式。

(6分) ∑∑+=),),,,,,,,,,138(1514109763210(d m Y.3电路如图所示,①试写出输出端逻辑式;2,已知输入信号的波形,请对应画出输出端的波形。

(4分)A B Y BA Y电路如图所示,其中所有的门均为TTL 门。

若已知各门的参数为I OH =,I OL =14mA ,I IH =,I IL =,试求能带多少个同类门?(4分)电路如图所示,请写出输出Q 的特性方程,并画出对应时钟脉冲CLK 的输出Q 的波形(4分)1. 6电路如图所示,①说明它的容量是多少?②写出各片的地址范围(十六进制表示)。

(6分)A DR'TTL NtR 'ACB555定时器接成的电路如图所示,若V CC =12V ,①试问CB555接成的是什么电路?②若输入电压v I 波形如图所示,试画出输出电压v 0的波形。

(6分)如图所示电路为4位倒T 型电阻网络D/A 转换器。

已知R=10K Ω,V REF =12V 。

当某位数字量d i =1时,开关接S i 接运算放大器的反相输入端,;当d i =0时,开关接S i 接地。

试求:①输出模拟电压v o 的范围;②求d 3d 2d 1d 0=1011时,对应的输出的模拟电压v o 值。

(4分)二、分析题(包含三道题,共32分)由3线-8线译码器74HC138构成的逻辑电路如图所示,分析电路的逻辑功能,要求写出输出端逻辑式和真值表,说明电路有什么作用。

(10分)S 11X 10X 1174HC 的功能表32S S '+'i Y 'i m '组合的最小项为012A A A i mv分析如图所示时序逻辑电路的功能,要求写出电路的驱动方程、状态方程、输出方程,画出状态转换图,说明是什么电路,并检查电路能否自启动。

2005-2006数字电路与逻辑设计II答案(A卷)

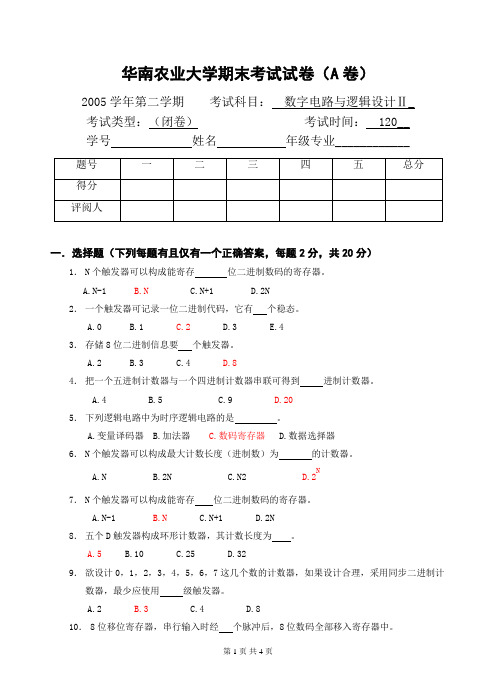

华南农业大学期末考试试卷(A卷)2005学年第二学期考试科目:数字电路与逻辑设计Ⅱ_考试类型:(闭卷)考试时间: 120__学号姓名年级专业____________一.选择题(下列每题有且仅有一个正确答案,每题2分,共20分)1.N个触发器可以构成能寄存位二进制数码的寄存器。

A.N-1B.NC.N+1D.2N2.一个触发器可记录一位二进制代码,它有个稳态。

A.0B.1C.2D.3E.43.存储8位二进制信息要个触发器。

A.2B.3C.4D.84.把一个五进制计数器与一个四进制计数器串联可得到进制计数器。

A.4B.5C.9D.205.下列逻辑电路中为时序逻辑电路的是。

A.变量译码器B.加法器C.数码寄存器D.数据选择器6.N个触发器可以构成最大计数长度(进制数)为的计数器。

NA.NB.2NC.N2D.27.N个触发器可以构成能寄存位二进制数码的寄存器。

A.N-1B.NC.N+1D.2N8.五个D触发器构成环形计数器,其计数长度为。

A.5B.10C.25D.329.欲设计0,1,2,3,4,5,6,7这几个数的计数器,如果设计合理,采用同步二进制计数器,最少应使用级触发器。

A.2B.3C.4D.810.8位移位寄存器,串行输入时经个脉冲后,8位数码全部移入寄存器中。

A.1B.2C.4D.811.要产生10个顺序脉冲,若用四位双向移位寄存器CT74LS194来实现,需片。

A.3B.4C.5D.1012.若要设计一个脉冲序列为1101001110的序列脉冲发生器,应选用个触发器。

A.2B.3C.4D.1013.随机存取存储器具有功能。

A.读/写B.无读/写C.只读D.只写14.只读存储器ROM在运行时具有功能。

A.读/无写B.无读/写C.读/写D.无读/无写15.只读存储器ROM中的内容,当电源断掉后又接通,存储器中的内容。

A.全部改变B.全部为0C.不可预料D.保持不变16.随机存取存储器RAM中的内容,当电源断掉后又接通,存储器中的内容。

数字电路与系统设计课后习题答案

4.8在双轨输入信号下,用最少或非门设计题4.7的组合电路。

解:将表达式化简为最简或与式:

(1)F=(A+C)(A+B+C)= A+C+A+B+C

(2)F=(C+D)(B+D)(A+B+C)= C+D+B+D+A+B+C

(3)F=(A+C)(A+B+D)(A+B+D)=A+C+A+B+D+A+B+D

解:F=AB+BC+AC

或:F=AB+AC+BC

(4) F=ACD+BC+BD+AB+AC+BC

解:F=AD+C+B

(5) F=AC+BC+B(AC+AC)

解:F=AC+BC

2.12用卡诺图把下列函数化简为最简与或式

(1)F(A,B,C)=m(0,1,2,4,5,7)

解:F=B+AC+AC

图略

(2)F(A,B,C,D)=m(0,2,5,6,7,9,10,14,15)

(3)F(ABC)=∏M(1,3,4,5,7)

2.10试写出下列各函数表达式F的F和F的最小项表达式。

(1)F=ABCD+ACD+BCD

(2)F=AB+AB+BC

解:(1)F=∑m(0,1,2,3,5,6,7,8,9,10,13,14)

F'=∑m(1,2,5,6,7,8,9,10,12,13,14,15)

数字电路与逻辑设计 徐秀平 第六章答案

读/写信号: W R 片选信号: CS

地址线: A0 ~ A7 , A8 , A9 读/写信号: W R

五邑大学

6.3 半导体存储器容量扩展

每一片256×8的A0~ A7可提供28=256个地址,为0~0到1~1,用扩展 的字A8、 A9构成的两位代码区别四片256×8的RAM,即将A8、 A9译成四 个低电平信号,分别接到四片256×8RAM的CS ,如下表 数

内容丢失),不能随便撕下。 586以后的ROM BIOS多采用E2PROM(电可擦写只

读ROM),通过跳线开关和系统配带的驱动程序盘,可

以对E2PROM进行重写,方便地实现BIOS升级。

五邑大学

6.1 半导体存储器的分类

ROM存储器的应用实例

数 字 电 路 与 逻 辑 设 计

• U盘是采用flash memory(也称闪存)存储技术的USB设备. USB (Universal Serial Bus)指“通用串行接口”,用 第一个字母U命名,所以简称“U盘”。 • 最新的数码存储卡是一种不需要电来维持其内容的固态

1

2

1

0

D1 W1 W2 W3

1

0

D2 W0 W2 W3

D3 W1 W3

存 储 内 容 D3 D2 D1 D0

3

1

0

1

0

0

1 0 1

1

0 1 1

0

1 1 1

1

0 1 0

存储器的容量:存储器的容量=字数(m)×字长(n)

五邑大学

6.3 半导体存储器容量扩展

1.位扩展

数 用8片1024(1K)×1位RAM构成的1024×8位RAM系统。 字 I/O I/O I/O 电 I/O I/O I/O 路 ... 102 4×1R AM 102 4×1R AM 102 4×1R AM 与 A A ... A R/W CS A A ... A R/W CS A A ... A R/W CS 逻 辑 A A 设A 计 R/W

完整版数字电路与逻辑设计试题与答案.doc

数字电路与逻辑设计( 1) 班级学号姓名成绩一.单项选择题(每题 1 分,共 10 分)1.表示任意两位无符号十进制数需要()二进制数。

A.6 B .7 C . 8 D .92.余 3 码 10001000 对应的 2421 码为()。

A.01010101 B.10000101 C.10111011 D.111010113.补码 1.1000 的真值是()。

A. +1.0111 B. -1.0111 C. -0.1001 D. -0. 10004.标准或 - 与式是由()构成的逻辑表达式。

A.与项相或 B. 最小项相或 C. 最大项相与 D. 或项相与5. 根据反演规则,FA C C DEE的反函数为()。

A. F [A C C(D E)] EB. F A C C(D E ) EC. F (A C CD E ) ED. F A C C (D E ) E6.下列四种类型的逻辑门中,可以用()实现三种基本运算。

A. 与门B. 或门C. 非门D. 与非门7.将 D 触发器改造成T 触发器,图 1 所示电路中的虚线框内应是()。

图1A.或非门B.与非门C.异或门D.同或门8.实现两个四位二进制数相乘的组合电路,应有(A. 8 B. 9 C. 10 D. 11)个输出函数。

9.要使 JK 触发器在时钟作用下的次态与现态相反,JK 端取值应为(A.JK=00 B. JK=01 C. JK=10 D. JK=11)。

10.设计一个四位二进制码的奇偶位发生器(假定采用偶检验码),需要()个异或门。

A.2 B. 3 C. 4 D. 5二.判断题(判断各题正误,正确的在括号内记“∨”, 错误的在括号内记“×”, 并在划线处改正。

每题 2 分,共 10 分)1.原码和补码均可实现将减法运算转化为加法运算。

()2. 函数 F(A, B, C)M(1,3,4,6, 7), F (A, B, C)m(0,2,5) 。

2012五邑大学数字电路与逻辑试卷B答案

命题人: 张京玲 审核人: 试卷分类(A 卷或B 卷) B五邑大学 试 卷学期: 2012 至 2013 学年度 第 1 学期 课程:数字电路与逻辑设计 课程代号: 005A1690使用班级:信息工程学院10级姓名: 学号:题号 一 二 三 四 五 六 七 总分 得分一、 填空题(每题2分,共16分)1、 触发器 是组成寄存器和移位寄存器的基本单元电器,一个n 位的数码寄存器需由 n 个触发器组成。

2、时序逻辑电路按照其触发器是否有统一的时钟控制分为 同步 时序电路和 异步 时序电路。

3、8位D/A 转换器当输入数字量时为5V 。

若只有最低位为高电平,则输出电压为 0.039 V ;若输入为,则输出电压为 5.312 V 。

4、已知原函数为CA CB A F ++=1 ,则它的反函数为C A C B A ⋅+)(5、施密特触发器有两个 稳定 状态;单稳态触发器有一个 稳定 状态和 暂 态;多谐振荡器只有两个 暂 态。

6、利用卡诺图化简法化简逻辑函数时,两个相邻项合并,消去一个变量,四个相邻项合并,消去 两 个变量等。

一般来说,2n 个相邻一方格合并时,可消去 n 个变量。

7、将模拟信号转换为数字信号,需要经过 采样 、 保持 、 量化 、 编码 四个过程。

8、一个同步RS 触发器在正常工作时,不允许输入R=S=1的信号,因此它的约束条件是 SR=0 。

二、 单项选择题(每小题1分,共8分)1、若在编码器中有50个编码对象,则要求输出二进制代码位数为( B )位。

A 、5 B 、6 C 、10 D 、502、某RAM 有8位数据线、13位地址线,则其存储容量为( B )。

A 、4KB B 、 8KB C 、16KB D 、 64KB3、以下各电路中,( B )可以完成延时功能。

A 、多谐振荡器B 、单稳态触发器C 、施密特触发器D 、石英晶体多谐振荡器 4、下面几种逻辑门中,可以用作双向开关的是( A )。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

A0 A1 A9 R /W CS

第6页共6页

n1 0

00 QQ2n 1nQ0n

Q2n1 01 11

10

01 0 0 1

00 QQ2n 1nQ0n 01 11 10 00 1 0 1

10 ×××

00 QQ2n 1nQ0n

Q1n1 01 11

10

00 0 0 0

(5)输出方程: Y Q2

(6) 此电路可以自启动。

10 ××× Q0n1

Y AB C A B C D A B CD A B C D A BCD ABC ABD A B (C D CD ) A B (C D CD) AB C AB CD

故: D10 C D,D11 CD,D12 C ,D13 CD

/0

/0

/0

/0

0000 0001 0010 0011

/1

0100

1000

0111 0110

0101 /0

/0

/0

/0

M=0

/0

/0

0000 0001 0010

/1

/0

0101 0100 0011

/0

/0

M=1

Q3Q2Q1Q0 /Y

2.试用 JK 触发器设计一同步 5 进制计数器,要求写出驱动方程、状态方程和输出方程,状态转

1 4

1

100%

6.7%

图7

八、若将 1024×1 位的 RAM 芯片组成 2048×2 位的 RAM 电路,(1)应需几片 1024×1 位的芯

片?(2)还需要哪种集成芯片?(3)试画出扩展电路,1024×1 位的 ROM 芯片的逻辑符号如下

图所示。(8 分)

答案:(1)需要 4 片; (2)还需要非门

m1 m2 m3 m5

m4 m6

m7 m7

ABC A BC

A BC AB C

AB C ABC

ABC ABC

2.真值表

3.此电路为全加器。Y1 为和,Y2 为向高位的 进位。

A B C Y1 Y2 00000 00110 01 010 0 11 0 1 10010 1 01 01 1 1 0 01 11111

&

&

答案:设输出高电平时可带 N1 个同类与非门,则

GM &

I OH (max) 2N1I IH

& 图2-1

N1

I OH (max) 2I IH

ห้องสมุดไป่ตู้

0.4 2 40 103

5

设输出低电平时可带 N2 个同类与非门,则

I OL(max) N 2 I IL

N2

I OL(max) I IL

Y1

Y2

&

&

Y7 Y6 Y5 Y4 Y3 Y2 Y1 Y0 74LS138

A0 A1 A2 S1 S2 S3

CBA 1

74LS138的功能表 S1 S2 + S3 Yi 0X 1 X1 1

1 0 mi (注:mi为A2、A1、A0组合的最小项)

图3-1

答案:1.输出端逻辑式:

YY12

3.试用卡诺图法将下面逻辑函数化成最简与-或式。(必须画出卡诺图 9 分)

Y2 f ( A, B,C, D) mi (i 0,2,6,8)

约束条件AB CD 0

CD

AB 00 01 11 10

00 1

×1

01

×1

答案:Y B C D AC

11 × × × ×

VREF 23

(23 d3

22 d2

21 d1

20 d0)

i V -

A

vo

23 R 22 R 21R 20 R

+

V

I0 I1 I2 I3

S0 S1 S2 S3

3.6 (22 20 ) 2.25V 8

VREF

d0 d1 d2 d3

(LSB)

(MSB)

(3)

分辨率=

2

六、试定性画出图 6 所示电路中电容上的电压 vC 和输出电压 vo

的波

形,并说明这是什么电路?已知施密特触发器为 CMOS 电路,且VOH VDD ,VOL 0(6 分)

答案:

R

vC

VT

vC

1

vo

VT

C

0

t

vo

图6

0

t

此电路为多谐振荡器。

七、某一 D/A 转换器电路如图 7 所示,当某位数 di 1时,对应的电子开关 Si 接参考电压U REF ,

CP

CP

RD 1

Q0 Q1 Q2 Q3

A2

Y

A1

74LS151

S

AO

DO D1 D2 D3 D4 D5 D6 D7

1

1

解:真值表为 输出的序列信号为 100111

图5-3

A2 A1 A0 D6 输出

Q3 Q2 Q1 Q0 Z

1 01 0 1 1 01 1 0 1100 0 1101 1 1110 1 1111 1

功能表

D0 D1 D2 D3

EP

C

1 ET 74LS160 LD

CP CP Q0 Q1 Q2 Q3 RD 1

CP RD LD EP ET 输出端工作状态

0

清零(异步)

10

预置数(同步)

1 1 0 1 保持(包括C)

M1

&1

Y 进位输出

11

0 保持(但C=0)

1111

计数

图5-1

答案: LD Q3M Q2Q0 M ,故 M=1 为 6 进制计数器,M=0 为 9 进制计数器。

第5页共6页

当 di 0 时, Si 接地。(1)说出该电路是哪一种 D/A 转换器;(2)若U REF 3.6 V,RF=R。

当 d3d2 d1 d0=0101 时,求输出电压的值;(3)电路的分辨率为多少?(4 分)

RF

答案:(1)此电路为权电阻网络 D/A 转换 器; (2)

vo i RF

CP

Q0

Q1

1

SD D

Q

C1

SD JQ C1

0

Q0

t

Q 1 RD

KQ RD

0

Q1

t

1

Z

CP

0

t

图4

Z

0

t

答案:Z 的频率为 CP 频率的 1/2。

第3页共6页

五、1.试分析图 5-1 的所示电路在 M=1 和 M=0 时各为几进制计数器?写出各自的状态转换图。 74LS160 的功能表如图 5-1 所示。(10 分)

I/O 1024×1

RAM

(3)如下图

A0 A1 A9 R /W CS

I/O0

I/O1

A0 A1 A9

R /W

A10

I/O 1024×1

RAM

A0 A1 A9 R /W CS

I/O 1024×1

RAM

A0 A1 A9 R /W CS

1

I/O 1024×1

RAM

A0 A1 A9 R /W CS

I/O 1024×1

换图,并说明能否自启动。(10 分)

答案: (1)状态转换图

/0

/0

000

001

010

Q1Q2Q3

(2)各输出端的卡诺图 (3)输出端的状态方程(4)驱动方程

/1

/0

Y

100

011

/0

QQ12nn

1 1

Q1Q0Q2 Q1Q0Q2 Q0Q1 Q0Q1

Q0n1 Q2Q0 0 Q0

第2页共6页

2. 试用双 4 选 1 数据选择器 74LS153 及必要的门电路实现下面逻辑函数

Y AB C A B C D A B CD A B C D A BCD ABC ABD

74LS153 的图形符号如图 3-2 所示。(12 分) 答案:解一:

J

2

J1

Q1Q0 , K 2 K1 Q0

1

J 0 Q2 , K 0 1

00 QQ2n 1nQ0n 01 11 10 0 001 010 100 011

00 QQ2n 1nQ0n 01 11 10 00 0 1 0

1 000 ××××××××× 1 0 × × ×

Q Q2n1Q1n1

11 ××× Y

第4页共6页

3.由 4 位二进制计数器 74LS161 与 8 选 1 数据选择其 74LS151 构成的序列信号发生器如图 5-3 所示,试求出序列信号 Z。74LS161 的功能表与参看图 5-1 的功能表(7 分)

0101

Z

D0 D1 D2 D3 C 1

1

ET

EP 74LS161 LD

16 1.6

10

故 GM 可驱动 5 个同类的与非门。

第1页共6页

2 写出图 2-2 所示电路的输出逻辑表达式(4 分) 答案:

Y AB BC D E AB BC D E

Vcc

A&

RL

B

& C

D& E

&Y

图2-2

三、1. 由 74LS138 构成的电路及功能表如图 3-1 所示,试写出输出端的逻辑式、真值表,并分 析逻辑功能。(8 分)

解二:构成 8 选 1,其中