第四章场效应管及其放大电路

第4章 场效应管及其放大电路讲解

6/19/2019 12:06:17 AM

当 uDS 继续增大到 uDS uGS UGS(off) ,即 uGD uGS uDS UGS(off)时,靠

近漏极端的耗尽层在 A 点合拢,如图 4-3c 所示,称为预夹断。此时,

A 点耗尽层两边的电位差用夹断电压UGS(off)表示。预夹断处 A 点的电

到漏极端的不同位置上,栅极与导电沟道之间的电位差在逐渐变化, 即距离源极越远电位差越大,施加到 PN 结的反偏压也越大,耗尽层 越向沟道中心扩展,使导电沟道形成楔形,如图 4-3b 所示。

增大 uDS 靠近漏极的沟道变窄,沟道电阻增大,产生了阻碍漏极

电流 iD 增大的因素。但在 uDS 较小时靠近漏极的沟道还没有被夹断,

第4章 场效应管 放大电路

6/19/2019 12:06:17 AM

基本要求

• 了解场效应管的分类、结型场效应管 (JFET)和金属-氧化物-半导体场效 应管(MOSFET)的结构、工作原理;

• 熟悉输出特性曲线和转移特性曲线,以 及场效应管的主要参数;

• 掌握场效应管放大电路的组成、分析方 法和应用。

6/19/2019 12:06:17 AM

4.1.2.1 uGS对导电沟道和 iD 的控制作用

d

d

d

g

g

U GG

g

U GG

s

uGS

s

(a)

(b)

uGS

s

(c)

图4-2 uDS 0时uGS 对沟道的控制作用

(a) uGS 0 (b) uGS 0 (c) uGS UGS(off)

导电沟道

增加(负数减小)近似按平方律上升,即

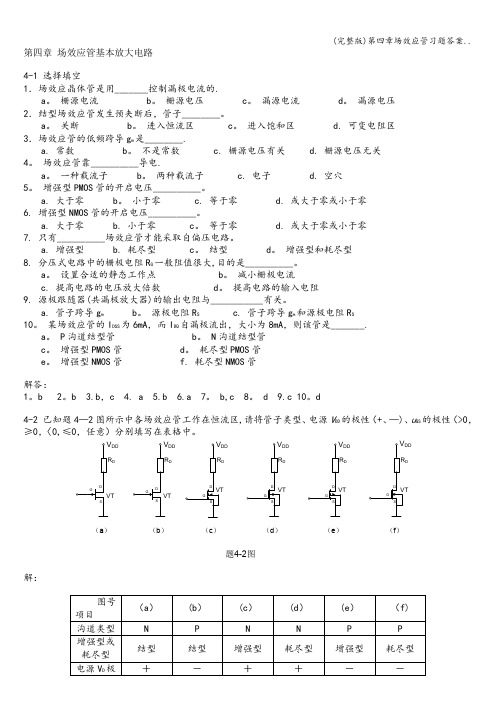

(完整版)第四章场效应管习题答案..

第四章 场效应管基本放大电路4-1 选择填空1.场效应晶体管是用_______控制漏极电流的.a 。

栅源电流b 。

栅源电压c 。

漏源电流d 。

漏源电压 2.结型场效应管发生预夹断后,管子________。

a 。

关断b 。

进入恒流区c 。

进入饱和区 d. 可变电阻区 3.场效应管的低频跨导g m 是________.a. 常数 b 。

不是常数 c. 栅源电压有关 d. 栅源电压无关 4。

场效应管靠__________导电.a 。

一种载流子b 。

两种载流子 c. 电子 d. 空穴 5。

增强型PMOS 管的开启电压__________。

a. 大于零 b 。

小于零 c. 等于零 d. 或大于零或小于零 6. 增强型NMOS 管的开启电压__________。

a. 大于零b. 小于零 c 。

等于零 d. 或大于零或小于零 7. 只有__________场效应管才能采取自偏压电路。

a. 增强型b. 耗尽型 c 。

结型 d 。

增强型和耗尽型 8. 分压式电路中的栅极电阻R G 一般阻值很大,目的是__________。

a 。

设置合适的静态工作点b 。

减小栅极电流c. 提高电路的电压放大倍数 d 。

提高电路的输入电阻 9. 源极跟随器(共漏极放大器)的输出电阻与___________有关。

a. 管子跨导g m b 。

源极电阻R S c. 管子跨导g m 和源极电阻R S 10。

某场效应管的I DSS 为6mA ,而I DQ 自漏极流出,大小为8mA ,则该管是_______.a 。

P 沟道结型管b 。

N 沟道结型管c 。

增强型PMOS 管d 。

耗尽型PMOS 管e 。

增强型NMOS 管 f. 耗尽型NMOS 管解答:1。

b 2。

b 3.b ,c 4. a 5.b 6.a 7。

b,c 8。

d 9.c 10。

d4-2 已知题4—2图所示中各场效应管工作在恒流区,请将管子类型、电源V DD 的极性(+、—)、u GS 的极性(>0,≥0,〈0,≤0,任意)分别填写在表格中。

第四章场效应管放大电路

N沟道MOS管,在VGS<VT时,不能形成导电 沟道,管子处于截止状态;只有当VGS≥VT时,才有沟 道形成。 VT——开启电压。

这种在VGS=0时没有沟道,只有VGS≥VT时才能 形成感生导电沟道的MOS管称为增强型MOS管。

第四章 场效应管放大电路

→形成由栅极指向P型

衬底的纵向电场

+

→将靠近栅极下方的空 穴向下排斥

-

→形成耗尽层。

第四章 场效应管放大电路

现假设vDS=0V,在s、g间加一电压vGS>0V 当vGS增大时→耗尽层增宽,并且该大电场会 把衬底的自由电子吸引到

耗尽层与绝缘层之间,形

成一N型薄层,构成漏-源 之间的导电沟道,称为反

N沟道耗尽型 MOS管 与 N沟 道 增 强型MOS管基本相 似。

区别:耗尽型

MOS 管 在 vGS=0 时 ,漏-源极间已有 导电沟道产生;

增强型MOS管要

在vGS≥VT时才出现 导电沟道。

5.1.5

第四章 场效应管放大电路

N沟道耗尽型MOSFET 在栅极下方的SiO2 层中掺入了大量的金 属正离子。所以当 vGS=0 时 , 这 些 正 离 子 已经感应出反型层, 形成了沟道。

夹断区

VT

2VT

第四章 场效应管放大电路

①截止区: vGS<vT

无导电沟道,iD=0,管子处于截止区.

②可变电阻区: vDS< vGS-vT

iD

K n [2(GS

T

)DS

2 DS

]

Kn

nCox

2

(W L

)

单位:mA V 2

第4章 场效应管及其电路

第4章

场效应管及其电路

场效应管(FET)是一种电压控制器件,它是利用输入电压 产生电场效应来控制输出电流的。它具有输入电阻高、噪声低、 热稳定性好、耗电省等优点,目前已被广泛应用于各种电子电 路中。 场效应管按其结构不同分为结型(JFET)和绝缘栅型(IGFET) 两种,其中绝缘栅型场效应管由于其制造工艺简单,便于大规 模集成,因此应用更为广泛。

求得ID和UGS后,再求

U DS VDD I D (Rd Rs )

第4章

场效应管及其电路

4.3 场效应管放大电路

(2) 动态分析

①FET的简化H参数等效电路

图4-14 FET简化H参数等效电路

第4章

场效应管及其电路

4.3 场效应管放大电路

图4-2

uGS 0 时的情况

第4章

场效应管及其电路

4.1 绝缘栅场效应管(MOSFET)

2.工作原理 0 (2) 栅源电压 uGS 0 ,漏源电压 uDS 时的情况 如图4-3所示,由P型 半导体转化成的N型薄层, 被称为反型层。反型层使 漏源之间形成一条由半导 体N-N-N组成的导电沟道 。 若此时加入漏源电压 , uDS i 就会有漏极电流 产生。D

D

第4章

场效应管及其电路

4.2 结型场效应管(JFET)

2.转移特性曲线

u 在N沟道JFET转移特性曲线上, GS 0处的 iD I DSS ,而 iD 0 i 处的 uGS U P 。在恒流区,D 与 uGS之间的关系可近似表示为

u iD I DSS 1 - GS UP

2

条件为: U P ≤ uDS ≤U (BR)DS

U P ≤ uGS ≤ 0

第4章 场效应管及其基本放大电路

恒流区

IDSS/V

G

D S

+

-

VGG

+

V uGS

VDD

-

O

UGS = 0V -1 -2 -3 -4 -5 -6 夹断区 -7 U P 8V

击穿区

uDS /V

特性曲线测试电路

漏极特性

漏极特性也有三个区:可变电阻区、恒流区和夹断区。

各类场效应管的符号和特性曲线 种类 结型 耗 尽 N 沟道 型 结型 耗 尽 P 沟道 型 绝缘 增 栅型 强 N 沟道 型 符号

S

S

VGG

(c) UGS <UGS(off)

(b) UGS(off) < UGS < 0

(2) 漏源电压uDS 对漏极电流iD的控制作用

uGD = uGS -uDS (a)

P+

D

iD

(b)

D

iD

G

N

P+

VDD

+ P+ GP N

P+

VDD

S iS uGS = 0,uGD > UGS(Off) ,iD 较大。

uDS /V

O

UT 2UT

uGS /V

二、N 沟道耗尽型 MOSFET

制造过程中预先在二氧化硅的绝缘层中掺入正离子, 这些正离子电场在 P 型衬底中“感应”负电荷,形成“反 型层”。即使 UGS = 0 也会形成 N 型导电沟道。 UGS = 0,UDS > 0,产生 较大的漏极电流; UGS < 0,绝缘层中正离 子感应的负电荷减少,导电 沟道变窄,iD 减小; UGS = UP , 感应电荷被 “耗尽”,iD 0。

导电沟道是 N 型的, 称 N 沟道结型场效应管。

第四章_MOSFET及其放大电路

GSQ

)则

TN

i K V V K V V v D

(

)2 2

n

GSQ

TN

(

)

n

GSQ

TN

gs

=IDQ

i K V V v 2 d

(

)

n

GSQ

TN

gs

g 2K V V 令

(

)

m

n

GSQ

TN

则

i g v d

m gs

跨导也可以通过求微分得到:

g i

2K V V m

D

vV

const

GS

GS Q

vGS

VGG

S

•在栅极和衬底之间施加的电压VGB>0,

形成自上而下的电场,该电场随电压的增

N+

大而加强。

G

D

N+ N型沟道

• 在电场的作用下, P区中的多子(空穴) 向衬底下部移动,少子(电子)被吸引到 G极并在sio2表面积累。

P型衬底

B

•若增大VGS ,则电子积累得越多,直到感应的电子能在漏极和源极

之间形成可测电流(即VGS增加到足够大),此时N型导电沟道形成,

U GQ

U AQ

Rg1 Rg1 Rg2

VDD

USQ I DQ Rs

IDQ Kn (UGSQ UTN )2

U DSQ VDD I DQ (Rd Rs )

为什么加Rg3?其数值应大些小些?

二、场效应管工作状态分析

[分析指南] MOSFET电路的直流分析

求VGS,VGS>VTN?

是

否

假设工作在放大区 ID=Kn(VGS-VTN)2

04第四章、场效应管放大电路例题解析-单元检测200310

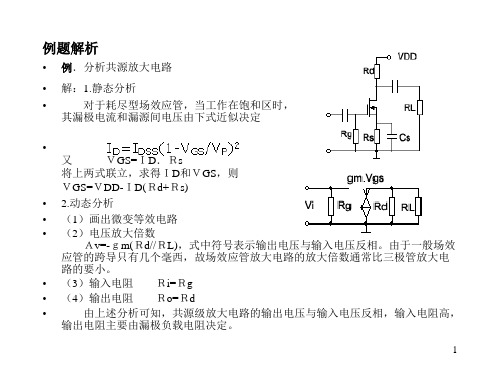

• • • 例.分析共源放大电路 解:1.静态分析 对于耗尽型场效应管,当工作在饱和区时, 其漏极电流和漏源间电压由下式近似决定

• 又 VGS=ID.Rs 将上两式联立,求得ID和VGS,则 VGS=VDD-ID(Rd+Rs) 2.动态分析 (1)画出微变等效电路 (2)电压放大倍数 Av=-gm(Rd//RL),式中符号表示输出电压与输入电压反相。由于一般场效 应管的跨导只有几个毫西,故场效应管放大电路的放大倍数通常比三极管放大电 路的要小。 (3)输入电阻 Ri=Rg (4)输出电阻 Ro=Rd 由上述分析可知,共源级放大电路的输出电压与输入电压反相,输入电阻高, 输出电阻主要由漏极负载电阻决定。Fra bibliotek• •

•

4、两级放大电路如图所示,已知T1管的gm,T2 管的rbe、β (1)画出微变等效电路; (2)求放大电路的中频电压放大倍数Av的表达式 及Ri、Ro的表达式。 (答案)

2

•

5、电路如图,已知:T1管gm=0.8mA/V,T2管 rbe=1.2k ,β=100;C1、C2、C3、Cs交流 短路。 (1)画出小信号等效电路。 (2)求Ri、Ro及Av。(答案与提示)

•

6、场效应管自举电路如图,已知VDD=+20V, Rg=51M ,Rg1=200k ,Rg2=200k ,Rs=22k ,g m=1mA/V,自举电容C很大,可以认为交流短路。 求:(1)无自举电路的输入电阻Ri。 (2)有自举电路的输入电阻Ri。 (3)说明自举的作用。

•

7、(提高题)图所示电路中,仅当源极电阻 R2增大时,放大电路的电压放大倍数|Av|如 何变化?(答案与提示)

1

• • •

• • •

单元检测

第4章场效应管放大电路.

如果用 id、ugs、uds 分别表示 iD、uGS、uDS 的变化部分, 则式(4-51可写为id = g mugs + gm = − 2 I DSS UP 1 uds rD ⎞⎟⎟⎠⎛ U GS ⎜⎜1 − U P ⎝ gm0 = − 2 I DSS UP ⎞⎟⎟⎠⎛ U GS gm = gm0 ⎜⎜1 − U P ⎝ 4.5.3 共源极放大电路与晶体管的共射放大电路相对应,由 N 沟道结型场效应管和 MOS 场效应管组成的共源放大电路分别如图(a和(b所示。

共源放大电路 (a N 沟道结型场效应管共源放大电路(b MOS 场效应管共源放大电路静态分析场效应管组成放大电路和晶体管一样,要建立合适的静态工作点,所不同是,场效应管是电压控制器件,因此它需要有合适的栅极电压。

通常场效应管的偏置电路形式有两种:自偏压电路和分压式自偏压电路,分别如图(a﹑(b所示。

自偏压电路只适用于结型场效应管或耗尽型MOS 管:分压式自偏压电路既适用于增强型场效应管,也能用于耗尽型场效应管。

栅极电压:对场效应管放大电路静态工作点的确定,可以采用图解法或公式计算,图解法的原理和晶体管相似。

用公式进行计算可通过特性方程:或交流分析共源放大电路的微变等效电 Ri=(Rg1//Rg2)+Rg3 Ro=Rd 共源放大电路与共射电路形式相类似。

只是共源放大电路的输入电阻要比共射电路的大得多(Rgs 通常很大),故需要高输入电阻时多宜采用场效应管放大电路。

(2)共漏放大电路共漏放大电路是与共集放大电路类似的一种电路形式。

电路如图所示。

共漏放大电路也常称为源极跟随器或源极输出器。

共漏放大电路(a)共漏放大电路 (b 微变等效电路确定静态工作点时,可列出回路方程与特性方程联立求解:交流性能分析共漏电路的特点与共集电极电路相似,电压极放大倍数小于 1,但场效应管的导跨比双极型晶体管的 ß低,所以共漏电路的电压放大倍数一般比共射电路低,另外它的输出电阻也较低。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

§4、1差动放大电路(第二页)

基本差动电路存在如下问题:

电路难于绝对对称,因此输出仍然存在零漂;管子没有采取消除零漂的措施,有时会使电路失去放大能力;它要对地输出,此时的零漂与单管放大电路一样。

为此我们要学习另一种差动放大电路------长尾式差动放大电路(源自)差模信号及差模电压放大倍数Aud

差模信号---在差动放大管T1和T2的基极分别加入幅度相等而极性相反的信号。如图(3)所示

差模信号的作用,由于信号的极性相反,因此T1管集电极电压下降,T2管的集电极电压上升,且二者的变化量的绝对值相等,因此:

此时的两管基极的信号为:

所以: ,由此我们可以看出差动电路的差模电压放大倍数等于单管电压的放大倍数。

它的大小反映了集成运放输入端向差模输入信号源索取电流的大小。要求它愈大愈好。

4、输出电阻 rO

它的大小反映了集成运放在小信号输出时的负载能力。

5、共模抑制比 CMRR

它放映了集成运放对共模输入信号的抑制能力,其定义同差动放大电路。CMRR越大越好。

§4、3总结

一:总结

这一章主要掌握的内容有一下几点:

它的放大作用(输入信号有两种类型)

(1)共模信号及共模电压的放大倍数Auc

共模信号---在差动放大管T1和T2的基极接入幅度相等、极性相同的信号。如图(2)所示

共模信号的作用,对两管的作用是同向的,将引起两管电流同量的增加,集电极电位也同量减小,因此两管集电极输出共模电压Uoc为零。因此: 。

于是差动电路对称时,对共模信号的抑制能力强

又∵CMR=67dB

∴CMRR≈2239

∴Auc=Aud/CMRR≈0.11

则输出电压为:

§4、2集成运算放大器

集成运放是一种高放大倍数、高输入电阻、低输出电阻的直接耦合放大电路

一:集成运放的组成

它有四部分组成:1、偏置电路;

2、输入级:为了抑制零漂,采用差动放大电路

3、中间级:为了提高放大倍数,一般采用有源负载的共射放大电路。

2:长尾式差动放大电路

它又被称为射极耦合差动放大电路,如右图所示:图中的两个管子通过射极电阻Re和Uee耦合。

下面我们来学习它的一些指标

(1)静态工作点

静态时,输入短路,由于流过电阻Re的电流为IE1和IE2之和,且电路对称,IE1=IE2,

因此:

(2)对共模信号的抑制作用

在这里我们只学习共模信号对长尾电路中的Re的作用。由于是同向变化的,因此流过Re的共模信号电流是Ie1+Ie2=2Ie,对每一管来说,可视为在射极接入电阻为2Re。

1、直接耦合放大器的零点漂移现象;

2、差动放大器(长尾电路和具有恒流源的电路)直流工作点的计算;

3、差动放大器的信号输入、输出方式;

4、差动放大器的动态性能(差模电压放大倍数、共模电压放大倍数、CMRR、输入电阻和输出电阻)的分析计算,电路参数变化对放大器的影响。

第四章无损检测技术

无损检测技术主要用于生产检验性实验,而且是个辅助手段。在生产检验性实验当中,主要还是靠预留试块来检测混凝土的强度,由监理员直接检测钢筋的配置等等。但是在有些情况下,也需要做一些检测,那么就是这一章主要介绍的内容。

产生零漂的原因是:晶体三极管的参数受温度的影响。解决零漂最有效的措施是:采用差动电路。

二:差动放大电路

1、差动放大电路的基本形式如图(1)所示

基本形式对电路的要求是:两个电路的参数完全对称两个管子的温度特性也完全对称。

它的工作原理是:当输入信号Ui=0时,则两管的电流相等,两管的集点极电位也相等,所以输出电压Uo=UC1-UC2=0。温度上升时,两管电流均增加,则集电极电位均下降,由于它们处于同一温度环境,因此两管的电流和电压变化量均相等,其输出电压仍然为零。

我们先来学习一个概念---------零点漂移

一:零点漂移

零点漂移可描述为:输入电压为零,输出电压偏离零值的变化。它又被简称为:零漂

问题:零点漂移是怎样形成的?

答:运算放大器均是采用直接耦合的方式,我们知道直接耦合式放大电路的各级的Q点是相互影响的,由于各级的放大作用,第一级的微弱变化,会使输出级产生很大的变化。当输入短路时(由于一些原因使输入级的Q点发生微弱变化 象:温度),输出将随时间缓慢变化,这样就形成了零点漂移。

4、输出级:为了提高电路驱动负载的能力,一般采用互补对称输出级电路

二:集成运放的性能指标(扼要介绍)

1、开环差模电压放大倍数 Aod

它是指集成运放在无外加反馈回路的情况下的差模电压的放大倍数。

2、最大输出电压 Uop-p

它是指一定电压下,集成运放的最大不失真输出电压的峰--峰值。

3、差模输入电阻rid

由于Re对差模信号不产生影响,故双端输出的差模放大倍数仍为单管放大倍数:

(4)共模抑制比(CMRR)

我们一般用共模抑制比来衡量差动放大电路性能的优劣。CMRR定义如下:

它的值越大,表明电路对共模信号的抑制能力越好。

有时还用对数的形式表示共模抑制比,即: ,其中 为差模增益。CMR的单位为:分贝 (dB)

它的共模放大倍数为: (用第二章学的方法求得)

由此式我们可以看出Re的接入,使每管的共模放大倍数下降了很多(对零漂具有很强的抑制作用)

(3)对差模信号的放大作用

差模信号引起两管电流的反向变化(一管电流上升,一管电流下降),流过射极电阻Re的差模电流为Ie1-Ie2,由于电路对称,所以流过Re的差模电流为零,Re上的差模信号电压也为零,因此射极视为地电位,此处“地”称为“虚地”。因此差模信号时,Re不产生影响。

(5)一般输入信号情况

如果差动电路的输入信号,即不是共模也不是差模信号时:我们要把输入信号分解为一对共模信号和一对差模信号,它们共同作用在差动电路的输入端。

例1:如右图所示电路,已知差模增益为48dB,共模抑制比为67dB,Ui1=5V,Ui2=5.01V,

试求输出电压Uo

解:∵ =48dB,∴Aud≈-251,

集成运算放大器(简称运放)是一种高电压放大倍数的直接耦合放大器。它工作在放大区时,输入

和输出呈线性关系,所以它又被称为线性集成电路。

这一章我们来学习集成放大电路的组成原理,重点来学习差动放大电路。在学习时我们把它的内容

分为三节,它们是:

§4、1差动放大电路

§4、2集成运算放大器

§4、3总结

§4、1差动放大电路(第一页)