Cadence中Capture向Allegro中导入网表时的常见错误讲解学习

cadence16.5与allegro无法交互

今天和往常一样将在软件cadence16.5里画好的原理图生成网表并导入allegro里面,然后着手对PCB进行元器件布局,但在开始布局的时候发现原理图和PCB无法交互。

在原理图中点击元器件时,PCB无法对相应的元器件显示高亮。

作为珠海鼎芯科技(D_Chip)公司的一名研发工程师,遇到问题最主要的不在于问题本身,而在于解决问题时的思路和步骤。

以下就是笔者解决这个问步骤。

1、刚开始以为导入网表路径不对,再次导入网表并确保网表路径正确。

导入之后发现还是无法交互。

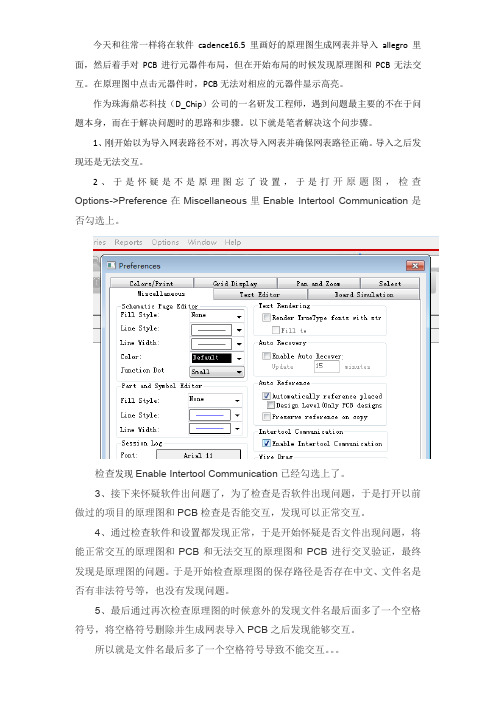

2、于是怀疑是不是原理图忘了设置,于是打开原题图,检查Options->Preference在Miscellaneous里EnableIntertoolCommunication是否勾选上。

检查发现EnableIntertool Communication已经勾选上了。

3、接下来怀疑软件出问题了,为了检查是否软件出现问题,于是打开以前做过的项目的原理图和PCB检查是否能交互,发现可以正常交互。

4、通过检查软件和设置都发现正常,于是开始怀疑是否文件出现问题,将能正常交互的原理图和PCB和无法交互的原理图和PCB进行交叉验证,最终发现是原理图的问题。

于是开始检查原理图的保存路径是否存在中文、文件名是否有非法符号等,也没有发现问题。

5、最后通过再次检查原理图的时候意外的发现文件名最后面多了一个空格符号,将空格符号删除并生成网表导入PCB之后发现能够交互。

所以就是文件名最后多了一个空格符号导致不能交互。

Cadence中Capture向Allegro中导入网表时的常见错误

一、Capture生成netlist的时候报错:1.Unable to open c:\Cadence\PSD_14.2\tools\capture\allegro.cfg for reading. Please correct the above error(s) to proceed错误解释:allegro.cfg文件找不到或allegro.cfg文件不能打开,这个问题的根源是,有可能每台电脑上安装Allegro的的位置不一样,allegro.cfg 文件找不到是理所当然的。

处理办法:点生成netlist,点setup,修改路径为capture\allegro.cfg所在路径,把allegro.cfg文件的位置选择你现在安装目录的文件位置。

2. Spawning... "C:\Cadence\PSD_15.1\tools\capture\pstswp.exe" -pst -d "F:\gcht\CC2430\Projects\mysch.dsn" -n"C:\CADENCE\PSD_15.1\TOOLS\PROJECTS" -c"C:\Cadence\PSD_15.1\tools\capture\allegro.cfg" -v 3 -j"CC2430_DEMO"#1 Error [ALG0012] Property "PCB Footprint" missing from instance U3: SCHEMATIC1, PAGE1 (2.00, 2.10).#2 Error [ALG0012] Property "PCB Footprint" missing from instance C2: SCHEMATIC1, PAGE1 (2.30, 0.30).#17 Aborting Netlisting... Please correct the above errors and retry.错误解释:Error [ALG0012] Property "PCB Footprint" missing from part <Part Reference>: <Schematic> , <Page> (<LocationX> , <LocationY)>A PCB Footprint (JEDEC_TYPE in Allegro) is required for all parts in Allegro. Therefore all parts without this property are listed before aborting the netlisting. You can add the PCB Footprint property by selecting the part listed, then choosing Edit Properties from the pop-up menu and placing a value, such as dip14_3, on the part.在Allegro中,每个器件都需要一个PCB封装。

Cadence中Capture向Allegro中导入网表时的常见错误

一、Capture生成netlist的时候报错:1.Unable to open c:\Cadence\PSD_14.2\tools\capture\allegro.cfg for reading. Please correct the above error(s) to proceed错误解释:allegro.cfg文件找不到或allegro.cfg文件不能打开,这个问题的根源是,有可能每台电脑上安装Allegro的的位置不一样,allegro.cfg 文件找不到是理所当然的。

处理办法:点生成netlist,点setup,修改路径为capture\allegro.cfg所在路径,把allegro.cfg文件的位置选择你现在安装目录的文件位置。

2. Spawning... "C:\Cadence\PSD_15.1\tools\capture\pstswp.exe" -pst -d "F:\gcht\CC2430\Projects\mysch.dsn" -n"C:\CADENCE\PSD_15.1\TOOLS\PROJECTS" -c"C:\Cadence\PSD_15.1\tools\capture\allegro.cfg" -v 3 -j"CC2430_DEMO"#1 Error [ALG0012] Property "PCB Footprint" missing from instance U3: SCHEMATIC1, PAGE1 (2.00, 2.10).#2 Error [ALG0012] Property "PCB Footprint" missing from instance C2: SCHEMATIC1, PAGE1 (2.30, 0.30).#17 Aborting Netlisting... Please correct the above errors and retry.错误解释:Error [ALG0012] Property "PCB Footprint" missing from part <Part Reference>: <Schematic> , <Page> (<LocationX> , <LocationY)>A PCB Footprint (JEDEC_TYPE in Allegro) is required for all parts in Allegro. Therefore all parts without this property are listed before aborting the netlisting. You can add the PCB Footprint property by selecting the part listed, then choosing Edit Properties from the pop-up menu and placing a value, such as dip14_3, on the part.在Allegro中,每个器件都需要一个PCB封装。

修改不规范Orcad生成的网表,正确导入allegro(四)

修改不规范Orcad生成的网表,正确导入allegro(四)第一篇:修改不规范Orcad生成的网表,正确导入allegro(四) 修改cadence生成的网表,正确导入allegro 原理图是硬件用Orcad画的,不太规范,存在一些非法字符等错误,如果pcb用pads 设计那是可以导入网表,可以同步,方法后续会说明,但用allegro设计,存在非法字符是不能直接导入网表,需要修改网表。

要正确导入必须要有正确的网表和库文件。

库文件:上次讲了pads转allegro,生成了brd文件,这里就可以用brd导出allegro的库,但库存在一些问题,问题的修改方法,可参考之前的文档--allegro修改pads生成的库文件。

网表:接下来就是要说明的重点。

A.打开Orcad的原理图,用第三方网表导出后缀名的文件。

为了避免后续找不到库文件路途,现统一放在一个文件夹内。

B.新生成brd文件,取名zxd.brd,画个板框属性,订好原点坐标。

如下图C.在allegro用第二方网表导入net,因为有非法字母,不行,出现问题报表,如图,把报表另存error.txt之后打开,一一查看错误。

可以类似总结出以下问题: 1.ERROR(SPMHNI-67): Cannot find device file for 'C0402'.RE:出现这种问题,主要是库文件,缺乏一个c0402.txt文档,用allegro打开c0402.dra,选择file---Create Device...---选择IC,确认ok即可。

这里只是选择一个代表,所有的库文件,都要如此做,生成TXT文档。

2.ERROR(SPMHNI-67): Cannot find device file for 'SOT23_123'.RE:前面已经生成了txt文档,还出现提示,那就去确认pcb封装名字和原理图footprint名字是否一样,如图,检查发现一个中横线一个下划线,导致不一样,这里就需要修改,一般我习惯于中横线,就要改原理图的footprint。

cadence生成网络表时出现如下错误解决办法-推荐下载

cadence⽣成⽹络表时出现如下错误解决办法-推荐下载U(ZE0B5L5b%X;n4g Allegro 对⼀些字符[例如"空格","⼩数点"等等]很在意,可以参阅相关⽂档的描述.(3)Error Illegal character "Dot(.)" found in "PCB Footprint"#1 Error [ALG0081] Illegal character "Dot(.)" found in "PCB Footprint" property for component instance C255: PG16_AC97, PG16_AC97 (226.06, 132.08) .封装命名不能包含“.”(4)Error Illegal character "Forward Slash(/)" found in "PCB Footprint" property#1 Error [ALG0081] Illegal character "Forward Slash(/)" found in "PCB Footprint" property for component instance C255: PG16_AC97, PG16_AC97 (226.06, 132.08) .#2 Error [ALG0081] Illegal character "Forward Slash(/)" found in "PCB Footprint" property for component instance D3: PG01_LED&Switch&7-Segment Disp, PG01_LED&Switch&7-Segment Disp (93.98, 33.02) .#3 Error [ALG0081] Illegal character "Forward Slash(/)" found in "PCB Footprint" property for component instance C245:PG16_AC97, PG16_AC97 (205.74, 35.56) .封装命名不能包含“/”(5)⽐较隐藏的排除法Loading... E:\FPGA\SCH\allegro/pstchip.dat#34 WARNING(SPCODD-34): Expected ';' character on line 5308. Check the name and value syntax for invalid characters in the primitive definition before the line number.ERROR(SPCODD-47): File ./allegro/pstchip.dat could not be loaded, and the pac kaging operation did not complete. Check the pxl.log file for the errors causing this situ ation and package the design again.、管路敷设技术通过管线不仅可以解决吊顶层配置不规范⾼中资料试卷问题,⽽且可保障各类管路习题到位。

allegro网络表导入

在使用DXP的时候,不存在网表导入等问题,大多数的行为已经是软件自动完成了,但是在Allegro中却不行,需要自己手动来完成。

注意在绘制电路板的时候,要先确定绘制区域,以及各个层的状况,边界,安装孔等,都不是随意的来修改。

网表的生成,首先要重新编辑元件编号,先选择dsn文件,然后选择Tools -> Annotate。

scope要选择整个工程,entire。

action中要先选择reset part references to "?"来取消所有的编号,然后再选择无条件的索引更行,Unconditional reference update 来进行全部重新跟新。

然后进行DRC检查,先选择dsn文件,然后再选择Tools -> Design Rules Check。

DRC只能检查出原理图的连接问题,和元器件的属性等。

接着再来查阅器件的封装,在确定器件封装的时候,我有一点点建议,虽然稍微麻烦一点,但是却能够减小出问题的概率。

原理图检查之后,不仅仅要保证没有DRC错误,还要保证没有原理上的错误,这样就生成一张器件清单列表,方法为:在dsn文件被选中的情况下,Tools -> Bill of Materials。

可以不做任何修改的生成bom清单,路径在最下面的Browse可以看到,不做修改会放在同一工程目录下的。

查阅工程目录表,可以看见Outputs下面就有一个.bom后缀名的文件,双击这个文件就可以看见使用了哪一些器件,以及个数。

生成元件清单除了是.bom的方式外,也可以是excel表格,但是由于生成的速度比较慢,所以我就直接选择复制粘贴到excel表格中了。

生成的这个表格有两个作用:一是采购元件的时候有一个详细列表,能够方便的采购人员来查阅;二是将各种器件的封装记录下来,保证每一个封装都存在。

器件封装的绘制见之前的博文。

封装的添加,在原理图中,在dsn文件出右键,选择Editor Object Property, 查阅PCB Footprint这一栏中是不是每一个器件的封装都已经填写上了,并且是不是和相应的原理图对应。

allegro导入网表错误详解

此文章由资深Layout攻城狗LGW(Gavin)提供,是其的经验笔记,可转可拷。

错误种类1:#1 WARNING(SPMHNI-192): Device/Symbol check warning detected.WARNING(SPMHNI-194): Symbol 'SOD_123' for device 'SCHOTTKY_SOD_123_B5819W(DNI)' not found in PSMPATH or must be "dbdoctor"ed.此类错误和没有PCB封装有关。

错误种类2:ERROR(SPMHNI-196): Symbol 'UTH12T02' for device 'XFMR-H1102_0_UTH12T02_H12T02' has extra pin '14'.此类错误表示原理图符号的PIN脚和PCB封装PIN数量或命名不对。

错误种类3:#5 ERROR(SPMHNI-176): Device library error detected.ERROR(SPMHNI-190): Device problem 'FERRITE BEAD_0_LC0805_100MHZ;10'. Package property error: 'VALUE'='100Mhz;100ohm±25%_3A'. Illegal character(s) present in the name or value..ERROR(SPMHNI-170): Device 'FERRITE BEAD_0_LC0805_100MHZ;10' has library errors. Unable to transfer to Allegro.这个错误是因为原理图元件的VALUE有非法字符。

利用Allegro画封装和布局时常见错误详解

利⽤Allegro画封装和布局时常见错误详解⼀:焊盘篇1. 问题⼀:⽤padstack editor制作完焊盘后,在pcb editor中找不到焊盘。

解决办法:在Pcb editor中选择set→user preference→paths→Library→分别在padpath和psmpath中加⼊焊盘的路径(选中所对应的上层⽂件夹即可)⼆:⽹表导⼊篇(Cadence中⽣成netlist失败的原因)1. 问题⼀:Unable to open c:\Cadence\PSD_14.2\tools\capture\allerro.cfg for reading.Please correct the above error(s) to proceed.错误原因:allegro.cfg⽂件找不到或allegro.cfg⽂件不能打开,这个问题的根源是,有可能每台电脑上安装Allegro的位置不⼀样,allegro.cfg⽂件找不到是理所当然的。

解决办法:点⽣成netlist,点setup,修改路径为capture\allegro.cfa所在路径,把allegro.cfg⽂件的位置选择你现在安装⽬录的⽂件位置。

(⽰例:D:\Cadence\SPB_16.5\tools\capture\allegro.cfg)2.问题⼆:#1 ERROR(ORCAP-36055):Illegal character in \hi-am13-mb-v.ooo(a10)#2 ERROR(ORCAP-36055):Illegal character in \hi-am13-mb-v.ooo(a10)\#3 ERROR(ORCAP-36055):Illegal character in \hi-am13-mb-v.ooo(a10)\…….错误原因:⾸先确认了是⾮法字符,ORCAD包含的⾮法字符有:”/”、”<”、”>”、”#”、”$”、”(”、”)”。

Allegro中网络表的导入以及回编到Capture中的一些注意事项

Allegro中网络表的导入以及回编到Capture中的一些注意事项Allegro中网络表的导入以及回编到Capture中的一些注意事项前言:网络表(Netlist)是沟通电路原理图和Layout实际板子的桥梁。

网络表包含的内容有零件Pin的连接线关系以及零件的包装等基本信息,Cadence提供的Capture到Allegro新的网络表的转发除了可以把一基本信息带到PCB Layout中,还可以把一些layout时用到的设定、约束通过网络表带到Allegro中,使工程师在设计电路时就可以大致了解PCB 板子上的布线情况,从而也节省了Layout工程师的时间,提高了工作效率!例如:电子工程师可以在原理图中把一些Power线设定好最小线宽,这样用新转法时就可以直接把设定带入Allegro,可以防止Layout工程师疏忽忘了设定走线没有达到要求。

相反把PCB上的信息反馈到原理图中,这过程一般称为回编(Backannotation),以保证实物PCB与原理图同步。

例如:Layout工程师会对PCB上的零件作swap,rename等动作,为了保持PCB与原理图的统一必须把PCB中更改的内容回编到原理图中。

用Capture设计的原理图转入Allegro中有两种方式:第一种,第三方软件导入netlist的方式第二种,针对Cadence产品的直接导入方式,也称为新转法下面内容将会对这两种方式的特定和操作做相应介绍。

第一种,第三方软件导入netlist的方式优点:在Capture中定义可以相对简单,缺点:导入网络表和回编原理图都相对复杂,导入时需要Device file,回编时需要提供.swp file主要特点:这种方式是Capture 9.2以前的版本产生网络表导入Allegro的唯一方法,就是通过Capture Create Netlist的Other方式,格式选Allegro.dll就可以了,现在很多公司还常使用这种方式。

Cadence中Capture向Allegro中导入网表时的常见错误

Cadence中Capture向Allegro中导入网表时的常见错误一、capture生成netlist的时候报错:1.unabletoopenc:\\cadence\\psd_14.2\\tools\\capture\\allegro.cfgforreading.ple asecorrecttheaboveerror(s)toproceed错误解释:allegro.cfg文件打听没或allegro.cfg文件无法关上,这个问题的根源就是,有可能每台电脑上加装allegro的的边线不一样,allegro.cfg文件打听没就是理所当然的。

处置办法:点生成netlist,点setup,修改路径为capture\\allegro.cfg所在路径,把allegro.cfg文件的位置选择你现在安装目录的文件位置。

2.spawning...\-pst-d\\\\#1error[alg0012]property\instanceu3:schematic1,page1(2.00,2.10).#2error[alg0012]property\instancec2:schematic1,page1(2.30,0.30).#17abortingnetlisting...pleasecorrecttheaboveerrorsandretry.错误表述:error[alg0012]property\footprint\missingfrompart:,(,apcbfootprint(jedec_typein allegro)isrequiredforallpartsinallegro.thereforeallpartswithoutthispropertyare listedbeforeabortingthenetlisting.youcanaddthepcbfootprintpropertybyselectingt hepartlisted,thenchoosingeditpropertiesfromthepop-upmenuandplacingavalue,suchasdip14_3,onthepart.在allegro中,每个器件都须要一个pcbPCB。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一、Capture生成netlist的时候报错:

1.Unable to open c:\Cadence\PSD_14.2\tools\capture\allegro.cfg for reading. Please correct the above error(s) to proceed

错误解释:

allegro.cfg文件找不到或allegro.cfg文件不能打开,这个问题的根源是,有可能每台电脑上安装Allegro的的位置不一样,allegro.cfg 文件找不到是理所当然的。

处理办法:

点生成netlist,点setup,修改路径为capture\allegro.cfg所在路径,把allegro.cfg文件的位置选择你现在安装目录的文件位置。

2. Spawning... "C:\Cadence\PSD_15.1\tools\capture\pstswp.exe" -pst -d "F:\gcht\CC2430\Projects\mysch.dsn" -n

"C:\CADENCE\PSD_15.1\TOOLS\PROJECTS" -c

"C:\Cadence\PSD_15.1\tools\capture\allegro.cfg" -v 3 -j

"CC2430_DEMO"

#1 Error [ALG0012] Property "PCB Footprint" missing from instance U3: SCHEMATIC1, PAGE1 (2.00, 2.10).

#2 Error [ALG0012] Property "PCB Footprint" missing from instance C2: SCHEMATIC1, PAGE1 (2.30, 0.30).

#17 Aborting Netlisting... Please correct the above errors and retry.

错误解释:

Error [ALG0012] Property "PCB Footprint" missing from part <Part Reference>: <Schematic> , <Page> (<LocationX> , <LocationY)>

A PC

B Footprint (JEDEC_TYPE in Allegro) is required for all parts in Allegro. Therefore all parts without this property are listed before aborting the netlisting. You can add the PCB Footprint property by selecting the part listed, then choosing Edit Properties from the pop-up menu and placing a value, such as dip14_3, on the part.

在Allegro中,每个器件都需要一个PCB封装。

所以在取消列出网表之前,软件会列出所有没有此项的器件。

你可以选择列出的器件添加PCB 封装,然后选择Edit Properties来编辑器件的值。

处理办法:

在导出Netlist 之前,只需要保证每个器件都是有封装的,且器件PCB Footprint值与对应的.dra封装文件名一致。

3. [DRC0011] Reference is invalid for this part

The reference for the part is invalid. For example, this occurs when a part reference like U?A has not been updated. Update the part reference。

Reference项不可随意修改。

4. Pin numbers do not match. Check device file.

原因:原理图中的晶振给了两个管脚,而其封装却是四个管脚。

原理图与PCB封装对应原则:

除了PCB Footprint的名字要写对以外,还有一点,就是原理图的元件的管脚数目一定要和封装的管脚数目必须一样。

这里说的管脚,包括了原理图中可能没有现实的Power Pins,不包括封装中的machanical pins;另外,原理图和封装的对应关系是依靠pin number来建立的,所以两者的相应的pin number一定要一样,而pin number是不是数字并没有关系。

5. ERROR(SPMHNI-191): Device/Symbol check error detected. WARNING(SPMHNI-337): Unable to load symbol 'HDR1X2' for device 'B2S_HDR1X2_B2S': WARNING(SPMHUT-127): Could not find padstack 57S40DP.

due to ERROR(SPMHDB-274): Unable to load flash symbol THS79X59X45X4X15 (Check PSMPATH setting for this symbol)."

原因:花焊盘Flash没有创建.fsm的symbol文件,或是该文件保存路径与.psm文件不一致。

二、Allegro导入netlist的时候报错can not find symbol:

出现Netrev succeeded即可,说明已没有error了,可以直接打开自动生成的.brd文件了。

但此时Updating Allegro PCB Editor Board

仍然会有红叉,貌似还有问题。

果然,在QuickPlace的时候,有一些

器件的Footprint无法Place,提示的错误原因是can not find symbol,不知所云。

有一种可能就是Allegro工作区的面积不够大,而QuickPlace放置的Footprint都位于Outline范围之外,因而如果工作区面积设置的不够大的话,会导致有一些器件的Footprint无法Place。

还有一种可能就是元件在原理图中的引脚数目与Footprint中的引脚数目不一致。

这是也会出现Netrev succeeded,同时有警告,但是同样会导致这些器件的Footprint无法Place。

第三种可能:在导入Netlist时会产生如下警告:

WARNING(SPMHNI-192): Device/Symbol check warning detected.

WARNING(SPMHNI-337): Unable to load symbol '8P4R_0402_CN_42' for device 'RESARR_IS_4/SM_8P4R_0402_CN_4_1': WARNING(SPMHUT-127): Could not find padstack 8P4R-0402_CN-42_BIGPAD.

即找不到PAD文件。

如果本身就没有PAD文件,则按照Datasheet上面引脚大小自己画一个;若有PAD文件,则应设置好路径:在PCB Editor 中Setup→User Preferences→Design_paths,设置padpath和psmpath;若对PAD文件进行过修改(包括重命名),则应在PCB Editor中Tools→Padstack,Replace或Refresh。

第四种可能:.dra封装文件有DRC错误。

此时在生成网表时,在Capture 的Session Log中只会有Warning而无Error,但QuickPlace仍无法放置该Footprint。

如何修改DRC错误。