标准单元库参数提取

cadence liberate 单元表征

cadence liberate 单元表征"Cadence Liberate"是一种用于半导体设计中的单元表征工具。

它被广泛应用于数字和模拟设计中,旨在帮助半导体行业快速而准确地建模和分析电路库。

以下是关于Cadence Liberate的详细介绍及其相关参考内容。

一、Cadence Liberate的特点和用途1. 特点:- Cadence Liberate提供了一个全面而灵活的环境,用于评估电路库在各种工艺过程和电压/温度/容忍度(PVT)条件下的性能。

- 它具有能够自动编辑和优化电路的能力,从而提供最佳性能和功耗的可能性。

- Cadence Liberate支持瞬态和静态分析,以验证电路的功能和时序行为。

- 该工具可以生成包括时序延迟、电流、功态和功耗在内的相关报告,用于电路库的建模和验证。

2. 用途:- 定时分析:Cadence Liberate可以评估电路中各个元件的时序性能,例如时钟延迟、数据传输延迟等。

这有助于设计人员在设计过程中提前发现和解决时序问题。

- 功耗优化:通过使用Cadence Liberate,设计人员可以分析电路库的功耗,识别功耗热点,并基于优化目标自动调整电路的逻辑结构和参数,以降低功耗。

- 可靠性分析:该工具可以评估电路在不同温度和工艺变化条件下的性能,帮助设计人员预测电路库在实际工作环境中的可靠性。

- 特性提取:Cadence Liberate可以提取电路库中各个元件的特性,例如电流、容忍度等。

这些特性可以用于电路的综合和仿真。

二、相关参考内容:(以下内容为虚构内容,无实际参考价值)1. 《Cadence Liberate用户手册》- 这本用户手册是Cadence官方提供的完整使用指南,详细介绍了Cadence Liberate的各个功能和用法。

它包括详细的步骤和示例,以帮助用户快速上手,并解决常见问题。

- 手册中包括了详细的命令和选项说明,以及用于生成报告和结果的示例代码。

标准单元库SCL

GDSII文件:包含了单元的版图信息, 用来合成最终的全芯片版图;

SCL

LEF文件: 本文件是SOC ENCOUNTER 环境下用于进行布局布线的文件, 该文件为布局布线工具提供了工 艺信息和各个单元的几何特性。

SCL

时序文件: 时序文件用于Design Complier及 其他数字综合工具进行门级综合,用 于SOC ENCOUNTER等布局布线工具 进行时序优化和调节。

SCL的设计

器件性能标注(Cell Characterization) Cell Characterization 是将标准单 元库的性能参数从实际电路中抽取出 来运用到设计工具(Design Kits)的一个 抽象化过程。这个过程相当于将工艺 的性能和实际的电路设计构建一个桥 梁。

SCL的设计

单元库的质量验证 1)保证数据的连续性; 2)保证时序的连续性; 3)模型行为检查; 4)反向标注检测; 5)布局布线验证; 6) DRC 和 LVS 检测。

SCL的设计

晶圆验证 晶圆验证是指在大规模生产前,将标 准单元器件在晶圆上进行试生产 (Tape-Out),然后将验证模块直接与被 测试器件的外部输入和输出端口相连 接。通常采用测试向量进行测试,因 为测试向量能够验证所有的逻辑功能 是否出错。

标准单元库 (SCL)

BJTU

内容 SCL的简介 SIMC18的SCL的介绍 SCL的设计

SCL

包括版图库、符号库、电路逻辑库等 包含了组合逻辑、时序逻辑、功能单 元和特殊类型单元 IC后端设计过程中的基础部分。一般 每个工艺厂商在每个工艺下都会提供 相应的标准单元。

SCL

用途:标准单元库用来为逻辑综合及

亚阈值数字标准单元库设计

亚阈值数字标准单元库设计

史兴荣;何进;张九柏;张子骥;贺雅娟

【期刊名称】《电子产品世界》

【年(卷),期】2018(025)011

【摘要】基于对0.18μm标准CMOS工艺的研究,本文设计了一套完备的电源电压为0.4 V的亚阈值数字标准单元库.设计流程包括工艺研究与方案设计、单元设计与物理实现、库文件的提取以及单元库验证.提出了传统沟道宽度调节与沟长偏置相结合的尺寸调整策略,有效增强PMOS管驱动并减小漏电流,提升库单元稳定性.利用ISCAS基准测试电路完成亚阈值标准单元库的验证,0.4 V电压下,相同设计,基于亚阈值数字标准单元库的设计的相比于基于商用库的设计,能耗减小20%以上,数据延时也有所减小,即亚阈值标准单元库性能明显优于商用库相比.

【总页数】5页(P38-42)

【作者】史兴荣;何进;张九柏;张子骥;贺雅娟

【作者单位】电子科技大学电子科学与工程学院成都 610054;电子科技大学电子科学与工程学院成都 610054;电子科技大学电子科学与工程学院成都 610054;电子科技大学电子科学与工程学院成都 610054;电子科技大学电子科学与工程学院成都 610054

【正文语种】中文

【相关文献】

1.亚100纳米级标准单元的可制造性设计 [J], 张培勇;严晓浪;史峥;高根生;马玥;陈晔

2.55nm工艺平台的标准单元库电路与版图设计研究 [J], 李向阳;胡晓明

3.基于施密特触发的高鲁棒性亚阈值标准单元 [J], 张跃军;韩金亮;张会红

4.采用标准单元库和阵列方法的混合模拟/数字ASIC设计 [J], 于宗光;林如霭;张宝元

5.面向近亚阈值的标准单元库设计方法 [J], 商新超;袁甲;张福海

因版权原因,仅展示原文概要,查看原文内容请购买。

SMIC

利用Catapult LB创建高层次综合工艺库中芯国际集成电路制造有限公司设计服务处夏克国[摘要]随着半导体制造工艺的持续缩小,在90纳米及以下的工艺中,时序、面积、功耗以及可制造性的问题都日趋复杂。

设计者希望在电子系统级 (ESL) 设计阶段,就能知道他们的设计在目标工艺下能否达到预期要求。

Mentor Graphics公司的Catapult Library Builder(以下简称Catapult LB),可以帮助半导体供应商提取高层次综合(high level synthesis)所需要的工艺库。

该工艺库能让客户把C/C++设计直接映射到特定的半导体工艺库,进行性能和面积的预估分析,尽早对设计进行优化和检验,增加设计成功的机会,同时该工艺库的建立也有利于半导体代工厂商对新的先进工艺的推广。

本文以中芯国际集成电路制造有限公司(SMIC) 90纳米的逻辑工艺库为例,介绍如何使用Catapult LB为半导体供应商的特定工艺建库,帮助客户实现从C/C++到GDSII的先进设计流程。

文章首先介绍Catapult LB 的建库流程,然后介绍Catapult LB针对ASIC工艺库不同的元件如标准单元、存储单元等建库的具体方法,最后介绍如何验证元件库并加快建库过程。

一、概述随着当代科技的发展,人们需要能支持无线宽带通信、日趋复杂的多媒体功能和海量存储的电子产品。

这就要求电子工程师们设计出日益强大的系统级芯片(SOC)来满足这些需求。

而随着芯片设计复杂度的不断增加,传统的人工编写并验证RTL代码所需的时间变得越来越长,容易引入各种错误;而且使用人工方法无法尝试所有可能的微架构和接口设计,无法得到面积和速度都最佳的设计。

Mentor公司的Catapult C 综合工具能很好的解决该问题,利用非定时的ANSI C++语言和ASIC供应商提供的工艺元件库,设计者能进行自动高层次综合,生成高品质RTL代码,速度最快可达到人工方式的20倍。

标准单元库参数提取

标准单元库参数提取参数提取是通过HSPICE对修改供电电压之后的标准单元重新进行时序和功耗的仿真。

由于需要对input transition time和output net capacitance的每一对组合点作HSPICE仿真,仿真工作量很大。

因此我们考虑写一个批处理程序调用HSPICE进行仿真。

这里我们采用微电子所开发的LPE工具进行参数提取仿真。

它是一个可以在UNIX环境运行的可执行文件(由于其C++源代码有问题,不能在LINUX环境下重新进行编译)。

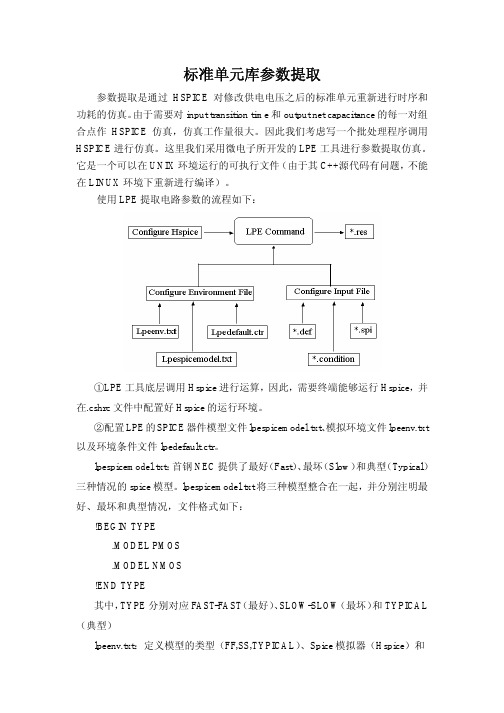

使用LPE提取电路参数的流程如下:①LPE工具底层调用Hspice进行运算,因此,需要终端能够运行Hspice,并在.cshrc文件中配置好Hspice的运行环境。

②配置LPE的SPICE器件模型文件lpespicemodel.txt、模拟环境文件lpeenv.txt 以及环境条件文件lpedefault.ctr。

lpespicemodel.txt:首钢NEC提供了最好(Fast)、最坏(Slow)和典型(Typical)三种情况的spice模型。

lpespicemodel.txt将三种模型整合在一起,并分别注明最好、最坏和典型情况,文件格式如下:!BEGIN TYPE.MODEL PMOS.MODEL NMOS!END TYPE其中,TYPE分别对应FAST-FAST(最好)、SLOW-SLOW(最坏)和TYPICAL (典型)lpeenv.txt:定义模型的类型(FF,SS,TYPICAL)、Spice模拟器(Hspice)和参数单位(如时间、电容、电压单位等),除模型类型根据用户需要制定外,一般采用缺省定义lpedefault.txt:定义环境条件,如电压、温度等,采用缺省定义即可③配置LPE的输入文件(以an02d0为例):an02d0.def(单元功能文件)、an02d0.spi(单元网表文件)和an02d0.condition(任务描述文件)。

提取单元格中的数值

提取单元格中的数值

当提取单元格中的数值时,可以使用不同的方法,具体取决于所使用的软件或工具。

在Excel中,可以使用函数来提取单元格中的数值。

例如,使用“=VALUE(A1)”函数可以提取A1单元格中的数值。

如果需要提取多个单元格中的数值,可以使用类似的函数来逐个提取。

另一种方法是使用文本函数,如LEFT、MID和RIGHT函数来提取特定位置的数值。

在编程语言中,可以使用字符串处理函数来提取单元格中的数值,例如在Python中可以使用正则表达式或者字符串切片来提取数值。

如果需要批量提取多个单元格中的数值,可以编写循环来逐个提取并存储数值。

总之,提取单元格中的数值需要根据具体情况选择合适的方法,并且需要确保提取的数值是准确的和完整的。

标准后端设计之单元设计参数说明(参考chart)

标准单元设计参数说明标准单元设计参数说明 (1)标准单元物理参数 (2)标准单元物理设计建议 (2)传播延时与转换延时 (3)衰减因子 (4)单元延时的计算 (4)时序约束 (5)建立时间 (5)保持时间 (5)恢复时间 (6)最小脉冲宽度 (6)功耗分析 (7)功耗计算 (7)例子:触发器DFF单元的功耗计算 (8)电源地轨线带 (10)布线通道的增加 (11)标准单元库的组成 (11)标准单元库提供的数据 (12)随着集成电路工艺技术的迅速发展,制造工艺向超深亚微米和纳米迈进。

系统级芯片(SOC)的规模越来越大,系统级芯片的设计越来越复杂。

尽可能使用已验证的可重复使用IP 库,是缩短设计周期,保证设计一次成功,降低系统级芯片成本的关键。

标准单元库是IP 库中最基本的一种,是设计的基础,对设计的性能、功耗、面积和成品率至关重要。

设计人员在设计之初,必须建立一套完整的与工艺线相对应的、内容丰富的、设计合理并且参数准确的标准单元库,这已成为加快设计的必要条件。

目前,标准单元库的设计面临着新的挑战。

首先,由于芯片集成度越来越大,功耗成为设计中需要着重考虑的因素之一;其次,从成本考虑,芯片的面积利用率需要进一步优化;其三,由于系统级芯片的工作频率越来越高,从而对芯片的速度提出了更高的要求。

目前,许多EDA 厂商推出了针对深亚微米技术带来的问题的解决方案与工具,但从现有的设计流程来说,对标准单元库进行针对深亚微米技术的优化仍是一个最关键的步骤。

然而出于成本的考虑,通常在一个标准单元库中很难同时面向高速、低功耗、面积进行优化。

对于标准单元库,人们总是非常关心这中间单元的一些参数,如单元延迟参数、扇出延迟特性、线延迟参数、最高振荡频率等等,因为只有清楚地知道了这些单元参数及特性之后,在利用这些库设计电路时才能把握设计灵活性。

在集成电路代工厂工艺特征尺寸不断缩小的同时,芯片的逻辑参数(时延、功耗、建立时间、保持时间等)也必须随工艺的不断进步而不断更新。

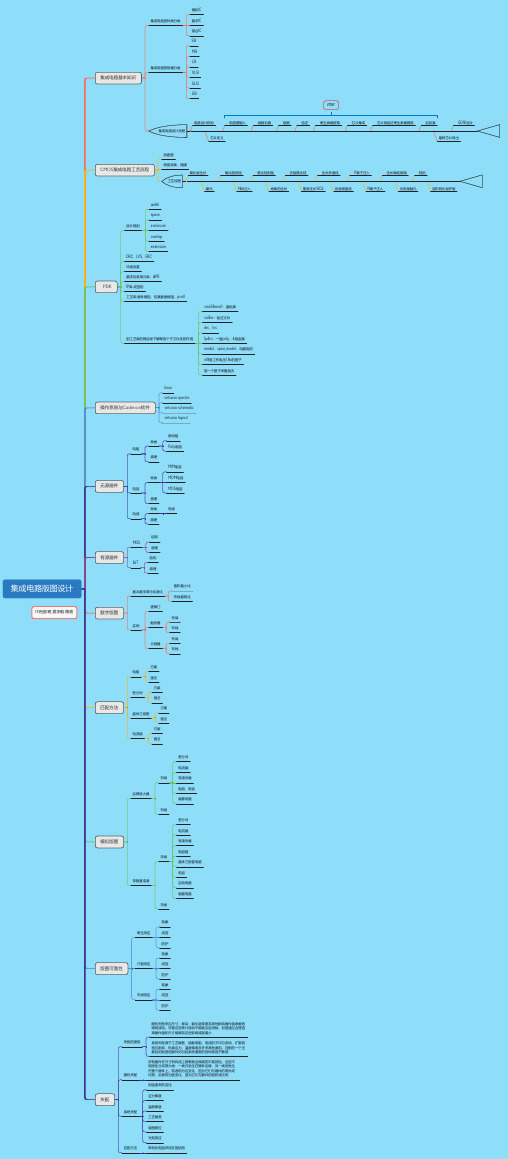

集成电路版图设计思维导图

集成电路版图设计集成电路基本知识集成电路按种类分类模拟IC数字IC混合IC集成电路按规模分类S SIM SIL SIV LSIU LSIG SI集成电路设计流程电路设计指标芯片定义电路图输入线路拟真版图验证寄生参数提取芯片集成芯片级验证寄生参数提取后拟真最终芯片导出G DSII流片P DKC MOS集成电路工艺流程剖面图俯视效果,掩膜工艺流程氧化层生长曝光氧化层刻蚀N阱注入氮化硅刻蚀场氧的生长去除氮化硅重新生长SIO2生长多晶硅刻蚀单晶硅P离子注入N离子注入生长磷硅玻璃光刻接触孔刻铝淀积钝化保护层PDK设计规则w idths pacee nclosureo verlape xtensionD RC、LVS、ERC环境设置数字标准单元库:APRI P库:成型的工艺库:器件模型、拟真数据模型、pcell到工艺库的根目录下解释各个子文件夹的作用s mic18mmrf:基础库c alibe:验证文件d rc,lvs1p4m,一层poly,4层金属m odel,spice_model,电路用的n18指工作电压1.8v的管子用一个管子来看层次操作系统与Cadence软件l inuxv irtuoso spectrev irtuoso schematicv irtuoso layout无源器件电阻种类阱电阻P oly电阻原理电容种类M IM电容M OM电容M OS电容原理电感种类电感原理有源器件M OS结构原理B JT结构原理数字版图基本数字单元标准化面积最小化布线最简化实例逻辑门触发器布局布线分频器布局布线匹配方法电阻方案画法差分对方案画法晶体三极管方案画法电流镜方案画法模拟版图运算放大器布局差分对电流镜有源负载电阻、电容偏置电路布线带隙基准源布局差分对电流镜有源负载电阻箱晶体三极管电路电容启动电路偏置电路布线版图可靠性寄生效应现象成因防护闩锁效应现象成因防护天线效应现象成因防护失配失配的原因随机失配来自尺寸、掺杂、氧化层厚度及其他影响器件值参数的微观波动。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

标准单元库参数提取

参数提取是通过HSPICE对修改供电电压之后的标准单元重新进行时序和功耗的仿真。

由于需要对input transition time和output net capacitance的每一对组合点作HSPICE仿真,仿真工作量很大。

因此我们考虑写一个批处理程序调用HSPICE进行仿真。

这里我们采用微电子所开发的LPE工具进行参数提取仿真。

它是一个可以在UNIX环境运行的可执行文件(由于其C++源代码有问题,不能在LINUX环境下重新进行编译)。

使用LPE提取电路参数的流程如下:

①LPE工具底层调用Hspice进行运算,因此,需要终端能够运行Hspice,并在.cshrc文件中配置好Hspice的运行环境。

②配置LPE的SPICE器件模型文件lpespicemodel.txt、模拟环境文件lpeenv.txt 以及环境条件文件lpedefault.ctr。

lpespicemodel.txt:首钢NEC提供了最好(Fast)、最坏(Slow)和典型(Typical)三种情况的spice模型。

lpespicemodel.txt将三种模型整合在一起,并分别注明最好、最坏和典型情况,文件格式如下:

!BEGIN TYPE

.MODEL PMOS

.MODEL NMOS

!END TYPE

其中,TYPE分别对应FAST-FAST(最好)、SLOW-SLOW(最坏)和TYPICAL (典型)

lpeenv.txt:定义模型的类型(FF,SS,TYPICAL)、Spice模拟器(Hspice)和

参数单位(如时间、电容、电压单位等),除模型类型根据用户需要制定外,一般采用缺省定义

lpedefault.txt:定义环境条件,如电压、温度等,采用缺省定义即可

③配置LPE的输入文件(以an02d0为例):an02d0.def(单元功能文件)、an02d0.spi(单元网表文件)和an02d0.condition(任务描述文件)。

单元功能文件an02d0.def:说明单元的输入、输出端口以及单元的功能函数,文件如下:

type:com;

input:A1,A2;

output:Z=A1*A2;

单元网表文件an02d0.spi:对Cadence导出的原始网表文件an02d0.cir进行修改(注释掉EQUIV、PARAM、+vss!,将PM、NM、vdd!、vss!分别改为P、N、vdd、vss)后保存。

an02d0.spi调用修改后的an02d0.cir,具体文件如下:.include’an02d0.cir’

.global vdd vss

x1 A1 A2 Z an02d0

*Z Z

*A1 A1

*A2 A2

.end

任务描述文件an02d0.condition:可以在文件中定义某一种参数的提取任务,也可以定义所有参数的提取任务,每种任务的描述格式基本相同,以提取A1到Z的上升沿延时为例,文件如下:

#Begin

#Table deley Rise Cell DRTemp2

#FromTo A1 Z

InputNetTransition 5 0.01 0.84 1.40 1.80 3.33

TotalOutputNetCapacitance 5 0.01 0.11 0.52 1.56 2.08

#End

注:Table表示输出查表模型的结果集,deley是参数类型(可以是power、setup、hold等),rise是沿(可以是fall),采样点为5×5,采样值为电压值和负载电容值。

④在UNIX环境命令行键入wave an02d0,执行LPE参数提取,参数结果存入文件an02d0.res

⑤改变lpeenv.txt的模型类型(SS、FF和TYPICAL),重新执行④,直至提取完所有情况、所有参数后为止。