数字电子技术 第六章 习题课

数字电子技术基础二版张克农6章习题解答.docx

6章习题题解6」集成施密特触发器及输入波形如图 题6.1所示,试画出输出妬的波形图。

施密 特触发器的阈值电平S+和U T -如图所示。

[解]集成施密特触发器输出如的波形如图解6」所示。

6.2图题6.2所示为数字系统屮常用的上电复位电路。

试说明其工作原理,并定性画岀 ⑷与心波形图。

若系统为高电平复位,如何改接电路?R\\C 丄I图题6.2[解]工作原理分析如下(1) 当Vcc 刚加上时,由于电容C 上的电压不能突变,尙为低电平,输出“()为低电平;随着电容充电,血按指数规律上升,当 QU T 时,输出仇()变为高电平,完成了低电平复位功 能。

波形如图解6.2所示。

(2) 若系统为高电平复位,仅将图中R, C 互换位置即可。

6.3图题6.3是用TTL 与非门、反相器和 肚积分电路组成的积分型单稳态触发器。

该电 路用图题6.3所示正脉冲触发,R<R试分析电路工作原理,画出w ()i> «i2和坎)的波形图。

JT图解6」1JT图解6.2图题6」[解]工作原理分析如下触发信号未到来时,⑷为低电平,输出问为高电平;正触发脉冲到来时,问I 翻为低电平 此时由于均2仍为高电平,输出如为高电平不变,电容通过尺放电,当⑷2下降到S 时 仙 仍为高电平),输出“()翻为高电平,暂稳态过程结束。

”()i 、”】2和〃()的波形见图解6.3。

图题6.51 M O1R U 12 Ln __ 1 --- ]・&)—w o"IG|C H 5Ot6.4集成单稳态触发器74121组成的延时电路如图丿 (1) 计算输出脉宽的调节范圉; (2) 电位器旁所串电阻有何作用?图题6.4[解]⑴ 输出脉宽:d=0fi7(R + RQ ,分别代入Rw=O 和22kQ 计算,可得心 的调节范围为:3.6mS</w <19mS o(2)电阻/?起保护作用。

若无R,当电位器 调到零时,若输出由低变高,则电容C 瞬间 相当于短路,将直接加于内部门电路输 出而导致电路损坏。

数字电子技术课后习题答案

❖ 3.21 用8选1数据选择器74151设计一个组合 逻辑电路。该电路有3三个输入逻辑变量A、B、 C和一个工作状态控制变量M。当M=0时电路 实现“意见一致”功能( A、B、C状态一致 时输出为1,否则输出为0),而M=1时电路 实现“多数表决”功能,即输出与A、B、C中 多数的状态一致。

数字电子技术作业

第一章数字逻辑基础 第二章逻辑门电路 第三章组合逻辑电路 第四章触发器 第五章时序逻辑电路 第六章脉冲波形的产生与整形 第七章半导体存储器 第八章可编程逻辑器件 第九章数/模和模/数转换器

1.12 写出下图所示各逻辑图的输出函数表达式,列 出它们的真值表。

F1 F4

F2

F3

解: F1 AB F2 A B F3 BC

ABACBC

BC

A

00 01 11 10

00

1

0

1

11

0

1

0

Y ABC

❖ 3.13某医院有一、二、三、四号病室4间,每室设有 呼叫按钮,同时在护士值班室内对应的装有一号、 二号、三号、四号4个指示灯。

❖ 现要求当一号病室的按钮按下时,无论其它病室的 按钮是否按下,只有一号灯亮。当一号病室的按钮 没有按下而二号病室的按钮按下时,无论三、四号 病室的按钮是否按下,只有二号灯亮。当一、二号 病室的按钮都未按下而三号病室的按钮按下时,无 论四号病室的按钮是否按下,只有三号灯亮。只有 在一、二、三号病室的按钮均未按下四号病室的按 钮时,四号灯才亮。试用优先编码器74148和门电路 设计满足上述控制要求的逻辑电路,给出控制四个 指示灯状态的高、低电平信号。

Y CBA CB CA CBACB CA

《数字电子技术基础》课后习题答案

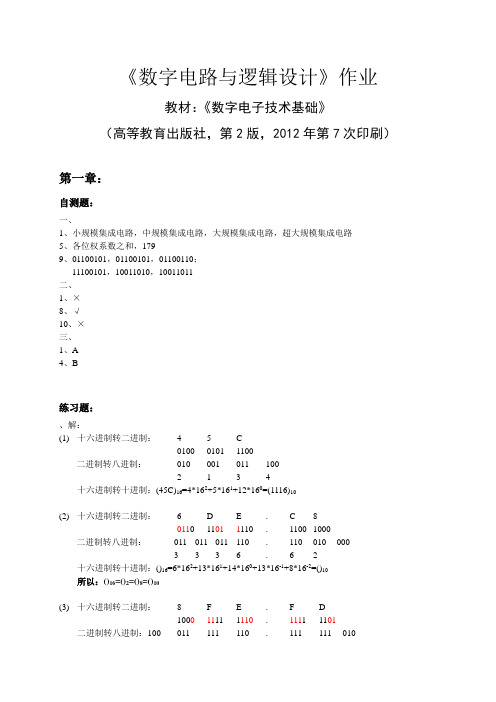

《数字电路与逻辑设计》作业教材:《数字电子技术基础》(高等教育出版社,第2版,2012年第7次印刷)第一章:自测题:一、1、小规模集成电路,中规模集成电路,大规模集成电路,超大规模集成电路5、各位权系数之和,1799、01100101,01100101,01100110;11100101,10011010,10011011二、1、×8、√10、×三、1、A4、B练习题:、解:(1) 十六进制转二进制: 4 5 C0100 0101 1100二进制转八进制:010 001 011 1002 13 4十六进制转十进制:(45C)16=4*162+5*161+12*160=(1116)10(2) 十六进制转二进制: 6 D E . C 80110 1101 1110 . 1100 1000 二进制转八进制:011 011 011 110 . 110 010 0003 3 3 6 . 6 2十六进制转十进制:()16=6*162+13*161+14*160+13*16-1+8*16-2=()10所以:()16=()2=()8=()10(3) 十六进制转二进制:8 F E . F D1000 1111 1110. 1111 1101二进制转八进制:100 011 111 110 . 111 111 0104 3 7 6 . 7 7 2十六进制转十进制:(8FE.FD)16=8*162+15*161+14*160+15*16-1+13*16-2=(2302.98828125)10 (4) 十六进制转二进制:7 9 E . F D0111 1001 1110 . 1111 1101二进制转八进制:011 110 011 110 . 111 111 0103 6 3 6 . 7 7 2十六进制转十进制:(79E.FD)16=7*162+9*161+14*160+15*16-1+13*16-2=(1950. 98828125)10 所以:()16.11111101)2=(363)8=(1950.98828125)10、解:(74)10 =(0111 0100)8421BCD=(1010 0111)余3BCD(45.36)10 =(0100 0101.0011 0110)8421BCD=(0111 1000.0110 1001 )余3BCD(136.45)10 =(0001 0011 0110.0100 0101)8421BCD=(0100 0110 1001.0111 1000 )余3BCD (374.51)10 =(0011 0111 0100.0101 0001)8421BCD=(0110 1010 0111.1000 0100)余3BCD、解(1)(+35)=(0 100011)原= (0 100011)补(2)(+56 )=(0 111000)原= (0 111000)补(3)(-26)=(1 11010)原= (1 11101)补(4)(-67)=(1 1000011)原= (1 1000110)补第二章:自测题:一、1、与运算、或运算、非运算3、代入规则、反演规则、对偶规则二、2、×4、×三、1、B3、D5、C练习题:2.2:(4)解:(8)解:2.3:(2)证明:左边=右式所以等式成立(4)证明:左边=右边=左边=右边,所以等式成立(1)(3)2.6:(1)2.7:(1)卡诺图如下:BCA00 01 11 100 1 11 1 1 1所以,2.8:(2)画卡诺图如下:BC A 0001 11 100 1 1 0 11 1 1 1 12.9:如下:CDAB00 01 11 1000 1 1 1 101 1 111 ×××10 1 ××2.10:(3)解:化简最小项式:最大项式:2.13:(3)技能题:2.16 解:设三种不同火灾探测器分别为A、B、C,有信号时值为1,无信号时为0,根据题意,画卡诺图如下:BC00 01 11 10A0 0 0 1 01 0 1 1 1第三章:自测题:一、1、饱和,截止7、接高电平,和有用输入端并接,悬空;二、1、√8、√;三、1、A4、D练习题:、解:(a)Ω,开门电阻3kΩ,R>R on,相当于接入高电平1,所以(e) 因为接地电阻510ΩkΩ,R<R off,相当于接入高电平0,所以、、解:(a)(c)(f)、解: (a)、解:输出高电平时,带负载的个数2020400===IH OH OH I I N G 可带20个同类反相器输出低电平时,带负载的个数78.1745.08===IL OL OL I I NG反相器可带17个同类反相器EN=1时,EN=0时,根据题意,设A为具有否决权的股东,其余两位股东为B、C,画卡诺图如下,BC00 01 11 10A0 0 0 0 01 0 1 1 1则表达结果Y的表达式为:逻辑电路如下:技能题::解:根据题意,A、B、C、D变量的卡诺图如下:CD00 01 11 10AB00 0 0 0 001 0 0 0 0 11 0 1 1 1 10 0 0 0 0电路图如下:第四章:自测题:一、2、输入信号,优先级别最高的输入信号7、用以比较两组二进制数的大小或相等的电路,A>B 二、 3、√ 4、√ 三、 5、A 7、C练习题:4.1;解:(a),所以电路为与门。

数字电子技术第6章 时序逻辑电路

RD—异步置0端(低电平有效) 1 DIR—右移串行输入 1 DIL—左移串行输入 S0、S1—控制端 1 D0D1 D2 D3—并行输入

《数字电子技术》多媒体课件

山东轻工业学院

4、扩展:两片74LS194A扩展一片8位双向移位寄存器

《数字电子技术》多媒体课件

山东轻工业学院

例6.3.1的电路 (P276) 74LS194功能 S1S0=00,保持 S1S0=01,右移 S1S0=10,左移 S1S0=11,并入

(5)状态转换图

《数字电子技术》多媒体课件

山东轻工业学院

小结

1、时序逻辑电路的特点、组成、分类及描述方法; 2、同步时序逻辑电路的分析方法; 课堂讨论: 6.1,6.4

《数字电子技术》多媒体课件

山东轻工业学院

6.3 若干常用的时序逻辑电路

寄存器和移位寄存器 时序 逻辑电路 计数器 顺序脉冲发生器 序列信号发生器

移位寄存器不仅具有存储功能,且还有移位功能。 可实现串、并行数据转换,数值运算以及数据处理。 所谓“移位”,就是将寄存器所存各位数据,在每个移 位脉冲的作用下,向左或向右移动一位。

2、类型: 根据移位方向,分成三种:

左移 寄存器 (a) 右移 寄存器 (b) 双向 移位 寄存器 (c)

《数字电子技术》多媒体课件

学习要求 :

* *

自学掌握

1. 掌握寄存器和移位寄存器的概念并会使用; 2. 掌握计数器概念,熟练掌握中规模集成计数器74161 和74160的功能,熟练掌握用160及161设计任意进制计 数器的方法。

《数字电子技术》多媒体课件

山东轻工业学院

6.3.1寄存器和移位寄存器

一、寄存器

寄存器是计算机的主要部件之一, 它用来暂时存放数据或指令。

《数字电子技术》课件第六章

Q1nQ2n Q3n

C Q3n

根据方程可得出状态迁移表, 如表 6-1 所示, 再由 表得状态迁移图, 如图 6-2 所示。 由此得出该计数器为 五进制递增计数器, 具有自校正能力(又称自启动能力)。

所谓自启动能力, 指当电源合上后, 无论处于何种状 态, 均能自动进入有效计数循环; 否则称其无自启动能力。

J 3 Q1nQ2n

___ ___

次态方程和时钟方程为 Q1n1 Q3n Q1n

___

Q2n1 Q2n

K3 1 CP1 CP CP2 CP1

___

Q3n1 Q1nQ2n Q3n

CP3 CP

由于各触发器仅在其时钟脉冲的下降沿动作,其余 时刻均处于保持状态,故在列电路的状态真值表时必须 注意。

(1) 当现态为000时,代入Q1和Q3的次态方程中,可

知在CP作用下Qn+1=1,

Q n 1 3

0

,

由于此时CP2=Q1,

Q1由

0→1 产生一个上升沿,用符号↑表示,故Q2处于保持状

态, 即 Q2n1 Q2n 0 。 其次态为 001。

(2)

当现态为

001

时,

Q n1 1

0,

Q n1 3

0

,此

z Q1n

(2) 列出状态真值表。 假定一个现态, 代入上述次态方程中得相应的次态, 逐个假定列表表示即得相应的状态真值表, 如表 6-3 所示。

(3) 画出状态迁移图。 由状态真值表可得出相应的状态图, 如图 6-8 所示。

图 6-8 例 3 状态迁移图

(4) 画出给定输入x序列的时序图。 根据给出的x序列, 由状态迁移关系可得出相应的次 态和输出。 如现态为 00, 当x=1 时, 其次态为 01, 输出 为0; 然后将该节拍的次态作为下一节拍的现态, 根据输 入x和状态迁移关系得出相应的次态和输出, 即 01 作为第 二节拍的现态。 当x=0 时, 次态为 11, 输出为 0, 如此 作出给定x序列的全部状态迁移关系, 如下所示, 其箭头 表明将该节拍的次态作为下一节拍的现态。

数字电子技术题目第六章

数字电子技术题目第六章第六章脉冲波形的变换与产生一.填空题1.用555构成的多谐振荡器如图所示,则其振荡频率为f=Hz,占空比q=2.用555构成的多谐振荡器如图所示,则其振荡频率为f=Hz,占空比q=。

3.用555构成的多谐振荡器如图4所示,其中R1=2kΩ,R2=2kΩ,C=10μF,则其振荡频率为f=Hz,占空比q=4.用555定时器构成的多谐振荡器如图2所示,其中R=80kΩ,C=100μF,则输入信号为(选择“高电平”还是“低电平”)时,灯泡L亮;灯泡亮的时间为秒。

二.简答题&计算题1.已知555定时器组成的单稳态触发器如图4所示,试画出电容器上电压波形vc和输出端vo的波形,并计算暂稳态的脉冲宽度。

其中R=10kΩ,C=10μF,要求写出分析计算过程。

uc2.已知如图4所示555定时器组成的施密特触发器中,VCC=9V,试画出输出端vo的波形,要求写出分析计算过程。

3.已知555定时器组成的单稳态触发器如图7所示,试画出电容器上电压波形vc和输出端vo 的波形,并计算脉冲宽度tw。

其中R=20kΩ,C=10μF,要求写出分析计算过程。

uc4.已知如图8所示555定时器组成的施密特触发器中,VCC=9V,试画出输出端vo的波形,要求写出分析计算过程。

(5分)答案一.填空题4.76,2/32.86,3/523.8,2/3低电平,8.8s二.简答题&计算题1.解:tW=1.1RC=1.1×10×103×10×10-6=0.11s2.解:∵∴∴………2分3.解:tW=1.1RC=1.1×20×103×10×10-6=0.22s4.解:∵∴∴。

数字电子技术第6章自测练习及习题解答

自测练习(6.1)1.4位寄存器需要()个触发器组成。

2.图6-1中,在CP()时刻,输入数据被存储在寄存器中,其存储时间为()。

3.在图6-4中,右移操作表示数据从()(FF0,FF3)移向(FF0,FF3)。

4.在图6-7中,当/SHIFT LOAD为()电平时,寄存器执行并行数据输入操作;5.74LS194的5种工作模式分别为()。

6.74LS194中,清零操作为()(同步,异步)方式,它与控制信号S1、S1()(有关,无关)。

7.74LS194中,需要()个脉冲可并行输入4位数据。

8.74LS194使用()(上边沿,下边沿)触发。

9.为了将一个字节数据串行移位到移位寄存器中,必须要()个时钟脉冲。

10.一组数据10110101串行移位(首先输入最右边的位)到一个8位并行输出移位寄存器中,其初始状态为11100100,在两个时钟脉冲之后,该寄存器中的数据为:(a)01011110 (b)10110101 (c)01111001 (d)001011011.42.上升沿,1个CP周期3.FF0,FF34.低5.异步清零,右移,左移,保持,并行置数6.异步,无关7.18.上边沿9.810.(c)01111001自测练习(6.2)1.为了构成64进制计数器,需要()个触发器。

2.2n进制计数器也称为()位二进制计数器。

3.1位二进制计数器的电路为()。

4.使用4个触发器进行级联而构成二进制计数器时,可以对从0到()的二进制数进行计数。

5.如题5图中,()为4进制加法计数器;()为4进制减法计数器。

题5图(a)Q0 Q1CP 111J>C1 FF01K1J>C1 FF11K题5图(b )6.一个模7的计数器有( )个计数状态,它所需要的最小触发器个数为( )。

7.计数器的模是( )。

(a )触发器的个数(b )计数状态的最大可能个数(b )实际计数状态的个数 8.4位二进制计数器的最大模是( )。

数字电路答案第六章

第六章可编程逻辑器件PLD可编程逻辑器件PLD是由用户借助计算机和编程设备对集成电路进行编程,使之具有预定的逻辑功能,成为用户设计的ASIC芯片。

近年来,可编程逻辑器件从芯片密度上、速度上发展相当迅速,已成为集成电路的一个重要分支。

本章要求读者了解PLD器件的工作原理,掌握用可编程逻辑器件设计数字电路的方法。

为掌握使用电子设计自动化和可编程逻辑器件设计电路系统的后续课程打下良好的基础。

第一节基本知识、重点与难点一、基本知识(一)可编程逻辑器件PLD基本结构可编程逻辑器件PLD包括只读存储器ROM、可编程只读存储器PROM、可编程逻辑阵列PLA、可编程阵列逻辑PAL、通用阵列逻辑GAL和可擦写编程逻辑器件EPLD等。

它们的组成和工作原理基本相似,其基本结构由与阵列和或阵列构成。

与阵列用来产生有关与项,或阵列把所有与项构成“与或”形式的逻辑函数。

在数字电路中,任何组合逻辑函数均可表示为与或表达式,因而用“与门-或门”两级电路可实现任何组合电路,又因为任何时序电路是由组合电路加上存储元件(触发器)构成的,因而PLD的“与或”结构对实现数字电路具有普遍意义。

(二)可编程逻辑器件分类1.按编程部位分类PLD有着大致相同的基本结构,根据与阵列和或阵列是否可编程,分为三种基本类型:(1)与阵列固定,或阵列可编程;(2)与或阵列均可编程;(3)与阵列可编程,或阵列固定。

2.按编程方式分类(1)掩膜编程;(2)熔丝与反熔丝编程;(3)紫外线擦除、电可编程;(4)电擦除、电可编程;(5)在系统编程(Isp)。

(三)高密度可编程逻辑器件HDPLD单片高密度可编程逻辑器件HDPLD(High Density Programmable Logic Device)芯片内,可以集成成千上万个等效逻辑门,因此在单片高密度可编程逻辑器件内集成数字电路系统成为可能。

HDPLD器件在结构上仍延续GAL的结构原理,因而还是电擦写、电编程的EPLD 器件。