数模混合电路设计的难点

模电重难点

4.安排习题课,讲解典型例题,引导学生掌握分析问题、解决问题的方法

5.加强辅导,安排每周有半天的答疑。

2

掌握双极型晶体管和MOS场效应管组成的三种基本组态放大器交流等效电路分析法。直流工作点计算,交流指标计算,频率响应的概念和基本分析方法。

3

掌握差分放大电路的电路组成、工作原理、小信号的分析方法

序号

课程教学重点与难点

主要Байду номын сангаас决办法

1

掌握晶体二极管、双极型晶体管和场效应管的半导体器件的工作原理。

解决办法:

1.讲课重点突出,把握好精讲细讲分寸,加强启发式、讨论式教学方法的运用,加强教师和学生的互动。

2.将EDA软件仿真(Electronics Workbench、Multsim等)引入课堂教学,提高学生对难点部分的感性认识。

4

掌握多级放大器的工作原理和分析方法。

5

掌握使用电子设计自动化软件multisim分析晶体管电路的基本方法。

6

掌握负反馈的概念。掌握四种基本类型的负反馈放大器的电路结构、工作原理、基本分析方法。

7

掌握负反馈对放大电路性能的影响及深度负反馈放大器的工程估算方法。

8

掌握集成运放的组成和基本特点。

掌握集成运放中常用的镜像电流源、有源负载放大器、互补输出电路、直接耦合多级放大器等基本单元电路的结构、工作原理和分析方法。

掌握理想运放典型应用电路的结构、工作原理和分析方法。

掌握乙类放大器的电路组成、工作原理、分析方法。

掌握整流、滤波、稳压电路的原理、性能指标和设计方法。

数模混合SOC的仿真验证的开题报告

数模混合SOC的仿真验证的开题报告题目:数模混合SOC的仿真验证1. 研究背景和意义随着电子技术的不断发展,单一的数字电路已经不能满足人们对于高性能、低功耗、小型化等方面的需求,混合信号芯片已经成为未来发展的趋势。

数模混合SOC(system on chip)是一种能够实现数字信号处理和模拟信号处理的集成电路系统,不仅可以实现模拟信号的处理,还可以集成数字信号的处理和处理器单元,实现更加复杂和高性能的功能。

数模混合SOC在各个领域拥有广泛的应用,例如物联网、医疗器械、汽车电子等。

为了保证系统的正确性、稳定性和可靠性,需要进行仿真验证,以便找出设计上存在的问题并加以解决。

因此,对数模混合SOC的仿真验证技术的研究具有重要的理论和实际意义。

2. 研究内容和方法本文的研究内容是数模混合SOC的仿真验证技术。

主要包括以下几个方面:(1)数模混合SOC的系统架构和设计流程(2)数模混合SOC的设计语言和仿真工具(3)数模混合SOC的仿真验证流程和方法(4)数模混合SOC的性能评估和结果分析以上四个方面,将会在本文中进行详细探讨。

其中,主要采用文献研究、实验仿真等方法进行研究。

3. 预期结果通过对数模混合SOC的仿真验证技术进行研究,将会取得以下预期结果:(1)对数模混合SOC的系统架构和设计流程有更加全面的认识。

(2)能够掌握数模混合SOC的设计语言和仿真工具的使用方法。

(3)对数模混合SOC的仿真验证流程和方法有更加深入的了解。

(4)对数模混合SOC的性能评估和结果分析具备一定的能力。

4. 论文结构与进度安排本文的结构安排如下:第一章:绪论第二章:数模混合SOC的系统架构和设计流程第三章:数模混合SOC的设计语言和仿真工具第四章:数模混合SOC的仿真验证流程和方法第五章:数模混合SOC的性能评估和结果分析第六章:结论与展望预计完成时间安排:2021年9月:文献综述和初步研究2021年11月:深入研究和实验仿真2022年1月:文章撰写、修订和定稿5. 参考文献[1] 陈信宏. 数模混合SOC设计[M]. 电子工业出版社, 2016.[2] Navabi Z. Mixed-Signal and DSP Design Techniques[M]. John Wiley & Sons, 2003.[3] Liu H, Li W. The Design of Low-Power High-Accuracy Hybrid Delta-Sigma Modulator for ADC of MEMS Gyroscope[J]. IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences, 2012, E95.A(2): 712-715.[4] Liu X, Zhao T, Shang X, et al. A low-power hybrid ADC based on continuous-time Delta-Sigma modulation and SAR conversion[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2018,65(3): 963-972.[5] Cheng M H, Luo H J, Shen J T, et al. Design of a High-PrecisionMixed-Signal Processor Based on FPGA[J]. IEEE Transactions on VeryLarge Scale Integration (VLSI) Systems, 2013, 21(8): 1505-1512.。

数模混合仿真电路功耗

数模混合仿真电路功耗

数模混合仿真电路功耗是指在数模混合电路中,数字电路和模拟电路所消耗的总功率。

它是评估数模混合电路性能的重要指标之一,因为功耗直接影响到电路的效率、可靠性和散热能力。

在进行数模混合仿真电路功耗分析时,需要考虑数字电路和模拟电路的功耗分别进行计算。

数字电路的功耗主要包括静态功耗和动态功耗两部分。

静态功耗是指在电路处于静态状态时所消耗的功率,主要由漏电流引起。

动态功耗是指在电路进行逻辑操作时所消耗的功率,主要由开关活动和短路电流引起。

模拟电路的功耗主要由电路中的有源元件(如晶体管、运算放大器等)所消耗的功率组成。

模拟电路的功耗通常比数字电路的功耗低,但在高精度模拟电路中,功耗仍然是一个重要的考虑因素。

为了降低数模混合仿真电路的功耗,可以采取以下措施:

1. 优化电路设计:通过合理选择器件、优化电路布局和布线等措施,可以降低电路的功耗。

2. 降低工作频率:降低电路的工作频率可以减少开关活动和短路电流,从而降低功耗。

3. 采用低功耗器件:选择低功耗的数字器件和模拟器件可以显著降低电路的功耗。

4. 采用节能技术:如动态电压缩放(DVS)、时钟门控(Clock Gating)等节能技术可以有效降低电路的功耗。

总之,数模混合仿真电路功耗是数模混合电路设计中需要重点考虑的因素之一。

通过合理的电路设计和采用节能技术,可以降低电路的功耗,提高电路的效率和可靠性。

数模混合仿真设计流程详解

数模混合仿真设计流程详解1.确定仿真对象与目标:首先确定要仿真的对象是什么,比如电路、通信系统等。

然后确定仿真的目标,比如系统的性能评估、故障模拟等。

2.收集仿真所需的数据:根据仿真对象和目标,收集所需的数据,包括电路元件的参数、信号源的特性等。

3.建立数字模型:根据收集到的数据,建立数字系统的数学模型。

这个模型可以是差分方程、状态空间方程等形式。

还可以使用一些仿真软件来建立模型,比如MATLAB、SPICE等。

4.建立模拟模型:根据仿真对象和目标,建立模拟系统的模型。

这个模型可以是电路图、信号流图等形式。

5. 进行系统级仿真:将数字模型和模拟模型结合起来,进行系统级的仿真。

可以使用专门的混合仿真软件,比如Multisim、PSPICE等。

6.分析仿真结果:对仿真结果进行分析,比如观察系统的响应、性能指标等。

根据分析结果,对系统进行优化或改进。

7.优化系统设计:根据仿真结果,对系统进行优化设计。

可以进行参数调整、电路结构改进等操作。

8.重新进行仿真:在优化设计之后,重新进行仿真,以验证优化效果。

9.验证仿真结果:将仿真结果与实际系统进行验证,比较其一致性。

如果两者一致,则说明仿真模型是可靠的。

10.提出改进方案:如果仿真结果与实际系统存在差异,根据差异提出改进方案,并重新进行仿真与验证。

11.输出仿真报告:根据仿真结果,编写仿真报告,包括仿真目标、仿真方法、仿真结果、分析与改进等内容。

总结起来,数模混合仿真设计流程包括确定仿真对象与目标、收集仿真所需数据、建立数字模型与模拟模型、进行系统级仿真、分析仿真结果、优化系统设计、重新进行仿真、验证仿真结果、提出改进方案和输出仿真报告。

这个流程是一个迭代的过程,需要根据实际情况进行调整和修改。

单片机毕设制作过程中遇到的困难及解决方法

单片机毕设制作过程中遇到的困难及解决方法引言单片机是电子信息类专业学生常见的毕业设计项目之一。

在单片机毕设制作的过程中,学生可能会遇到各种困难和问题,需要通过不断的尝试和解决来完成设计和实现。

本文将从硬件和软件两个方面,详细介绍单片机毕设制作过程中可能遇到的困难,并提供相应的解决方法。

硬件方面的困难及解决方法1. 电路设计困难在进行单片机毕设制作时,首先需要进行电路设计。

对于初学者来说,电路设计可能是一个较大的挑战。

其中常见的问题包括如何选择合适的元器件、如何进行连线布局等。

解决方法:•学习相关教材或网络教程,了解基本电路原理和常用元器件。

•参考已有的开源电路设计,借鉴其经验。

•寻求老师或同学的帮助,在实践中不断积累经验。

2. 元器件选型困难在进行单片机毕设制作时,选择合适的元器件对于整个项目的成功至关重要。

然而,市场上存在众多不同类型、不同品牌的元器件,初学者可能会感到困惑。

解决方法:•研究相关的电子元器件手册,了解各种元器件的特性和性能参数。

•参考已有的开源项目或论文,查看其所使用的元器件型号。

•咨询专业人士,寻求他们对于不同元器件的建议和意见。

3. 硬件故障排查困难在单片机毕设制作过程中,可能会出现硬件故障导致系统无法正常工作。

初学者可能会面临如何准确找出故障点以及修复问题的挑战。

解决方法:•仔细检查电路连接是否正确,是否存在短路或接触不良等问题。

•使用示波器、逻辑分析仪等测试设备进行信号测量和分析。

•检查元器件是否损坏或失效,并进行更换或修复。

软件方面的困难及解决方法1. 编程语言选择困难在单片机毕设制作中,选择合适的编程语言对于软件开发至关重要。

然而,市场上存在多种编程语言可供选择,初学者可能会感到困惑。

解决方法:•研究各种编程语言的特点和适用范围,根据项目需求选择合适的语言。

•参考已有的开源项目或论文,查看其所使用的编程语言。

•咨询专业人士,寻求他们对于不同编程语言的建议和意见。

2. 编程技术难题在进行单片机毕设制作时,可能会遇到各种编程技术难题。

配电工程难点问题方案

配电工程难点问题方案一、难点问题:1. 设备选择和电气设计问题在配电工程中,设备的选择和电气设计是一个重要的环节。

配电设备的选型和电气设计需要考虑到用电负荷、电气系统的可靠性、安全性等因素,这需要对各种配电设备和电气设计方案进行比较和分析,才能选择出最合适的设备和方案。

2. 施工现场环境复杂问题配电工程的施工现场环境通常比较复杂,例如现场的环境复杂、施工条件受限、地形地貌复杂等因素都会给配电工程带来很大的挑战。

对这些问题的解决需要有丰富的施工经验和专业的技术水平。

3. 设备安装和调试问题配电设备的安装和调试是一个繁琐的工作,这需要对设备的技术要求较高,对现场施工条件也有一定的要求。

特别是高压设备的安装和调试,需要有丰富的经验和技术水平,否则会对工程的质量和安全构成严重的隐患。

4. 工程验收和交付问题配电工程的验收和交付是工程的最后一道关口,这需要进行复杂的检测和测试工作,对工程的质量和安全进行全面的评估,确保工程能够按质按量交付使用。

工程验收和交付环节的不严谨将会对工程的运行和维护带来较大的隐患。

二、方案:1. 设备选择和电气设计问题方案:(1)建立完善的配电设备选型和电气设计标准,确保设备的性能符合要求,电气设计方案的合理性和安全性。

(2)充分考虑用电负荷、电气系统的可靠性和安全性等因素,在选择配电设备和电气设计方案时仔细比较和分析各种方案的优缺点,确保最终选择出最合适的设备和方案。

2. 施工现场环境复杂问题方案:(1)做好施工前的环境调查和分析,对施工现场的环境进行全面的评估,确保施工条件的合理性和安全性。

(2)充分发挥施工人员的专业技术水平和施工经验,合理分配施工人员和施工设备,确保施工工期和质量的有效控制。

3. 设备安装和调试问题方案:(1)制定严格的设备安装和调试标准,确保设备的安装和调试程序的合理性和严谨性。

(2)充分发挥施工人员的专业技术水平和经验,确保设备的安装和调试工作的高效性和严谨性,避免出现质量和安全问题。

数模混合电路设计1

TR R TC ∂∂≡1依赖于迁移率、阈值电压、栅氧化层电容,因而精度差依赖于源漏电压,因而有较强的非线性特征用于非关键路径或具有自动调整的电路(负反馈环)方块数的计算方法()1−⎥⎦⎤⎢⎣⎡−−≈DS th GS ox ds V V V L W C r μ0.560.514+0.56*4+0.5*2=17.24高频时应当考虑趋肤效应孤立导体低频高频导体地低频高频趋肤深度:电流密度降低到表面电流密度的1/e 时的厚度1/f δπμρ=dc lR wtρ=2()hf lR w t ρδ=+22ac dchfR R Rκ=+ 1.44κ≈任何两个连线层都可以用作平板电容,层间绝缘介质较厚,0.5~1.0微米, 5e -5 pF/um 2有的工艺有专门的电容工序(绝缘介质薄)底层极板与别的连线层、特别是衬底间的寄生电容通常不可忽略,约占10-30%用于非关键路径或具有自动调整的电路(负反馈环)d衬底WL)22()2)(2(dWLL W d L d W dC ++≈++≈εε电容三明治结构同层导体nF j j V C C )/1(0φ−≈n =1/3,缓变结n =1/2,突变结φφTC V n TC n TC F Si ⎥⎦⎤⎢⎣⎡−−−≈/11)1(TC ~200ppm/°C 较大的反偏电压TC ~100ppm/°C 零电压偏置1-5fF/um 2含寄生电阻确保Vgs>>阈电压,保证工作在强反型,否则损耗大电容值很小,而且非线性严重R dsR ds /2R ds /24R ds特别注意: 极性Vin VoutVAGCcntlCgate drain sourceN+N+pWell考虑沟道中电荷层的厚度(capMod=3),相当于对栅氧化层电容串联了一个电容.,ox cen ox effox cenC C C C C =+SicenDCC X ε=积累/耗尽工作区0.25161exp [cm]3210gs bs fb sub DCdebye cde ox V V V N X L a T −⎡⎤−−⎛⎞=⎢⎥⎜⎟×⎝⎠⎢⎥⎣⎦反型工作区()10.7,7421.9101 [cm]2gst eff th fb B DCoxVV v X T −−⎡⎤⎛⎞+−−Φ⎢⎥⎜⎟=×+⎢⎥⎜⎟⎝⎠⎢⎥⎣⎦简单情形(地/ 单一导体)TWH⎥⎥⎦⎤⎢⎢⎣⎡⎥⎥⎦⎤⎢⎢⎣⎡⎟⎠⎞⎜⎝⎛+⎟⎠⎞⎜⎝⎛++==5.025.006.177.0H T H W H W C εN.P. van der Meijs and J.T. Fokkema ,“VLSI circuit reconstruction frommask topology ”, Integration, Vol.2, no.2,1984:85-119E. Barke , “Line -to -Ground Capacitor Calculation for VLSI:A Comparison,”IEEE Trans, Vol.CAD -7, no.2, Feb, 1988:295-298.三明治情形TWH 1H 2nn n xx x x f /121212)(⎟⎟⎠⎞⎜⎜⎝⎛+=+加权平均N.P. van der Meijs and J.T. Fokkema取n =4,得:⎪⎭⎪⎬⎫⎥⎥⎦⎤⎢⎢⎣⎡⎟⎟⎠⎞⎜⎜⎝⎛++⎟⎟⎠⎞⎜⎜⎝⎛++⎩⎨⎧+⎟⎟⎠⎞⎜⎜⎝⎛+==25.022225.025.021*********.077.011H H TH H W H H W C ε同层多导体情形TWH 1S34.1222.0222.007.083.003.08.215.12−⎟⎠⎞⎜⎝⎛⎥⎥⎦⎤⎢⎢⎣⎡⎟⎠⎞⎜⎝⎛−+=⎥⎥⎦⎤⎢⎢⎣⎡⎟⎠⎞⎜⎝⎛+=+=H S H T H T H W C H T H W C C C C mutualSingle mutual Single total εε平面螺旋电感2r2720104rnrn L Square −×≈≈πμSquareOctagon Square Circle L L L L 91.04/==π其它形状:同直径的面积之比的平方根3/163/10102.1⎥⎦⎤⎢⎣⎡×≈⎟⎟⎠⎞⎜⎜⎝⎛≈−PL PL n μ匝数的计算方法P 是每米的匝数空心平面螺旋电感2rar an L re HollowSqua 14225.37220−≈μ其中,a 是中位圈的半径精度在5%左右,Q 值更高a平面螺旋电感的特点面积大串连电阻有损耗与衬底间的电容也有损耗10nH 左右Q 值低,5~10, 通常<5C1R1C1R1C ox 2C ox 2衬底C pL R s)1(/δσδt S e w lR −−≈l 是电感线圈的总长度w ,t 分别是导线的宽度和厚度σ为导线的电导率,δ称为趋肤深度2σμδw =ox ox P t nw C /2ε=oxs ox ox t wl C /ε=)/(21sub wlG R =2/1sub wlC C =ox t 电感两端所在连线层间的氧化层厚度oxs t 电感主线圈与衬底间的氧化层厚度单位面积的电导、电容,由衬底材料及其与电感主线圈层的距离决定sub sub C G ,空心电感,优化n在电感下交替放置n阱和衬底,使感生电流深入到衬底的底部采用多晶硅或金属掩蔽层,减小衬底噪声到电感底耦合效应,减小损耗;但电容会增加,降低自激频率综合使用上述策略,可将Q提高约50%dChoong-Mo Nam Young-Se Kwon,High-performance planar inductor on thick oxidized porous silicon(OPS) substrate, Microwave and Guided Wave Letters, IEEE [see also IEEE Microwave and Wireless Components Letters], August, 1997, pp.236-238246810121416182022High-Q InductorsQ -f a c t o rFrequency (GHz)d =200μm100μm 20μm 10μm5μm 1μm Decreasing d(d : remaining Si)Courtesy :黄茹, 2007gatedrainsourceN +N +p -substratebulk长沟道线性区饱和区()⎥⎦⎤⎢⎣⎡−−=22DS DS th GS ox n DSV V V V L WC I μ()212DSn ox GS th W I C V V Lμ=−thGS DS V V V −<()DSox n th GS ox n m I L W C V V LWC g μμ2=−=MOSFETgatedrainsourcebulk长沟道动态元件p -subN +N +jDBC ov C CBC GCC ovC jSBC j oxD ox oxov Wx C WL t C 7.0=≈ε)2(D ox GC L L W C C −≈)2(D d Si CB L L W x C −≈εFS subSid qN x φφε−≈2j x 源漏极结深sub N 衬底杂质浓度F φ衬底的表面势和费米势,S φ管脚电容截止区线性区饱和区gs C gd C gb C dbC sb C ov C ov C CBGC CB GC C C C C +jSB C jDBC ov GC C C +2/ovGC C C +2/00jSB CB C C +2/jSB CB C C +32jDBCB C C +2/jDBC ovGC C C +32ov CBSIM3V3.3中的V th()()011,2,133,01101011exp 2exp 2exp 2exp 2th th S ox S bs eff ox bs efflx oxox S b bs eff Seff eff VT w eff eff VT w effeff VT w bi S tw tw VT eff VT t V V K K V K V N T K K K V L W W D W L D W L D V l l D L D l =−Φ+Φ−−⎛⎞⎜⎟++−Φ++Φ⎜⎟′+⎝⎠′′⎡−−⎤⎛⎞⎛⎞−+−Φ⎜⎟⎜⎟⎢⎥⎝⎠⎝⎠⎣⎦−−⎛⎞−+⎜⎟⎝⎠()()10,00exp 2exp 2VT eff bi S t sub eff sub eff ta tab bs eff ds t t D L V l D L D L E E V V l l ⎡⎤⎛⎞−Φ⎜⎟⎢⎥⎝⎠⎣⎦⎡−−⎤⎛⎞⎛⎞−+−⎜⎟⎜⎟⎢⎥⎝⎠⎝⎠⎣⎦准静态模型的缺陷: 在接近fT 、且栅电压变化很快时,沟道电流的尖峰在实际中是不存在nqsMod=1, 直流/瞬态使用非准静态模型acnqsMod=1, 交流使用非准静态模型栅衬底源漏......(a) 用RC 传输线等效的沟道(b) 准静态模型等效电路栅源漏gsC gdC sR dR chR 栅源漏......(c) 用串联晶体管等效的电路(d) 非准静态模型等效电路栅源漏gsC gdC sR dR ch R Elmore R Elmore R单位电流增益频率栅极接理想电流源,漏极接交流地单位功率增益频率栅电阻的来源及计算方法Tωgdgs mT gd gs m in ds C C g C C g i i +=⇒+≈ωω )(maxωgdT gd gs gd m out C C C C g g ω=+≈)(gd g T gdg T g in outds in L C r C r r i g i P P ωωωω21 4 2/)2/(max 221221=⇒≈≈−T indsi i ω=单位电流增益频率假设gdgs C C >>2322)(3))(/(L V V WLC V V L W C C g th gs n oxth gs ox n gs m Ts −=−≈≈μμω跨导/沟道电流亚阈区工作gs thV V <)exp(gs ds V I ∝↑↓ds m m I g g / 双极型电路可翻版为MOS 电路DSDS GS DS m DS th GS ox DSI mkTqconst V V I g q kT V q mkT V V q kT m L WC I ==∂∂=⎥⎦⎤⎢⎣⎡⎟⎟⎠⎞⎜⎜⎝⎛−−⎟⎟⎠⎞⎜⎜⎝⎛−⎟⎟⎠⎞⎜⎜⎝⎛−=/exp 1/exp )1(2eff μdplox dplox oxSi ox dpl W t W t C C m /3111+≈+=+=εε其中,衬底效应因子杨华中、汪蕙、刘润生《模拟集成电路的自动综合方法》,北京:科学出版社,1999,pp.72Brokaw 能隙基准电压源()⎥⎥⎦⎤⎢⎢⎣⎡⎟⎟⎠⎞⎜⎜⎝⎛−−+=R TR R G out T T V n r T TV T V ln 1)(0启动电路1:mR2R1Vout Vcc/R1V I be Δ=使M1和M2工作在亚阈区启动电路1:m R2R1Vout Vcc M2M1启动电路1:mR2R1Vout VccQ2Q1P -衬底n -阱P+n+n+EBC速度饱和效应饱和电流跨导沟道调制效应、衬底电流、栅电流、背栅调制效应sat th gs satth gs sat th gs dsat LE V V LE V V LE V V V +−−=−⇒)()//()( satth gs E L V V >−~/)(()12()//()W dsat n ox gs th gs th sat LI C V V V V LE μ⎡⎤=−−⎣⎦satth gs sat th gs ox n dsat E L V V if E V V C W I >>−−=/)( ,)(21μsatox n gs ds m WE C V I g μ21=∂∂≡LL E C g sat n gsm T /1/43∝=≈μωgdgs C C >>设实际值低3-5倍,因为V gs 通常不能使载流子到达速度饱和小尺寸效应thV jx jL x max 2()()11j d Ath th j oxx x Q V L V L L x C ⎡⎤==∞++−⎢⎥⎢⎥⎣⎦max22ln Si A d BS A i N kT x V qN q n ε⎛⎞=−⎜⎟⎝⎠4lnAA A Si iN Q kTN n ε=−gatedrainsource bulkgdC gs C sbC dbC bsmb V g gsm V g1/f 噪声,在栅极回路产生的,等效噪声源应放在栅极回路沟道热噪声非饱和区饱和区诱生栅极噪声()()12221132411nD m i kTg fηηη−=−+−Δ2234nDm i kTg f=×Δ()DS GS th V V V η=−22210.124nGoxmi kT f Cg ω=×Δgs C nGi ()m gsg v ωdsR gsR nDi 1/f 噪声为主,频率低,不需要考虑Cgdgatedrainsource bulkgdC gs C sbC dbC bsmb V g gsm V g。

数模混合IC设计流程

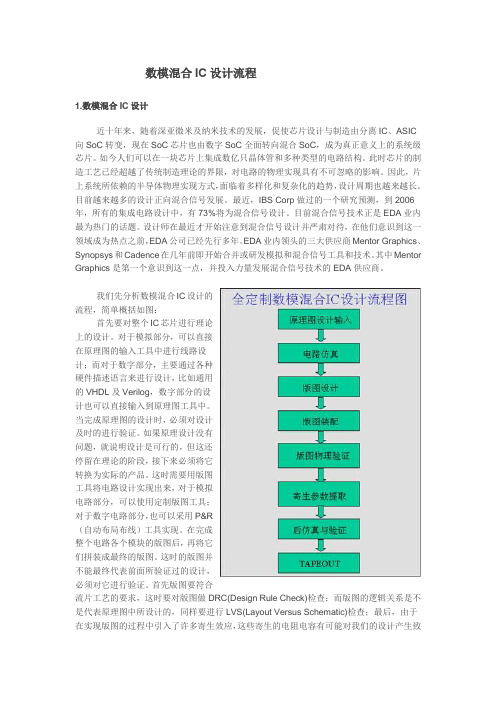

数模混合IC设计流程1.数模混合IC设计近十年来,随着深亚微米及纳米技术的发展,促使芯片设计与制造由分离IC、ASIC 向SoC转变,现在SoC芯片也由数字SoC全面转向混合SoC,成为真正意义上的系统级芯片。

如今人们可以在一块芯片上集成数亿只晶体管和多种类型的电路结构。

此时芯片的制造工艺已经超越了传统制造理论的界限,对电路的物理实现具有不可忽略的影响。

因此,片上系统所依赖的半导体物理实现方式,面临着多样化和复杂化的趋势,设计周期也越来越长。

目前越来越多的设计正向混合信号发展。

最近,IBS Corp做过的一个研究预测,到2006年,所有的集成电路设计中,有73%将为混合信号设计。

目前混合信号技术正是EDA业内最为热门的话题。

设计师在最近才开始注意到混合信号设计并严肃对待,在他们意识到这一领域成为热点之前,EDA公司已经先行多年。

EDA业内领头的三大供应商Mentor Graphics、Synopsys和Cadence在几年前即开始合并或研发模拟和混合信号工具和技术。

其中Mentor Graphics是第一个意识到这一点,并投入力量发展混合信号技术的EDA供应商。

我们先分析数模混合IC设计的流程,简单概括如图:首先要对整个IC芯片进行理论上的设计。

对于模拟部分,可以直接在原理图的输入工具中进行线路设计;而对于数字部分,主要通过各种硬件描述语言来进行设计,比如通用的VHDL及Verilog,数字部分的设计也可以直接输入到原理图工具中。

当完成原理图的设计时,必须对设计及时的进行验证。

如果原理设计没有问题,就说明设计是可行的,但这还停留在理论的阶段,接下来必须将它转换为实际的产品。

这时需要用版图工具将电路设计实现出来,对于模拟电路部分,可以使用定制版图工具;对于数字电路部分,也可以采用P&R(自动布局布线)工具实现。

在完成整个电路各个模块的版图后,再将它们拼装成最终的版图。

这时的版图并不能最终代表前面所验证过的设计,必须对它进行验证。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数模混合电路设计的难点

数模混合电路设计的难点

数模混合电路的设计,一直是困扰硬件电路设计师提高性能的瓶颈。众所

周知,现实的世界都是模拟的,只有将模拟的信号转变成数字信号,才方便

做进一步的处理。模拟信号和数字信号的转变是否实时、精确,是电路设计

的重要指标。除了器件工艺,算法的进步会影响系统数模变换的精度外,现

实世界中众多干扰,噪声也是困扰数模电路性能的主要因素。

数模混合电路设计当中,干扰源、干扰对象和干扰途径的辨别是分析数模

混合设计干扰的基础。通常的电路中,模拟信号上由于存在随时间变化的连

续变化的电压和电流有效成分,在设计和调试过程中,需要同时控制这两个

变量,而且他们对于外部的干扰更敏感,因而通常作为被干扰对象做分析;

数字信号上只有随时间变化的门限量化后的电压成分,相比模拟信号对干扰

有较高的承受能力,但是这类信号变化快,特别是变化沿速度快,还有较高

的高频谐波成分,对外释放能量,通常作为干扰源。

作为干扰源的数字电路部分多采用CMOS工艺,从而导致数字信号输入端

极高的输入电阻,通常在几十k欧到上兆欧姆。这样高的内阻导致数字信号

上的电流非常微弱,因而只有电压有效信号在起作用,在数模混合干扰分析

中,这类信号可以作为电压型干扰源,如CLK信号,Reset等信号。除了快

速交变的数字信号,数字信号的电源管脚上,由于引脚电感和互感引起的同

步开关噪声(SSN),也是数模混合电路中存在的重要一类电压型干扰源。此

外,电路中还存在一些电流信号,特别是直流电源到器件负载之间的电源信