基于FPGA的高速图像采集系统

基于FPGA的图像采集卡的设计

基于FPGA的图像采集卡的设计1 引言现代化生产和科学研究对视频图像采集系统的要求日益提高。

传统的图像采集卡速度慢、处理功能简单、采用分立元件、电路非常复杂;而且可靠性差、不易调试、不能很好地满足特殊要求。

FPGA(现场可编程门阵列)是专用集成电路中集成度最高的一种,用户可对FPGA 内部的逻辑模块和I/O模块重新配置,以实现用户所需逻辑功能。

用户对FPGA的编程数据放入芯片,通过上电加载到FPGA中,对其进行初始化;也可在线对其编程,实现系统在线重构。

基于FPGA技术的图像采集主要是通过集成的FPGA开发板,使用软件编程把图像的采集控制程序写入FPGA开发板的芯片上,通过仿真技术来进行图像的采集处理分析。

通过这种方式,便于及时地发现设计中的错误,从而有效地缩短研发时间。

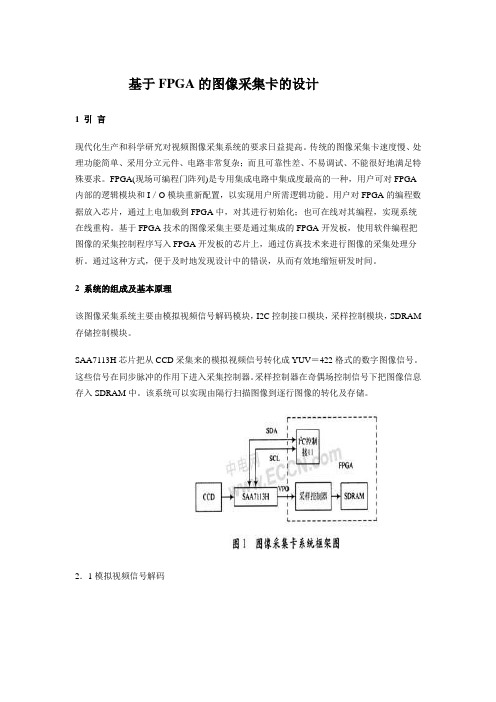

2 系统的组成及基本原理该图像采集系统主要由模拟视频信号解码模块,I2C控制接口模块,采样控制模块,SDRAM 存储控制模块。

SAA7113H芯片把从CCD采集来的模拟视频信号转化成YUV=422格式的数字图像信号。

这些信号在同步脉冲的作用下进入采集控制器。

采样控制器在奇偶场控制信号下把图像信息存入SDRAM中。

该系统可以实现由隔行扫描图像到逐行图像的转化及存储。

2.1模拟视频信号解码由于SAA7113H芯片具有I2C接口,该模块则通过I2C总线来配置SAA7113H初始化的信息。

工作涉及SAA7113H的初始化字的配置、工作方式的配置;行同步开始和结束标志位、确定亮度、色度、饱和度的大小以及输出图像数据信号的格式。

2.2 I2C控制接口模块I2C模块作为SAA7113H寄存器初始配置的整体控制模块。

具体可以分成I2C_cmd和数据传输2个模块I2C_cmd模块为纯组合逻辑电路,完成信号的发送控制任务,配合rom_data[7.0]和rom_addr[7.0]信号完成数据的寻址与存入等工作;而数据传输模块主要和I2C_cmd模块一起组合成I2C的数据控制写入模块,他主要负责对I2C_cmd模块的输出信号进行缓存,并在其输出端输出I2C总线的串行数据SDA以及I2C总线的串行时钟信号SCL。

基于FPGA的MIPI CSI-2图像采集系统设计

基于FPGA的MIPI CSI-2图像采集系统设计赵清壮【摘要】This paper elaborates a design of MIPI CSI-2 high-definition camera interface image acquisition system based on FPGA. Now, MIPI high-definition CCD is used widely, this design uses FPGA to achieve MIPI high-definition CCD collect and provides two outputs of LCD screen and USB, the data transmission is stable and reliable, it make MIPI interface camera applied widely by the other circuit systems, accelerates system development and saves cost.%阐述一种基于FPGA的MIPI CSI-2接口高清摄像头图像采集系统设计,该设计用FPGA实现当前应用广泛的MIPI高清CCD采集,并提供LCD屏、USB两路输出,数据传输稳定可靠,把MIPI接口摄像头应用到更广泛的其他电路系统中,加快系统开发,节省成本。

【期刊名称】《价值工程》【年(卷),期】2015(000)029【总页数】2页(P84-85)【关键词】MIPI;CSI-2;图像采集;FPGA【作者】赵清壮【作者单位】广州飒特红外特股份有限公司,广州510000【正文语种】中文【中图分类】TP302.10 引言CSI(Camera Serial Interface)是由MIPI(Mobile Industry Processor Interface)联盟下Camera工作组制定的接口标准,是MIPI联盟发起的为移动应用处理器制定的开放标准,MIPI联盟由ARM、诺基亚、意法半导体和德州仪器发起成立,作为移动行业领导者的合作组织,MIPI联盟旨在确定并推动移动应用处理器接口的开放性标准。

基于FPGA和USB3.0的高速视频图像采集处理系统设计

摘要随着机器视觉的广泛应用,以及工业4.0和“中国制造2025”的提出,在数字图像的采集、传输、处理等领域也提出了越来越高的要求。

传统的基于ISA接口、PCI接口、串行和并行等接口的图像采集卡已经不能满足人们对于高分辨率、实时性的图像采集的需求了。

一种基于FPGA和USB3.0高速接口,进行实时高速图像采集传输的研究越来越成为国内外在高速图像采集研究领域的一个新的热点。

针对高速传输和实时传输这两点要求,通过采用FPGA作为核心控制芯片与USB3.0高速接口协调工作的架构,实现高帧率、高分辨率、实时性的高速图像的采集和传输,并由上位机进行可视化操作和数据的保存。

整体系统采用先硬件后软件的设计方式进行设计,并对系统各模块进行了测试和仿真验证。

通过在FPGA 内部实现滤波和边缘检测等图像预处理操作,验证了FPGA独特的并行数据处理方式在信号及图像处理方面的巨大优势。

在系统硬件设计部分,采用OV5640传感器作为采集前端,选用Altera的Cyclone IV E系列FPGA作为系统控制芯片,由DDR2存储芯片进行数据缓存,采用Cypress公司的USB3.0集成型USB3.0芯片作为数据高速接口,完成了各模块的电路设计和采集卡PCB实物制作。

系统软件设计,主要分为FPGA逻辑程序部分、USB3.0固件程序部分和上位机应用软件部分。

通过在FPGA上搭建“软核”的方式,由Qsys系统完成OV5640的配置和初始化工作。

由GPIF II接口完成FPGA和FX3之间的数据通路。

通过编写状态机完成Slave FIFO的时序控制,在Eclipse中完成USB3.0固件程序的设计和开发。

上位机采用VS2013软件通过MFC方式设计,从而完成整体图像采集数据通路,并在上位机中显示和保存。

整体设计实现预期要求,各模块功能正常,USB3.0传输速度稳定在320MB/s,通过上位机保存至PC机硬盘的图像分辨率大小为1920*1080,与传感器寄存器设置一致,采集卡图像采集帧率为30fps,滤波及边缘检测预处理符合要求,采集系统具有实际应用价值和研究意义。

基于FPGA的高速彩色线阵CCD实时图像采集系统

基于FPGA的高速彩色线阵CCD实时图像采集系统刘伟;齐美彬;许建平;胡龙飞【摘要】文中设计了一款彩色线阵CCD实时图像采集系统,选用FPGA作为主控芯片.该系统完成了线阵CCD传感器、模数转换芯片的驱动、数据采集与转换.转换后的数据通过FPGA预处理后,由USB2.0传输至上位机实现图像实时成像.结果表明:设计的彩色线阵CCD实时图像采集系统能够满足工业应用要求,每行像素点达2098个,行频可达9000 fps.%The color linear CCD real?time image acquisition system was designed in this paper. The system chose FPGA to be the master chip.The system completed the driver of linear CCD sensor and analog?digital conversion chip,data acquisition and conversion. The transformed data after pretreatment by FPGA was transmitted to the computer for real?time imaging by the USB 2.0. The results show that the design of color linear CCD real?time image acquisition system can meet the requirements of indus?trial application ,the pixel resolution of the system is 2098 and the line frequency can reach 8000 fps.【期刊名称】《仪表技术与传感器》【年(卷),期】2017(000)005【总页数】4页(P91-94)【关键词】FPGA;高速;线阵CCD;实时成像【作者】刘伟;齐美彬;许建平;胡龙飞【作者单位】合肥工业大学计算机与信息学院,安徽合肥 230009;合肥工业大学计算机与信息学院,安徽合肥 230009;合肥工业大学计算机与信息学院,安徽合肥230009;合肥工业大学计算机与信息学院,安徽合肥 230009【正文语种】中文【中图分类】TP273电荷耦合器件(charge coupled device,CCD),具有集成度高、性能稳定、响应速度快、分辨率高、抗干扰能力强等优点[1]。

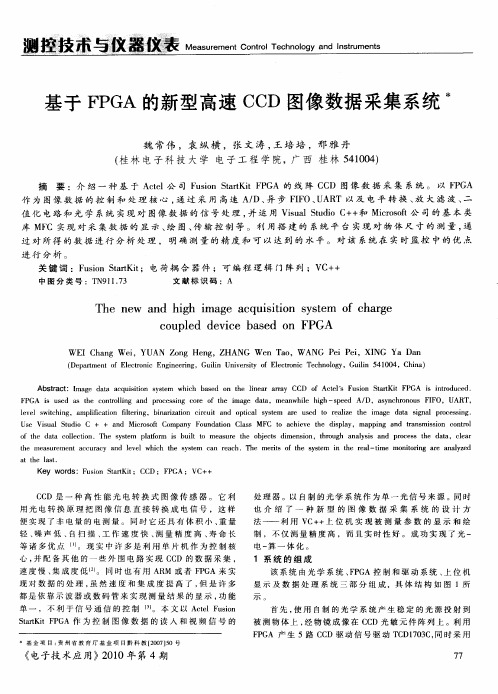

基于FPGA的新型高速CCD图像数据采集系统

作 为 图 像 数 据 的 控 制 和 处 理 核 心 , 过 采 用 高速 A/ 异 步 FF U R 以 及 电 平 转 换 、 大 滤 波 、 通 D、 IO、 A T 放 二 值 化 电 路 和 光 学 系 统 实 现 对 图 像 数 据 的 信 号 处 理 , 运 用 V s a Su i + 和 Mirsf 公 司 的 基 本 类 并 i l tdo C + u coot 库 MF 实现 对 采 集 数 据 的 显 示 、 图 、 输 控 制 等 。 利 用 搭 建 的 系统 平 台 实 现 对 物 体 尺 寸 的 测 量 , C 绘 传 通

Ue s Vi a t d o s l ui u S C + + a d n Mir s f Co a y F u d t n l s MF t a he e h d s ly coot mp n o n a i C a s o C o c i v t e ip a .ma p n a d r n miso o t l p ig n t s s in c n r a o

W EI Ch n W e ,YUAN Zo g ag i n He g,ZHANG W e Ta n n o,W ANG i e ,XI Pe P i NG Da Ya n

( e a m n o lc o i E gneig u i U i r t o Eet ncT c nlg,G in 5 10 ,C ia D p r e t fEet nc nier ,G in nv sy f lc o i eh o y ul 4 0 4 hn ) t r n l e i r o i

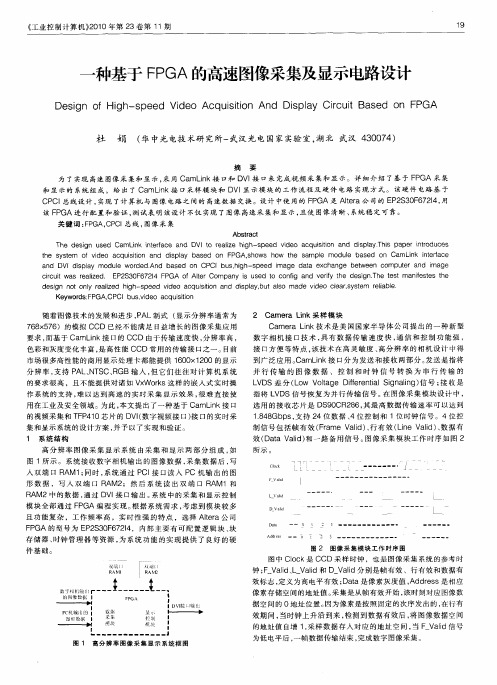

一种基于FPGA的高速图像采集及显示电路设计

1 9

一

种基于 F G P A的高速图像采集及显示电路设计

De i f Hi —s e d Vi o Ac ust n An Dip a r utBa e o P sgn o gh— p e de q iio d i s ly Ci i c s d n F GA

选 用 的 接 收 芯 片是 DS 0 R 8 , 最 高 数 据 传输 速 率 可 以达 到 9 C 2 6其

该 F G 进 行 配 置和 验 证 , 试 表 明该 设 计 不仅 实现 了 图像 高 速 采 集和 显 示 , 使 图像 清 晰 、 PA 测 且 系统 稳 定 可 靠 。

关 键 词 :P F GA, Cl CP 总线 , 图像 采 集

Ab ta t s rc

Th si u e Ca Ln nera e nd e de gn s d m ik it f c a DVI o r al e i -s ed i a qust d t e i hgh pe vdeo c iion an diply.hi z i s a T s pap itodu es er nr c t e y tm of i a quiion nd h s se vdeo c st a diply a d i s a b se on PGA,h ws o F s o h w t s m pl m o e he a e dul ba ed s on Cam Lnk n e ce i it da an DVI s a o e d diply m dul wor d. d de An ba ed n s o CP bu ,i Cl shgh- ee i a da a ex h ge et e c sp d m ge t c an b we n ompu e an i tr d mag e ci ui wa r aied. EP 30 7 4 FP r t c s el z 2S F6 21 GA o t m p y i u e t n i d ery h de i . e es manfses h fAl Co an s s d o co fg an v i te er f sgnTh t t i t te e de i n tonl eaied i sgn o y r l z hgh—s ee vdeo a p d i cqust a d iion n diply, talo m a de ea ,y tm r i l i s a bu s de vi o cl rs se el e ab Ke wo d : P y r s F GA. Cl s, de a quiion CP bu vi o c st i

基于FPGA的高速图像采集系统设计.

基于FPGA的高速图像采集系统设计引言在低速的数据采集系统中,往往采用单片机或者DSP进行控制;而对于图像采集这种高速数据采集的场合,这种方案就不能满足需要。

因此这种方案极大浪费了单片机或DSP的端口资源且灵活性差;若改用串口方式收集数据,则一方面降低了数据采集的速度,另一方面极大地耗费CPU的资源。

本系统采用FPGA作为数据采集的主控单元,全部控制逻辑由硬件完成,速度快、成本低、灵活性强。

为了增加缓冲功能,系统在FPGA外扩展了256Mb的RAM,不仅增大了缓冲区容量,而且极大地降低了读写频率,有效地减轻了上位机CPU的负担。

在图像数据接口中,比较常见的是VGA、PCI—Express,而这些接口扩展性差、成本高。

本系统采用高速的USB接口作为与上位机通信的端口,速度快、易安装、灵活性强。

1 系统框图系统框图如图1所示。

FPGA控制单元采用A1tera公司Cyclone II系列的EP2C5F256C6,主要由4个部分组成——主控模块、CMOS传感器接口、RAM 控制器以及EZ—USB接口控制器。

传感器接口负责完成SCCB时序控制,RAM控制器用于实现RAM读写与刷新操作的时序,USB接口模块完成主控模块与EZ—USB之间的数据读写;而主控模块负责对从EZ—USB部分接收过来的上位机命令进行解析,解析完命令后产生相应的信号控制各个对应模块,如CMOS传感器传输的图像格式、RAM的读写方式、突发长度等。

2 OV7620模块设计图像传感器采用OV7620,接口图如图2所示。

该传感器功能强大,提供多种数据格式的输出,自动消除白噪声,白平衡、色彩饱和度、色调控制、窗口大小等均可通过内部的SCCB控制线进行设置。

OV7620属于CMOS彩色图像传感器。

它支持连续和隔行两种扫描方式,VGA与QVGA两种图像格式;最高像素为664×492,帧速率为30fps;数据格式包括YUV、YCrCb、RGB三种。

基于FPGA的高速线阵CCD图像采集系统_任慧建

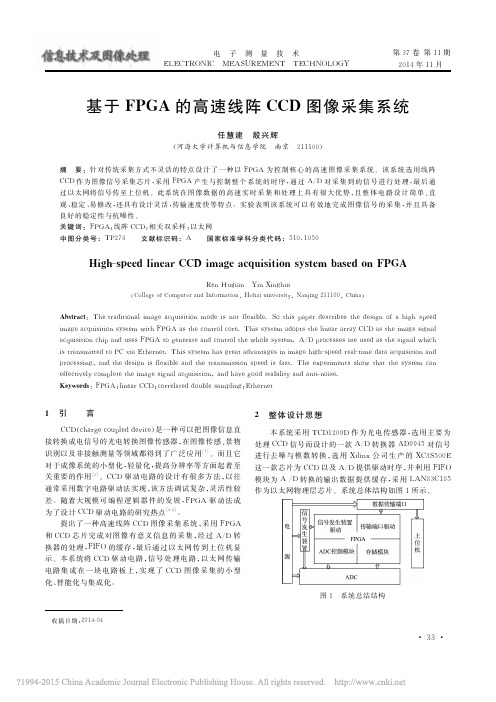

3.1 TCD1209D 采样模块设计 TCD1209D 的驱动时序如图2所示,由图 知,完成芯片

的驱动需要5路驱动脉冲,分别为:移位脉冲 φ1 和 φ2,转移 脉冲 SH,复位脉冲 RS,钳位脉冲 CP[5],各路脉冲必须严格 满 足 时 序 要 求 。 每 帧 输 出 信 号 首 先 是 32 个 哑 元 像 素 信 号 ,

1 引 言

CCD(charge coupled device)是 一 种 可 以 把 图 像 信 息 直 接 转 换 成 电 信 号 的 光 电 转 换 图 像 传 感 器 ,在 图 像 传 感 、景 物 识别以及非接触测量等领域都得到了 广 泛 应 用 。 [1] 而 且 它 对 于 成 像 系 统 的 小 型 化 ,轻 量 化 ,提 高 分 辨 率 等 方 面 起 着 至 关重要的作用[2]。CCD 驱 动 电 路 的 设 计 有 很 多 方 法,以 往 通 常 采 用 数 字 电 路 驱 动 法 实 现 ,该 方 法 调 试 复 杂 ,灵 活 性 较 差。随着大规模可 编 程 逻 辑 器 件 的 发 展,FPGA 驱 动 法 成 为了设计 CCD 驱动电路的研究热点 。 [3-4]

图 1 系 统 总 结 结 构

收 稿 日 期 :2014-04

· 33 ·

第 37 卷

电 子 测 量 技 术

首先通过 代 码控 制 FPGA 输出 与 CCD 芯片 时序要 求 相对应 的 驱 动 信 号 对 CCD 进 行 驱 动,CCD 输 出 信 号 经 过 电容滤波后送入 AD9945进行相关 双 采样 与 A/D 转换,之 后将获得的数字信 号 放 入 FPGA 的 FIFO 数 据 缓 存 器,再 经过以太网传至上位机。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Abstract:A hardware scheme for high—speed image acquisition system based on FPGA is proposed in this paper.The principle of high—speed,high resolution image acquisition system is described.The system design is finished based on the study of the temporary storage of burst data,the transform storage of large capacity data,the real time transmission of high—resolution and high frame frequency image and the terminal transmission of large capacity data.The testing results Of designed hardware show that the system could acquire and store the high—speed and large capacity data flow,which is generated by the image sensor.Since the FPGA is used to be the core processor.the high—speed image acquisition system is simplified on its hardware structure,and the system performance is improved. Key words:high—resolution;high frame frequency;FPGA

太网是建立在标准以太网基础上的一种新型高速局 域网,它可以提供100 Mbit/s的通信带宽,特别适 用本设计中的高速率大容鬣数据的传输.

由于CMOS图像传感器最大分辨率可达l 280× l 024,远远超过了普通电视视频信号的最大分辨率. 要想将处理后的图像显示出来,必须使用VGA接13 的电脑显示器.电脑显示器由于其输出信息量大、输 出形式多样等特点已经成为现在大多数设计的常用 输出设备,显示器采用逐行扫描显示r引.

1119

对差分线实现高速信号传输,使信号能在差分PCB

线对或平衡电缆上以几百MB/s的速率传输.设计 中采用了低至400 mV的电压摆幅和大约3.5 mA 的低电流驱动输出,加之差分对线的共模抑制功能,

LVDS具有低噪声和低功耗的优点∞].

高速摄像系统需要传输的图像数据为1 280X 1 024,帧频为500 Hz,为满足实时传输的要求,需要

高速摄像机(一般指帧频在100帧/s以上)在 军事领域具有广泛的应用’1].

在高速图像采集系统中,接收机瞬间收到大量 数据,要对这样海量的迸发数据进行处理和分析,必 须通过高速摄像机采集图像数据.由于在高分辨率 图像处理系统中,数据量十分庞大,因此对硬件处理 器的实时处理速度要求很高,需要合理设计硬件电 路,满足系统分辨率及图像帧速率的要求.

2高分辨率、高速图像采集系统设计

2.1迸发数据暂时存储 目标的运动图像信息通过光学系统进入图像传

感器,图像传感器片内的模数转换器(ADC)将模拟 信号转换成数字信号传送到FPGA控制单元.由于 图像传感器输出10路10 bit宽的数据,时钟频率为 66 MHz,由此将产生100 bit×66 MHz(约为0.825 GB/s)的数据量,如此快速的数据量即所谓的迸发 数据流无法用硬盘直接存储,需要将它暂时存储在 内存条(DDR2 SDRAM)中.通过FPGA访问 DDR2 SDRAM存储器控制大容量迸发数据的读、 写、刷新等时序操作.

第30卷第9期

北京理工大学学报

2010年9月Transactions of Beijing Institute ot Technology

V01.30 No.9 Sep.2010

基于FPGA的高速图像采集系统

张彦梅, 柴芳娇

(北京理工大学信息与电子学院。北京 100081)

摘 要:提出了一种基于FPGA的高速图像采集系统硬件方案.论述了高速、高分辨率图像采集系统的工作原理,

本文中采用硬件描述语言实现FPGA对图像 采集系统的逻辑设计及控制,图3为截取的几段时 序仿真结果,图4所示为传感器帧时序.

万方数据

图3仿真结果 Fig.3 Simulation result

1120 ROW...AD R[0:9]j窭)北 C二京理 j二工×大二学]学二报)[二互=X砸[j匝]圃[二日第 (30卷

由于DDR2 SDRAM一旦掉电,数据就会全部 丢失,因此需要将存储在DDR2 SDRAM中的大容 量数据转发到可以永久保存数据的存储器中,本文 采取大容量数据转存技术实现对DDR2 SDRAM中 数据的永久保存.

本文中选用掉电后仍可保持数据且加电后可以 实现现场可擦除、可编程的Flash来存储大容量的 数据.采用1 GB/片×4片的超大容量与非 (NAND)结构的Flash芯片接收转发的图像数据. NAND结构的Flash容量大、回写速度快、芯片面 积小,而NAND结构能提供极高的单元密度,并且 写入和擦除的速度也很快,适于高密度数据的存储.

SDRAM

DQS[0:8].

DII[0:8 J.

RsT

图2 DDR2 SDRAM和FPGA接口协议 Fig.2 Protocol of DDR2,SDRAM and FPGA interface

采用了多块Bank存储器结构和突发模式,每一个 Bank通过行列来寻址.列地址空间对应一页的存 储器空间.

中图分类号:TP 752

文献标志码:A

文章编号:1001—0645(2010)09—1117一04

A High—Speed Image Acquisition System Based on FPGA

ZHANG Yan—mei。 CHAI Fang—jiao (School of Information and Electronics,Beijing Institute of Technology,Beijing 100081,China)

从迸发数据暂存、大容量数据转存、高解析度、高帧频图像的实时传输及大容茸数据终端传输等内容的研究完成了 系统设计.对硬件电路的测试结果表明,该系统能够对图像传感器产生的高速大容量数据流进行采集存储,以FP—

GA为核心处理器设计的高速图像采集系统大大简化了系统硬件结构,提高了系统可靠性.

关键词:高分辨率;高帧频;FPGA

万方数据

北京理工大学学报

第30卷

Fig.1

图1 高速图像采集系统原理框图 Principle Diagram of high-speed image acquisition system

内部构建CMOS图像传感器的驱动模块,产生 CMOS工作所需的驱动信号.数字化的图像数据一 路通过FPGA控制传送到DDR2 SDRAM存储器 暂时存储,然后再通过嵌入式主板送往PC机进行 进一步的处理和数据分析;另一路的图像数据合成 为VGA信号,通过LVDS差分传输实时的信号送 到显示器进行监控.

3 仿真结果

在高速图像采集系统中,FPGA是核心控制器 件,由它控制所有的外围芯片,FPGA具有密度高、 速度快、带宽高和通用性强的特点,非常适合高速系 统的设计要求[7].FPGA的选型主要考虑芯片的规 模(片内RAM大小、逻辑单元数等),用户I/0的个 数以及电平兼容等问题.根据设计要求,选用Al— tera公司StratixII系列的FPGA,其内部使用了先 进的设计构架,包括自适应逻辑模块(ALM)、逻辑 阵列块(LAB)、TriMatrix存储器、外部存储器接口 以及数字信号处理(DSP)模块.

ROW_STRT N——]厂——]厂——]厂—一 ]广——]厂——]广——]厂——]厂——]I ROW_DONE N——————]厂——]厂—一 ]广——]厂——]厂——]厂——]厂——]l

LD_SHFr__N

Hale Waihona Puke 00n0

8

0

DATA_READ..EN..N

作者从迸发数据暂时存储,大容量数据转存,高 解析度、高帧频图像的实时传输,大容量数据终端传 输与显示几个方面进行系统设计.

1 高分辨率、高速图像采集系统工作 原理

高分辨率、高速图像采集系统原理框图如图1 所示,由图像传感器(image sensor)、FPGA、内存条 (DDR2 SDRAM)、Flash存储器、FRAM、低电压差 分信号(LVDS)、嵌入式主板、以太网等模块组成.

655.36/198=3.31.

(3)

因此应选用4片LVDS芯片并行输出.

2.4大容量数据终端传输与显示

为了便于用户终端对所得图像数据进行后续处 理,FPGA通过ISA总线接口与嵌入式主板相连,

待迸发过程和转存操作结束,通过嵌入式系统的以

太网接口,将内存条指定地址段中的数据通过以太

网传输至用户PC上. 为传输大容量数据,选用百兆以太网.百兆以