ModelSim+Synplify+Quartus的Altera FPGA的仿真实现

fpga开发流程及工具链

fpga开发流程及工具链FPGA(Field-Programmable Gate Array)的开发流程包括设计、仿真、综合、布局布线和配置等几个步骤。

常用的工具链包括Vivado、Quartus Prime等。

开发流程如下:1. 设计:在HDL(硬件描述语言)中使用VHDL或Verilog等语言对FPGA的逻辑电路进行设计。

可以使用设计工具如Vivado或Quartus Prime进行设计,也可以使用其他常用的IDE(集成开发环境)进行开发。

2. 仿真:使用仿真工具对设计进行验证。

通过仿真可以提前检测设计中的错误,以保证FPGA系统的正确性。

常用的仿真工具有ModelSim、VCS等。

3. 综合:将设计转化为可实现的逻辑电路,并生成布局和布线所需的网表。

综合工具会将设计转换为FPGA可以理解和实现的硬件描述,并生成逻辑网表。

常用的综合工具包括Synplify、Xilinx ISE等。

4. 布局布线:将逻辑网表映射到FPGA芯片的具体物理位置,并进行信号线的布线。

布局布线工具会根据设计的物理约束,将逻辑电路映射为FPGA芯片上的实际连线。

常用的布局布线工具有PAR(Place and Route)等。

5. 配置:将生成的bit文件(二进制配置文件)下载到FPGA芯片中,使其按照设计的功能进行配置和工作。

配置工具一般由FPGA厂商提供,如Xilinx的Vivado、Altera的Quartus Prime等工具。

常用的工具链有:1. Xilinx Vivado:Xilinx公司推出的综合工具和开发环境,用于设计、仿真和配置Xilinx FPGA芯片。

2. Altera Quartus Prime:Altera公司(现为Intel)的FPGA开发工具,支持设计、仿真、综合和布局布线等。

3. ModelSim:Mentor Graphics公司的一款通用的数字电路仿真工具,可用于FPGA开发中的设计验证。

QuartusII9.0与Modelsim-Altera6.4a无缝连接

end

assign fm = (cnt <= 6'd24) ? 1'b1 : 1'b0;

endmodule

2、编写TestBench测试平台,选择QuartusII9.0菜单栏Processing—>start—>start TsetBench Template Writer,QuartusII9.0会自动生成TestBench模板。

clk,rst_n,

fm

);

input clk;

input rst_n;

output fm;

reg[5:0] cnt;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n) cnt <= 6'd0;

else if(cnt < 6'd49) cnt <= cnt + 1'b1;

// port map - connection between master ports and signals/registers

.clk(clk),

.fm(fm),

.rst_n(rst_n)

);

initial//时钟信号产生

begin

clk = 0;

forever

#20 clk = ~clk;

3、然后打开TestBench模板编写测试代码,代码如下:

`timescale 1ns/1ps

module fp_verilog_vlg_tst();

reg clk;

reg rst_n;

// wires

wire fm;

ModelSim中Altera仿真库的添加

ModelSim中Altera仿真库的添加最近,做一个IP核的调试,但是里面调用了Altera的syncram,这样ModelSim就不能直接进行仿真,而QuartusII又不支持Tesbbench的仿真,所以为了在ModelSim中仿真就必须将Altera的这些仿真库添加到ModelSim中。

通常,在ModelSim中进行仿真需要加入Quartus提供的仿真库,原因是下面三个方面:·Quartus不支持Testbench;·调用了megafunction或者lpm库之类的Altera的函数;·时序仿真要在Modelsim下做仿真。

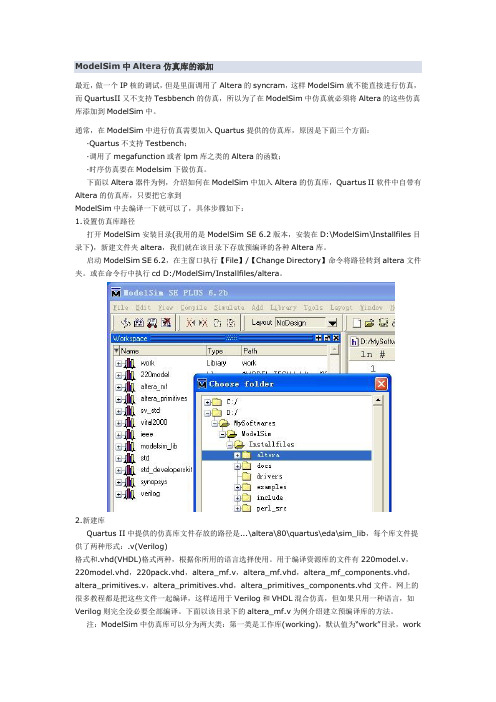

下面以Altera器件为例,介绍如何在ModelSim中加入Altera的仿真库,Quartus II软件中自带有Altera的仿真库,只要把它拿到ModelSim中去编译一下就可以了,具体步骤如下:1.设置仿真库路径打开ModelSim安装目录(我用的是ModelSim SE 6.2版本,安装在D:\ModelSim\Installfiles目录下),新建文件夹altera,我们就在该目录下存放预编译的各种Altera库。

启动ModelSim SE 6.2,在主窗口执行【File】/【Change Directory】命令将路径转到altera文件夹。

或在命令行中执行cd D:/ModelSim/Installfiles/altera。

2.新建库Quartus II中提供的仿真库文件存放的路径是...\altera\80\quartus\eda\sim_lib,每个库文件提供了两种形式:.v(Verilog)格式和.vhd(VHDL)格式两种,根据你所用的语言选择使用。

用于编译资源库的文件有220model.v,220model.vhd,220pack.vhd,altera_mf.v,altera_mf.vhd,altera_mf_components.vhd,altera_primitives.v,altera_primitives.vhd,altera_primitives_components.vhd文件。

Quartus II 13.1 +ModelSim-Altera 10.1d (Quartus

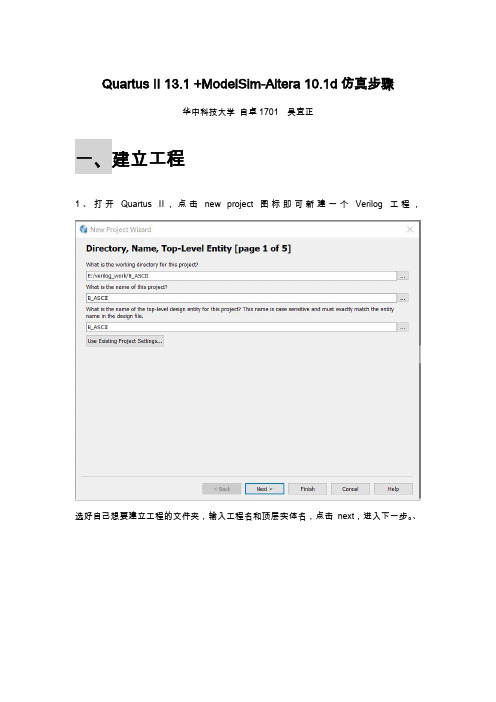

Quartus II 13.1 +ModelSim-Altera 10.1d仿真步骤华中科技大学自卓1701 吴宜正一、建立工程1、打开Quartus Ⅱ,点击new project图标即可新建一个Verilog工程,选好自己想要建立工程的文件夹,输入工程名和顶层实体名,点击next,进入下一步。

、2、可以向工程中加入已经存在的文件,如果没有点击next即可。

3、选取自己想要的器件,点击next即可。

4、在实验中最好在方框中选取Verilog HDL,以便之后编写Testbench文件。

点击next按钮。

之后finish即可。

5、添加Verilog文件在file菜单中选择new,之后输入自己的代码保存即可添加到工程中。

二、编译代码以二进制-ASCII码转化器为例输入代码后进行编译,编译可以按照以下步骤进行1、分析与综合。

点击菜单项Processing->start->Start Analysis &Synthesis也可以直接在工具栏找到。

如果编译成功,左下角窗口有如下显示。

2、全编译文件。

点击菜单项Processing->start compilation,或使用CTRL+L执行全编译。

执行后,如果程序没有问题左下角窗口有如下显示:三、电路仿真1、设定仿真工具此版本Quartus不提供仿真功能,需要调用Modelsim进行仿真,而如果要使用Modelsim 进行仿真首先要编写Testbench文件,在Quartus中,首先要设定仿真工具assignments-setting -EDA tool setting -simulation选择你需要的工具。

这里如果你使用的是下载Quartus时自动下载的ModelSim-Altera那么就选择这个,而如果使用的是单独下载的ModelSim那么就要选择ModelSim。

2. 自动产生测试激励文件模板:在菜单项中选择processing - start - Start test bench template writer3、添加testbench这时Quartus已经自动为你生成一个.vt文件,但是没有自动添加到你的工程内,需要自己去工程目录内寻找。

华为fpga设计规范(Verilog Hdl)

FPGA设计流程指南前言本部门所承担的FPGA设计任务主要是两方面的作用:系统的原型实现和ASIC的原型验证。

编写本流程的目的是:●在于规范整个设计流程,实现开发的合理性、一致性、高效性。

●形成风格良好和完整的文档。

●实现在FPGA不同厂家之间以及从FPGA到ASIC的顺利移植。

●便于新员工快速掌握本部门FPGA的设计流程。

由于目前所用到的FPGA器件以Altera的为主,所以下面的例子也以Altera为例,工具组合为modelsim + LeonardoSpectrum/FPGACompilerII + Quartus,但原则和方法对于其他厂家和工具也是基本适用的。

目录1. 基于HDL的FPGA设计流程概述 (1)1.1 设计流程图 (1)1.2 关键步骤的实现 (2)1.2.1 功能仿真 (2)1.2.2 逻辑综合 (2)1.2.3 前仿真 (3)1.2.4 布局布线 (3)1.2.5 后仿真(时序仿真) (4)2. Verilog HDL设计 (4)2.1 编程风格(Coding Style)要求 (4)2.1.1 文件 (4)2.1.2 大小写 (5)2.1.3 标识符 (5)2.1.4 参数化设计 (5)2.1.5 空行和空格 (5)2.1.6 对齐和缩进 (5)2.1.7 注释 (5)2.1.8 参考C语言的资料 (5)2.1.9 可视化设计方法 (6)2.2 可综合设计 (6)2.3 设计目录 (6)3. 逻辑仿真 (6)3.1 测试程序(test bench) (7)3.2 使用预编译库 (7)4. 逻辑综合 (8)4.1 逻辑综合的一些原则 (8)4.1.1 关于LeonardoSpectrum (8)4.1.1 大规模设计的综合 (8)4.1.3 必须重视工具产生的警告信息 (8)4.2 调用模块的黑盒子(Black box)方法 (8)参考 (10)修订纪录 (10)1. 基于HDL的FPGA设计流程概述1.1 设计流程图说明:●逻辑仿真器主要指modelsim,Verilog-XL等。

quartus第三方工具的使用

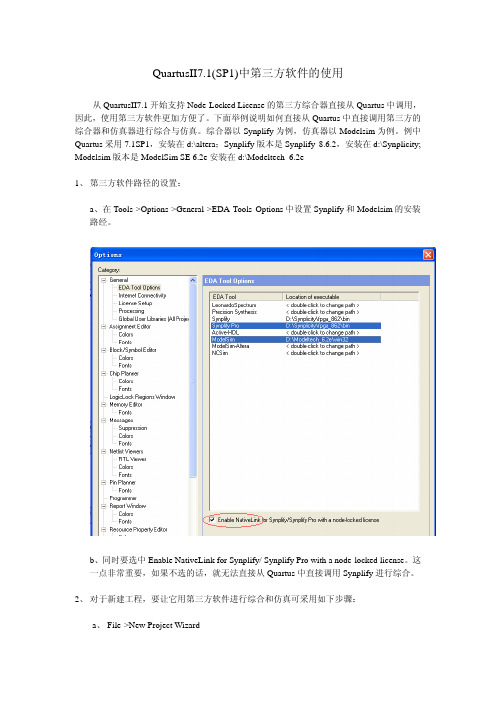

QuartusII7.1(SP1)中第三方软件的使用从QuartusII7.1开始支持Node-Locked License的第三方综合器直接从Quartus中调用,因此,使用第三方软件更加方便了。

下面举例说明如何直接从Quartus中直接调用第三方的综合器和仿真器进行综合与仿真。

综合器以Synplify为例,仿真器以Modelsim为例。

例中Quartus采用7.1SP1,安装在d:\altera;Synplify版本是Synplify 8.6.2,安装在d:\Synplicity; Modelsim版本是ModelSim SE 6.2e安装在d:\Modeltech_6.2e1、第三方软件路径的设置:a、在Tools->Options->General->EDA Tools Options中设置Synplify和Modelsim的安装路经。

b、同时要选中Enable NativeLink for Synplify/ Synplify Pro with a node-locked license。

这一点非常重要,如果不选的话,就无法直接从Quartus中直接调用Synplify进行综合。

2、对于新建工程,要让它用第三方软件进行综合和仿真可采用如下步骤:a、File->New Project Wizard点Next进行下一步。

b、设置工程路径,完成后点Next进行下一步。

c、如果己有源程序,可以在此加入到工程中,如果没有选Next进行下一步。

d、选择器件e、设置第三方工具,EDA design entry/synthesis tool选Synplify,选中Run this toolautomatically to synthesize the current design;EDA simulation tool选Modelsim;如果让Quartus在综合、适配后自动调用Modelsim进行门级时序仿真可以选中Run Gate Level Simulation automatically after compilation,点Next进行下一步。

quartus与modelsim联合仿真步骤总结自己

1.首先安装好quartus和modelsim2.复制altera quartus eda sim_lib 中对应芯片的.v文件到modelsim文件夹内3.打开quartus新建工程在第四步eda tool setting 中simulation选项中选择modelsim 语言默认为veillog 后面不打勾4.assignments settings eda stimulation工具选择modelsim 路径选择modelsim安装的路径写到win32这一步点击确定至此准备工作全部完成5.写veillog 程序然后保存编译编译后会在我们的工程目录下生成simulation文件夹,里面又有一个modelsim文件夹。

6.创建或者是编写testbench引导文件简单的可以创建复杂的需要自己编写quartus自己创建不了这是一个端口引导文件目的是建立modelsim和quartus之间的桥梁能够让modelsim创建出我们需要的与quartus中相匹配的端口并且执行相同的功能这些功能执行信息都存放在了testbench引导文件当中7.创建testbench文件过程:Processing->Start->Start Test Bench Template Write这时创建的testbench文件存放在4中所说的modelsim文件夹中以.vt为后缀名以工程名命名8.添加该文件:Assignments->EDA Tool Settings选择Simulation设置仿真环境在NativeLink settings中选择Compile test bench并点击后面的Test Benches 在Test Benches中点击New设置Test Bench属性在Test bench entity栏一定要填写刚刚我们创建的testbench文件的实体名即module top_vlg_tst();中的top_vlg_tst。

如何在modelsim中添加altera的仿真库

1.在quartus中运行2.选择器件及输出目录,编译后生成库。

3.打开D:\altera\modeltech64_10.1c\altera_lib\modelsim.ini查看[Library] 中的这就是所选的器件对应的生成库。

altera_ver = D:/altera/modeltech64_10.1c/altera_lib/verilog_libs/altera_ver lpm_ver = D:/altera/modeltech64_10.1c/altera_lib/verilog_libs/lpm_versgate_ver = D:/altera/modeltech64_10.1c/altera_lib/verilog_libs/sgate_veraltera_mf_ver = D:/altera/modeltech64_10.1c/altera_lib/verilog_libs/altera_mf_veraltera_lnsim_ver = D:/altera/modeltech64_10.1c/altera_lib/verilog_libs/altera_lnsim_vermaxii_ver = D:/altera/modeltech64_10.1c/altera_lib/verilog_libs/maxii_vercycloneii_ver = D:/altera/modeltech64_10.1c/altera_lib/verilog_libs/cycloneii_ver可以复制这些项存到D:\altera\modeltech64_10.1c\modelsim.ini即根目录下的modelsim.ini中的[Library] 注意修改只读属性; Altera library add by Sylaraltera_ver = $MODEL_TECH/../altera_lib/verilog_libs/altera_verlpm_ver = $MODEL_TECH/../altera_lib/verilog_libs/lpm_versgate_ver = $MODEL_TECH/../altera_lib/verilog_libs/sgate_veraltera_mf_ver = $MODEL_TECH/../altera_lib/verilog_libs/altera_mf_veraltera_lnsim_ver = $MODEL_TECH/../altera_lib/verilog_libs/altera_lnsim_vermaxii_ver = $MODEL_TECH/../altera_lib/verilog_libs/maxii_vercycloneii_ver = $MODEL_TECH/../altera_lib/verilog_libs/cycloneii_ver或者如何在modelsim中添加altera的仿真库上一篇/ 下一篇2009-07-31 14:36:17查看( 6137 ) / 评论( 1 ) / 评分( 0 / 0 )呵呵,这个问题纠结了我两天了,刚才又试了一下就通过了,其实网上的资料说的很清楚的,但是操作起来还真的容易失误,所以说不会的时候觉得怎么这么难搞,会了之后、发现怎么这么简单!首先为什么要在modelsim中加仿真库呢?我的理解是这样的,modelsim仿真功能强大,但是没有跟具体的器件相结合所以不能够进行时序仿真和后仿真。

在quartusII中用modelsim-altera仿真

在quartusII中用modelsim_altera做功能仿真1.设置modelsim_altera的执行路径(即其安装路径中的可执行文件的路径)(1)Tool→Options(2)打开如下图:(3)选择general →EDA Tool Options,在右侧的窗口中选择Modelsim_Altera,在Location of Executable中单击,用浏览的方式找到该软件的安装路径中的可执行文件路径,单击确定。

到此仿真软件的设置基本完成了。

2.项目仿真当我们建立一个新的项目时是需要对其中代码进行仿真的,整个过程需要三步:2.1首先,要预先设置仿真软件;下面介绍如何预设仿真软件。

1.Assignments→Settings…2.打开如下界面3选择“Simulation”,右侧设置按上图设置。

2.2其次,仿真之前需要编写测试平台,测试平台有两种的方法:●直接建立XX.v文件●在quartusII中自动生成测试平台模板文件,文件为XX.vt文件下面介绍如何自动生成测试平台模板文件。

1.Processing→Start→Start Test Bench Template Writer注意:要生成testbench模板的前提条件是为项目选择预用的仿真软件,然后模块必须编译成功。

Testbench模板生成后的默认路径为:项目目录\simulation\modelsim\项目名.vt(因为刚才在预设置仿真软件时的“Output Directory”选择的是默认的值simulation\modelsim)。

2.对于自动生成的测试平台模版需要打开修改测试激励信号,这里不做介绍,很简单的。

2.3改写完后要在项目里添加测试平台文件到项目里。

1.Assignments→Settings…2.在打开界面做如下操作:(1)选择“Compile test bench”,然后单击“Test Benches…”(2)打开下面的窗口(3)单击“New”打开下面的窗口,且按图中填写相关信息这个窗口是用来输入testbench的资料和选择testbench的路径的。

【转】Xilinx和Altera的FPGA的对比

【转】Xilinx和Altera的FPGA的对⽐Xilinx和Altera的FPGA的对⽐[原创⽂章,转载请注明出处tengjingshu]⽼板布置了⼀个任务:搞⼀个符合要求的DDS(直接数字频率合成),其中要求DDS存储波形的ROM地址要48位,天啊,这可是2的48次这么多个byte,FPGA有这么多空间吗?于是我就⽐较了⼀下Xilinx和Altera的FPGA逻辑资源。

(其实DDS中存储波形数据的ROM地址为没必要搞到48位,正弦波形间隔两位的数据差不了多少可以省了很多步长,加上其实只要存储1/4正弦波波形的数据既可,所以地址位可以减少到12位)。

要⽐较Xilinx和Altera的FPGA,就要清楚两个⼤⼚FPGA的结构,由于各⾃利益,两家的FPGA结构各不相同,参数也各不相同,但可以统⼀到LUT(Look-Up-Table)查找表上。

关于两家FPGA的结构,可以参考:1.2.我师姐⽤的是Altera的Cyclone II系列的EP2C35,我⽤的是Xilinx的Spartan-3E系列的XC3S500E。

可以参考Datasheet。

Cyclone IISpartan-3E其中Altera的LEs和Xilnx的CLB(Slice)【其中1 Slices="1" CLB】对应于LUT的结构。

Altera从LEs的结构可以知道 1 LEs = 1 LUTXilinx下图是1 Slice的结构,从Slice的结构可以看到1 Slice = 2 LUT =4 CLB从⽽可以知道Xilinx和Altera FPGA逻辑资源的对应关系:(为了统⼀度量衡(感觉像QSH⼀样),业界⼀般会归结到BLM(Basic Logic Module)1 BLM=1 LUT4(四输⼊查找表)+DFF(D触发器)1 BLM=0.5 Slice(Xilinx)=1 LE(Altera)=2.25 Tile(Actel)于是就可以知道Altera的Cyclone II系列的EP2C35有33216个LUT,我⽤的是Xilinx的Spartan-3E系列的XC3S500E有9312个LUTL 呜呜……加上EP2C35还有4个PLL,我的XC3S500E就跟⽐不上了参考资料:1. Altera Cyclone II系列⼿册 2. Xilinx Spartan-3E系列⼿册 3. 【器件求助】XILINX FPGA 和 ALTERA FPGA在逻辑单元是怎么算的? 4. PLD/FPGA 结构与原理初步5. xilinx和Altera的fpga對⽐?6. 做个⼩调查,Xilinx的Spartan-3和Altera的MAX II,哪个⽤的更多? 7. Altera/Xilinx FPGA逻辑门计算 8. 【EDA技术】第⼆章 FPGA/CPLD的结构与应⽤(⼀)9. 【EDA技术】第⼆章 FPGA/CPLD的结构与应⽤(⼆)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ModelSim+Synplify+Quartus 的Altera FPGA 的仿真实

现

工作内容: 1、设计一个多路选择器,利用ModelSimSE 做功能仿真;2、利用Synplify Pro 进行综合,生成xxx.vqm 文件;3、利用Quartus II 导入xxx.vqm 进行自动布局布线,并生成xxx.vo(Verilog 4、利用ModelSimSE 做后仿真,看是否满足要求。

注: 1. 仿真器(Simulator)是用来仿真电路的波形。

2. 综合工具(Synthesizer)的功能是将HDL 转换成由电路所组成的Netlist。

3. 一般而言,在电路设计的仿真上可分为Pre-Sim 和Post-Sim。

Pre-Sim 是针而Post-Sim 则是针对综合过且做完成了Auto Place and Route(APR)的电路进行仿真,以确保所设计的电路实现在FPGA 上时,与Pre-Sim 的功能一样。

1、前仿真(Pre-Sim)步骤一:打开ModelSimSE,然后建立一个Project;※建立Project 的方式为点选File →New →Project…;※设定Project Name 与Project location,按OK 即可建立Project。

步骤二:新增设计文档或加入文档。

※新增文档的方式为点选File →New →Source →Verilog,然后对文档进行编辑并

储存为xxx.v;※加入文档的方式为点选File →Add to Project →File...,然后

点选xxx.v;步骤三:编译(Compile)。

※编译文档的方式为点选Compile →Compile All,即可编译所有的文档。

※如果编译时发生错误,在显示错误的

地方(红字)点两下,即可跳到错误。

步骤四:新增或加入测试平台(Testbench)。

※当设计完电路后,为了确定所设计的电路是否符合要求,我们会写一个测

试平台(Testbench);※新增或加入测试平台,然后编译它。

步骤五:仿真(Simulate)。

※仿真的方式为点选Simulate →Simulate…;※打开Design 里面的work,然后点选mux_4_to_1_tb 并Add 它,最后按Load 即可跳到仿真窗口。

步骤六:加入信号线。

※在窗口上按右键,然后点选Add →Add to。