8触发器_第五章(latch_flipflop)

第五章触发器Flip-Flops触发器具有记忆功能的基本逻辑

特征方程 Q* =S+R’Q

CLK=1

约束条件 RS=0 Q* = Q CLK=0 在S=R=1时,CP↓0,输出状态不确定。

简化真值表 S R 0 0 1 1 0 1 0 1 Q* Q 0 1 1*

输出波形

异步置位端S’D、异步复位端R’D,置0、置1 不受CLK 、S 、R影响,预置成指定的状态。

主从J-K触发器的一次翻转问题: 0 主触发器在CLK=1期间随J、 0 K输入变化。 从触发器的输出Q、Q’反 馈到J、K端, 0 1 0

1

0

1 1 由于Q、Q’在CLK=1期间不变, 所以J、K变化只能引起主触发器的一次翻转。

多输入端的主从JK触发器符号

J K

0 0 1 1 0 1 0 1

Q*

特性表、真值表 (Truth table)

S’D R’D Q Q*

0

S’D =0,R’D =1时Q*=1,置1信号,与Q无关。 S’D =1,R’D =0时Q*=0,置0信号,与Q无关。 置1端set,清0端、复位端Reset。 S’D =1,R’D =1时Q*= Q。 S’D =0,R’D =0时Q*=1*,不确定。 S’D,R’D不能同时为0, 约束条件S’D + R’D =1

D触发器 The Gated D Latch

D 0 1 Q* 0 1

CP=0 Q保持不变 CP=1 Q* =D

5.3 脉冲触发的主从RS触发器 The Master-slave R-S Flip-Flops

G1--G4门从触发器, G5—G8门主触发器, CLK=1,G3、G4封锁, G7、G8打开,主触发器翻转, 从触发器保持不变。 CLK↓=0,G7、G8封锁, S、R输入变化不会引起主触发器 状态变化,G3、G4打开, 从触发器按照主触发器相同状态翻转。 在CLK↓,从触发器只变化一次。 真值表、特性方程、约束条件与钟控RS触发器一样。 CLK=1期间,主触发器状态随SR可以改变多次, 从触发器只在CP↓下降沿时改变一次。 已知CP、S和R的电压波形,初态为0,求Q和Q’的输出波形:

Chapter 8.1

Q

Q

Qn+1 = SRQn + SRQn + SRQn = SR + SRQn

SR = 0 Qn+1 = S+ RQn

13

8.1 Latches

Example (1):

14

8.1 Latches

An IC S-R Latch 74LS279

Pin diagram Logic diagram

15

8.1 Latches

Q

R

1

G2

Q

0 1

R

G2

Q

0 1

9

8.1 Latches

5) S =1 R = 0, Q=1 ,

1

6) S =1 R = 0, Q= 0 ,

1

S

1 0 G1

Q

S

0 G1

Q

R

0

G2

Q

0 1 0

R

G2

Q

1

10

8.1 Latches

7) S = 0, R = 0, Q=1

0

8) S = 0, R = 0, Q= 0

Q

18

8.1 Latches

5) S = 0, R = 1, Q = 0

0 1 G1 G3

6) S = 0, R = 1, Q = 1

0 0 1 G1 G3

S

1 0

S Q

1 0

0 1

Q

EN R

1 G2 0 G4 1

EN

Q

1

R

G2 0

G4 0 1

Q

19

8.1 Latches

7) S = 1, R = 1, Q = 0

数字电路触发器详解

广东工业大学 自动化学院

解:

[例] 试对应输入波形画出下图中 Q 端波形。假设触发器的初态为“0”。

Q

CLK

R

Q

Q

S

0

0

1

0

0

0

0

1

CLK = 0 时, 触发器状态不变。

CLK = 1 时,触发器根据 S、R 取值翻转。

只在CLK= 1期间接受输入信号

5.3 电平触发的触发器

本章的重点: 1.各种电路结构的触发器所具有的特点; 2.触发器逻辑功能的分类和触发器逻辑功能的描述方法。 3.要注意区分触发器的电路结构和逻辑功能这两个不同的概念。

5.1 概述

广东工业大学 自动化学院

一、触发器的特点

(1)有两个稳定状态(简称稳态),用来表示逻辑 0 和 1。

异步置1端

异步置0端

小圆圈表示低电平有效

5.3 电平触发的触发器

广东工业大学 自动化学院

[例] 试对应输入波形画出下图中 Q 端波形。

R'D

CLK

R

Q'

Q

1S

S

C1

CLK

R

1R

R

S

VCC

R'D

S

解:

原态未知

Q

VCC

R'D

R'D

0

0

1

0

0

0

0

1

异步置0

5.3 电平触发的触发器

广东工业大学 自动化学院

0

0

0

0

广东工业大学 自动化学院

动作特点 直接控制:输入信号直接加在输出门上,在输入信号全部作用时间内,都能直接改变输出端的状态(即只要有输入信号,就能作用于电路)。故又称该电路为直接复位、置位锁存器。

第五章_11_概述基本SRFF.讲义

逻辑功能 不允许 (不定) 置“ 1”

置“ 0”

保

持

10

表 5.2.2 与非门基本触发器的功能表

SD

0 Байду номын сангаас 1 1

RD

0 1 0 1

Q n 1

× (ф )

1 0

Q

n

RDQ SD

0

1

n

00 0

01

11

10

×

×

0

1

1

1

0

图 5.2.2 求次态方程的卡诺图

第五章 触发器 11

(4)状态转移图

(5)激励表(驱动表) (6)波形图(时序图) SD=0 RD=1 S D= RD=1

n+1

Q

n+1

0 1

Q

n n+1

G1 & 置0 置1 SD 保持 = 1 不允许

& G2

RD

= Q

结论:SD 、RD 低电平有效。

第五章 触发器 8

(4)脉冲工作特性

触发脉冲的持续时间 tw > 2tpd 3.逻辑功能的表示方法 (1)状态转移表(特性表)

(2)功能表:状态转移表简化形式

(3)次态方程

SD=1 R D=

0

1

SD=1 RD=0 图 5.2.3 与非门基本触发器的状态转移图

第五章 触发器 12

表 5.2.3 与非门基本触发器的激励表

状 态 转 移

输 入 条 件

n 1

Q

0 0 1 1

n

Q

SD 1 0 1 ф

RD ф 1 0 1

0 1 0 1

第五章 触发器

数字电子技术第五章 触发器

缺点:在CLK有效电平期间,且脉冲宽带较宽时,触发 器将会出现连续不停的多次翻转。

由于在CLK=1期间,同步触发器的控制门都是开放的,触发 器都可以接收输入信号而翻转,所以在CP=1期间,如果输入信 号发生多次变化,触发器的状态也会发生相应的改变。

这种由于输入信号变化而引起的触发器翻转的现象,称为触 发器的空翻现象。

5.4 脉冲触发的触发器 在每个CLK周期里输出端的状态只能改变一次。 一、脉冲触发的SR触发器(主从触发器) 1.电路结构:由两个相同的电平触发SR触发器组成,主从 CLK信号的相位相反。

Qm

S,Q' m

R;

Q

Qm , Q'

Q' m

S R

Qm Q'

Q Q'

m

主触发器的输出信号是从触发器的输入信号,因而从触发 器的输出状态将按照主触发器的输出状态来动作。

CLK=1时,S、R通过G3、G4反相加到与非门锁存器上, 输出端状态跟随输入信号的变化而改变,将CLK的这种控制

方式称为电平触发方式。 与非门锁存器本身是低电平有效,加上G1G2的反相,此

电平触发器SR变为高电平有效。

CLK S 0×

功能表(特性表)

R Q Q*

功能

× × Q Q*=Q 保持

1 0 00 0 Q*=Q保持

SR锁存器也可以用与非门构成

0

SD ' RD ' Q Q *

1

01 0 1 01 1 1

0 1

SR锁存器也可以用与非门构成

1

SD ' RD ' Q Q *

0

01 0 1

01 1 1

10 0 0

锁存器Latch和触发器Flip-flop有何区别

锁存器Latch和触发器Flip-flop有何区别锁存器Latch概述锁存器(Latch)是一种对脉冲电平敏感的存储单元电路,它们可以在特定输入脉冲电平作用下改变状态。

锁存,就是把信号暂存以维持某种电平状态。

锁存器的最主要作用是缓存,其次完成高速的控制器与慢速的外设的不同步问题,再其次是解决驱动的问题,最后是解决一个I/O口既能输出也能输入的问题。

锁存器是利用电平控制数据的输入,它包括不带使能控制的锁存器和带使能控制的锁存器。

锁存器Latch结构latch:锁存器,是由电平触发,结构图如下:锁存器latch的优缺点优点:1、面积比ff小门电路是构建组合逻辑电路的基础,而锁存器和触发器是构建时序逻辑电路的基础。

门电路是由晶体管构成的,锁存器是由门电路构成的,而触发器是由锁存器构成的。

也就是晶体管-》门电路-》锁存器-》触发器,前一级是后一级的基础。

latch完成同一个功能所需要的门较触发器要少,所以在asic中用的较多。

2、速度比ff快用在地址锁存是很合适的,不过一定要保证所有的latch信号源的质量,锁存器在CPU设计中很常见,正是由于它的应用使得CPU的速度比外部IO部件逻辑快许多。

缺点:1、电平触发,非同步设计,受布线延迟影响较大,很难保证输出没有毛刺产生2、latch将静态时序分析变得极为复杂触发器Flip-flop结构lip-flop:触发器,是时钟边沿触发,可存储1bitdata,是register的基本组成单位,结构图如下:flip-flop的优缺点优点:1、边沿触发,同步设计,不容易受毛刺的印象2、时序分析简单缺点:1、面积比latch大,消耗的门电路比latch多锁存器Latch和触发器flipflop的区别1、锁存器Latch和触发器flipflop锁存器能根据输。

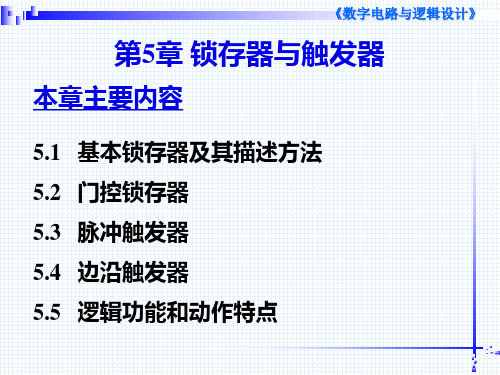

第5章 锁存器与触发器

《数字电路与逻辑设计》

3) 状态转换图与激励表

将锁存器两个状态之间的转换及其所需要的输 入条件用图形的方式表示称为状态转换图(简称为 状态图),用表格的形式表示则称为激励表。

基本SR锁存器的状态图如下图所示,表5-2为 其激励表。

表5-2 基本SR锁存器的激励表

SD=0

RD=´

0

SD=1 RD=0

《数字电路与逻辑设计》

第5章 锁存器与触发器

本章主要内容

5.1 基本锁存器及其描述方法 5.2 门控锁存器 5.3 脉冲触发器 5.4 边沿触发器 5.5 逻辑功能和动作特点

《数字电路与逻辑设计》

本章重点:

掌握锁存器与触发器的电路结构、逻辑 功能和动作特点

本章难点:

触发器的工作原理

《数字电路与逻辑设计》

此外,锁存器的功能还可以用状态转换图和激 励表表示。

《数字电路与逻辑设计》

1) 特性表(真值表) 基本锁存器的特性表如表5-1所示。

表5-1 基本SR锁存器特性表 与非门构成的锁存器 或非门构成的锁存器 SD RD Q Q* SD RD Q Q* 1 1 0 0 0000 1 1 1 1 0011 1 0 0 0 0100 1 0 1 0 0110 0 1 0 1 1001 0 1 1 1 1011 0 0 0 × 1 1 0× 0 0 1 × 1 1 1×

《数字电路与逻辑设计》

(2) CLK为高电平时, 由于SD=(S·CLK)=S、RD=(R·CLK)=R,因 此门控锁存器将根据输入信号S和R实现其相应的 功能。

将SD=S、RD=R代入到基本锁存器的特性方 程Q*=SD+RD·Q,可得到门控锁存器的特性方程为

Q*=S+R·Q

触发器Flip-Flops和时序电路

组合逻辑电路组成,能够将输入信号向左或向右移动指定的位数。

时序电路的应用

数字逻辑控制

时序电路在数字逻辑控制中有着 广泛的应用,例如在计算机、数 字交换机、数控机床等设备中, 都需要使用时序电路来实现数字

逻辑控制。

通信技术

在通信技术中,时序电路被广泛 应用于数字信号处理、调制解调、

信道编码等领域。

自动控制

寄存器

寄存器是一种常见的触发器与时序电 路的组合,它由多个触发器组成,用 于存储二进制数据。

计数器

计数器是一种能够自动计数输入脉冲 个数的时序电路,它由多个触发器和 门电路组成。

05 触发器Flip-flops和时序 电路的优化与挑战

触发器Flip-flops的优化策略

减少功耗

通过降低时钟频率、使用低功耗设计 和工艺、以及优化时钟网络来降低功 耗。

触发器Flip-flops是数字逻辑电路 中的基本存储单元,用于存储二进 制状态(0或1)。

工作原理

触发器Flip-flops采用双稳态电路 ,通过时钟信号控制数据输入和 输出,实现状态的存储和切换。

触发器Flip-flops的类型

01

02

03

JK触发器

具有置0、置1、翻转和保 持四种功能,通过改变时 钟信号的相位实现不同操 作。

提高速度

通过优化触发器的结构、减少内部延 迟和传播延迟,以及采用更快的时钟 源来提高速度。

减小面积

通过优化设计、采用更小的单元尺寸 和更高效的布局布线技术来减小面积。

提高可靠性

通过采用冗余设计、错误检测和纠正 技术以及容错逻辑来提高可靠性。

时序电路的优化策略

优化时钟网络

通过减少时钟源的数量、降低时钟频率、 优化时钟分布和减少时钟偏斜来优化时钟

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

•

•

所以,为了使电路正常工作,必须: – 禁止锁存器,直到+将新值准备好。 – 锁存器只需要在很短的时间使能,以便更新数据. 两个问题: 如何知道新值已准备好? 加入新的信号,当该信号变为1时,锁存器知道 +计算已完成,可 以 将新数据存入。

如何使能,然后迅速禁止latches? 使用触发器

28

Current Q Q‟ 0 1 0 1 0 1 1 0 1 0 1 0

Next Q Q‟ 0 1 0 0 1 1 1 0 1 1 0 0

17

SR latches 是时序电路!

• • •

注意到 SR = 00, Q 的 次态可能为“0”,也可能为 “1”,依赖于 Q 的现态. 同样的输入产生了不同的 输出,与锁存器的当前状 态有关。 与组合电路不同。

•

Qnext = Q’next = 1 返回到 NOR 输入端,使 得: Qnext = (0 + 1)’ = 0 Q’next = (0 + 1)’ = 0

0

0

• • •

电路进入到一个无限循环,Q , Q’ 不断在 0 和 1 之间变化。 所以要求 不能出现SR=11! 总结:当有效电平同时撤消时,次态不确定。 所以 SR=0 为或非门SR锁存器的约束条件。

8

什么是存储器(单元,内存)?

存储单元应有三个性质: 1. 能够保存值. 2. 能够将保存的值读出. 3. 能够写入新值. 一个一位存储单元: 1. 能够保存一位二进制数, 0 或者 1. 2. 能够读. 3. 能够写: – Set:写 1 置位 – Reset, 或 clear:写 0. 复位

9

16

SR latche 存储单元!

• • •

如右图,或非门SR锁存器高电平有效. 输出 Q 代表锁存器保存的数据,称为锁 存器的状态. 下图称为状态表state table, 包含输入, 现态,次态。

S 0 0 1 R 0 1 0 Q No change 0 (reset) 1 (set)

Inputs S R 0 0 0 0 1 1 0 0 1 1 0 0

•

clห้องสมุดไป่ตู้ck :特殊的设备,连续周期性地输出 0,1.

时钟周期 (clock period)

• • • •

时钟周期 (clock period, or clock cycle time.) 时钟频率 ( clock frequency) : hertz. Clocks 通常用于同步电路。 – 依赖连续的,可预期的0,1 触发电路中某种事件,例如写入锁存器 – 如果若干电路模块共享时钟,则可以协调它们之间的行为。 正如人类.

0

1

0

1

19

S’R’ latch

• •

SR锁存器的其它形式: 用 NAND 取代 NOR 成为 S’R’ latch.

S‟ 1 1 0 0 R‟ 1 0 1 0 Q No change 0 (reset) 1 (set) Avoid!

在任何时刻,输入都能直接影响输出的状态。 没有控制信号!!!

20

3. 锁存器状态保持稳定直到S , R 发生变化。

R

Q Q‟

15

复位(置0): SR = 01

• •

S = 0 且 R = 1? 当 R = 1: Qnext = (1 + Q’current)’ = 0 Q 的新值加到NOR 门,此时 S = 0. Q’next = (0 + 0)’ = 1

•

• • •

• • •

Qnext = Q’next = 0 与 Q , Q’ 互补的假设相反。 若此时SR同时变化, S = 0 且 R = 0 ,则: Qnext = (R + Q‟current)‟ Q‟next = (S + Qcurrent)‟

0 0

Qnext = (0 + 0)’ = 1 Q’next = (0 + 0)’ = 1

14

Latch 的延迟

• •

时序图对理解时序电路非常有用 下面是 SR=10 的时序图.

0. 假设初始状态, Q = 0 and Q’ = 1.

1. 当 S=1, Q’在1个门延迟后从 1 变到 0。 2. Q’的变化以及 R=0, 使得Q在1个门延迟后 变为1 . Qnext = (R + Q‟current)‟ Q‟next = (S + Qcurrent)‟ 0 S 1 2 3 4

3

Clocks 在数字系统中普遍使用

• 处理器在一个内部时钟下工作. – 当代处理器芯片的时钟 3.2 – 时钟周期为0.31 ns!

• •

GHz.

内存模块也以时钟作为分类: —如 “PC133” , “DDR400” 注意:高的时钟不一定运行更快! – 还应该考虑在一个clock cycle 里究竟完成了那些工作

S 0 0 1

R 0 1 0

Q No change 0 (reset) 1 (set)

Inputs S R 0 0 0 0 1 1 0 0 1 1 0 0

Current Q Q‟ 0 1 0 1 0 1 1 0 1 0 1 0

Next Q Q‟ 0 1 0 0 1 1 1 0 1 1 0 0

18

SR = 11?

组合电路 (Combinational circuits )

Inputs 组合电路 Outputs

组合电路: • 任何时候,相同输入 产生 相同输出.

•

•

类似于数学函数,每个输入有唯一的,确定的输 出。

在程序设计领域,组合电路类似于没有参数和赋 值功能的“子函数” 。

1

时间?

2

Clocks 和同步

C 0 1 1 1 1 S x 0 0 1 1 R x 0 1 0 1 S‟ 1 1 1 0 0 R‟ 1 1 0 1 0 Q No change No change 0 (reset) 1 (set) Avoid!

电平触发

在CLK 1期间,Q和Q可能随S、R变化多次翻转

22

D latch

•

6

时序电路设备的实例

– 密码锁. – 电梯控制器 – 交通灯的控制

计算机本身也是时序电路: 当你按下键盘和鼠标时,计算机的响应不同, 这取决于当前运行的程序和程序所处的状态。

7

时序电路 :具有记忆功能的硬件电路.

学习内容 : – 基本的记忆单元. – 时序电路的分析与设计. – 常用的时序部件.

• •

• •

总之:SR = 10, Q’next = 0 , Qnext = 1.

此状态称为锁存器的“1”状态 ,实现了写“1” ,即置位 “set” 。S称为置位端。 注意:当S为1 至 Qnext =1 ,有两级门延迟。 但一旦 Qnext 成为1 ,输出不再变化,成为稳定 状态stable state.

•

•

即当 SR = 00, Qnext = Qcurrent. 为何值,它将保存该值. 这就是锁存器的存储store功能 .

所以不论 Q

Qnext = (R + Q’current)’ Q’next = (S + Qcurrent)’

13

置位: SR = 10

• • •

S = 1 且R = 0? 因为S = 1, 所以: Q’next = (1 + Qcurrent)’ = 0 所以: Qnext = (0 + 0)’ = 1 Qnext = (R + Q‟current)‟ Q‟next = (S + Qcurrent)‟

带有控制端的 SR 锁存器

C 0 1 1 1 1

S x 0 0 1 1

R x 0 1 0 1

S‟ 1 1 1 0 0

R‟ 1 1 0 1 0

Q No change No change 0 (reset) 1 (set) Avoid!

控制信号C作为使能信号

注意:有效电平为高电平

21

动作特点:在CLK=1的全部时间里,S和R的变化都将引起输出状态的变化。导致空翻 。

30

触发器Flip-Flops

•

锁存器的问题? – 何时使能锁存器. – 应该快速地禁止锁存器. – 即锁存器的定时 所以,引入: 时钟clocks,触发器 flip-flops – Clocks 解决何时写入的问题. – Flip-flops 保证在精准的时刻快速地将数据写入。

26

•

当+ 完成运算,使能锁存器 ,C=1, 将新值存入锁存器。

+1 0001 Q Latches S X + G 0001 D

C

1

• 迅速禁止锁存器,以免在+完成 0001+1= 0010. 之前将 0001 再次装入锁存

器。

+1 0001 Q Latches S X

+

G

0010 D C 0

27

•

使用 clock 同步锁存器和 +. – 时钟信号送入 C. – 用时钟信号控制锁存器,当其为1时,使能锁存器,可使其写入。

+1 S X Q

+

G

Latches

D

C

• •

时钟周期必须仔细设计 : – 不能太短,否则在+完成运算之前,就会开始写入旧值。 – 不能太长,否则 + 可能“意外”存入一个新值。 如果 + 运行更快,则时钟周期可以更短。

存储的基本思想

• • •

如何让一堆门具有 “记忆” ? 基本的想法是设计一个回路,电路的输出也是输入. 如下:

•

是记忆单元? – 能够记忆 Q,. – 能够读. – 但是不能写Q!