4选1数据选择器的VHDL设计

相关主题

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

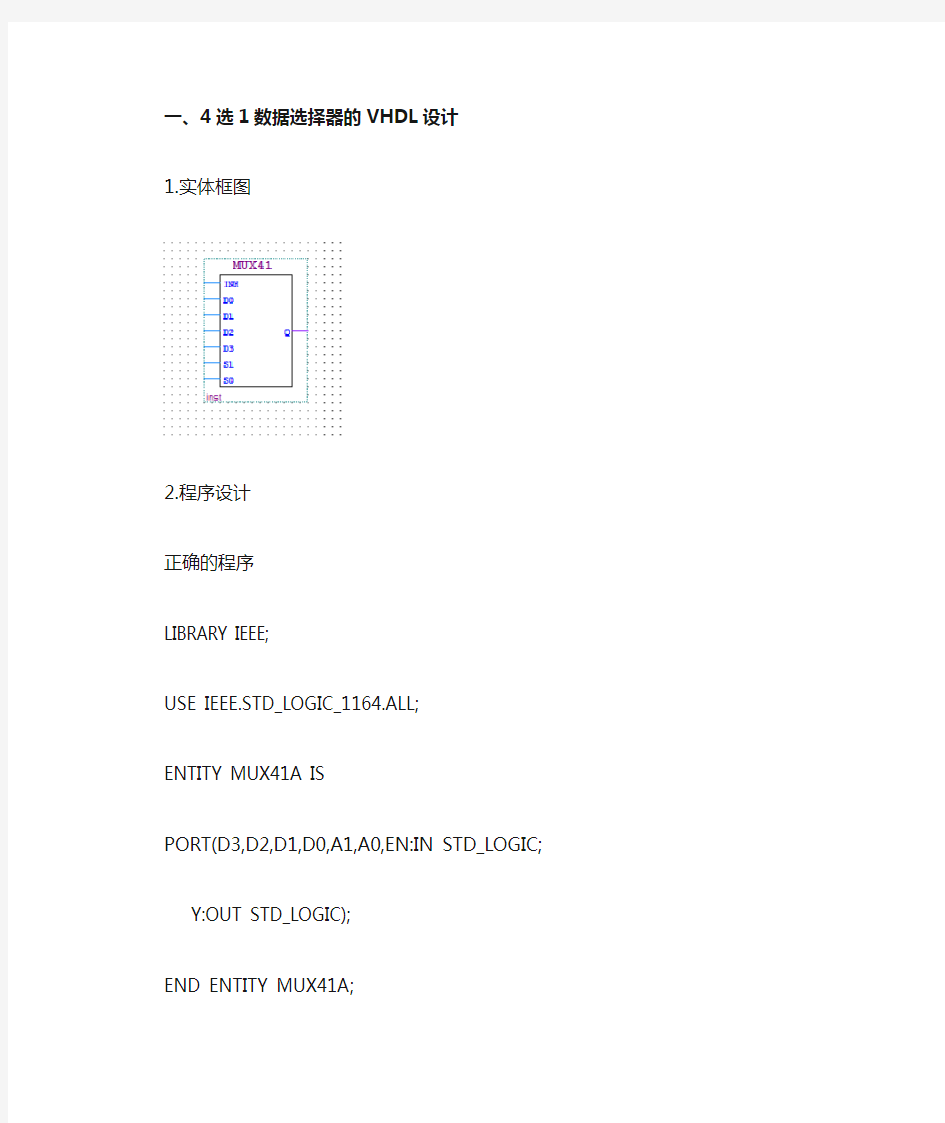

一、4选1数据选择器的VHDL设计

1.实体框图

2.程序设计

正确的程序

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY MUX41A IS

PORT(D3,D2,D1,D0,A1,A0,EN:IN STD_LOGIC;

Y:OUT STD_LOGIC);

END ENTITY MUX41A;

ARCHITECTURE ONE OF MUX41A IS

BEGIN

Y<=D0 WHEN A1='0' AND A0='0' AND EN='1'

ELSE D1 WHEN A1='0' AND A0='1' AND EN='1' ELSE D2 WHEN A1='1' AND A0='0' AND EN='1' ELSE D3 WHEN A1='1' AND A0='1' AND EN='1' ELSE 'Z';

END ARCHITECTURE ONE;

3.仿真波形图

4.仿真波形分析

由图可知,当使能EN为0时,无波形输出,当EN=1时,A1 A0=00,输出Y=D0,A1 A0=01,Y=D1,A1 A0=10,Y=D2,A1 A0=11,Y=D3。所以改程序设计为数据选择器。