MXIC Serial Flash

1主板架构讲解

18

AMD K8

PCB板

印刷電路板:Print Circuit Board

4層板包括主信號層、接地層、電源層、輔信號層 6層板比四層板多了內信號層和電源層 8層板

晶片組

晶片組(Chipset)是主機板的核心組成局部 分為北橋晶片和南橋晶片 目前主要的廠商有 Intel AMD NVIDIA SIS

DDR2 61.68mm 47%

DDR4

DDR3 53.88mm 41% DDR4 61.68mm 47%

DDR DDR2

DDR3

硬碟

硬碟由一個或多個鋁制或 玻璃制的碟片組成 它屬於外記憶體 資料存入後永久存儲 主要廠商有:

日立 三星 希捷 西部數據等

光碟機

光碟機就是光碟驅動器 光碟機可分為 CD-ROM驅動器 DVD光碟機 康寶〔COMBO〕 燒錄機 HD DVD光碟機 藍光(Blu-ray)光碟機

主機板架構講解

部門:工程部產品工程課

審核:

製作人:餘小駿

製作日期

PC總體介紹 主機板的類型 主機板上的元件 插槽及介面類別型 匯流排介紹

目錄

2021/5/18

2

PC的定義

PC (Personal Computer)個人電腦,又稱個人電腦 在機型上分為 桌上型電腦 筆記型電腦 在系統上分為 IBM整合制定的IBM PC/AT系統標准〔WINXP、 WIN7、WIN8、WIN10等〕 蘋果電腦所開發的IOS系統

SATA介面

介面 - FLOPPY 介面

FLOPPY 介面是軟盤機介面

是一種的平行傳輸介面

FLOPPY大小多為3.5英寸 FLOPPY容量1.44MB

FLOPPY

IDE

29LV160B中文资料

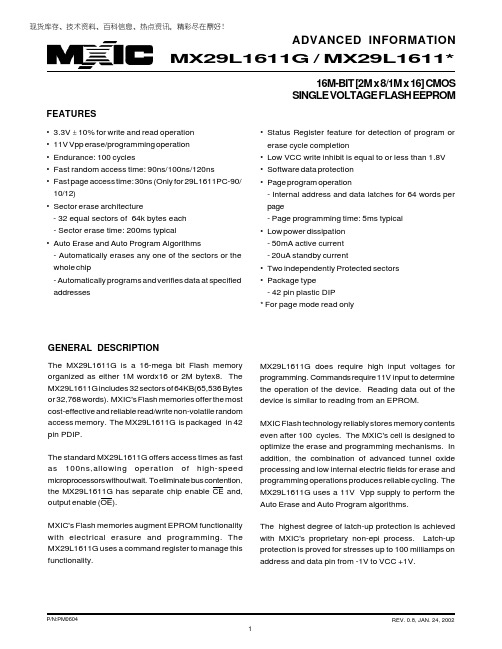

MX29LV160BT/BB16M-BIT [2Mx8/1Mx16] CMOS SINGLE VOLTAGE3V ONLY FLASH MEMORYerase operation completion.•- Provides a hardware method of detecting program or erase operation completion.•Sector protection- Hardware method to disable any combination of sectors from program or erase operations- Temporary sector unprotect allows code changes in previously locked sectors.•CFI (Common Flash Interface) compliant- Flash device parameters stored on the device and provide the host system to access•100,000 minimum erase/program cycles•Latch-up protected to 100mA from -1V to VCC+1V •Boot Sector Architecture - T = Top Boot Sector - B = Bottom Boot Sector•Low VCC write inhibit is equal to or less than 1.4V •Package type:- 44-pin SOP - 48-pin TSOP - 48-ball CSP•Compatibility with JEDEC standard- Pinout and software compatible with single-power supply Flash•10 years data retentionFEATURES•Extended single - supply voltage range 2.7V to 3.6V •2,097,152 x 8/1,048,576 x 16 switchable •Single power supply operation- 3.0V only operation for read, erase and program operation•Fully compatible with MX29LV160A device •Fast access time: 70/90ns •Low power consumption- 30mA maximum active current - 0.2uA typical standby current •Command register architecture- Byte/word Programming (9us/11us typical)- Sector Erase (Sector structure 16K-Bytex1,8K-Bytex2, 32K-Bytex1, and 64K-Byte x31)•Auto Erase (chip & sector) and Auto Program- Automatically erase any combination of sectors with Erase Suspend capability.- Automatically program and verify data at specified address•Erase Suspend/Erase Resume- Suspends sector erase operation to read data from,or program data to, any sector that is not being erased,then resumes the erase.•Status Reply- Data polling & Toggle bit for detection of program andGENERAL DESCRIPTIONThe MX29L V160BT/BB is a 16-mega bit Flash memory organized as 2M bytes of 8 bits or 1M words of 16 bits.MXIC's Flash memories offer the most cost-effective and reliable read/write non-volatile random access memory. The MX29L V160BT/BB is packaged in 44-pin SOP , 48-pin TSOP and 48-ball CSP . It is designed to be reprogrammed and erased in system or in standard EPROM programmers.The standard MX29LV160BT/BB offers access time as fast as 70ns, allowing operation of high-speed micropro-cessors without wait states. To eliminate bus conten-tion, the MX29LV160BT/BB has separate chip enable (CE) and output enable (OE) controls.MXIC's Flash memories augment EPROM functionality with in-circuit electrical erasure and programming. The MX29LV160BT/BB uses a command register to man-age this functionality. The command register allows for100% TTL level control inputs and fixed power supply levels during erase and programming, while maintaining maximum EPROM compatibility.MXIC Flash technology reliably stores memory contents even after 100,000 erase and program cycles. The MXIC cell is designed to optimize the erase and programming mechanisms. In addition, the combination of advanced tunnel oxide processing and low internal electric fields for erase and program operations produces reliable cy-cling. The MX29LV160BT/BB uses a 2.7V~3.6V VCC supply to perform the High Reliability Erase and auto Program/Erase algorithms.The highest degree of latch-up protection is achieved with MXIC's proprietary non-epi process. Latch-up pro-tection is proved for stresses up to 100 milliamps on address and data pin from -1V to VCC + 1V .RPIN CONFIGURATIONSPIN DESCRIPTIONSYMBOL PIN NAME A0~A19Address Input Q0~Q14Data Input/OutputQ15/A-1Q15(Word mode)/LSB addr(Byte mode)CE Chip Enable Input WE Write Enable Input BYTE Word/Byte Selection inputRESET Hardware Reset Pin/Sector Protect Unlock OE Output Enable Input RY/BY Ready/Busy OutputVCC Power Supply Pin (2.7V~3.6V)GNDGround Pin48 TSOP (Standard Type) (12mm x 20mm)44 SOP(500 mil)A B C D E F GH6A13A12A14A15A16BYTE Q15/A-1GND 5A9A8A10A11Q7Q14Q13Q64WE RESET NC A19Q5Q12VCC Q43RY/BY NC A18NC Q2Q10Q11Q32A7A17A6A5Q0Q8Q9Q11A3A4A2A1A0CEOEGND48-Ball CSP 6mm x 8mm (Ball Pitch=0.8mm) Top View, Balls Facing Down234567891011121314151617181920212244434241403938373635343332313029282726252423RESETA18A17A7A6A5A4A3A2A1A0CE GND OE Q0Q8Q1Q9Q2Q10Q3Q11WE A19A8A9A10A11A12A13A14A15A16BYTE GND Q15/A-1Q7Q14Q6Q13Q5Q12Q4VCCM X 29L V 160B T /B BA15A14A13A12A11A10A9A8A19NC WE RESETNC NC RY/BY A18A17A7A6A5A4A3A2A1123456789101112131415161718192021222324A16BYTE GND Q15/A-1Q7Q14Q6Q13Q5Q12Q4VCC Q11Q3Q10Q2Q9Q1Q8Q0OE GND CE A0484746454443424140393837363534333231302928272625MX29LV160BT/BBBLOCK STRUCTURETable 1: MX29LV160BT SECTOR ARCHITECTURESector Sector Size Address range Sector Address Byte Mode Word Mode Byte Mode(x8) Word Mode(x16)A19A18A17A16A15A14A13A12 SA064Kbytes32Kwords000000-00FFFF00000-07FFF00000X X X SA164Kbytes32Kwords010000-01FFFF08000-0FFFF00001X X X SA264Kbytes32Kwords020000-02FFFF10000-17FFF00010X X X SA364Kbytes32Kwords030000-03FFFF18000-1FFFF00011X X X SA464Kbytes32Kwords040000-04FFFF20000-27FFF00100X X X SA564Kbytes32Kwords050000-05FFFF28000-2FFFF00101X X X SA664Kbytes32Kwords060000-06FFFF30000-37FFF00110X X X SA764Kbytes32Kwords070000-07FFFF38000-3FFFF00111X X X SA864Kbytes32Kwords080000-08FFFF40000-47FFF01000X X X SA964Kbytes32Kwords090000-09FFFF48000-4FFFF01001X X X SA1064Kbytes32Kwords0A0000-0AFFFF50000-57FFF01010X X X SA1164Kbytes32Kwords0B0000-0BFFFF58000-5FFFF01011X X X SA1264Kbytes32Kwords0C0000-0CFFFF60000-67FFF01100X X X SA1364Kbytes32Kwords0D0000-0DFFFF68000-6FFFF01101X X X SA1464Kbytes32Kwords0E0000-0EFFFF70000-77FFF01110X X X SA1564Kbytes32Kwords0F0000-0FFFFF78000-7FFFF01111X X X SA1664Kbytes32Kwords100000-10FFFF80000-87FFF10000X X X SA1764Kbytes32Kwords110000-11FFFF88000-8FFFF10001X X X SA1864Kbytes32Kwords120000-12FFFF90000-97FFF10010X X X SA1964Kbytes32Kwords130000-13FFFF98000-9FFFF10011X X X SA2064Kbytes32Kwords140000-14FFFF A0000-A7FFF10100X X X SA2164Kbytes32Kwords150000-15FFFF A8000-AFFFF10101X X X SA2264Kbytes32Kwords160000-16FFFF B0000-B7FFF10110X X X SA2364Kbytes32Kwords170000-17FFFF B8000-BFFFF10111X X X SA2464Kbytes32Kwords180000-18FFFF C0000-C7FFF11000X X X SA2564Kbytes32Kwords190000-19FFFF C8000-CFFFF11001X X X SA2664Kbytes32Kwords1A0000-1AFFFF D0000-D7FFF11010X X X SA2764Kbytes32Kwords1B0000-1BFFFF D8000-DFFFF11011X X X SA2864Kbytes32Kwords1C0000-1CFFFF E0000-E7FFF11100X X X SA2964Kbytes32Kwords1D0000-1DFFFF E8000-EFFFF11101X X X SA3064Kbytes32Kwords1E0000-1EFFFF F0000-F7FFF11110X X X SA3132Kbytes16Kwords1F0000-1F7FFF F8000-FBFFF111110X X SA328Kbytes4Kwords1F8000-1F9FFF FC000-FCFFF11111100 SA338Kbytes4Kwords1FA000-1FBFFF FD000-FDFFF11111101 SA3416Kbytes8Kwords1FC000-1FFFFF FE000-FFFFF1111111XNote: Byte mode: address range A19:A-1, word mode:address range A19:A0.Table 2: MX29LV160BB SECTOR ARCHITECTURESector Sector Size Address range Sector Address Byte Mode Word Mode Byte Mode (x8)Word Mode (x16)A19A18A17A16A15A14A13A12 SA016Kbytes8Kwords000000-003FFF00000-01FFF0000000X SA18Kbytes4Kwords004000-005FFF02000-02FFF00000010 SA28Kbytes4Kwords006000-007FFF03000-03FFF00000011 SA332Kbytes16Kwords008000-00FFFF04000-07FFF000001X X SA464Kbytes32Kwords010000-01FFFF08000-0FFFF00001X X X SA564Kbytes32Kwords020000-02FFFF10000-17FFF00010X X X SA664Kbytes32Kwords030000-03FFFF18000-1FFFF00011X X X SA764Kbytes32Kwords040000-04FFFF20000-27FFF00100X X X SA864Kbytes32Kwords050000-05FFFF28000-2FFFF00101X X X SA964Kbytes32Kwords060000-06FFFF30000-37FFF00110X X X SA1064Kbytes32Kwords070000-07FFFF38000-3FFFF00111X X X SA1164Kbytes32Kwords080000-08FFFF40000-47FFF01000X X X SA1264Kbytes32Kwords090000-09FFFF48000-4FFFF01001X X X SA1364Kbytes32Kwords0A0000-0AFFFF50000-57FFF01010X X X SA1464Kbytes32Kwords0B0000-0BFFFF58000-5FFFF01011X X X SA1564Kbytes32Kwords0C0000-0CFFFF60000-67FFF01100X X X SA1664Kbytes32Kwords0D0000-0DFFFF68000-6FFFF01101X X X SA1764Kbytes32Kwords0E0000-0EFFFF70000-77FFF01110X X X SA1864Kbytes32Kwords0F0000-0FFFFF78000-7FFFF01111X X X SA1964Kbytes32Kwords100000-10FFFF80000-87FFF10000X X X SA2064Kbytes32Kwords110000-11FFFF88000-8FFFF10001X X X SA2164Kbytes32Kwords120000-12FFFF90000-97FFF10010X X X SA2264Kbytes32Kwords130000-13FFFF98000-9FFFF10011X X X SA2364Kbytes32Kwords140000-14FFFF A0000-A7FFF10100X X X SA2464Kbytes32Kwords150000-15FFFF A8000-AFFFF10101X X X SA2564Kbytes32Kwords160000-16FFFF B0000-B7FFF10110X X X SA2664Kbytes32Kwords170000-17FFFF B8000-BFFFF10111X X X SA2764Kbytes32Kwords180000-18FFFF C0000-C7FFF11000X X X SA2864Kbytes32Kwords190000-19FFFF C8000-CFFFF11001X X X SA2964Kbytes32Kwords1A0000-1AFFFF D0000-D7FFF11010X X X SA3064Kbytes32Kwords1B0000-1BFFFF D8000-DFFFF11011X X X SA3164Kbytes32Kwords1C0000-1CFFFF E0000-E7FFF11100X X X SA3264Kbytes32Kwords1D0000-1DFFFF E8000-EFFFF11101X X X SA3364Kbytes32Kwords1E0000-1EFFFF F0000-FFFFF11110X X X SA3464Kbytes32Kwords1F0000-1FFFFF F8000-FFFFF11111X X XNote: Byte mode:address range A19:A-1, word mode:address range A19:A0.AUTOMATIC PROGRAMMINGThe MX29LV160BT/BB is byte/word programmable us-ing the Automatic Programming algorithm. The Auto-matic Programming algorithm makes the external sys-tem do not need to have time out sequence nor to verify the data programmed. The typical chip programming time at room temperature of the MX29LV160BT/BB is less than 18 sec (byte)/12 sec (word). AUTOMATIC PROGRAMMING ALGORITHM MXIC's Automatic Programming algorithm requires the user to only write program set-up commands (including 2 unlock write cycle and A0H) and a program command (program data and address). The device automatically times the programming pulse width, provides the pro-gram verification, and counts the number of sequences.A status bit similar to DA TA polling and a status bit tog-gling between consecutive read cycles, provide feed-back to the user as to the status of the programming operation. Refer to write operation status, table 7, for more information on these status bits. AUTOMATIC CHIP ERASEThe entire chip is bulk erased using 10 ms erase pulses according to MXIC's Automatic Chip Erase algorithm. T ypical erasure at room temperature is accomplished in less than 25 second. The Automatic Erase algorithm automatically programs the entire array prior to electri-cal erase. The timing and verification of electrical erase are controlled internally within the device. AUTOMATIC SECTOR ERASEThe MX29LV160BT/BB is sector(s) erasable using MXIC's Auto Sector Erase algorithm. The Automatic Sector Erase algorithm automatically programs the specified sector(s) prior to electrical erase. The timing and verification of electrical erase are controlled inter-nally within the device. An erase operation can erase one sector, multiple sectors, or the entire device. AUTOMATIC ERASE ALGORITHMMXIC's Automatic Erase algorithm requires the user to write commands to the command register using stan-dard microprocessor write timings. The device will auto-matically pre-program and verify the entire array. Then the device automatically times the erase pulse width, provides the erase verification, and counts the number of sequences. A status bit toggling between consecu-tive read cycles provides feedback to the user as to the status of the erasing operation.Register contents serve as inputs to an internal state-machine which controls the erase and programming cir-cuitry. During write cycles, the command register inter-nally latches address and data needed for the program-ming and erase operations. During a system write cycle, addresses are latched on the falling edge, and data are latched on the rising edge of WE or CE, whichever hap-pens first.MXIC's Flash technology combines years of EPROM experience to produce the highest levels of quality, reli-ability, and cost effectiveness. The MX29LV160BT/BB electrically erases all bits simultaneously using Fowler-Nordheim tunneling. The bytes are programmed by us-ing the EPROM programming mechanism of hot elec-tron injection.During a program cycle, the state-machine will control the program sequences and command register will not respond to any command set. During a Sector Erase cycle, the command register will only respond to Erase Suspend command. After Erase Suspend is completed, the device stays in read mode. After the state machine has completed its task, it will allow the command regis-ter to respond to its full command set. AUTOMATIC SELECTThe automatic select mode provides manufacturer and device identification, and sector protection verification, through identifier codes output on Q7~Q0. This mode is mainly adapted for programming equipment on the de-vice to be programmed with its programming algorithm. When programming by high voltage method, automatic select mode requires VID (11.5V to 12.5V) on address pin A9. Other address pin A6, A1 and A0 as referring to T able 3. In addition, to access the automatic select codes in-system, the host can issue the automatic select com-mand through the command register without requiring VID, as shown in table 5.To verify whether or not sector being protected, the sec-tor address must appear on the appropriate highest or-der address bit (see Table 1 and Table 2). The rest ofaddress bits, as shown in T able 3, are don't care. Onceall necessary bits have been set as required, the pro-gramming equipment may read the corresponding iden-tifier code on Q7~Q0.TABLE 3. MX29LV160BT/BB AUTO SELECT MODE BUS OPERATION (A9=VID)A19A11A9A8A6A5A1A0Description Mode CE OE WE RESET | | | |Q15~Q0A12A10A7A2Read Silicon ID L L H H X X VID X L X L L C2H Manufacture CodeDevice ID Word L L H H X X VID X L X L H22C4H (Top Boot Block)Byte L L H H X X VID X L X L H XXC4H Device ID Word L L H H X X VID X L X L H2249H (Bottom Boot Block)Byte L L H H X X VID X L X L H XX49HXX01HSector Protection L L H H SA X VID X L X H L(protected) Verification XX00H(unprotected) NOTE: SA=Sector Address, X=Don't Care, L=Logic Low, H=Logic HighQUERY COMMAND AND COMMON FLASH INTERFACE (CFI) MODEMX29LV160BT/BB is capable of operating in the CFI mode. This mode all the host system to determine the manufacturer of the device such as operating param-eters and configuration. Two commands are required in CFI mode. Query command of CFI mode is placed first, then the Reset command exits CFI mode. These are described in T able 4.The single cycle Query command is valid only when the device is in the Read mode, including Erase Suspend, Standby mode, and Automatic Select mode; however, it is ignored otherwise.The Reset command exits from the CFI mode to the Read mode, or Erase Suspend mode, or Automatic Se-lect mode. The command is valid only when the device is in the CFI mode.Table 4-1. CFI mode: Identification Data Values(All values in these tables are in hexadecimal)Description Address Address Data(Byte Mode)(Word Mode) Query-unique ASCII string "QRY"201000512211005224120059 Primary vendor command set and control interface ID code2613000228140000 Address for primary algorithm extended query table2A1500402C160000 Alternate vendor command set and control interface ID code (none)2E17000030180000 Address for secondary algorithm extended query table (none)32190000341A0000 Table 4-2. CFI Mode: System Interface Data Values(All values in these tables are in hexadecimal)Description Address Address Data(Byte Mode)(Word Mode) VCC supply, minimum (2.7V)361B0027 VCC supply, maximum (3.6V)381C0036 VPP supply, minimum (none)3A1D0000 VPP supply, maximum (none)3C1E0000 Typical timeout for single word/byte write (2N us)3E1F0004 Typical timeout for Minimum size buffer write (2N us) (not supported)40200000 Typical timeout for individual sector erase (2N ms)4221000A Typical timeout for full chip erase (2N ms)44220000 Maximum timeout for single word/byte write times (2N X Typ)46230005 Maximum timeout for buffer write times (2N X Typ)48240000 Maximum timeout for individual sector erase times (2N X Typ)4A250004 Maximum timeout for full chip erase times (not supported)4C260000Table 4-3. CFI Mode: Device Geometry Data Values(All values in these tables are in hexadecimal)Description Address Address Data(Byte Mode)(Word Mode) Device size (2N bytes)4E270015 Flash device interface code (x8/x16 async.)5028000252290000 Maximum number of bytes in multi-byte write (not supported)542A0000562B0000 Number of erase sector regions582C0004 Erase sector region 1 information (refer to the CFI publication 100)5A2D00005C2E00005E2F004060300000 Erase sector region 2 information62310001643200006633002068340000 Erase sector region 3 information6A3500006C3600006E37008070380000 Erase sector region 4 information7239001E743A0000763B0000783C0001 Table 4-4. CFI Mode: Primary Vendor-Specific Extended Query Data Values(All values in these tables are in hexadecimal)Description Address Address Data(Byte Mode)(Word Mode) Query-unique ASCII string "PRI"804000508241005284420049 Major version number, ASCII86430031 Minor version number, ASCII88440030 Address sensitive unlock (0=required, 1= not required)8A450000 Erase suspend (2= to read and write)8C460002 Sector protect (N= # of sectors/group)8E470001 Temporary sector unprotect (1=supported)90480001 Sector protect/chip unprotect scheme92490004 Simultaneous R/W operation (0=not supported)944A0000 Burst mode type (0=not supported)964B0000 Page mode type (0=not supported)984C0000in the improper sequence will reset the device to the read mode. Table 5 defines the valid register command sequences. Note that the Erase Suspend (B0H) and Erase Resume (30H) commands are valid only while the Sector Erase operation is in progress.COMMAND DEFINITIONSDevice operations are selected by writing specific ad-dress and data sequences into the command register.Writing incorrect address and data values or writing themFirst Bus Second Bus Third Bus Fourth Bus Fifth Bus Sixth Bus CommandBusCycleCycleCycleCycleCycle CycleCycle AddrData Addr Data Addr Data Addr DataAddrData Addr DataReset 1XXXH F0H Read1RARDRead Silicon IDWord 4555H AAH 2AAH 55H 555H 90H ADI DDI Byte4AAAH AAH 555H 55H AAAH 90H ADI DDI Sector Protect Word4555H AAH 2AAH55H555H90H (SA)XX00H Verifyx02HXX01H Byte4AAAH AAH 555H55HAAAH90H (SA)00H x04H01H Program Word 4555H AAH 2AAH 55H 555H A0H PA PD Byte4AAAH AAH 555H 55H AAAH A0H PAPDChip Erase Word 6555H AAH 2AAH 55H 555H 80H 555H AAH 2AAH 55H 555H 10H Byte6AAAH AAH 555H 55H AAAH 80H AAAH AAH 555H 55H AAAH 10H Sector Erase Word 6555H AAH 2AAH 55H 555H 80H 555H AAH 2AAH 55H SA 30H Byte6AAAH AAH 555H 55HAAAH80H AAAH AAH555H 55HSA30HSector Erase Suspend 1XXXH B0H Sector Erase Resume 1XXXH 30H CFI QueryWord 155H 98ByteAAHTABLE 5. MX29LV160BT/BB COMMAND DEFINITIONSNote:1. ADI = Address of Device identifier; A1=0, A0 = 0 for manufacturer code,A1=0, A0 = 1 for device code. A2-A19=do not care. (Refer to table 3)DDI = Data of Device identifier : C2H for manufacture code, C4H/49H (x8) and 22C4H/2249H (x16) for device code. X = X can be VIL or VIHRA=Address of memory location to be read. RD=Data to be read at location RA.2.PA = Address of memory location to be programmed. PD = Data to be programmed at location PA. SA = Address of the sector to be erased.3.The system should generate the following address patterns: 555H or 2AAH to Address A10~A0 in word mode/AAAH or 555H to Address A10~A-1 in byte mode.Address bit A11~A19=X=Don't care for all address commands except for Program Address (P A) and Sector Address (SA). Write Sequence may be initiated with A11~A19 in either state.4. For Sector Protect Verify operation: If read out data is 01H, it means the sector has been protected. If read out data is 00H,it means the sector is still not being protected.5. Any number of CFI data read cycles are permitted.TABLE 6. MX29LV160BT/BB BUS OPERATIONADDRESS Q8~Q15 DESCRIPTION CE OE WE RESET A19A11A9A8A6A5A1A0Q0~Q7BYTE BYTEA12A10A7A2=VIH=VIL Read L L H H AIN Dout Dout Q8~Q14=High ZQ15=A-1 Write L H L H AIN DIN(3)DINReset X X X L X High Z High Z High Z Temporary sector unlock X X X VID AIN DIN DIN High Z Output Disable L H H H X High Z High Z High Z Standby Vcc±X X Vcc±X High Z High Z High Z0.3V0.3VSector Protect L H L VID SA X X X L X H L DIN X X Chip Unprotect L H L VID X X X X H X H L DIN X X Sector Protection Verify L L H H SA X VID X L X H L CODE(5)X XNOTES:1.Manufacturer and device codes may also be accessed via a command register write sequence. Refer to T able 4.2. VID is the high voltage, 11.5V to 12.5V.3.Refer to T able 5 for valid Data-In during a write operation.4.X can be VIL or VIH.5.Code=00H/XX00H means unprotected.Code=01H/XX01H means protected.6.A19~A12=Sector address for sector protect.7.The sector protect and chip unprotect functions may also be implemented via programming equipment.REQUIREMENTS FOR READING ARRAY DATAT o read array data from the outputs, the system must drive the CE and OE pins to VIL. CE is the power control and selects the device. OE is the output control and gates array data to the output pins. WE should remain at VIH.The internal state machine is set for reading array data upon device power-up, or after a hardware reset. This ensures that no spurious alteration of the memory con-tent occurs during the power transition. No command is necessary in this mode to obtain array data. Standard microprocessor read cycles that assert valid address on the device address inputs produce valid data on the device data outputs. The device remains enabled for read access until the command register contents are altered. WRITE COMMANDS/COMMAND SEQUENCESTo program data to the device or erase sectors of memory, the system must drive WE and CE to VIL, and OE to VIH.An erase operation can erase one sector, multiple sec-tors, or the entire device. T able 1 and T able 2 indicate the address space that each sector occupies. A "sector ad-dress" consists of the address bits required to uniquely select a sector. The Writing specific address and data commands or sequences into the command register ini-tiates device operations. Table 5 defines the valid regis-ter command sequences. Writing incorrect address and data values or writing them in the improper sequence resets the device to reading array data. Section has de-tails on erasing a sector or the entire chip, or suspend-ing/resuming the erase operation.After the system writes the "read silicon-ID" and "sector protect verify" command sequence, the device enters the "read silicon-ID" and "sector protect verify" mode. The system can then read "read silicon-ID" and "sector protect verify" codes from the internal register (which is separate from the memory array) on Q7-Q0. Standard read cycle timings apply in this mode. Refer to the "read silicon-ID" and "sector protect verify" Mode and "read silicon-ID" and "sector protect verify" Command Se-quence section for more information.ICC2 in the DC Characteristics table represents the ac-tive current specification for the write mode. The "AC Characteristics" section contains timing specification table and timing diagrams for write operations. STANDBY MODEWhen using both pins of CE and RESET, the device enter CMOS Standby with both pins held at Vcc ± 0.3V. If CE and RESET are held at VIH, but not within the range of VCC ± 0.3V, the device will still be in the standby mode, but the standby current will be larger. During Auto Algorithm operation, Vcc active current (ICC2) is required even CE = "H" until the operation is completed. The de-vice can be read with standard access time (tCE) from either of these standby modes, before it is ready to read data.OUTPUT DISABLEWith the OE input at a logic high level (VIH), output from the devices are disabled. This will cause the output pins to be in a high impedance state.RESET OPERATIONThe RESET pin provides a hardware method of reset-ting the device to reading array data. When the RESET pin is driven low for at least a period of tRP, the device immediately terminates any operation in progress, tristates all output pins, and ignores all read/write com-mands for the duration of the RESET pulse. The device also resets the internal state machine to reading array data. The operation that was interrupted should be re-initiated once the device is ready to accept another com-mand sequence, to ensure data integrity.Current is reduced for the duration of the RESET pulse. When RESET is held at VSS±0.3V, the device draws CMOS standby current (ICC4). If RESET is held at VIL but not within VSS±0.3V, the standby current will be greater.The RESET pin may be tied to system reset circuitry. A system reset would that also reset the Flash memory, enabling the system to read the boot-up firmware from the Flash memory.If RESET is asserted during a program or erase opera-READ/RESET COMMANDThe read or reset operation is initiated by writing the read/reset command sequence into the command reg-ister. Microprocessor read cycles retrieve array data. The device remains enabled for reads until the command register contents are altered.If program-fail or erase-fail happen, the write of F0H will reset the device to abort the operation. A valid com-mand must then be written to place the device in the desired state.SILICON-ID READ COMMANDFlash memories are intended for use in applications where the local CPU alters memory contents. As such, manu-facturer and device codes must be accessible while the device resides in the target system. PROM program-mers typically access signature codes by raising A9 to a high voltage (VID). However, multiplexing high volt-age onto address lines is not generally desired system design practice.The MX29LV160BT/BB contains a Silicon-ID-Read op-eration to supple traditional PROM programming meth-odology. The operation is initiated by writing the read silicon ID command sequence into the command regis-ter. Following the command write, a read cycle with A1=VIL, A0=VIL retrieves the manufacturer code of C2H/ 00C2H. A read cycle with A1=VIL, A0=VIH returns the device code of C4H/22C4H for MX29LV160BT, 49H/ 2249H for MX29LV160BB.The system must write the reset command to exit the "Silicon-ID Read Command" code.AUTOMATIC CHIP ERASE COMMANDSChip erase is a six-bus cycle operation. There are two "unlock" write cycles. These are followed by writing the "set-up" command 80H. Two more "unlock" write cy-cles are then followed by the chip erase command 10H. The device does not require the system to entirely pre-program prior to executing the Automatic Chip Erase. Upon executing the Automatic Chip Erase, the device will automatically program and verify the entire memory for an all-zero data pattern. When the device is auto-matically verified to contain an all-zero pattern, a self-timed chip erase and verify begin. The erase and verify operations are completed when the data on Q7 is "1" at which time the device returns to the Read mode. The system is not required to provide any control or timing during these operations.When using the Automatic Chip Erase algorithm, note that the erase automatically terminates when adequate erase margin has been achieved for the memory array (no erase verification command is required).If the Erase operation was unsuccessful, the data on Q5 is "1" (see Table 8), indicating the erase operation exceed internal timing limit.The automatic erase begins on the rising edge of the last WE or CE pulse, whichever happens first in the command sequence and terminates when either the data on Q7 is "1" at which time the device returns to the Read mode or the data on Q6 stops toggling for two consecutive read cycles at which time the device re-turns to the Read mode.tion, the RY/BY pin remains a "0" (busy) until the inter-nal reset operation is complete, which requires a time of tREADY (during Embedded Algorithms). The system can thus monitor RY/BY to determine whether the reset op-eration is complete. If RESET is asserted when a pro-gram or erase operation is completed within a time of tREADY (not during Embedded Algorithms). The sys-tem can read data tRH after the RESET pin returns to VIH.Refer to the AC Characteristics tables for RESET parameters and to Figure 22 for the timing diagram.。

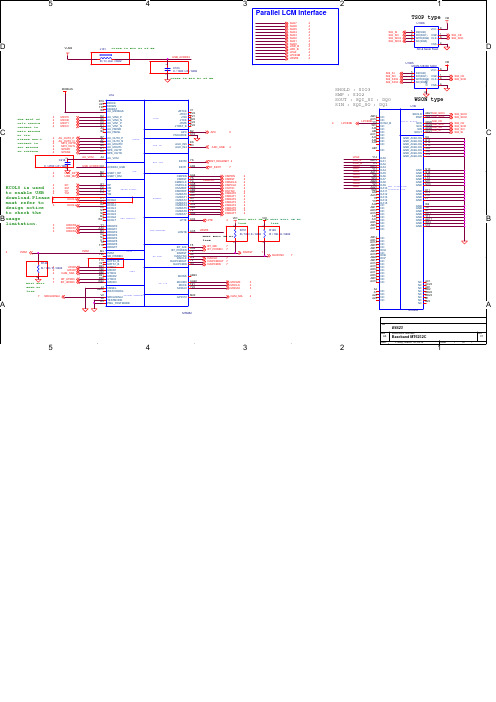

MT6252原理图资料

1

TSOP type

8 1 6 4 SQI_CE SQI_SCK VM

D

VUSB

L101

Close to pin K3 of BB

USB_AVDD33

NC & Serial Flash

D

VM

R / 0 / ohm / 0402 1 C103 C / 1000 / nF / 0402 2

U1005 MX25L12833E MXIC SQI_SI SQI_SO SQI_SIO2 SQI_SIO3 5 2 3 7 VCC DI(DQ0) DO(DQ1) CS# WP#(DQ2) CLK NC(DQ3) VSS GND 9 8 1 6 4

C

The pin1 of C218 should connect to main ground by via. Please don't connect to any ground on surface.

4 4 4 4

MICP0 MICN0 MICP1 MICN1

D2 E2 C2 C1 A3 B3 B7 A7 A6 B5 H1 H2 AU_VCM A4

Baseband MT6252C

Friday, March 16, 2012 Sheet 1 of 7

Rev V1

5

4

3

1

5

4

3

2

1

D

VBAT

TP6

TP7

TP9

TP10

D

If bead is necessary, DCR must be small

R1645 1 1 C203 C / 4700 / nF / 0603 2 1 R1646 R / 0 / ohm / 0402 2 2 R / 0 / ohm / 0402 1 VBAT_RF VBAT_DIGITAL VBAT_ANALOG VBAT_AMP B15 A13 A15 J1 J2 VBAT_RF VBAT_DIGITAL VBAT_ANALOG VBAT_SPK VBAT_SPK VBAT IN

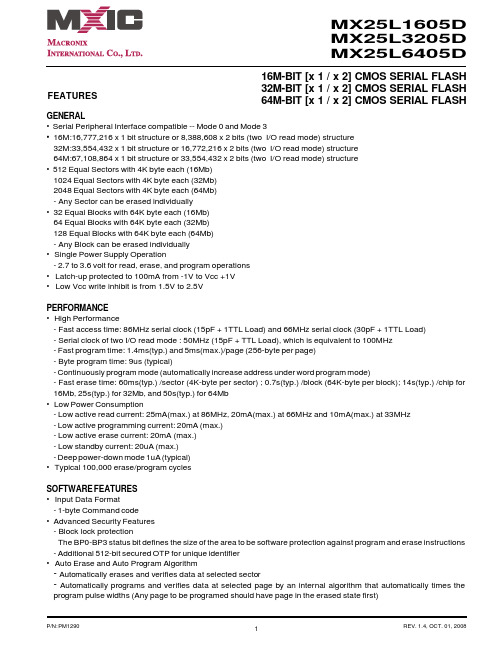

MX25L3205D中文资料

16M-BIT [x 1 / x 2] CMOS SERIAL FLASH 32M-BIT [x 1 / x 2] CMOS SERIAL FLASH 64M-BIT [x 1 / x 2] CMOS SERIAL FLASHFEATURESGENERAL• Serial Peripheral Interface compatible -- Mode 0 and Mode 3• 16M:16,777,216 x 1 bit structure or 8,388,608 x 2 bits (two I/O read mode) structure 32M:33,554,432 x 1 bit structure or 16,772,216 x 2 bits (two I/O read mode) structure 64M:67,108,864 x 1 bit structure or 33,554,432 x 2 bits (two I/O read mode) structure • 512 Equal Sectors with 4K byte each (16Mb)1024 Equal Sectors with 4K byte each (32Mb)2048 Equal Sectors with 4K byte each (64Mb)- Any Sector can be erased individually•32 Equal Blocks with 64K byte each (16Mb)64 Equal Blocks with 64K byte each (32Mb)128 Equal Blocks with 64K byte each (64Mb)- Any Block can be erased individually • Single Power Supply Operation- 2.7 to 3.6 volt for read, erase, and program operations • Latch-up protected to 100mA from -1V to Vcc +1V • Low Vcc write inhibit is from 1.5V to 2.5VPERFORMANCE • High Performance- Fast access time: 86MHz serial clock (15pF + 1TTL Load) and 66MHz serial clock (30pF + 1TTL Load)- Serial clock of two I/O read mode : 50MHz (15pF + TTL Load), which is equivalent to 100MHz - Fast program time: 1.4ms(typ.) and 5ms(max.)/page (256-byte per page)- Byte program time: 9us (typical)- Continuously program mode (automatically increase address under word program mode)- Fast erase time: 60ms(typ.) /sector (4K-byte per sector) ; 0.7s(typ.) /block (64K-byte per block); 14s(typ.) /chip for 16Mb, 25s(typ.) for 32Mb, and 50s(typ.) for 64Mb • Low Power Consumption- Low active read current: 25mA(max.) at 86MHz, 20mA(max.) at 66MHz and 10mA(max.) at 33MHz - Low active programming current: 20mA (max.)- Low active erase current: 20mA (max.)- Low standby current: 20uA (max.)- Deep power-down mode 1uA (typical)• Typical 100,000 erase/program cyclesSOFTWARE FEATURES • Input Data Format- 1-byte Command code •Advanced Security Features - Block lock protectionThe BP0-BP3 status bit defines the size of the area to be software protection against program and erase instructions - Additional 512-bit secured OTP for unique identifier • Auto Erase and Auto Program Algorithm- Automatically erases and verifies data at selected sector- Automatically programs and verifies data at selected page by an internal algorithm that automatically times the program pulse widths (Any page to be programed should have page in the erased state first)MX25L1605D MX25L3205D MX25L6405D元器件交易网•Status Register Feature•Electronic Identification- JEDEC 1-byte manufacturer ID and 2-byte device ID- RES command for 1-byte Device ID- Both REMS and REMS2 commands for 1-byte manufacturer ID and 1-byte device IDHARDWARE FEATURES• SCLK Input- Serial clock input• SI Input- Serial Data Input• SO Output- Serial Data Output• WP#/ACC pin- Hardware write protection and program/erase acceleration• HOLD# pin- pause the chip without diselecting the chip• PACKAGE- 16-pin SOP (300mil)- 8-land WSON (8x6mm or 6x5mm)- 8-pin SOP (200mil, 150mil)- 8-pin PDIP (300mil)- 8-land USON (4x4mm)- All Pb-free devices are RoHS CompliantALTERNATIVE• Security Serial Flash (MX25L1615D/MX25L3215D/MX25L6415D) may provides additional protection features for op-tion. The datasheet is provided under NDA.GENERAL DESCRIPTIONThe MX25L1605D are 16,777,216 bit serial Flash memory, which is configured as 2,097,152 x 8 internally. When it is in two I/O read mode, the structure becomes 8,388,608 bits x 2. The MX25L3205D are 33,554,432 bit serial Flash memory, which is configured as 4,194,304 x 8 internally. When it is in two I/O read mode, the structure becomes 16,772,216 bits x 2. The MX25L6405D are 67,108,864 bit serial Flash memory, which is configured as 8,388,608 x 8 internally. When it is in two I/O read mode, the structure becomes 33,554,432 bits x 2. (please refer to the "Two I/O Read mode" section). The MX25L1605D/3205D/6405D feature a serial peripheral interface and software protocol allowing operation on a simple 3-wire bus. The three bus signals are a clock input (SCLK), a serial data input (SI), and a serial data output (SO). Serial access to the device is enabled by CS# input.When it is in two I/O read mode, the SI pin and SO pin become SIO0 pin and SIO1 pin for address/dummy bits input and data output.The MX25L1605D/3205D/6405D provides sequential read operation on whole chip.After program/erase command is issued, auto program/ erase algorithms which program/ erase and verify the specified page or sector/block locations will be executed. Program command is executed on byte basis, or page (256 bytes) basis, or word basis for Continuously program mode, and erase command is executes on sector (4K-byte), or block (64K-byte), or whole chip basis.To provide user with ease of interface, a status register is included to indicate the status of the chip. The status read command can be issued to detect completion status of a program or erase operation via WIP bit.Advanced security features enhance the protection and security functions, please see security features section for more details.When the device is not in operation and CS# is high, it is put in standby mode and draws less than 20uA DC current. The MX25L1605D/3205D/6405D utilizes MXIC's proprietary memory cell, which reliably stores memory contents even after typical 100,000 program and erase cycles.Table 1. Additional Feature ComparisonPIN CONFIGURATIONSSYMBOL DESCRIPTION CS#Chip SelectSI/SIO0Serial Data Input (for 1 x I/O)/ Serial Data Input & Output (for 2xI/O read mode)SO/SIO1Serial Data Output (for 1 x I/O)/ Serial Data Input & Output (for 2xI/O read mode)SCLK Clock InputWP#/ACCWrite protection: connect to GND ;9.5~10.5V for program/eraseacceleration: connect to 9.5~10.5V HOLD#Hold, to pause the device without deselecting the device VCC + 3.3V Power Supply GNDGroundPIN DESCRIPTION16-PIN SOP (300mil)8-LAND WSON (8x6mm, 6x5mm), USON (4x4mm)8-PIN SOP (200mil, 150mil)PACKAGE OPTIONS16M 32M 64M150mil 8-SOP V 200mil 8-SOP V V 300mil 16-SOP V V V300mil 8-PDIP V V 6x5mm WSON V V 8x6mm WSON V4x4mm USONVV12345678HOLD#VCC NC NC NC NC CS#SO/SIO1161514131211109SCLK SI/SIO0NC NC NC NC GND WP#/ACCCS#SO/SIO1WP#/ACCGND VCC HOLD#SCLK SI/SIO0CS#SO/SIO1WP#/ACC GND VCC HOLD#SCLK SI/SIO01234CS#SO/SIO1WP#/ACC GND 8765VCC HOLD#SCLK SI/SIO08-PIN PDIP (300mil)BLOCK DIAGRAMDATA PROTECTIONThe MX25L1605D/3205D/6405D is designed to offer protection against accidental erasure or programming caused by spurious system level signals that may exist during power transition. During power up the device automatically resets the state machine in the Read mode. In addition, with its control register architecture, alteration of the memory contents only occurs after successful completion of specific command sequences. The device also incorporates several features to prevent inadvertent write cycles resulting from VCC power-up and power-down transition or system noise.•Power-on reset and tPUW: to avoid sudden power switch by system power supply transition, the power-on reset and tPUW (internal timer) may protect the Flash.• Valid command length checking: The command length will be checked whether it is at byte base and completed on byte boundary.• Write Enable (WREN) command: WREN command is required to set the Write Enable Latch bit (WEL) before other command to change data. The WEL bit will return to reset stage under following situation:- Power-up- Write Disable (WRDI) command completion- Write Status Register (WRSR) command completion- Page Program (PP) command completion- Continuously Program mode (CP) instruction completion- Sector Erase (SE) command completion- Block Erase (BE) command completion- Chip Erase (CE) command completion- Write Read-lock Bit (WRLB) instruction completion•Deep Power Down Mode: By entering deep power down mode, the flash device also is under protected from writing all commands except Release from deep power down mode command (RDP) and Read Electronic Signature command (RES).•Advanced Security Features: there are some protection and securuity features which protect content from inadvertent write and hostile access.I. Block lock protection- The Software Protected Mode (SPM) use (BP3, BP2, BP1, BP0) bits to allow part of memory to be protected as read only. The proected area definition is shown as table of "Protected Area Sizes", the protected areas are more flexible which may protect various area by setting value of BP0-BP3 bits.Please refer to table of "protected area sizes".- The Hardware Proteced Mode (HPM) use WP#/ACC to protect the (BP3, BP2, BP1, BP0) bits and SRWD bit.Table 2. Protected Area SizesII. Additional 512-bit secured OTP for unique identifier: to provide 512-bit one-time program area for setting device unique serial number - Which may be set by factory or system customer. Please refer to table 3. 512-bit secured OTP definition.- Security register bit 0 indicates whether the chip is locked by factory or not.- To program the 512-bit secured OTP by entering 512-bit secured OTP mode (with ENSO command), and going through normal program procedure, and then exiting 512-bit secured OTP mode by writing EXSO command.- Customer may lock-down the customer lockable secured OTP by writing WRSCUR(write security register) command to set customer lock-down bit1 as "1". Please refer to table of "security register definition" for security register bit definition and table of "512-bit secured OTP definition" for address range definition.- Note: Once lock-down whatever by factory or customer, it cannot be changed any more. While in 512-bit secured OTP mode, array access is not allowed.Table 3. 512-bit Secured OTP DefinitionAddress range Size Standard Customer LockFactory Lockxxxx00~xxxx0F128-bit ESN (electrical serial number)Determined by customer xxxx10~xxxx3F384-bit N/AHOLD FEATURESHOLD# pin signal goes low to hold any serial communications with the device. The HOLD feature will not stop the operation of write status register, programming, or erasing in progress.The operation of HOLD requires Chip Select(CS#) keeping low and starts on falling edge of HOLD# pin signal while Serial Clock (SCLK) signal is being low (if Serial Clock signal is not being low, HOLD operation will not start until Serial Clock signal being low). The HOLD condition ends on the rising edge of HOLD# pin signal while Serial Clock(SCLK) signal is being low( if Serial Clock signal is not being low, HOLD operation will not end until Serial Clock being low), see Figure 1. Figure 1. Hold Condition OperationThe Serial Data Output (SO) is high impedance, both Serial Data Input (SI) and Serial Clock (SCLK) are don't care during the HOLD operation. If Chip Select (CS#) drives high during HOLD operation, it will reset the internal logic of the device. To re-start communication with chip, the HOLD# must be at high and CS# must be at low.PROGRAM/ERASE ACCELERATIONTo activate the program/erase acceleration function requires ACC pin connecting to 9.5~10.5V voltage (see Figure 2), and then to be followed by the normal program/erase process. By utilizing the program/erase acceleration operation, the performances are improved as shown on table of "ERASE AND PROGRAM PERFORMACE".After power-up ready, it should wait 10ms at least to apply VHH(9.5~10.5V) on the WP#/ACC pin.Figure 2. ACCELERATED PROGRAM TIMING DIAGRAMNote: tVHH (VHH Rise and Fall Time) min. 250nsTable 4. COMMAND DEFINITIONCOMMAND (byte)WREN (writeenable)WRDI (write disable)RDID (read identification )RDSR (read statusregister)WRSR(write status register)READ (read data)FAST READ(fast read data)2READ (2x I/O read command)note1SE (sector erase)1st byte 06 (hex)04 (hex)9F (hex)05 (hex)01 (hex)03 (hex)0B (hex)BB (hex)20 (hex)2nd byte AD1AD1ADD(2)AD13rd byte AD2AD2ADD(2) &Dummy(2)AD24th byte AD3AD3AD35th byte Actionsets the (WEL)write enable latch bit resets the (WEL)write enable latch bitoutputs JEDEC ID:1-byte manufactur er ID & 2-byte device IDto read out the values of the status register to writenew values to the statusregister n bytes read out until CS#goes high n bytes read out until CS#goes high n bytes read out by 2 x I/O until CS#goes high to erase the selectedsector Note 1: The count base is 4-bit for ADD(2) and Dummy(2) because of 2 x I/O. And the MSB is on SI/SIO0 which is different from 1 x I/O conditionCOMMAND (byte)BE (block erase)CE (chip erase)PP (Page program)CP (Continuo-usly program mode)DP (Deep powerdown)RDP (Release from deep power down)RES (read electronic ID)REMS(read electronic manufactu-rer &device ID)REMS2(read ID for 2x I/O mode)1st byte D8 (hex)60 or C7(hex)02 (hex)AD (hex)B9 (hex)AB (hex)AB (hex)90 (hex)EF (hex)2nd byte AD1AD1AD1x x x 3rd byte AD2AD2AD2x x x 4th byte AD3AD3AD3x ADD(note 2)ADD(note2)5th byteAction to erase theselected block to erase whole chip to program the selected page continously program wholechip, theaddress is automatica lly increaseentersdeep power down moderelease from deep power down mode to read out 1-byte device ID outout the manufactu-rer ID &device ID output the manufactu-rer ID &device ID Note 2: ADD=00H will output the manufacturer ID first and ADD=01H will output device ID first Note 3: It is not recommoded to adopt any other code not in the command definition table, which will potentially enter the hidden mode.COMMAND (byte)ENSO (enter secured OTP)EXSO (exit secured OTP)RDSCUR (read security register)WRSCUR (write security register)ESRY (enable SO to output RY/BY#)DSRY (disable SO to output RY/BY#)1st byte B1 (hex)C1 (hex)2B (hex)2F (hex)70 (hex)80 (hex)2nd byte 3rd byte 4th byte 5th byte Actionto enter the 512-bit secured OTP mode to exit the 512-bit secured OTP mode to read value of security registerto set the lock-down bit as "1"(once lock-down,cannot be updated)to enable SO to output RY/BY#during CP mode to disable SO to output RY/BY#during CP modeDummyTable 5-1. Memory Organization (16Mb)Table 5-2. Memory Organization (32Mb)Table 5-3. Memory Organization (64Mb)DEVICE OPERATION1.Before a command is issued, status register should be checked to ensure device is ready for the intended operation.2.When incorrect command is inputted to this LSI, this LSI becomes standby mode and keeps the standby mode until next CS# falling edge. In standby mode, SO pin of this LSI should be High-Z.3.When correct command is inputted to this LSI, this LSI becomes active mode and keeps the active mode until next CS# rising edge.4.Input data is latched on the rising edge of Serial Clock(SCLK) and data shifts out on the falling edge of SCLK. The difference of Serial mode 0 and mode 3 is shown as Figure 3.Figure 3. Serial Modes Supported5.For the following instructions: RDID, RDSR, RDSCUR, READ, FAST_READ, 2READ, RES, REMS and REMS2 the shifted-in instruction sequence is followed by a data-out sequence. After any bit of data being shifted out, the CS# can be high. For the following instructions: WREN, WRDI, WRSR, SE, BE, CE, PP, CP, RDP, DP, ENSO, EXSO,and WRSCUR, the CS# must go high exactly at the byte boundary; otherwise, the instruction will be rejected and not executed.6.During the progress of Write Status Register, Program, Erase operation, to access the memory array is neglected and not affect the current operation of Write Status Register, Program, Erase.Note:CPOL indicates clock polarity of Serial master, CPOL=1 for SCLK high while idle, CPOL=0 for SCLK low while not transmitting. CPHA indicates clock phase. The combination of CPOL bit and CPHA bit decides which Serial mode is supported.SCLKMSBCPHASI 01CPOL 0(Serial mode 0)(Serial mode 3)1SO SCLKMSBCOMMAND DESCRIPTION(1) Write Enable (WREN)The Write Enable (WREN) instruction is for setting Write Enable Latch (WEL) bit. For those instructions like PP, CP, SE, BE, CE, and WRSR, which are intended to change the device content, should be set every time after the WREN instruction setting the WEL bit.The sequence of issuing WREN instruction is: CS# goes low-> sending WREN instruction code-> CS# goes high. (see Figure 12)(2) Write Disable (WRDI)The Write Disable (WRDI) instruction is for resetting Write Enable Latch (WEL) bit.The sequence of issuing WRDI instruction is: CS# goes low-> sending WRDI instruction code-> CS# goes high. (see Figure 13)The WEL bit is reset by following situations:- Power-up- Write Disable (WRDI) instruction completion- Write Status Register (WRSR) instruction completion- Page Program (PP) instruction completion- Sector Erase (SE) instruction completion- Block Erase (BE) instruction completion- Chip Erase (CE) instruction completion- Continuously program mode (CP) instruction completion(3) Read Identification (RDID)The RDID instruction is for reading the manufacturer ID of 1-byte and followed by Device ID of 2-byte. The MXIC Manufacturer ID is C2(hex), the memory type ID is 20(hex) as the first-byte device ID, and the individual device ID of second-byte ID are listed as table of "ID Definitions".The sequence of issuing RDID instruction is: CS# goes low-> sending RDID instruction code -> 24-bits ID data out on SO -> to end RDID operation can use CS# to high at any time during data out. (see Figure. 14)While Program/Erase operation is in progress, it will not decode the RDID instruction, so there's no effect on the cycle of program/erase operation which is currently in progress. When CS# goes high, the device is at standby stage.(4) Read Status Register (RDSR)The RDSR instruction is for reading Status Register Bits. The Read Status Register can be read at any time (even in program/erase/write status register condition) and continuously. It is recommended to check the Write in Progress (WIP) bit before sending a new instruction when a program, erase, or write status register operation is in progress.The sequence of issuing RDSR instruction is: CS# goes low-> sending RDSR instruction code-> Status Register data out on SO (see Figure. 15)The definition of the status register bits is as below:WIP bit. The Write in Progress (WIP) bit, a volatile bit, indicates whether the device is busy in program/erase/write status register progress. When WIP bit sets to 1, which means the device is busy in program/erase/write status register progress. When WIP bit sets to 0, which means the device is not in progress of program/erase/write status register cycle.WEL bit. The Write Enable Latch (WEL) bit, a volatile bit, indicates whether the device is set to internal write enable latch. When WEL bit sets to 1, which means the internal write enable latch is set, the device can accept program/erase/write status register instruction. When WEL bit sets to 0, which means no internal write enable latch; the device will not accept program/erase/write status register instruction. The program/erase command will be ignored and not affect value of WEL bit if it is applied to a protected memory area.BP3, BP2, BP1, BP0 bits. The Block Protect (BP3, BP2, BP1, BP0) bits, non-volatile bits, indicate the protected area(as defined in table 1) of the device to against the program/erase instruction without hardware protection mode being set. To write the Block Protect (BP3, BP2, BP1, BP0) bits requires the Write Status Register (WRSR) instruction to be executed. Those bits define the protected area of the memory to against Page Program (PP), Sector Erase (SE), Block Erase (BE) and Chip Erase(CE) instructions (only if all Block Protect bits set to 0, the CE instruction can be executed).Continuously Program Mode( CP mode) bit. The Continuously Program Mode bit indicates the status of CP mode, "0" indicates not in CP mode; "1" indicates in CP mode.SRWD bit. The Status Register Write Disable (SRWD) bit, non-volatile bit, is operated together with Write Protection (WP#/ ACC) pin for providing hardware protection mode. The hardware protection mode requires SRWD sets to 1 and WP#/ACC pin signal is low stage. In the hardware protection mode, the Write Status Register (WRSR) instruction is no longer accepted for execution and the SRWD bit and Block Protect bits (BP3, BP2, BP1, BP0) are read only.Status Registernote1: see the table "Protected Area Sizes"(5) Write Status Register (WRSR)The WRSR instruction is for changing the values of Status Register Bits. Before sending WRSR instruction, the Write Enable (WREN) instruction must be decoded and executed to set the Write Enable Latch (WEL) bit in advance. The WRSR instruction can change the value of Block Protect (BP3, BP2, BP1, BP0) bits to define the protected area of memory (as shown in table 1). The WRSR also can set or reset the Status Register Write Disable (SRWD) bit in accordance with Write Protection (WP#/ACC) pin signal. The WRSR instruction cannot be executed once the Hardware Protected Mode (HPM)is entered.The sequence of issuing WRSR instruction is: CS# goes low-> sending WRSR instruction code-> Status Register data on SI-> CS# goes high. (see Figure 16)The WRSR instruction has no effect on b6, b1, b0 of the status register.The CS# must go high exactly at the byte boundary; otherwise, the instruction will be rejected and not executed. The self-timed Write Status Register cycle time (tW) is initiated as soon as Chip Select (CS#) goes high. The Write in Progress (WIP) bit still can be check out during the Write Status Register cycle is in progress. The WIP sets 1 during the tW timing,and sets 0 when Write Status Register Cycle is completed, and the Write Enable Latch (WEL) bit is reset.Table 6. Protection ModesNote:1. As defined by the values in the Block Protect (BP3, BP2, BP1, BP0) bits of the Status Register, as shown in Table 1.As the above table showing, the summary of the Software Protected Mode (SPM) and Hardware Protected Mode (HPM).Software Protected Mode (SPM):-When SRWD bit=0, no matter WP#/ACC is low or high, the WREN instruction may set the WEL bit and can changethe values of SRWD, BP3, BP2, BP1, BP0. The protected area, which is defined by BP3, BP2, BP1, BP0, is at software protected mode (SPM).-When SRWD bit=1 and WP#/ACC is high, the WREN instruction may set the WEL bit can change the values of SRWD,BP3, BP2, BP1, BP0. The protected area, which is defined by BP3, BP2, BP1, BP0, is at software protected mode (SPM)ModeStatus register condition Software protection mode(SPM)Status register can be written in (WEL bit is set to "1") and the SRWD, BP0-BP3bits can be changedWP# and SRWD bit status MemoryWP#=1 and SRWD bit=0, or WP#=0 and SRWD bit=0, or WP#=1 and SRWD=1The protected area cannot be program or erase.The protected area cannot be program or erase.WP#=0, SRWD bit=1The SRWD, BP0-BP3 ofstatus register bits cannot be changedHardware protection mode (HPM)Note: If SRWD bit=1 but WP#/ACC is low, it is impossible to write the Status Register even if the WEL bit has previously been set. It is rejected to write the Status Register and not be executed.Hardware Protected Mode (HPM):-When SRWD bit=1, and then WP#/ACC is low (or WP#/ACC is low before SRWD bit=1), it enters the hardware protected mode (HPM). The data of the protected area is protected by software protected mode by BP3, BP2, BP1, BP0 and hardware protected mode by the WP#/ACC to against data modification.Note: to exit the hardware protected mode requires WP#/ACC driving high once the hardware protected mode is entered. If the WP#/ACC pin is permanently connected to high, the hardware protected mode can never be entered; only can use software protected mode via BP3, BP2, BP1, BP0.(6) Read Data Bytes (READ)The read instruction is for reading data out. The address is latched on rising edge of SCLK, and data shifts out on the falling edge of SCLK at a maximum frequency fR. The first address byte can be at any location. The address is automatically increased to the next higher address after each byte data is shifted out, so the whole memory can be read out at a single READ instruction. The address counter rolls over to 0 when the highest address has been reached.The sequence of issuing READ instruction is: CS# goes low-> sending READ instruction code-> 3-byte address on SI -> data out on SO-> to end READ operation can use CS# to high at any time during data out. (see Figure. 17)(7) Read Data Bytes at Higher Speed (FAST_READ)The FAST_READ instruction is for quickly reading data out. The address is latched on rising edge of SCLK, and data of each bit shifts out on the falling edge of SCLK at a maximum frequency fC. The first address byte can be at any location. The address is automatically increased to the next higher address after each byte data is shifted out, so the whole memory can be read out at a single FAST_READ instruction. The address counter rolls over to 0 when the highest address has been reached.The sequence of issuing FAST_READ instruction is: CS# goes low-> sending FAST_READ instruction code-> 3-byte address on SI-> 1-dummy byte address on SI->data out on SO-> to end FAST_READ operation can use CS# to high at any time during data out. (see Figure. 18)While Program/Erase/Write Status Register cycle is in progress, FAST_READ instruction is rejected without any impact on the Program/Erase/Write Status Register current cycle.(8) 2 x I/O Read Mode (2READ)The 2READ instruction enable double throughput of Serial Flash in read mode. The address is latched on rising edge of SCLK, and data of every two bits(interleave on 2 I/O pins) shift out on the falling edge of SCLK at a maximum frequency fT. The first address byte can be at any location. The address is automatically increased to the next higher address after each byte data is shifted out, so the whole memory can be read out at a single 2READ instruction. The address counter rolls over to 0 when the highest address has been reached. Once writing 2READ instruction, the following address/dummy/ data out will perform as 2-bit instead of previous 1-bit.The sequence of issuing 2READ instruction is: CS# goes low→ sending 2READ instruction→ 24-bit address interleave on SIO1 & SIO0→ 8-bit dummy interleave on SIO1 & SIO0→ data out interleave on SIO1 & SIO0→ to end 2READ operation can use CS# to high at any time during data out (see Figure of 2 x I/O Read Mode Timing Waveform)While Program/Erase/Write Status Register cycle is in progress, 2READ instruction is rejected without any impact on the Program/Erase/Write Status Register current cycle.The 2 I/O only perform read operation. Program/Erase /Read ID/Read status/Read ID....operation do not support 2 I/O throughputs.(9) Sector Erase (SE)The Sector Erase (SE) instruction is for erasing the data of the chosen sector to be "1". The instruction is used for any 4K-byte sector. A Write Enable (WREN) instruction must execute to set the Write Enable Latch (WEL) bit before sending the Sector Erase (SE). Any address of the sector (see table 3) is a valid address for Sector Erase (SE) instruction. The CS# must go high exactly at the byte boundary (the latest eighth of address byte been latched-in); otherwise, the instruction will be rejected and not executed.Address bits [Am-A12] (Am is the most significant address) select the sector address.The sequence of issuing SE instruction is: CS# goes low -> sending SE instruction code-> 3-byte address on SI -> CS# goes high. (see Figure 22)The self-timed Sector Erase Cycle time (tSE) is initiated as soon as Chip Select (CS#) goes high. The Write in Progress (WIP) bit still can be check out during the Sector Erase cycle is in progress. The WIP sets 1 during the tSE timing, and sets 0 when Sector Erase Cycle is completed, and the Write Enable Latch (WEL) bit is reset. If the page is protected by BP3, BP2, BP1, BP0 bits, the Sector Erase (SE) instruction will not be executed on the page.(10) Block Erase (BE)The Block Erase (BE) instruction is for erasing the data of the chosen block to be "1". The instruction is used for 64K-byte sector erase operation. A Write Enable (WREN) instruction must execute to set the Write Enable Latch (WEL) bit before sending the Block Erase (BE). Any address of the block (see table 3) is a valid address for Block Erase (BE) instruction. The CS# must go high exactly at the byte boundary (the latest eighth of address byte been latched-in); otherwise, the instruction will be rejected and not executed.The sequence of issuing BE instruction is: CS# goes low -> sending BE instruction code-> 3-byte address on SI -> CS# goes high. (see Figure 23)The self-timed Block Erase Cycle time (tBE) is initiated as soon as Chip Select (CS#) goes high. The Write in Progress (WIP) bit still can be check out during the Sector Erase cycle is in progress. The WIP sets 1 during the tBE timing, and sets 0 when Sector Erase Cycle is completed, and the Write Enable Latch (WEL) bit is reset. If the page is protected by BP3, BP2, BP1, BP0 bits, the Block Erase (BE) instruction will not be executed on the page.(11) Chip Erase (CE)The Chip Erase (CE) instruction is for erasing the data of the whole chip to be "1". A Write Enable (WREN) instruction must execute to set the Write Enable Latch (WEL) bit before sending the Chip Erase (CE). Any address of the sector (see table 3) is a valid address for Chip Erase (CE) instruction. The CS# must go high exactly at the byte boundary( the latest eighth of address byte been latched-in); otherwise, the instruction will be rejected and not executed.The sequence of issuing CE instruction is: CS# goes low-> sending CE instruction code-> CS# goes high. (see Figure 24)。

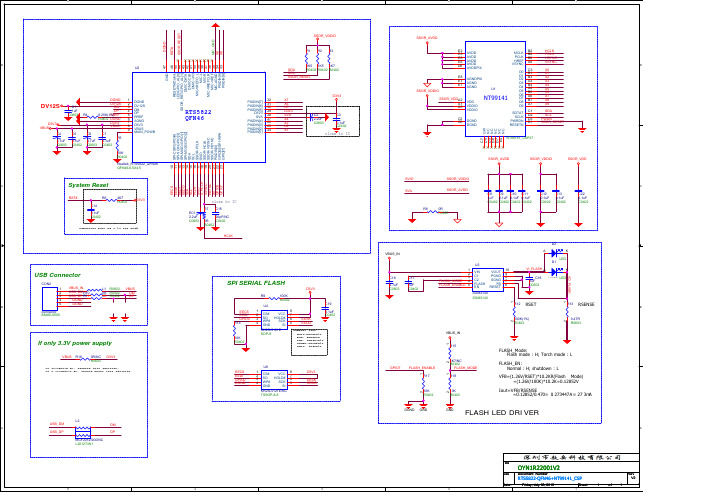

RTS5822_QFN+NT99141_CSP推荐线路

GND

1K5 1K5 4K7 R0402 R0402 R0402 SDA SCL SSOR_RESET

E2 E3 E5 E6 D8 E8 E1 E7 SSOR_VDDIO

AVDD AVDD AVDD AVDD AVDDPIX AGNDPIX AGND AGND

MCLK PCLK HREF VSYNC D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 SDTAT SCLK PWRDN RESETN GPI NC NC NC NC NC

Support List: MXIC,MX25L512 EON, EN25F05 PMC, PM25LV512 ATMEL,AT25F512 AMIC, A25L512

4.7uF C0603

1 2 3 FLASH_MODE 4 FLASH_ENABLE 5

VIN C1 C2 FLASH EN SGM3140 SGM3140

close to IC

R7 C15 EC1 2.2uF C0603

0.1uF C0402

Capacitor must be 0.1u for RST#

20pF/NC 0R C0402 R0402 HCLK D2 VBUS_IN U3 A D1 VOUT PGND SGND FB RESET 10 9 8 7 6 VI_FLASH A C18 1uF C0603 K

VO_FLASH

1

R12

RSET

1

R13

RSENSE

B

connector 88460-0500

100K(1%) R0402

0.47R R0603

2

KH25L5121E SOP-8

VBUS_IN 1

If only 3.3V power supply

MX29GL256EHT2I-90Q