第3章VHDL设计初步-2选1选择器设计

VHDL 设计初步-PPT精选文档

结束

4.1 多路选择器VHDL描述

设计: 2选1多路选择器

s y 0 a 1 b

y=as+bs

目录

结束

4.1 多路选择器VHDL描述

4.1.1

【例4-1】

2选1多路选择器的VHDL描述

ENTITY mux21a IS PORT( a, b : IN BIT ; s : IN BIT; y : OUT BIT ) ; END ENTITY mux21a ;

用其他的语句 形式来描述相 同的逻辑行为

【例4-3】 . . . ARCHITECTURE one OF mux21a IS BEGIN y <= (a AND (NOT s)) OR (b AND s) ; END ARCHITECTURE one;

目录 结束

4.1.1 2选1多路选择器的VHDL描述

VHDL 设计初步

唐英姿编制

教学内容

教学导入

设计举例: 2选1多路选择器

VHDL相关语法 课堂练习 小结

结束

现代电子设计新技术:EDA技术

EDA:电子设计自动化

Electronic Design Automation EDA技术就是: 依赖 功能强大的计算机在 EDA工具软 件 平台上,用 硬件描述语言(HDL)作 为系统逻辑描述手段来完成 电子线路设 计文件。 最终实现 ->特定电子线路的硬件(芯 片或者电路板)

电路的VHDL描述由两大部分组成:

以关键词ENTITY 引导,END ENTITY mux21a 结尾的语句部分,称为实体。 VHDL 的实体描述了电路器件的外部情况 及各信号端口的基本性质,如信号流动的 方向,流动在其上的信号结构方式和数据 类型等。 以关键词ARCHITECTURE 引导,END ARCHITECTURE one 结尾的语句部分, 称为结构体。结构体负责描述电路器件的 内部逻辑功能和电路结构。

第三章VHDL程序设计案例

第三章VHDL程序设计案例

37

带允许端的十二进制计数器

第三章VHDL程序设计案例

38

可逆计数器(加减计数器)

第三章VHDL程序设计案例

39

可逆计数器仿真结果:

第三章VHDL程序设计案例

40

例:六十进制(分、秒)计数器

第三章VHDL程序设计案例

end decoder;

architecture rtl of decoder is

begin

process(inp)

begin

outp<=(others=>’0’);

outp(conv_integer(inp))<=‘1’;

end process;

end rtl;

第三章VHDL程序设计案例

sel=000 sel =001 sel =010 sel =011 sel =100 sel =101 sel =110 sel =111

第三章VHDL程序设计案例

25

clock sig_in reset 同步复位 sig_out1 异步复位 sig_out2

第三章VHDL程序设计案例

26

二) 常用时序电路设计

1、触发器(Flip_Flop) 1)D触发器

第三章VHDL程序设计案例

27

异步置位/复位D触发器

第三章VHDL程序设计案例

1)“”序列发生器

第三章VHDL程序设计案例

49

第三章VHDL程序设计案例

50

第三章VHDL程序设计案例

51

仿真结果:

第三章VHDL程序设计案例

52

2)序列信号检测器的状态机设计与实现, 检测“”

3 VHDL基础1

在结构体中定义信号

y <= a WHEN s=‘0’ ELSE b;

结构体中的语句是并行语句。 无论有多少行语句,都是同时执行,与语句的先后顺序无关。

综合适配后,选择菜单 Tools->Netlist Viewers->RTL Viewer 可 观察所生成的电路示意图。

ARCHITECTURE one OF mux21a IS BEGIN y <= a WHEN s=‘0’ ELSE b; END ARCHITECTURE one ;

3.2 VHDL基本语法

CASE语句 一定要包含所有的选择情况; 小心WHEN OTHERS条件下的赋值;

3.2 VHDL基本语法

IF语句

ARCHITECTURE one OF ex38 IS BEGIN PROCESS(sel,a,b,c,d) BEGIN IF sel=“1110” THEN ELSIF sel=“1101” THEN …… ELSE y<='0'; END IF; END PROCESS; END ARCHITECTURE one;

: OUT STD_LOGIC );

3.2 VHDL基本语法

ARCHITECTURE one OF mux41a IS BEGIN PROCESS(sel,i0,i1,i2,i3) BEGIN CASE sel IS WHEN “00” WHEN “01” WHEN “10” WHEN “11” END CASE; END PROCESS; END ARCHITECTURE one;

例:教材P93,3-8。 Sel(3 DOWNTO 0) 1110 1101 1011 0111 Others 输出y a b c d 0

EDA技术与VHDL设计 第三章VHDL语言入门

L10 ARCHITECTURE construct OF mux21 IS

L13 BEGIN

4

L12 L14 L15 L16

SIGNAL d : STD_LOGIC; d<= a AND (NOT S); e<= b AND s; y<= d OR e;

L13 BEGIN

第3章 VHDL语言入门

L17 END ARCHITECTURE construct; L18 ------------------------------------------------------------------------------------------------------------------------L19 ARCHITECTURE behavior OF mux21 IS L20 BEGIN L21 L22 L23 L24 L25 L26 PROCESS(a, b, s) BEGIN IF s='0' THEN y <= a; ELAE y <= b; END IF; END PROCESS;

17

第3章 VHDL语言入门

图3-6 半加器真值表和逻辑表达式

18

第3章 VHDL语言入门

图3-7 半加器电路结构

19

第3章 VHDL语言入门

【例 3-2】

L1 L2 L3 L4 L5 L6 L7 L8 L9 L10 L11 L12 L13 L14 -----------------------------------------------------库和程序包----------------------------------------------------LIBRARY ieee ; USE ieee.std_logic_1164.all; ---------------------------------------------------------实体---------------------------------------------------------ENTITY halfadd IS PORT ( a, b co, so : IN STD_LOGIC; : OUT STD_LOGIC );

第3章_VHDL设计初步_习题

END COMPONENT; BEGIN u1:mux21a PORT MAP (a2,a3,s0,tmp); u2:mux21a PORT MAP (a1,tmp,s1,outy); END behave;

必须先编译、调试子模块,才能使用元件例化语句。

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY muxk IS PORT ( a1,a2,a3:in std_logic;

s0,s1: in std_logic; outy: out std_logic);

END ENTITY muxk; ARCHITECTURE behave OF muxk IS SIGNAL tmp :std_logic; COMPONENT mux21a

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY CNT12 IS PORT (CLK,RST,EN,LOAD:IN STD_LOGIC;

DATA : IN STD_LOGIC_VECTOR(3 DOWNTO 0); DOUT : OUT STD_LOGIC_VECTOR(3 DOWNTO 0); COUT : OUT STD_LOGIC); END ; ARCHITECTURE behav OF CNT12 IS

COM:PROCESS(Q) IF Q="1011" THEN COUT<='1'; ELSE COUT<='0'; END IF; END PROCESS;

第三章用VHDL语言设计基本逻辑电路

(3)选择信号赋值语句的用法

ARCHITECTURE ar_7 OF fzh_2 IS

BEGIN

WITH q SELECT

y<= a WHEN

结束

″00″, --选择值用“,”

b WHEN ″01″,

c WHEN ″10″,

d WHEN OTHERS;

END ar_7;

4)元件例化语句:主要用于在VHDL中的层次设计。

• Sequential circuits in which the values of the outputs depend on not only on the present values of the inputs but also on the past behavior of the circuit. Such circuits include storage elements that store the values of logic signals.

IF B(0)='1' THEN tmp0<=A; ELSE tmp0<="000"; END IF; IF B(1)='1' THEN tmp1<=A&'0'; ELSE tmp1<="0000"; END IF;

IF B(2)='1' THEN tmp2<=A&"00"; ELSE tmp2<="00000"; END IF;

M: OUT STD_LOGIC_VECTOR(5 DOWNTO 0)); END mul;

ARCHITECTURE beha OF mul IS SIGNAL tmp0:STD_LOGIC_VECTOR(2 DOWNTO 0); SIGNAL tmp1:STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL tmp2:STD_LOGIC_VECTOR(4 DOWNTO 0); BEGIN PROCESS(A,B) BEGIN

二选一数据选择器报告

EDA实验报告组合电路设计一、实验目的1、熟悉quartusⅡ的VHDL文本设计全过程,2、学习简单组合电路的设计、多层次电路设计、仿真和硬件测试。

二、实验内容1、实验内容2:将此多路选择器看成一个元件mux21a,利用元件例化语句描述成三选一,然后进行编译、综合、仿真。

2、实验内容3:引脚锁定以及硬件下载测试。

选实验电路模式5,用键1(PIO0)控制s0;用键2(PIO1)控制s1;a3、a2和a1分别接clock5、clock0和clock2;输出信号outy仍接spker,通过短路帽选择clock0接256Hz信号,clock5接1024Hz信号,aclock2接8 Hz信号。

最后进行编译、下载和硬件测试实验。

三、实验器材PC机一台、Quartus II软件、EDA实验箱一台、下载电缆一根(已接好)。

四、实验程序实验内容2:三选一library ieee;use ieee.std_logic_1164.all;entity muxk isport(a1,a2,a3: in std_logic;s0,s1: in std_logic;outy: out std_logic);end entity muxk;architecture bhv of muxk iscomponent mux21aport( a,b: in std_logic;s: in std_logic;y: out std_logic);end component;signal tmp: std_logic;beginu1: mux21a port map(a=>a2,b=>a3,s=>s0,y=>tmp);u2: mux21a port map(a=>a1,b=>tmp,s=>s1,y=>outy);end architecture bhv;五、实验步骤实验二:在实验一的基础上,新建VHDL文件,命名为muxk。

基于HDL实现的2选1数据选择器设计

3、变量以及数据类型

reg寄存器型

reg类型定义的是一种能暂存数据的变量。 reg 信号名1,信号2,……;//定义一位reg型数据 reg [n-1:0]信号名1,源自号2,……; //定义n位reg型数据

用reg数据类型定义的信号必须放在过程块 (如always,initial)中通过过程赋值语句赋值。

时,运算的结果就为真。只有当两个操作数都为假时,则运算的结

果才为假。

逻辑非“!”只有一个操作数,用法:!操作数。

h

16

3、 关系运算符

关系运算符号 > >= < <=

功能 大于 不大于(小于等于) 小于 不小于(大于等于)

h

17

4、位运算符

位运算符号 ~ & | ^

^~、~^

功能 按位取反

按位与 按位或 按位异或 按位同或

第五讲:基于HDL实现的2选1数据选择器设计 主讲人:雷求胜

h

1

复习: Verilog HDL模块的一般结构

模块声明 module 模块名(port1,port2,port3…portn); 端口声明语句块 逻辑功能描述语句块 Endmodule

h

2

一、数据类型及常量变量

1、标识符

标识符用于表示电路系统中模块、寄存器、输 入/输出端口、连线等物理对象名字。

h

10

二、连续赋值语句及“?:”语句

1、连续赋值语句 assign wire型变量=表达式;

连续赋值语句assign与过程语句always中过程赋值语 句的区别.

a、连续赋值语句用于wire型数据,而过程赋值语句用于 寄存器型变量的赋值。

第3章 VHDL设计初步计数器..

七段(八段)数码管示意图

七段(八段)数码管实物图

数码管静态显示

对应的引脚给出 相应的编码,即 可发光。以共阴 极数码管为例, 如右图所示。

数码管动态显示

把所有数码管的8个笔划段a-h同名端共阳 极连在一起,而每一个数码管的公阴极是 各自独立地控制。

数码管动态显示

所有数码管接收到相同的字形码。所有数 码管的8个笔划段a-h同名端连在一起,同一 个瞬间所有的数码管显示都是相同的。那 么在一个屏幕上如何显示0,1,2,3,4,5这样不 同的数字呢?

3.3 计数器的VHDL设计

3.3 计数器的VHDL设计

3.3.1 4位二进制加法计数器设计 Buffer 只接收内部信号,不接收外部信号,兼有out功能 Out类型端口只能输出,不能与内部信号运算 3.3.2 整数类型

3.3.3计数器的其他VHDL表达方式

3.3 计数器的VHDL设计

3.3.3 计数器的其他VHDL表达方式

3.4 实用计数器的VHDL设计

带有异步复位同步使能的十进制加法计数器

RST

EN CLK

CNT10

CQ(3) CQ(2) CQ(1) CQ(0)

COUT

3.4 实用计数器的VHDL设计

3.3.3 计数器的其他VHDL表达方式

接下页

3.4 实用计数器的VHDL设计

接上页

3.4 实用计数器的VHDL设计

3. 时序模块中的同步控制信号和异步控制信号的构建

4. 另一种描述方式

3.4 实用计数器的VHDL设计

3.3.3 计数器的其他VHDL表达方式

3. 时序模块中的同步控制信号和异步控制信号的构建 4. 另一种描述方式

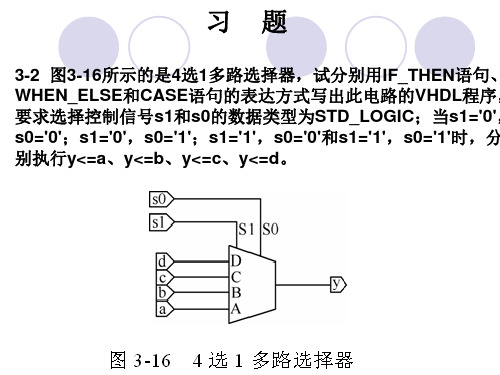

习

题

第三章 VHDL程序结构与要素

件、函数和过程只能用于这个结构体中,若希望其能

用于其他的实体或结构体中,则需要将其作为程序包

来处理。

第3章

VHDL程序结构与要素

ARCHITECTURE behavioral OF example_dairu IS

SIGNAL a, b, c, d : BIT ;

SIGNAL temp0, temp1 : STD_LOGIC ; BEGIN

第3章

VHDL程序结构与要素

数 D1 据 输 入 D2-1 n

D0

„

Y

数 据 输 出

n 位地址选择信号

S 0 1

Y a b

第3章

VHDL程序结构与要素

【例3-1】 2选1多路选择器程序 LIBRARY IEEE; --IEEE库使用说明语句 USE IEEE.STD_LOGIC_1164.ALL; ENTITY mux21 IS --实体说明部分 PORT( a,b : IN STD_LOGIC; s: IN STD_LOGIC; y: OUT STD_LOGIC ); END ENTITY mux21;

[3]结构体说明用于描述该设计实体内部工作的逻辑关 系,是不可视部分。在一个实体中,可以含有一个或一个 以上的结构体,而在每一个结构体中又可以含有一个或多 个进程以及其他的语句。

第3章

VHDL程序结构与要素

3.1.1 实体

实体是一个设计实体的表层设计单元,其功能

是对这个设计实体与外部电路进行接口描述。它规

INOUT

BUFFER

双向(可以输入,也可以输出)

输出(结构体内可再使用),可以读或 写

第3章

VHDL程序结构与要素

IN

OUT