低功耗射频电路设计与应用

低功耗无线通信技术的设计与优化研究

低功耗无线通信技术的设计与优化研究随着移动通信和物联网技术的迅速发展,低功耗无线通信技术成为了当前研究的热点之一。

在许多应用场景中,如物联网、智能家居和可穿戴设备,低功耗通信技术对于延长设备寿命和减少能源消耗至关重要。

本文将重点探讨低功耗无线通信技术的设计与优化研究。

首先,低功耗通信技术需要考虑的一个关键方面是能量效率。

在无线通信中,能量效率是指每传输一个比特所需的能量消耗。

为了提高能量效率,有几个方面需要考虑。

首先是传输距离的优化。

通信系统应该尽量减小传输距离,以降低能量消耗。

其次是信号调制方案的选择。

选择适当的信号调制方案可以减少功耗,提高能量效率。

最后是功率控制。

通过动态功率控制,系统可以在不同的信道状态下调整传输功率,以降低能量消耗。

第二个关键方面是通信协议的设计与优化。

通信协议是无线通信中的关键组成部分,它负责处理数据传输、路由和资源分配等任务。

在低功耗通信中,通信协议的设计需要考虑以下几个因素。

首先是数据采样率的优化。

通过降低数据采样率可以减少数据传输量,从而降低能量消耗。

其次是分组和压缩算法的应用。

通过合理的分组和压缩算法可以减少数据传输的次数和数据量,从而减少能量消耗。

最后是通信协议的能量管理。

通信协议应该具备动态的能量管理机制,根据通信需求和能源状况调整通信模式和功率控制。

第三个关键方面是硬件设计与优化。

低功耗无线通信技术的设计需要仔细考虑硬件的功耗消耗。

首先是功耗优化器的设计。

功耗优化器是指用于减小功耗的电路设计和优化技术。

通过优化器的设计,可以达到最小化功耗的目标。

其次是射频设计的优化。

射频电路是无线通信系统中的关键部分,其功耗消耗在整个系统中占比较高。

通过采用低功耗的射频设计和优化技术,可以显著减少系统的功耗。

最后是能量收集和能量管理的设计。

通过能量收集技术,可以利用环境能量来为无线通信系统供电,减少电池的耗电量。

能量管理系统可以智能地管理系统中各个部分的能量消耗,提高能量利用率。

低功耗电路设计中的VLSI技术及应用

低功耗电路设计中的VLSI技术及应用随着科技的不断进步,电子设备越来越普及,而低功耗设计就越发成为电路设计中的热点话题。

在众多低功耗电路设计中,VLSI技术具有其独特的优势,也成为低功耗电路设计的重点研究方向。

一、 VLSI技术简介VLSI即Very Large Scale Integration(超大规模集成电路)技术,它是指在单片半导体芯片上集成数亿个(至少包括几十万个至上百万个)晶体管和其它电子元器件,用来实现各种功能的技术。

VLSI技术在现代电路设计中扮演着至关重要的角色,它的应用不仅能够大大提高电路性能,还能减少芯片的功率消耗,进而实现低功耗电路的设计。

二、低功耗设计的重要性低功耗设计是现代电路设计中不可或缺的一部分。

随着移动设备,可穿戴设备等电子产品的不断涌现,低功耗电路将更加重要。

低功耗电路设计对于电子设备的使用寿命、效率、成本等方面都有极大的影响。

当电子设备在待机状态下,电路应能够在最小功耗的前提下,仍然能够快速唤醒;当处于工作状态时,芯片也应尽量保持低功耗状态。

而VLSI技术正是为实现低功耗电路提供了可靠的技术支持。

三、VLSI技术在低功耗电路设计中的应用1. 通用体积缩小技术在现代电路设计中,体积缩小已成为一种大势所趋。

VLSI技术可以通过缩小器件等方式,实现芯片体积的缩小。

这样做可以带来许多好处,如更加轻便的设备,更方便的携带与使用等。

缩小器件的工艺流程,可以进一步改善芯片材料及结构,使得芯片的功耗降低。

2. 针对特殊应用的设计设计专门针对特定应用领域的芯片也是VLSI技术的一个优势。

例如,深度学习等领域需要大量的计算资源。

针对这种需求,VLSI芯片可以在保证计算能力的前提下,使芯片功耗降低,达到低功耗的效果。

3. 低功耗模式的设计在电子产品使用过程中,待机状态下芯片应能够在最小功耗的前提下,仍然能够快速唤醒。

同时,当处于工作状态时,芯片也应尽量保持低功耗状态。

这就需要在设计电路时,针对特定功能需求,实现低功耗模式的设计。

SX1278低功耗硬件设计方案_202001081640062

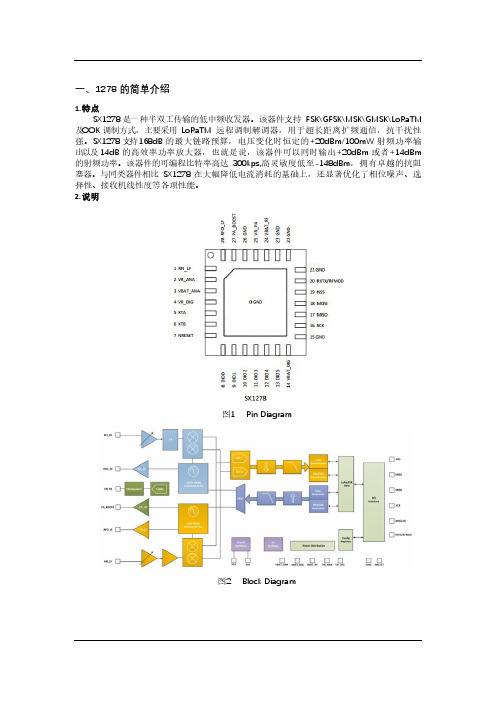

一、1278的简单介绍1.特点SX1278是一种半双工传输的低中频收发器。

该器件支持FSK\GFSK\MSK\GMSK\LoRaTM 及OOK调制方式,主要采用LoRaTM远程调制解调器,用于超长距离扩频通信,抗干扰性强。

SX1278支持168dB的最大链路预算,电压变化时恒定的+20dBm/100mW射频功率输出以及14dB的高效率功率放大器,也就是说,该器件可以同时输出+20dBm或者+14dBm 的射频功率。

该器件的可编程比特率高达300kps,高灵敏度低至-148dBm,拥有卓越的抗阻塞器。

与同类器件相比SX1278在大幅降低电流消耗的基础上,还显著优化了相位噪声、选择性、接收机线性度等各项性能。

2.说明图1Pin Diagram图2Block Diagram注:由SX1278的数据手册可知,发射时从第27引脚PA_BOOST引脚出来功率才能达到20dBm,但是做不到发射时功耗低,电流有120mA左右;但是发射时从第28引脚RFO_LF/RFO_HF引脚出来,功率可达14dBm,电流可低至29mA,适合有低功耗需求的应用场景。

这里主要介绍低功耗的硬件设计方案,电路分为2个部分:原理图的设计和PCB的设计。

二、原理图的设计整体框架:电源电路,复位时钟电路,射频电路和外部接口电路这四部分组成。

1.电源电路SX1278的第3引脚VBAT1(VBAT_ANA)为模拟电路电源电压,第14引脚VBAT3(VBAT_DIG)为数字部分电源电压,24引脚VBAT2(VBAT_RF)为射频电路电源电压。

电源电路主要是这3个引脚的供电,供电范围为1.8V-3.7V,都推荐3.3V供电,可用同一个电源供电。

并且在每个电源处需要至少加一个滤波电容,减少电源的纹波以保证供电的稳定性。

2.复位时钟电路晶振电路有无源晶振和有源晶振,正常情况下,为保证频率的准确度和更高的灵敏度,推荐用有源晶振。

但是为了保证尺寸最小、性价比最高同时成本低,建议换成无源晶振。

射频芯片设计中的功耗优化技巧

射频芯片设计中的功耗优化技巧射频(Radio Frequency,RF)芯片是无线通信系统中重要的组成部分。

功耗优化对于射频芯片的性能和续航能力至关重要。

在射频芯片设计中,合理的功耗优化技巧可以提高功耗效率、延长电池寿命,并提高系统性能。

本文将探讨一些射频芯片设计中的功耗优化技巧,旨在帮助工程师们更好地优化射频芯片的功耗表现。

1. 模拟电路功耗优化模拟电路是射频芯片中主要功耗来源之一。

通过合理的电路设计和优化,可以降低功耗,并提高系统性能。

1.1 选择低功耗器件:在设计射频芯片时,选择低功耗的无源器件和功率放大器是至关重要的。

低功耗器件具有较低的漏电流和电流噪声,可以显著降低功耗。

1.2 优化电源电压:合理的电源电压设计可以降低功耗。

通过选择适当的电源电压,可以在兼顾功耗和性能的前提下降低功耗。

1.3 降低振荡器功耗:振荡器在射频芯片中运行频率高且功耗较大。

通过采用低功耗振荡器设计,如电容中性振荡器(CMOS Oscillator)或谐振薄膜振荡器,可以降低功耗。

1.4 时钟管理技术:在射频芯片设计中,时钟是关键的元件之一。

采用适当的时钟管理技术,如动态时钟门控、时钟闪存和动态电压调整(DVM)等技术可以降低功耗。

2. 数字电路功耗优化射频芯片中的数字电路也是功耗的重要组成部分。

优化数字电路设计可以有效降低功耗并提升系统性能。

2.1 降低时钟频率:适当降低时钟频率可以降低功耗。

通过减小时钟频率,可以降低电路开销和功率消耗。

2.2 逻辑优化:采用适当的逻辑优化技术可以降低功耗。

例如,通过使用更简单的逻辑电路和减少逻辑门数量,可以降低功耗。

2.3 管理器件的活动功耗:在数字电路设计中,减少门的切换次数可以显著降低功耗。

因此,在设计中应该尽量减少冗余切换和不必要的信号重新计算。

2.4 功耗管理技术:采用功耗管理技术也是降低数字电路功耗的有效方法。

例如,动态电压调整(DVC)、主动电压调整(AVC)和功耗感知自适应电源(PAAP)等技术可以根据系统需求进行功耗调整。

Sub-1G和2.4G超低功耗双频段无线系统设计与应用

胡波

(安 徽 中 科 光 电 色 选 机 械 有 限 公 司 ,合 肥 231202)

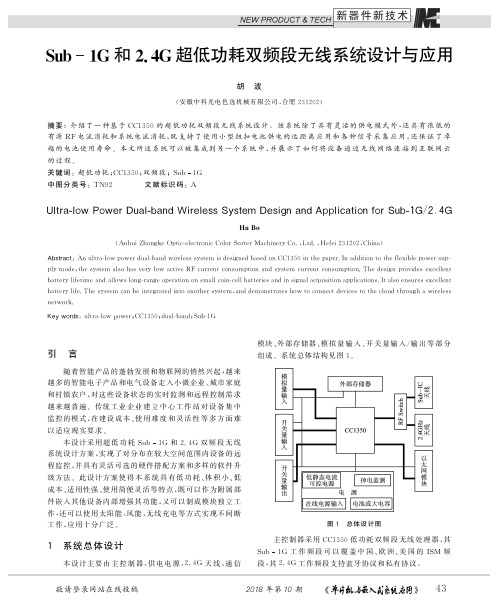

摘要:介 绍 了 一 种 基 于 CC1350 的 超 低 功 耗 双 频 段 无 线 系 统 设 计 。 该 系 统 除 了 具 有 灵 活 的 供 电 模 式 外 ,还 具 有 很 低 的

2.7 通信模块

将系统 UART 接口与以太 网 模 块、CAN 总 线 模 块 等 互 联 ,可 以 完 成 从 有 线 系 统 到 无 线 系 统 的 通 信 连 接 。

图3 电源结构

由 AC DC 模块或 DC DC 模 块 输 出 的 12 V DC 电 源为开关量输出电路供电,用于驱动继电器、直流电 机、声 光报警器等设备;而3.3V DC 则 为 以 太 网 模 块 等 外 围 接 口电路直接供电,同时通过防反流 电 路 与 电 池 提 供 的 3 V DC 电路汇合;汇合后的3 V DC 电 路 为 主 控 制 器 CC1350 供电,保证其在无外 部 电 源 输 入 时 仍 能 不 间 断 工 作,同 时 3V DC 电路还通过低静态电流可控电 源 降 为 1.8 V DC, 为 模 拟 量 输 入 电 路 、开 关 量 输 入 电 路 和 外 部 存 储 器 供 电 。

敬请登录网站在线投稿

2018 年第10 期

43

2 电路设计

2.1 系统核心部分

2.1.1 处理器 CC1350简介 CC1350 是 德 州 仪 器 (TI)出 品 的 一 款 多 核 心 双 频 带 无

线 微控制器,其内部集成了强大的 Cortex M3内核、专用 于处理底层 RF 协议的 Cortex M0无线内核和一个超低

一种低功耗的航空无线网络系统技术研究

一种低功耗的航空无线网络系统技术研究摘要:本文中航空无线网络系统是基于无线通信芯片CC2530,并以终端节点、协调器节点为主要框架来建立的;硬件主要基于目前不同电路功能单元CBB模块设计理念;软件设计基于Z-Stack协议栈,针对不同的传感器功能进行了具体设计,实现了无线网络系统的组建以及传感器数据的发送,后续对无线传感器网络系统进行分析测试验证。

关键词:低功耗、无线网络系统、传感器、Z-Stack协议栈1 概述在现代航空领域中,存在大量机载设备(传感器设备、导航设备、显示设备、飞行控制设备等)。

各设备之间的数据传输主要采用数据总线的方式来实现,但存在如下问题:一是中心节点失效导致网络瘫痪问题;二是电缆极为复杂,电缆数量较多时重量可达数吨,制造及敷设困难;三是随运行时间的增长,屏蔽线缆的脱焊会使得信号传输质量大大降低;四是系统改进升级灵活性受电缆的限制较大;五是设备测试技术装配过程中需要引入大量的现场连线和附加重量,导致系统维护越来越麻烦,测试效率低下。

基于有线传输存在的问题,对转变信号传输方式提出了新的要求,通过无线传感器网络对对信号进行采集、数据传输和系统测试提出了新的要求。

应用无线网络来替代现有线缆架构的机载传感器系统,将大量传感器网络节点部署在监测区域内对目标的温度、压力等信号进行测量,通过多节点协作以及无线信号发送,能够满足飞机日益增长的传感器数量和冗余度要求,大幅减轻飞机重量,将直接提高飞机的战斗生存性和总体系统的可靠性。

2设计方案无线网络系统主要包括架构设计、无线网络系统中的终端节点与协调器节点结构设计、功能模块硬件设计(电源管理单元、总线通信单元、信号采集单元、无线通讯单元等)、系统软件设计(无线通信协议、节点应用程序、无线网络系统传感器组网、多节点数据融合传感器信号采集处理、系统通信开发及设计)等。

2.1架构设计测量场景中分布的多类型无线传感器节点(终端节点)与协调器节点通过自组织方式构成了无线传感器网络系统。

射频电子电路设计与应用

用于产生射频信号,用于 测试电路的输入性能。

示波器

4

用于观察信号波形,分析 信号的时域特性。

频谱分析仪

2

用于测量射频信号的频率

、功率、信号质量等参数

。

网络分析仪

3

用于测量射频电路的阻抗 、增益、相位等参数。

调试方法与步骤

电源检查

确保电路供电正常,无短路或断 路现象。

优化调整

根据测量结果对电路进行调整, 优化性能参数。

参数计算

根据电路原理图,计算元 件参数、性能指标和电路 性能参数。

元件选择与匹配

元件规格

根据电路性能参数和设计 目标,选择合适的元件规 格和型号。

元件匹配

确保电路中元件的参数匹 配,避免因元件不匹配导 致性能下降或失真。

元件稳定性

选择稳定性好、可靠性高 的元件,以提高电路的稳 定性和可靠性。

电路布局与布线

电磁兼容性设计

01

02

03

电磁干扰源

识别和分析电路中的电磁 干扰源,如电压电流突变 、谐波等。

电磁屏蔽

采用电磁屏蔽技术,减小 电磁干扰对电路的影响, 提高电磁兼容性。

滤波技术

采用滤波器、电容器等元 件,减小电磁干扰的传播 ,提高信号质量。

Part

03

射频电子电路的测量与调试

测量仪器与技术

信号发生器

02

射频电子电路设计

设计流程与方法

确定设计目标

明确电路的功能、性能指 标和限制条件,如工作频 率、功率、尺寸等。

优化改进

根据仿真结果,对电路进 行优化改进,提高性能和 稳定性。

原理图设计

根据设计目标,使用电路 元件和器件构建电路原理 图。

物联网节点的低功耗通信电子电路研究与设计

Telecom Power Technology设计应用技术物联网节点的低功耗通信电子电路研究与设计张逸卓(东南大学,江苏南京 210096主要设计物联网节点的低功耗通信电子电路,以提高设备的能效和寿命。

通过深入研究芯片选型、电源成功设计出一种综合考虑性能、物联网节点;低功耗;电压管理;通信Power Communication Electronic Circuits for Internet ofThings NodesZHANG Yizhuo(Southeast University, Nanjing 210096Abstract: The main focus is to design low-power communication electronic circuits for Internet of Things nodesin order to improve the energy efficiency and lifetime of the devices. Through inmanagement circuit design, communication module design, and actual testing, a circuit scheme with comprehensive 2024年2月10日第41卷第3期29 Telecom Power TechnologyFeb. 10, 2024, Vol.41 No.3张逸卓:物联网节点的低功耗通信电子电路研究与设计量控制部分是为了实现对设备功耗的精准监测和优化[3]。

该部分的关键作用之一是实时监测设备的功耗状况,使系统能够根据实际需求调整电源工作状态,从而最大限度地降低功耗。

通过电流测量,系统可以智能管理电源,延长电池寿命,动态调整电流,以适应设备在不同工作模式下的电流需求。

此外,电流测量为系统提供了故障检测、实时性能监控和智能休眠唤醒等功能,使设备在保持高效性能的同时能够实现最大限度的节能和稳定性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

低功耗射频电路设计与应用射频电路在现代通信系统中扮演着重要的角色。

随着无线通信技术的快速发展,对低功耗射频电路的需求也日益增加。

本文将介绍低功耗射频电路的设计原理和应用,以及相关的技术趋势。

一、低功耗射频电路设计原理

低功耗射频电路设计的核心目标是在满足通信系统要求的前提下,尽可能降低功耗。

以下是一些常用的低功耗射频电路设计原理:

1. 低噪声放大器设计:在接收机中,噪声是一个重要指标。

采用低噪声放大器可以减小接收机的噪声系数,提高信噪比。

2. 功放设计:功放在发送机中起到放大信号的作用。

低功耗射频功放的设计应注重提高效率,减小功耗。

3. 频率合成器设计:频率合成器用于产生稳定的射频信号。

采用低功耗的VCO(Voltage Controlled Oscillator)和PLL(Phase-Locked Loop)可以有效降低功耗。

4. 信号调理电路设计:信号调理电路包括滤波器、混频器等,用于对射频信号进行处理。

低功耗的滤波器设计可以减小功耗。

5. 硬件设计与算法优化:对于某些特定的射频应用,通过硬件设计与算法优化可以有效降低功耗。

例如,通过优化通信协议、减小数据传输量等方式来降低功耗。

二、低功耗射频电路应用

低功耗射频电路在各种通信系统中都有广泛的应用。

以下是一些常见的低功耗射频电路应用:

1. 无线传感网络:无线传感网络是由大量分布式传感器节点组成的网络,用于监测和收集环境信息。

低功耗射频电路在无线传感网络中应用可以实现节点长时间工作,延长电池寿命,并降低维护成本。

2. 物联网设备:物联网设备涉及到大规模的数据采集和传输,对功耗要求非常高。

低功耗射频电路可以帮助物联网设备实现长时间的工作,并且减少更换电池的频率。

3. 个人移动设备:如智能手机、平板电脑等个人移动设备对低功耗射频电路有着强烈的需求。

低功耗射频电路的应用可以延长设备的待机时间,提供更长的通信时长。

4. 物联网智能家居:低功耗射频电路在物联网智能家居系统中可以实现设备之间的通信与协调。

以智能家居中的智能插座为例,低功耗射频电路可以帮助智能插座实现与智能手机的远程通信控制。

三、低功耗射频电路的技术趋势

随着射频技术的不断发展,低功耗射频电路也在不断演进。

以下是一些低功耗射频电路的技术趋势:

1. 集成化设计:随着半导体工艺的进步,低功耗射频电路的集成化程度越来越高。

通过集成化设计,可以减小电路面积、降低功耗、提高性能。

2. 新型材料应用:研究人员不断尝试新型材料的应用,如石墨烯、

碳纳米管等,来实现低功耗射频电路的设计。

3. 节能技术创新:节能技术创新是低功耗射频电路发展的重要方向。

例如,采用动态电源管理技术、低功耗睡眠模式等,可以有效减小功耗。

4. 软件无线电技术(SDR):SDR技术的发展使得射频电路的设计

更加灵活。

通过软件编程,可以对射频电路进行优化和调整,降低功耗。

结论

低功耗射频电路的设计与应用在现代通信系统中具有重要意义。

随

着技术的不断进步,我们可以预见低功耗射频电路将在各个领域得到

广泛应用,并为通信系统的发展带来更多的创新和便利。