实验五全加器的设计及应用

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一、实验目的

(1) 进一步加深组和电路的设计方法。

(2) 会用真值表设计半加器和全加器电路,验证其逻辑功能 (3) 掌握用数据选择器和译码器设计全加器的方法。

二、预习要求

(1) 根据表5-1利用与非门设计半加器电路。

(2) 根据表5-2利用异或门及与非门设计全加器电路

三、 实验器材

(1) 实验仪器:数字电路实验箱、万用表;

(2) 实验器件:74LS04 74LS08 74LS20 74LS32、74LS86 74LS138 74LS153;

四、 实验原理

1. 半加器及全加器

电子数字计算机最基本的任务之一就是进行算术运算,在机器中的四则运算一一 加、减、乘、除都是分解成加法运算进行的,因此加法器便成了计算机中最基本的运算 单元。 (1)半加器

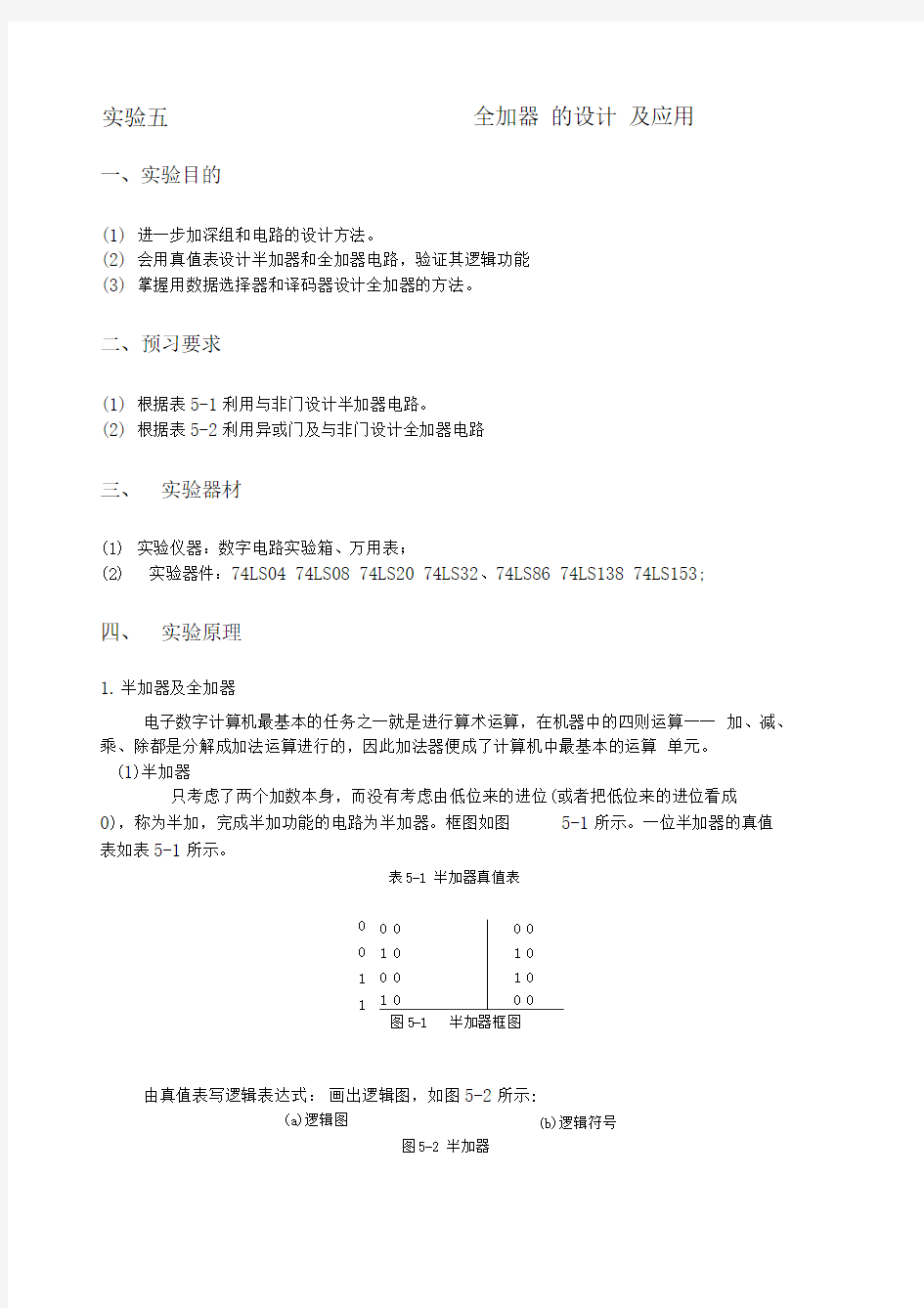

只考虑了两个加数本身,而没有考虑由低位来的进位(或者把低位来的进位看成

0),称为半加,完成半加功能的电路为半加器。框图如图 5-1所示。一位半加器的真值

表如表5-1所示。

由真值表写逻辑表达式: 画出逻辑图,如图5-2所示:

(a )逻辑图

图5-2 半加器

实验五

全加器 的设计 及应用

0 0

0 0 1 0

1 0

0 0

1 0 1 0

0 0

图5-1

半加器框图

表5-1 半加器真值表

0 0 1 1 (b )逻辑符号

(2)全加器

能进行加数、被加数和低位来的进位信号相加, 称为全加,完成全加功能的电路为 全加器。根据求和结果给出该位的进位信号。即一位全加器有3个输入端:A (被加数)、

B i (加数)、

C i i (低位向本位的进位);2个输出端:S i (和数)、C i (向高位的进位) 下面

给出了用基本门电路实现全加器的设计过程。

图5-3 全加器的卡诺图

3) 由卡诺图写出逻辑表达式:

如用代数法写表达式得: 即:

4) 画出逻辑图,如图5-4 (a )所示;图5-4 (b )是全加器的逻辑符号

(a )逻辑图

(b )逻辑符号

图5-4全加器

五、实验内容

1 •利用异或门及与非门实现一位全加器,并验证其功能。

答:逻辑电路图如下:

2. 试用全加器实现四位二进制全减器。

3. 试用一片四位二进制全加器将一位 8421BCD 码转换成余3码,画出电路图,并测试 其功能。

4. 试用一片3— 8线译码器及四输入与非门设计一位全加器, 要求电路最简,画出设计

电路图,并测试其功能。

5•试用74LS86组成二个四位二进制数的比较电路,要求两数相等时其输出为“ 1” , 反之为“ 0”。

6.试用双四选一数据选择器和与非门分别构成全加器及全减器,写出表达式,画出逻 辑图,要求

电路最简,并测试其功能。

六、实验报告及要求

1 •在熟知实验基本原理的基础上,实验报告中要简明阐述实验原理 2.整理实验结果、图表,并对实验结果进行分析讨论

1)列出真值表,如表5-2所示。

表5-2 全加器真值表

从表5-2 器中

包含着

0时,不 的进

位,就是 全加器中C i ! 值可为0或1。

2)画出

图,如图5-3

全加器

中看出,全加 半加器,当 考虑低位来 半加器。而在 是个变量,其

S 、C i 的卡诺

所示。

(b ) C i

(a ) S

3.总结组合逻辑电路的设计方法。