Allegro的使用总结

allegro总结『精』

广州飞哥汽车音响有限公司

Plated:金属化的; Non-Plated:非金属化的。 一般的通孔元件的管脚焊盘要选择金属化的, 而元件安装孔或者定位孔则选择非金属化 的。 在 Drill diameter 编辑框中输入钻孔的直径。 如果选择的是椭圆或者矩形孔则是 Slot size X,Slot size Y 两个参数,分别对应椭圆的 X,Y 轴半径和矩形的长宽。 一般情况下只要设置上述几个参数就行了,其它参数默认就可以。设置好以后单击 Layers 标签,进入如图 1.2 所示界面。

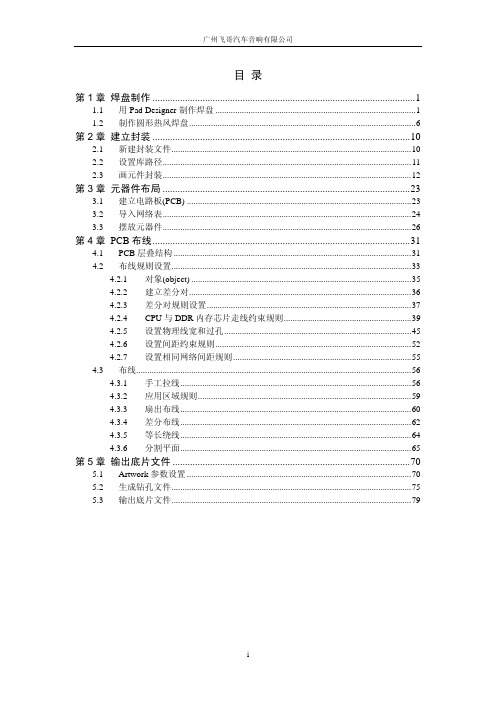

第 4 章 PCB 布线 .......................................................................................................31

PCB 层叠结构 ............................................................................................................31 布线规则设置 .............................................................................................................33 4.2.1 对象(object) ....................................................................................................35 4.2.2 建立差分对 .....................................................................................................36 4.2.3 差分对规则设置 .............................................................................................37 4.2.4 CPU 与 DDR 内存芯片走线约束规则 ..........................................................39 4.2.5 设置物理线宽和过孔 .....................................................................................45 4.2.6 设置间距约束规则 .........................................................................................52 4.2.7 设置相同网络间距规则 .................................................................................55 4.3 布线.............................................................................................................................56 4.3.1 手工拉线 .........................................................................................................56 4.3.2 应用区域规则 .................................................................................................59 4.3.3 扇出布线 .........................................................................................................60 4.3.4 差分布线 .........................................................................................................62 4.3.5 等长绕线 .........................................................................................................64 4.3.6 分割平面 .........................................................................................................65

Allegro使用技巧

Allegro使用技巧这几个分别是通用,布局,布线。

右键不一样,注意区别,最后一个是修剪直角。

Allegro技巧有太多了,就先选择我们会用到的10个类型。

Allegro封装神器FPM,写进教科书的网友作品。

快速生成封装。

•快速丝印丝印摆放总共分三步。

第一步调整统一大小先打开丝印层。

选择Edit-change,在find中只选择text,options中只选择text block并设置成自己需要的字体。

框选左右丝印。

第二步全部居中Manufacture-label Tune弹出label tune:配置如上,框选所有字体。

字体自动对齐器件中心。

如果没有label Tun选型,选择file-change edit勾选allegro productivity toolbox第三步放到合适位置可以第二步中的Center text设置好便宜距离之后,框选对应字体,对于0603元件通常短边60,长边110。

对于不规则或者密集器件,只能手动摆放。

•器件对齐除了选择大个网格摆放对齐外,对于高密度板,我们可以利用allegro的对齐功能进行器件对齐1.选择第二个placementedit2.框选需要对齐器件后,右键选择Align components 根据需要选择对齐模式,同时可以通过equal spaceing选择间距。

•Env文件Env可以快速的配置快捷键,比如实现AD里面的“空格”旋转器件(这里设置的是R)。

我们通常配置为全局量。

位置在...\Cadence\SPB_Data\pcbenv 下,直接替换即可。

替换前注意保存原来的set padpath等路径。

不然替换后还要重新设置路径。

快捷键有两种alias和funckey,Alias对于字母、数字类快捷键需要回车才会执行,Funckey则无需回车。

部分设置如下:funckey A slide #修线funckey B unrats net #关掉网络飞线funckey C change #改变属性funckey D shape select #修改铜皮funckey E add line #添加没有电气属性的线funckey F Delay Tune #等长蛇形线funckey G define grid #格点设置funckey H hilight #高亮funckey I zoom in #放大funckey J dehilight #取消高亮funckey K swap components #器件位置交换funckey L mirror #镜像funckey M move #移动funckey N show element #查看属性funckey O zoom out #缩小funckey P show measure #测距funckey Q done #完成funckey R angle 90 #旋转90funckey S shape add #添加铜皮funckey T text edit #文本编辑funckey U Assign Color #用颜色高亮funckey V rats net #打开网络飞线funckey W add connect #走线funckey Y Shape Edit Boundary #切割铜皮funckey Z align components #对齐使用注意事项,1.大小写匹配,2.输入快捷键前没有输入其他字母,可以在cmmand栏查看•增加组同样在placementedit下选中需要设置为同一组的元件,右键add to group,这样在移动的时候在find中选中groups,就可以一起移动了•相似布局对于具有相似的元件特别是电源电路,我们可以利用allegro的相似布局功能,快速布局1.先补好一组布局,右键place replicate create,再次右键选择done。

Allegro操作大汇总

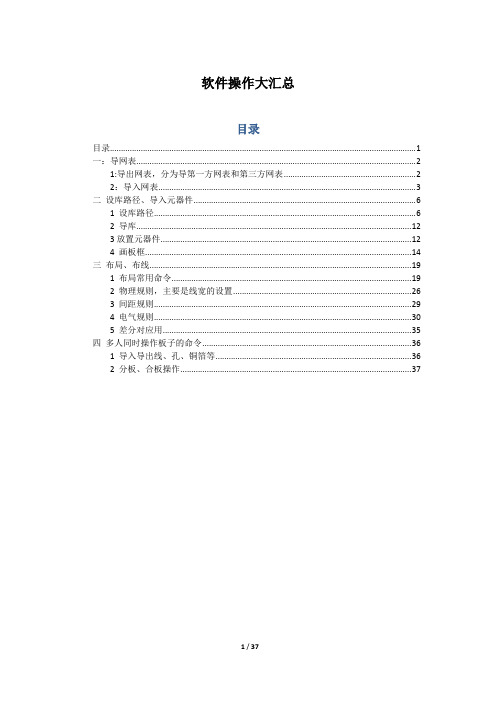

软件操作大汇总目录目录 (1)一:导网表 (2)1:导出网表,分为导第一方网表和第三方网表 (2)2:导入网表 (3)二设库路径、导入元器件 (6)1 设库路径 (6)2 导库 (12)3放置元器件 (12)4 画板框 (14)三布局、布线 (19)1 布局常用命令 (19)2 物理规则,主要是线宽的设置 (26)3 间距规则 (29)4 电气规则 (30)5 差分对应用 (35)四多人同时操作板子的命令 (36)1 导入导出线、孔、铜箔等 (36)2 分板、合板操作 (37)一:导网表1:导出网表,分为导第一方网表和第三方网表第一方网表:a,打开原理图b创建网表(第一方)设好路径后点击确定即可C 创建第三方网表,完成后点击确定即可2:导入网表先打开Allegro软件,操作步骤如下ab 单击上图的Logic后弹出如下对话框(一方网表)设好以上路径后点击Import cadence 即可C 导第三方网表设好以上路径后点击Import Other 即可注:第三方网表容易出错,慎用!在导第三方网表是容易出现非法字符,可用以下小软件去掉非法字符:在完成以上去非法字符后,重新执行C选项中的步骤即可,若仍不成功则可能是原理图出了问题,如非法命名,个别器件无封装名等。

二设库路径、导入元器件1 设库路径a 建立工作文件夹此工作文件夹仅是个人工作习惯,如本人通常情况下是见所有的原始文件放在YUANWENJIAN中,原理图则放在SCH中,PCB文件则放在PCB中,其他的也是依此类推。

b 设路径譬如说我要设置a中的LPS MUNCK 项目的路径则有:依此类推:设好后每次都点击OK即可2 导库按以上步骤操作即可完成导库工作在完成导网表和间库导库工作后就可以开始放置元器件了3放置元器件a上步骤中可以看出未放的元器件有104个,按步骤2点击Place 就可以出现以下界面;说到这就得说说如何画板框了4 画板框完成以上操作后就可以在工作框中画板形了板子标注尺寸,先进行设置进行以上设置后就可以标注尺寸了板边倒角,分为导非圆角和圆角倒圆角三布局、布线1 布局常用命令分配差分对关闭某一网络飞线,如GND以上是布局布线的常用窗口命令,接下来给大家详细讲讲规则设置的操作;2 物理规则,主要是线宽的设置a 规则的建立b 规则的应用完成以上步骤后规则就应用成功了3 间距规则a4 电气规则a 创建Class弹出如下对话框添加NET接下来进行约束等长设置弹出如下对话框经行图示操作5 差分对应用四多人同时操作板子的命令1 导入导出线、孔、铜箔等2 分板、合板操作写得不够详尽还请大家多多包涵,后续反响好的话我会进一步详尽我的操作。

Allegro使用总结之BGA出线Fanout

Allegro使⽤总结之BGA出线FanoutFanout About SMDSMD元件的扇出(Fanout)主要是为了后续布线的时候更⽅便的进⾏内层⾛线,尤其是多层板。

⼀般在布局的时候,就可以进⾏相关元件的扇出⼯作了,如BGA等器件。

其它的分⽴SMD元件,由于其引脚数较少,可以在后期布线时进⾏,⽽且也不必像BGA的扇出那样⼯整和美观。

扇出(Fanout)就是指从SMD焊盘引⼀⼩段线然后打过孔(为内层连线做准备)的操作。

iMX31C项⽬的布线⼯作开始时⾸先要进⾏的就是BGA元件⽹络的扇出⼯作。

⽬前ITG没有相关的规范,完全按照泰齐的样板进⾏设计,同时需要做成ITG相关的规范。

1.BGA扇出BGA扇出受到⼏⽅⾯因素制约,封装本⾝PIN-PIN距离过⼩,选择的过孔⼤⼩,BGA周围区域空间以及底层空间是否充裕,规则的设置(主要是Spacing约束规则),当然正确的扇出设置也⽐较重要。

Fanout设置准备⼯作(约束规则)做好以后就可以进⾏Fanout操作了,Route--Fanout by pick,然后右键选择Setup...弹出下图所⽰FANOUT设置对话框。

主要设置Direction和Via Location,Direction中有in、out、either三个选项,in表⽰扇出的过孔在以所有PIN 的边沿框内部,out表⽰外部,either则是两种都可以,见下图即为Direction设置为in的扇出图,仔细点可以看出,有部分PIN没有扇出成功,因为没有扇出空间。

下图是设置为out的情况,发现所有的过孔都被放置在以PIN外围框外,这种扇出设置不适合BGA等IC。

那么,Via Location的设置⼜是如何的呢?下⾯我们来讨论⼀下,下图所⽰的设置是Via Location设置为inside的情况,这种扇出结果是成功的,因为Via Location设置中的inside、outside是以器件的Placebound层为基准的。

ALLEGRO基本使用指南

ALLEGRO基本使用指南一.常用术语和概念PCB(Printed Circuit Board):印刷电路板,指所有具有互关系的元器件放在一块指定大小、形状、由特殊材料叠加而成、实现一定电路功能的线路板。

Symbol:器件封装Pad:焊盘Etch: 线,用于接各pin点以实现物理电路功能。

Line width :线宽,连接线的宽度。

Spacing: 线距,连接线与连接线、pin等之间的距离。

Outline: 板边Rats:飞线,指释各pin点间连接关系的虚线。

DRC:PCB板上产生短路及各种不符合约束规则时产生的报错标志。

Shape:铜铂Via:过孔Text :丝印,也称文字.Top 层:PCB板表面层.Bot 层:PCB板底面层.内层:压合在PCB板内的,用于布线和电源使用。

spacingtopFR4In1FR4 内层FR4二.ALLEGRO 菜单的使用File 菜单:File\new命令:建一个文档,如图2—1-1…进行选择;在在Drawing Name 中输入新文档的保存路径及名称,可点击B B r r o o w w s s e e…Drawing_Type:的下拉栏中选择要新建的文档的格式,主要有以下几种:Board/board(wizard):新建一个。

brd文档;Module:Package symbol:/Package symbol(wizard):Mechanical symbol:Format symbol:Shape symbol:Flash symbol:本文只介召.brd 文档的建立,其它各模块暂不说明。

File\open命令:打开一个已经存在的文档。

File\save命令:保存一个文档。

File\save as…命令:将文档以其它名字保存。

注意:ALLEGRO 进行此命令后,当前正在编辑的文档也将随这更名。

Import/export命令:此部份将在后面中会介召。

Viewlog…/File viewer…命令:查看ALLEGRO一些命令运行后产生的错误信息,信息以。

allegro 操作技巧和总结

allegro 操作技巧和总结Allegro是一款广泛使用的电子设计自动化软件,主要用于PCB设计。

以下是一些Allegro操作技巧和总结:1. 布局技巧:摆放元件时,可以使用Edit菜单中的move、mirror或rotate命令。

设置各层颜色,例如top层为粉色,bottom层为蓝色,有助于区分正反面。

当大电容和小电容同时对一点滤波时,应将小电容拉出的线连接到器件管脚,以靠近管脚的方式放置小电容。

2. 查看线宽和线长:使用Display菜单中的Element功能,并勾选Cline Segs选项,然后点击连线,即可在弹出的信息框中查看线宽和线长信息。

3. 显示过孔焊盘轮廓:在Setup菜单中选择DesignParameters,然后在Display菜单栏中勾选Display planted holes选项。

4. 使用CRTL键:在执行逐个多选指令如Hilight-Temp Group时,按CRTL键可实现反向选择的功能;执行逐个多选指令如Dehilight-Temp Group时,按CRTL键可实现取消选择的功能。

5. 更新封装:完成封装修改后,在Palce-Update Symbols中选择要更新的封装,并确保勾选Update Symbol Padstacks和Ignore FIXED property选项。

6. 设置约束规则:在Setup-Constrains-Set Standard Values中设置线宽和线间距,间距主要包括pin to pin、line to pin、line to line等。

主要使用spacing rule set和physical rule set。

7. 设置Hilight的显示方式:在Setup-User Preferences-Display中勾选Display_Nohilitefont,则以实线显示Hilight,反之则以虚线显示。

8. 设置Differential Pair属性:先设定对net的Differential Pair property,然后在Constraints System控制面板中选择Spacing Rule Nets栏的Attach Property Nets,并在Allegro窗口Control Panel的Find by Name下选择Property,选取相应Property,再对其套用Spacing Rule即可。

Allegro学习总结0523

1、Allegro软件快捷键自定义功能非常好用,例如:通过输入命令:alias F zoom in就表示定义F键功能是zoom in,个人感觉要比PADS使用起来方便。

用这种方法创建的快捷键是不能保存的,可以在创建时同时录制脚本,以脚本方式保存快捷键。

2、Allegro的脚本录制功能根PADS宏命令功能很相似。

3、Allegro的热焊盘定义:如果平面层采用负平面,定义热焊盘时必须定义Thermal Relief 和Antipad层。

创建焊盘过程与xpeditional创建焊盘过程难易程度差不多。

4、Allegro使用坐标命令绘制电路板板框方法实现起来比较方笔(在输出窗口中输入坐标值)5、Allegro的约束管理器功能和使用方法根xpeditional极为相似。

6、Allegro中具有按照区域摆放元件功能:为便于区分模拟、数字电路,精确定位元件布局,可将电路板划分为若干个区域,Allegro将这些区域称为Room。

创建好Room区域后,为每个器件分配这些区域,使用快速放置方式,把元件按照Roo区域来进行放置,可以准确、快速、高效的进行器件的放置,而PADS软件没有该功能(PADS可以安装REFDES参考位号顺序进行放置元件)。

7、Allegro的区域规则很好但是PADS没有区域规则,Xpedition具有区域规则功能。

8、Allegro中元件的对齐是参照鼠标放置在哪个元件上,就依据该元件为基准进行对齐,然而PADS软件是依据鼠标最后选择的元件为基准进行对齐。

9、Allegro中可以删除走线中的一小段、也可以实现移动走线中的一小段线,PADS软件中没有该功能。

10、Allegro学习中布线章节内容:1、设置布线格点2、添加连接线3、布线命令下的Option 控制面板设置4、添加过孔和过孔的选择5、设置盲埋孔6、Bubble布线方式7、Working layer Mode 8、走线基本操作—Slide/Delay Tune/Custom Smooth/Delete/Cut option 9、布线扇出10、群组布线11、自动布线12、Differential pairs 13、设置查分规则14、查分约束说明1—7 15、布线优化Gloss 16、Via Eliminate/line smoothing/centering lines/improve line entry/line fattening/converting corners/11、Allegro可以对指定区域内的元件进行命名,PADS软件没有该功能。

allegro使用汇总.doc

allegro使用汇总1.如何在allegro中勾销花焊盘十字焊盘set up-design parameter - shape-edit global dynamic shape parameters-Thermal relief connects - Thru pins ,Smd pins - full contact2.allegro 中如何设置等长setup - constraints-electrical-net-routing-Min Max Propagation delays 选摘要等长的net-右击-create-pin pair-选择pin 修改prop daly 的min 和max项3.如何设置allegro的快捷键修改文件inst_dir\share\pcb\text\env 或inst_dir\pcbevn\env 快捷键定义如下alias F12 zoom out alias R angle 90 扭转90 度alias F mirror 激活镜相号令alias Z next 执行下一步号令alias End redisplay刷新屏幕alias Del Delete激活删除号令alias Home Zoom fit全屏显示alias Insert Define grid设置栅格alias End redisplay alias Pgdown zoom out alias Pgup zoom in alias F12 custom smooth alias Pgup slide alias Pgdown done alias Home hellolight alias End dehellolight alias Insert add connect alias Del Delete4.如何在allegro中删除有过孔或布线的层时不影响其他层 1.输出specctra的dsn文件allegro-file-export-router-demo.dsn-run 2.产生session文件specctrapcb router-file-write-session-demo.ses-ok 3.删除某一层中的布线和过孔deletectrlD-.. 4.删除allegro中的板层setup-cross section-鼠标右键-delete5.导入session文件allegro-file-import-router-demo.ses-run 也可先将通过该层的过孔先替换成顶层焊盘,删除该层以后再替换回来 5.如何在Allegro中同时扭转多个零件 1.Edit-Move 在Options中Rotation的Point选User Pick 2 再右键选Term Group 按住鼠标左键不放并拉1个框选中器件多余的可用Ctrl鼠标左键点击去掉. 3. 选好需整体扭转的器件后右键complete. 4. 提示你Pick orgion 鼠标左键选扭转中心. 5 下面右键选rotate 即可扭转了. 6.allegro 16.0 透明度设置display-colour/visibility-display-OpenGL-Global transparency-transparent 7.allegro Drill hole size is equal or larger than smallest pad size.Pad will be drilled away.提示Drill hole size is equal or larger than smallest pad size.Pad will be drilled away. 不用理睬这一提示8.ALLEGRO 如何生成钻孔文件Manufacture - NC - Drill Customization-auto generate symbols Manufacture - NC - Drill Legend Manufacture - NC -NC parameters-enhanced excellon format-close Manufacture - NC - NC Drill-auto tool select-optimize drill head travel 9.CAM350如何正确导入钻带文件导进去后MACRO-PLAY-选择CAM350--SCRIPTSPADS_DRILL-选择钻带的REP文件还没测试过,rep文件从哪儿来的呢10.allegro 如何设置route keepin,package keepin 1.setup-area-route keepin,package keepin -画框 2.edit-z-copy-options-package keepin,route keepin-offset-50-点击外框11.allegro 中如何禁止显示shape 完全禁止的方法没找到setup-user preference editor-display-display_shapefill-输入1个较大的数shape在显示时就不是那么显眼了set-user preference editor-shape-no shape fillv 12.如何在allegro设置自定义元件库路径鄙人面两个位置新增自定义元件的路径Setup-User Preferences Editor-Design_paths-padpath Setup-User Preferences Editor-Design_paths-psmpath 1.在allegro中如何修改线宽在Allegro的Setup-constraints里的set standard values中可定义每一层走线的宽度,比如,可以定义VCC和GND的线宽为10 Mil。

allegro?使用汇总

allegro?使用汇总1.如何在allegro中取消花焊盘(十字焊盘)set up->design parameter ->shape->edit global dynamic shape parameters->Thermal relief connects ->Thru pins ,Smd pins -> full contact2.allegro 中如何设置等长setup -> constraints->electrical->net->routing->Min Max Propagation delays选择要等长的net->右击->create->pin pair->选择pin修改 prop daly 的min 和max项3.如何设置allegro的快捷键修改文件$inst_dir\share\pcb\text\env 或$inst_dir\pcbevn\env快捷键定义如下:alias F12 zoom outalias ~R angle 90 (旋转90 度)alias ~F mirror (激活镜相命令)alias ~Z next (执行下一步命令)alias End redisplay(刷新屏幕)alias Del Delete(激活删除命令)alias Home Zoom fit(全屏显示)alias Insert Define grid(设置栅格)alias End redisplayalias Pgdown zoom outalias Pgup zoom inalias F12 custom smoothalias Pgup slidealias Pgdown donealias Home hilightalias End dehilightalias Insert add connectalias Del Delete4.如何在allegro中删除有过孔或布线的层时不影响其他层1.输出specctra的dsn文件allegro->file->export->router->demo.dsn->run2.产生session文件specctra(pcb router)->file->write->session->demo.ses->ok3.删除某一层中的布线和过孔delete(ctrl+D)->..4.删除allegro中的板层setup->cross section->鼠标右键->delete5.导入session文件allegro->file->import->router->demo.ses->run也可先将通过该层的过孔先替换成顶层焊盘,删除该层以后再替换回来5.如何在Allegro中同时旋转多个零件1.Edit->Move 在Options中Rotation的Point选User Pick2 再右键选Term Group 按住鼠标左键不放并拉一个框选中器件多余的可用Ctrl+鼠标左键点击去掉.3. 选好需整体旋转的器件后右键complete.4. 提示你Pick orgion 鼠标左键选旋转中心.5 下面右键选rotate 即可旋转了.6.allegro 16.0 透明度设置display->colour/visibility->display->OpenGL->Global transparency->transparent7.allegro Drill hole size is equal or larger than smallest padsize.Pad will be drilled away.提示Drill hole size is equal or larger than smallest pad size.Pad will be drilled away.不用理睬这一提示8.ALLEGRO 如何生成钻孔文件Manufacture -> NC -> Drill Customization->auto generate symbolsManufacture -> NC -> Drill LegendManufacture -> NC ->NC parameters->enhanced excellon format->closeManufacture -> NC -> NC Drill->auto tool select->optimize drill head travel9.CAM350如何正确导入钻带文件导进去后MACRO->PLAY->选择(CAM350--SCRIPTS)PADS_DRILL->选择钻带的REP文件还没测试过,rep文件从哪儿来的呢10.allegro 如何设置route keepin,package keepin1.setup->area->route keepin,package keepin ->画框2.edit ->z-copy->options->package keepin,route keepin->offset->50->点击外框11.allegro 中如何禁止显示shape完全禁止的方法没找到setup->user preference editor->display->display_shapefill->输入一个较大的数shape在显示时就不是那么显眼了set-user preference editor-shape-no shape fill(v)12.如何在allegro设置自定义元件库路径在下面两个位置添加自定义元件的路径Setup->User Preferences Editor->Design_paths->padpath Setup->User Preferences Editor->Design_paths->psmpath1.在allegro中如何修改线宽在Allegro的Setup->constraints里的set standard values中可定义每一层走线的宽度,比如,可以定义VCC和GND的线宽为10 Mil。

allegro学习问题总结日志

allegro学习问题总结⽇志Allegro 初学习问题总结1.0 基本功能及常应⽤ (2)1.1 制作⼀个板⼦,对于边框要考虑实际的应⽤,这时需要将边框做成弧形,以免伤⼿。

如图下 (2)1.2 分割覆铜图解 (3)1.3 ALLEGRO PCB制版,遇到的问题? (5)1.3.1焊盘制作 (5)1.3.2 原点定义 (6)1.4.1布局与布线以及细节问题 (7)1.5快捷键设置。

(9)1.6 z-cope 覆铜 (11)1.7 ⽹络属性的修改 (12)1.71 引脚⽹络属性的修改。

(12)1.72 shape⽹络属性的修改。

(12)1.9 DRC 处理 (13)1.91 对于out of date shape 错误如何修改 (14)1.10 BGA布线设置规则 (14)2.0 Cadence layout布局布线常见问题详解 (18)丁辉---2010.6.4--1.0 基本功能及常应⽤1.1 制作⼀个板⼦,对于边框要考虑实际的应⽤,这时需要将边框做成弧形,以免伤⼿。

如图下可以吧直⾓转换为圆弧⾓!选择后点击两边即可。

选择Fillet 之后,在画的长⽅形两边,点击下就可以形成⼀个弧形,弧形的⼤⼩在OPTION ⾥⾯设置。

1.2 分割覆铜图解1.3 ALLEGRO PCB制版,遇到的问题?1.3.1焊盘制作1.制作焊盘时要根据具体尺⼨来,在命名时要能够⼀看就知道什么样的焊盘。

2.在制作封装时候:a)如果要引⽤⾃⼰的做的焊盘,⼀定要在建package sysbol 的⾯板中设置好⾃⼰焊盘以及封装的路径,焊盘和封装各⽤⼀个⽂件夹装起来,避免混乱不清。

(这个路径⼀定要设置对,如果你做了⼀个封装,⽤了别个库的焊盘,此时也应该把另⼀个库的焊盘路径设置出来)b)封装做完后:⼀个要确定做的器件的名称,不然你在PCB调⼊⽹络表的时候就调不进去。

在这⾥⾯设置焊盘的路径,以及封装的路径。

有热风焊盘的时候,也需要添加到⾥⾯去。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1. Allegro中我设置了highlight的颜色为白色,但选中后颜色是白蓝相间的,很不方便查看。

是什么地方需要设置,哪位大虾告诉哈我?答:setup/user preferences/display/display_nohilitefont 这个选项打勾就行了。

2. 不小心按了Highlight Sov后部分线高亮成白色,怎样取消?答:这个是用来检查跨分割的,取消的办法是:如果是4层板的话,在电源层跟地层都铺上地网络,然后再按Highlight Sov刷新即可。

3. 如何更改Highlight高亮默认颜色?答:可以在Display->Color/Visibility->Display->Temporary Highlight里修改即可,临时修改颜色可以点Display->Assign Color来实现。

4. 如实现Highlight高亮部分网络,而背景变暗,就像Altium Designer那样?答:可以在Display->Color/Visibility->Display->Shadow Mode打开该模式,并且选中Di m active layer即可。

5. 快速切换层快捷键答:可以按数字区里的“-”或“+”来换层。

6. OrCAD跟Allegro交互时,出现WARNING [CAP0072] Could not find compone nt to highlight错误等?答:OrCAD输出网表,Allegro导入网表,确保两者对的上号,然后在Orcad选中元件,再右键Editor Select,即可在Allegro中选中该元件;反过来,在Allegro中要先Highlight某元件,在Orcad中变会选中该元件。

1.ORcad :首先打开orcad和allegro分别占1/2的窗口界面。

然后orcad中 Tools/creatn etlist/PCB Editor中Create PCB Editor Netlist下的Options中设置导出网表的路径。

然后确定导出网表。

2.Allegro:Files/Import/Logic/ 最底下的Import directory中设置刚才导出网表的路径。

然后导入即可,只要不出现error即可。

3.操作互动:首先在allegro中选中高亮display/Highlight,然后到orcad中选中一个元件或者引脚哪么对应的allegro中旧高亮显示了。

当然了选中Dehighlight就可以不高亮显示了。

7. 关于盲孔及埋孔B/B Via的制作方法?答:可先制作通孔Thru via,然后Setup->B/B via definitions->Define B/B via,如下图,完成后,再在Constraint Manager->Physical->all layers->vias里添加B/B Via即可。

8. 在用Router Editor做BGA自动扇出时,遇到提示无法找到xxx解决方法?答:路径里不能有中文或者空格。

9. 在制作封装时,如何修改封装引脚的PIN Number?答:Edit->Text,然后选中PIN Number修改即可。

10. 对于一些机械安装孔,为什么选了pin后,选中老是删除不了?答:因为这些Mechanical Pin属于某个Symbol的,在Find里选中Symbols,再右键该机械孔,点Unplace Component即可。

11. 在OrCAD里用Off Page Connector为什么没起到电气连接的作用?答:先科普下:1.off_page connector确实是用在不同页间比较合适,同一页中可以选择用连线,总线或者Place net alias来连通管脚,没有见过在同一页中用off_page connector的。

2.off_page connector在电气特性上是没有方向性的,但是在制图时,为了人看方便,所以使用的双向信号和单向信号的符号还是不同的,这是为了让人知道它是输入还是输出。

电气特性的连接是在芯片做原理图封装时,对管脚定义时形成的。

原因分析:Off Page Connector用于平坦式电路图中多页面原理图电气连接(这些原理图必须从属于同一个Parent Sheet Symbol)。

如下图所示才算同一个Parent sheet symbol。

12. 如何将两块电路板合成一块?答:先将电路板A导出成Sub-drawing,然后电路板B再导入该Sub-drawing,同时原理图也合成一个原理图,完后创建网表Netlist,电路板B再导入该Netlist,此时电路板B存在一些未名的器件和已名的器件,因为导入Sub-drawing元件布局跟连线都跟原来的保持一致,但是去掉了电路板A中元件的网表信息的,而导入该Netlist则导入了网表信息,为了利用原来的元件布局,可用Swap->Component命令来交换元件网表信息而保持原来的布局不变。

13. 元件封装中的机械安装孔Mechanical Symbol?答:使用Allegro PCB Design XL的Package symbol模板建立一个元件封装,对于有电气连接性的pin将其按照实际元件的引脚编号。

而对于机械安装孔的pin,将其pin number删除掉,表明它是一个非电气连接性的引脚,大多数指安装孔。

比如DB9、RJ45等接插件都具有两个(或者以上)的机械孔。

14. Mechanical Symbol已经存在库中,但Place->Manually在Mechanical Symbols 里见不到?答:在Placement里的Advance Settings选项卡中选中Library即可。

15. ORCAD画原理图时,off page connector 后加上页码的方法?答:用ORCAD画原理图,很多ORCAD的SCH中,大多在offpage connector 加上一个页码。

方法很简单:Tools->annotate->action->add intersheet reference即可。

16. 布线时,添加到约束中的所有的通孔和盲孔都可以显示,但是所有埋孔都不能显示,不知道为什么。

比如,L1—L2,L1--L3, L1--L8(8层板)都可以显示,但是L2——L7,L3--L6都无法显示?答:在pad制作时需要把microvia点上即可。

17. Allegro Region区域规则设置?答:setup - constraints - constraint manager或者快捷菜单中带cm标记的,Cmgr图标启动constraints manager图表窗体,在窗体中选择object-->create-->region,此后就在表中设置一下物理或者间距规则,只不过在设置通孔时可以双击弹出选择过孔窗体,非常方便。

最后设置完了点击OK,此后在allegro pcb的菜单中shape下有利用Rectangular建立一个矩形,然后在option中的active class 选择Constraint Region,subclass选择all.assgin to region选择你刚刚在规则管理中建立的区域规则名称,如果没有说明你没有保存好,重新操作一遍以上的规则建立过程。

18. 与某个Symbol的引脚相连的Clins和Vias删除不了?答:可能该Symbol为fix,Unfix该Symbol即可。

19. Allegro使用Fanout by pick功能时老是扇不出,而且停到一半卡死?答:可能待扇出Symbol所在区域中存在Etch层的Shape,要删掉这些Shape才行。

20. 将某个网络设置成电源网络,并设置其电压、线宽等属性?答:选中该Net,然后Edit->Properties,按下图修改其属性即可。

或者也可以依次点击T ools->Setup Advisor->Next->Next->Identify DC Nets->填入网络的Voltage即可。

21. 为什么器件bound相互重叠了,也不显示DRC错误呢?是不是哪里设置要打开以下?3 u# n/ O$ F1 d3 @# l. |答:有两种,一个是pin到pin的距离约束,主要是防止短路,需要在constrain中设置smd pin 到smd pin的距离,然后在setup——constrain——modes中的spacing modes中勾选smd pin to smd pin。

另外一个是检查两个器件是否重叠,需要用到place bound top/bottom,至于是顶层还是底层,要更具你的器件而定,这个规则只要是两个器件的place bound层相互重叠就会报警,同样需要打开检查开关,在setup——constrain——modes中的design modes(package)中勾选package to package为on(其中on为实时监测,只要触犯规则就报警,batch为只有点击update drc才监测报警,off是不监测,违反规则不报警)。

当然,Color/Visibility中Stack-UP中相应层中的DRC显示也要开启。

22. 拖动时为什么不显示鼠线?移动铺铜或元件时,原来与之相连的过孔和线都消失了,怎么解决?答:Move时要选中Ripup Etch。

选中Ripup Etch时将去掉跟该Symbol引脚相连的Cli nes,同时显示Rats,选中Stretch Etch时用Clines代替Rats,而什么都不选时则保留Clines 同时显示Rats。

所以移动铺铜或元件为保留原来的过孔和线,则不能选中Ripup Etch。

另外:定制Allegro环境Find(选取)Design Object Find Filter选项:Groups(将1个或多个元件设定为同一组群)Comps(带有元件序号的Allegro元件)Symbols(所有电路板中的Allegro元件)Functions(一组元件中的一个元件)Nets(一条导线)Pins(元件的管脚)Vias(过孔或贯穿孔)Clines(具有电气特性的线段:导线到导线;导线到过孔;过孔到过孔)Lines(具有电气特性的线段:如元件外框)Shapes(任意多边形)Voids(任意多边形的挖空部分)Cline Segs(在clines中一条没有拐弯的导线)Other Segs(在line中一条没有拐弯的导线)Figures(图形符号)DRC errors(违反设计规则的位置及相关信息)Text(文字)Ratsnets(飞线)Rat Ts(T型飞线)文件类型:.brd(普通的电路板文件).dra(Symbols或Pad的可编辑保存文件).pad(Padstack文件,在做symbol时可以直接调用).psm(Library文件,保存一般元件).osm(Library文件,保存由图框及图文件说明组成的元件).bsm(Library文件,保存由板外框及螺丝孔组成的元件).fsm(Library文件,保存特殊图形元件,仅用于建立Padstack的Thermal Relief) .ssm(Library文件,保存特殊外形元件,仅用于建立特殊外形的Padstack).mdd(Library文件,保存module definition).tap(输出的包含NC drill数据的文件).scr(Script和macro文件).art(输出底片文件).log(输出的一些临时信息文件).color(view层面切换文件).jrl(记录操作Allegro的事件的文件)设定Drawing Size(setup\Drawing size....)设定Drawing Options(setup\Drawing option....)status:on-line DRC(随时执行DRC)Default symbol heightDisplay:Enhanced Display Mode:Display drill holes:显示钻孔的实际大小Filled pads:将via 和pin由中空改为填满Cline endcaps:导线拐弯处的平滑Thermal pads:显示Negative Layer的pin/via的散热十字孔设定Text Size(setup\Text Size....)设定格子(setup \grids...)Grids on:显示格子Non-Etch:非走线层All Etch:走线层Top:顶层Bottom:底层设定Subclasses选项(setup\subclasses...)添加\删除 LayerNew Subclass..设定B/Bvia(setup\Vias\Define B/Bvia...)Ripup etch:移动时显示飞线Stretch etch:移动时不显示飞线信号线的基本操作:更改信号线的宽度(Edit\Change\Find\Clines)option\linewidth删除信号线(Edit\Delete)改变信号线的拐角(Edit\Vertex)删除信号线的拐角(Edit\Delete Vertex)23. 如何修改某个Shape或Polygon的网络属性以及边界?答:Shape->Select Shape or void->单击选中该Shape->在右边Option栏Assign net n ame中将Dummy Net修改成自己想要的网络,当鼠标光标停留在边界时可以拖动光标修改边界。