《计算机组成原理》实验报告---8位算术逻辑运算实验

计算机组成原理实验(接线、实验步骤)

计算机组成原理实验(接线、实验步骤)实验⼀运算器[实验⽬的]1.掌握算术逻辑运算加、减、乘、与的⼯作原理;2.熟悉简单运算器的数据传送通路;3.验证实验台运算器的8位加、减、与、直通功能;4.验证实验台4位乘4位功能。

[接线]功能开关:DB=0 DZ=0 DP=1 IR/DBUS=DBUS接线:LRW:GND(接地)IAR-BUS# 、M1、M2、RS-BUS#:接+5V控制开关:K0:SW-BUS# K1:ALU-BUSK2:S0 K3:S1 K4:S2K5:LDDR1 K6:LDDR2[实验步骤]⼀、(81)H与(82)H运算1.K0=0:SW开关与数据总线接通K1=0:ALU输出与数据总线断开2.开电源,按CLR#复位3.置数(81)H:在SW7—SW0输⼊10000001→LDDR2=1,LDDR1=0→按QD:数据送DR2置数(82)H:在SW7—SW0输⼊10000010→LDDR2=0,LDDR1=1→按QD:数据送DR1 4.K0=1:SW开关与数据总线断开K1=1:ALU输出与数据总线接通5. S2S1S0=010:运算器做加法(观察结果在显⽰灯的显⽰与进位结果C的显⽰)6.改变S2S1S0的值,对同⼀组数做不同的运算,观察显⽰灯的结果。

⼆、乘法、减法、直通等运算1.K0K1=002.按CLR#复位3.分别给DR1和DR2置数4.K0K1=115. S2S1S0取不同的值,执⾏不同的运算[思考]M1、M2控制信号的作⽤是什么?运算器运算类型选择表选择操作S2 S1 S00 0 0 A&B0 0 1 A&A(直通)0 1 0 A+B0 1 1 A-B1 0 0 A(低位)ΧB(低位)完成以下表格ALU-BUS SW-BUS# 存储器内容S2S1S0 DBUS C输⼊时:计算时:DR1:01100011DR2:10110100(与)DR1:10110100DR2:01100011(直通)DR1:01100011DR2:01100011(加)DR1:01001100DR2:10110011(减)DR1:11111111DR2:11111111(乘)实验⼆双端⼝存储器[实验⽬的]1.了解双端⼝存储器的读写;2.了解双端⼝存储器的读写并⾏读写及产⽣冲突的情况。

计算机组成原理实验报告

重庆理工大学《计算机组成原理》实验报告学号 __***********____姓名 __张致远_________专业 __软件工程_______学院 _计算机科学与工程二0一六年四月二十三实验一基本运算器实验报告一、实验名称基本运算器实验二、完成学生:张致远班级115030801 学号11503080109三、实验目的1.了解运算器的组成结构。

2.掌握运算器的工作原理。

四、实验原理:两片74LS181 芯片以并/串形式构成的8位字长的运算器。

右方为低4位运算芯片,左方为高4位运算芯片。

低位芯片的进位输出端Cn+4与高位芯片的进位输入端Cn相连,使低4位运算产生的进位送进高4位。

低位芯片的进位输入端Cn可与外来进位相连,高位芯片的进位输出到外部。

两个芯片的控制端S0~S3 和M 各自相连,其控制电平按表2.6-1。

为进行双操作数运算,运算器的两个数据输入端分别由两个数据暂存器DR1、DR2(用锁存器74LS273 实现)来锁存数据。

要将内总线上的数据锁存到DR1 或DR2 中,则锁存器74LS273 的控制端LDDR1 或LDDR2 须为高电平。

当T4 脉冲来到的时候,总线上的数据就被锁存进DR1 或DR2 中了。

为控制运算器向内总线上输出运算结果,在其输出端连接了一个三态门(用74LS245 实现)。

若要将运算结果输出到总线上,则要将三态门74LS245 的控制端ALU-B 置低电平。

否则输出高阻态。

数据输入单元(实验板上印有INPUT DEVICE)用以给出参与运算的数据。

其中,输入开关经过一个三态门(74LS245)和内总线相连,该三态门的控制信号为SW-B,取低电平时,开关上的数据则通过三态门而送入内总线中。

总线数据显示灯(在BUS UNIT 单元中)已与内总线相连,用来显示内总线上的数据。

控制信号中除T4 为脉冲信号,其它均为电平信号。

由于实验电路中的时序信号均已连至“W/R UNIT”单元中的相应时序信号引出端,因此,需要将“W/R UNIT”单元中的T4 接至“STATE UNIT”单元中的微动开关KK2 的输出端。

计算机组成原理--实验报告

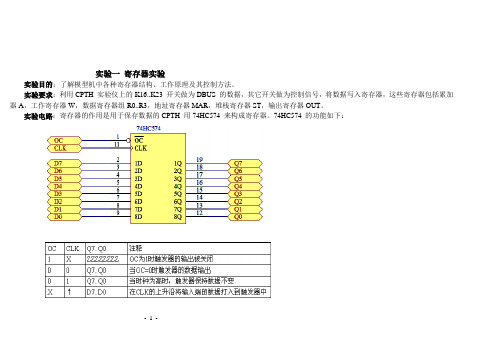

实验一寄存器实验实验目的:了解模型机中各种寄存器结构、工作原理及其控制方法。

实验要求:利用CPTH 实验仪上的K16..K23 开关做为DBUS 的数据,其它开关做为控制信号,将数据写入寄存器,这些寄存器包括累加器A,工作寄存器W,数据寄存器组R0..R3,地址寄存器MAR,堆栈寄存器ST,输出寄存器OUT。

实验电路:寄存器的作用是用于保存数据的CPTH 用74HC574 来构成寄存器。

74HC574 的功能如下:- 1 -实验1:A,W 寄存器实验原理图寄存器A原理图寄存器W 原理图连接线表:- 2 -系统清零和手动状态设定:K23-K16开关置零,按[RST]钮,按[TV/ME]键三次,进入"Hand......"手动状态。

在后面实验中实验模式为手动的操作方法不再详述.将55H写入A寄存器二进制开关K23-K16用于DBUS[7:0]的数据输入,置数据55H置控制信号为:按住STEP脉冲键,CK由高变低,这时寄存器A的黄色选择指示灯亮,表明选择A寄存器。

放开STEP键,CK由低变高,产生一个上升沿,数据55H被写入A寄存器。

将66H写入W寄存器二进制开关K23-K16用于DBUS[7:0]的数据输入,置数据66H- 3 -置控制信号为:按住STEP脉冲键,CK由高变低,这时寄存器W 的黄色选择指示灯亮,表明选择W寄存器。

放开STEP 键,CK 由低变高,产生一个上升沿,数据66H 被写入W 寄存器。

注意观察:1.数据是在放开STEP键后改变的,也就是CK的上升沿数据被打入。

2.WEN,AEN为高时,即使CK有上升沿,寄存器的数据也不会改变。

实验2:R0,R1,R2,R3 寄存器实验连接线表- 4 -将11H、22H、33H、44H写入R0、R1、R2、R3寄存器将二进制开关K23-K16,置数据分别为11H、22H、33H、44H置控制信号为:K11、K10为10,K1、k0分别为00、01、10、11并分别按住STEP 脉冲键,CK 由高变低,这时寄存器R0、R1\R2\R3 的黄色选择指示灯分别亮,放开STEP键,CK由低变高,产生一个上升沿,数据被写入寄存器。

计算机组成原理运算器实验

输入设备数据开关经一个三态门(74LS273)和数据总线相连。输出设备经一锁存器(74LS273)实现,盖锁存起的输入端和数据总线相连,输出端以二进制的形式输出结果。

实验电路如下图所示:

四.实验结果分析(含执行结果验证、输出显示信息、图形、调试过程中所遇的问题及处理方无进位)

CN=0(有进位)

0 0 0 0

F=/A

F=A

F=A加1

0 0 0 1

F=/(A+B)

F=(A+B)

F=(A+B)加1

0 0 1 0

F=(/A)B

F=A+/B

F=(A+/B)加1

0 0 1 1

F=0

F=负1(补码形式)

F=0

0 1 0 0

F=/(AB)

F=A加A(/B)

F=A加A/B加1

虽然这是计算机组成原理的第一个实验,但是经过老师的示范基本熟悉了整个实验系统的基本结构,了解了寄存器的添加和绘制,最重要的是通过实验掌握了运算器工作原理,熟悉了算术/逻辑运算的运算过程以及控制这种运算的方法。经过了这次实验的认真学习相信在下一次的实验中会更加顺利的。

运算数1,引脚3为最高位

B3 B2 B1 B0

运算数2,引脚3为最高位

Cn 最低位进位输入

Cn=0有进位,Cn=1无进位;

Cn+4本片产生的进位信号

Cn+4=0有进位,Cn+4=1无进位;

F3 F2 F1 F0

F3 F2 F1 F0运算结果,F3为最高位

(2)74LS181的A3 A2 A1 A0,B3 B2 B1 B0作为输入端口,分别输入二进制数值,然后用运算选择控制端口S3 S2 S1 S0来选择执行什么操作,通过改变控制端口的操作来观察输出结果的不同。

山东大学计算机组成原理课程设计实验报告

运算器结构如下图所示。R0、R1、R2 均为 D 触发器组成的八位寄存器,在打入 脉冲 CPRi 的作用下,接收数据输入端提供的信息送入 Ri 中。

μIR23-16 为微指令寄存器的高八位,可定义为操作数。进位信号 C0、打入脉冲 CPR0、CPR1、CPR2、M、S0、S1、S2、S3 均由微指令寄存器的 μIR8 和 μIR7--μIR0 产生。

算术逻辑运算单元 ALU 的设计

该部分中算术逻辑运算单元用两片 74LS181 芯片按如下图所示结构实现八位 组间串行进位运算器。

74LS181 功能表如下图所示。

5

计算机一班 鸿武 QQ:2420430689(2 号)

ALU 的实现电路图如下。

实验调试

将设计完成的电路图下载到 FPGA 中。按照前面所给的 74LS181 功能表编写 微指令,并写入到 ROM 中,微指令从 0 地址单元开始存放。

微程序控制的存储器读写系统设计............................................... 7 设计目的................................................................. 7 设计要求................................................................. 7 结构与信号索引........................................................... 8 微指令格式及微指令编制................................................... 8

微程序控制的运算器设计详细电路图 ........................................ 22 微程序控制的存储器读写系统设计详细电路图 ................................ 24 微程序设计模型机详细电路图.............................................. 25 硬布线控制的模型机详细电路图............................................ 34

计算机组原实验报告_加法器减法器

计算机科学与技术学院课程实验报告

课程名称:计算机组成原理年级:2014级上机日期:姓名:学号:班级:

实验名称:运算器组成实验教师:成绩:

File菜单中选择New项,将出现新建文件对话框,选择“BlockDiagram/Schematic File”项,点击ok。

双击右侧的主绘图区添加元器件,绘制一位全加器的电路图(如下图),绘制完成后,保存,重命名为fa,生成为fa. bdf的文件。

New项,将出现新建文件对话框,选择“BlockDiagram/Schematic ”项。

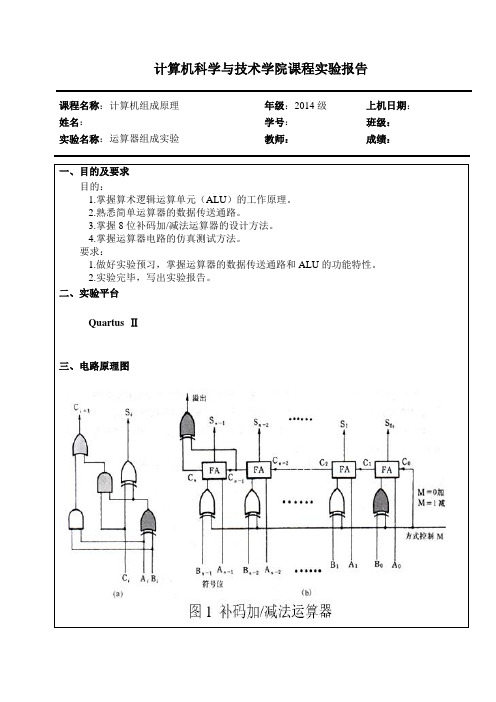

利用刚刚生成的元件绘制8位补码加/减法运算器的原理图。

8位补码加/减法运算器

6.绘制完成后,保存(必须与顶层文件同名),保存完成后,进行编译,编译成功(如下图)。

7.进行实验测试,(1)菜单栏中File选择New新建Other Files中“Vector Waveform File”文件,双及“name”下方空白部分,插入Node or Bus。

(2)Filt选择Pins:all,按start,将A,B,M,S,YC选中移到右边,完成后,自己设置数据。

计算机组成原理-运算器组成实验

南通大学计算机科学与技术学院上机实验报告

课程名称:计算机组成原理年级:上机日期:2014 姓名:学号: 班级:

实验名称:实验二运算器组成实验教师:成绩:

1.设计一个8位补码加/减法运算器

(1)参考图1,在QUARTUS II里输入原理图,设计一个8位补码加/减法运算器。

①一位二进制的加减法器电路图为:

③封装为芯片,设计8位二进制的加减法器,电路图如下

④创建波形文件,对该8位补码加/减法运算器进行功能仿真测试测试通过后,封装成一个芯片。

3.利用仿真波形,测试数据通路的正确性。

设定各控制信号的状态,完成下列操作,要求记录各控制信号的值及时序关系。

(1)在输入数据IN7~IN0上输入数据后,开启输入缓冲三态门,检查总线

时序关系表为:

检查方法,在DR1中存入55H,同时在DR2中存入00H,检测总线输出的数即为存入的数据,波形图如下:

时序关系表为:

方法与上相同,在DR1中存入55H,同时在DR2中存入00H,检测总线输出的数即为存入的数据,波形图如下:

时序关系表为:

(4)完成加法运算,求55H+AAH,检查运算结果是否正确,请说明检查方法。

波形图如下:

(5)完成减法运算,分别求55H-AAH和AAH-55H,检查运算结果是否正确,请说明检查方法。

①计算AA-55,波形图如下:

时序图如下:

②计算

(6)求12H+34H-56H ,将结果存入寄存器R0,检查运算结果是否正确,同时检查数据是否存入,请说明检查方法。

①首先计算结果,波形图,时序图如下:

②检查结果的保存,则把结果存入LDR1,把00H 存入LDR2,通过与0的相加,输出结果就可确定数据已存入。

计算机组成原理实验实验一运算器实验(一)算术逻辑运算实验一

计算机组成原理实验实验一运算器实验(一)算术逻辑运算实验一、实验目的1、掌握简单运算器的数据传送通路。

2、验证运算功能发生器(74LS181)的组合功能。

二、实验原理1、实验中所用的运算器数据通路图1所示。

三、实验步骤1、用二进制数码开关向DR1和DR2寄存器置数。

具体操作步骤图2所示。

2、验证74LS181的算术运算和逻辑运算功能(二) 进位控制实验一、实验目的1、验证带进位控制算术运算功能发生器的功能。

2、按指定数据完成几种算术运算。

二、实验原理实验原理图如图3所示。

三、实验步骤1、用二进制数码开关向DR1和DR2寄存器置数向DR1存入01010101,向DR2存入10101010。

具体操作步骤图4所示。

图2图3 进位控制实验原理图2、进位标志清零S3 S2 S1 S0 M 的状态置为00000,AR 状态置为0,按动微动开关KK2。

进位标志指示灯CY 亮时表示无进位,进位标志为“0” ;指示灯CY 灭时表示有进位,进位标志为“1”。

3、验证带进位运算及进位锁存功能时,使Cn=1, Ar=0, SW-B=1。

T4脉冲到来时,将本次运算的进位结果锁存到进位锁存器中。

注意观察进位标志显示灯CY 。

(三) 移位运算实验一、实验目的验证移位运算控制的组合功能。

二、实验原理移位运算实验原理图如图5所示, 74LS299功能表如表1所示图4表1 74LS299功能表三、实验步骤1、移位操作:(1)置数,具体步骤如图6所示。

2、移位,参照功能表改变S0 S1 T4 299-B 的状态,按动微动开关KK2,观察移位的结果。

实验二 存储器实验一、实验目的掌握静态随机存储器的工作特性及数据的读写方法。

二、实验原理图5 移位运算实验原理图图6实验所用的静态存储器电路原理图如图7所示。

三、实验步骤1、写操作。

给存储器的00、01、02、03、04地址单元中分别写入数据11、12、13、14、15,具体操作步骤图8所示(以向0号单元写入数据11为例)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

计算机专业类课程

实

验

报

告

课程名称:计算机组成原理

学 院:信息与软件工程学院

专 业:软件工程

学生姓名:

学 号:

指导教师:

日 期: 2012 年 12 月 15 日

ﻬ

电 子 科 技 大 学

实 验 报 告

一、实验名称: 8位算术逻辑运算实验

二、实验学时:2

三、实验内容、目得与实验原理:

实验目得:

1、掌握算术逻辑运算器单元ALU(74LS181) 得工作原理。

2、掌握模型机运算器得数据传送通路组成原理。

3、验证74LS181得组合功能。

4、按给定数据,完成实验指导书中得算术/逻辑运算。

实验内容:

使用模型机运算器,置入两个数据DR1=35,DR2=48,改变运算器

得功能设定,观察运算器得输出,记录到实验表格中,将实验结果对比分

析,得出结论。

实验原理:

1. 运算器由两片74LS181以并/串形式构成8位字长得ALU。

2. 运算器得输出经过一个三态门(74LS245)与数据总线相连.

3. 运算器得两个数据输入端分别由两个锁存器(74LS273)锁存.

4. 锁存器得输入连至数据总线,数据开关(INPUT DEVICE)用来给

出参与运算得数据,并经过一三态门(74LS245)与数据总线相连.

5. 数据显示灯(BUS UNIT)已与数据总线相连,用来显示数据总线内

容。

实验器材(设备、元器件):模型机运算器

四、实验步骤:

1、 仔细查瞧试验箱,按以下步骤连线

1)ALUBUS连EXJ3

2) ALU01连BUS1

3) SJ2连UJ2

4) 跳线器J23上T4连SD

5) LDDR1,LDDR2,ALUB,SWB四个跳线器拨在左边

6) AR跳线器拨在左边,同时开关AR拨在“1”电平

2、 核对线路,核对正确后接通电源

3、 用二进制数据开关KD0—KD7向DR1与DR2寄存器置入8位运算

数据。

① 调拨8位数据开关KD0-KD7为01100101(35H) ,准备向

DR1送二进制数据。

② 数据输出三态缓冲器门控信号ALUB=1(关闭)。

③ 数据输入三态缓冲器门控信号 SWB=0(打开)。

④ 数据锁存DRi控制信号LDDR1=1(打开),同时,LDDR2=0(关

闭).

⑤ 打入脉冲信号T4 ,将数据65H置入DR1。

重复步骤1—5,同理将数据A7H置入DR2

4、 检验DR1与DR2置入得数据就是否正确。

1) 数据输出三态缓冲器门控信号ALUB=0(打开);

2) 数据输入三态缓冲器门控信号SWB=1(关闭);

3) 数据锁存DRi控制信号LDDR1、LDDR2=0(关闭)

4) 设置开关M 、开关S3、S2、S1、S0 相应值

如M=1,S3、S2、S1、S0=1111,验证8位数据 DR1;S3、S2、S1、

S0=1010验证8位数据DR2

5. 验证74LS181得算术与逻辑运算功能。

1)在给定DR1=65、DR2=A7得情况下,改变算术逻辑运算功能发

生器得功能设置,观察运算器得输出。

2)将输出结果填入实验报告表中,并与理论分析进行比较、验证。

6. 填写实验数据.

五、实验数据及结果分析(包括各种截图:实验过程截图、界面截图、操作截

图、运算结果截图):

运算器数据通路图:

模型机运算器连线及跳线完毕图:

实验数据输出表:

六、实验结论、心得体会与改进建议:

通过这次试验,掌握了算术逻辑运算器单元ALU(74LS181)得工作

原理,,掌握了简单运算器得数据传送通道,了解了由74LS181等组合逻

辑电路得运算功能发生器运算功能,能够按给定数据,完成实验指定得算术

/逻辑运算。