淀积氮化硅光刻

CMOS工艺流程与MOS电路版图举例资料

P阱

N阱

推阱

– 退火驱入,双阱深度约1.8μm – 去掉N阱区的氧化层

43

形成场隔离区

– 生长一层薄氧化层 – 淀积一层氮化硅

– 光刻2场隔离区,非隔离区被光刻胶保护起来

– – – –

反应离子刻蚀氮化硅 场区硼离子注入以防止场开启 热生长厚的场氧化层 去掉氮化硅层

44

光刻胶

31P+

11B+

合金 形成钝化层

– 在低温条件下(小于300℃)淀积氮化硅 – 光刻11,钝化版 – 刻蚀氮化硅,形成钝化图形

测试、封装,完成集成电路的制造工艺 CMOS集成电路采用(100)晶向的硅材料

53

4) 图解双阱硅栅 CMOS制作流程

54

首先进行表面清洗,去除wafer 表面的保护层和 杂质,三氧化二铝 必须以高速粒子撞击,并 用化学溶 液进行清洗。

47

形成N管源漏区

– 光刻6,利用光刻胶将PMOS区保护起来 – 离子注入磷或砷,形成N管源漏区

形成P管源漏区

– 光刻7,利用光刻胶将NMOS区保护起来 – 离子注入硼,形成P管源漏区

48

形成接触孔

– 化学气相淀积BPTEOS硼磷硅玻璃层 – 退火和致密 – 光刻8,接触孔版 – 反应离子刻蚀磷硅玻璃,形成接触孔

Top View

Cross-Section

82

A Complete CMOS Inverter

阈值电压调整注入 光刻3,VTP调整注入 光刻4,VTN调整注入

45

P阱

N阱

形成多晶硅栅(栅定义)

– 生长栅氧化层 – 淀积多晶硅 – 光刻5, 刻蚀多晶硅栅

46

形成硅化物

CMOS工艺流程版图剖面

P sub. 〈100〉

形成N阱

– 初始氧化,形成缓冲层,淀积氮化硅层

– 光刻1,定义出N阱

– 反应离子刻蚀氮化硅层 – N阱离子注入,先注磷31P+ ,后注砷75As+

41

N阱 P sub. 〈100〉

形成P阱

– 在N阱区生长厚氧化层,其它区域被氮化硅层 保护而不会被氧化 – 去掉光刻胶及氮化硅层 – P阱离子注入,注硼

70

71

2. 典型P阱CMOS工艺的剖面图

硅栅 漏 薄氧化层

源

金属 低氧

场氧化层 (FOX)

n-衬底

p-阱

72

CMOS process

p+

p+

p-

73

Process (Inverter)p-sub

In

GND

S G D

VDD

D G S

图例

Legend of each layer

N-well P-diffusion N-diffusion

49

形成第一层金属

– 淀积金属钨(W),形成钨塞

50

形成第一层金属

– 淀积金属层,如Al-Si、Al-Si-Cu合金等 – 光刻9,第一层金属版,定义出连线图形 – 反应离子刻蚀金属层,形成互连图形

51

正硅酸乙脂(TEOS)分解 650~750℃

形成穿通接触孔 – 化学气相淀积PETEOS, 等离子增强正硅酸四乙酯热分解 Plasma Enhanced TEOS :tetraethylorthosilicate [Si(OC2H5)4] -- 通过化学机械抛光进行平坦化 – 光刻穿通接触孔版 – 反应离子刻蚀绝缘层,形成穿通接触孔 形成第二层金属 – 淀积金属层,如Al-Si、Al-Si-Cu合金等 52 – 光刻10,第二层金属版,定义出连线图形

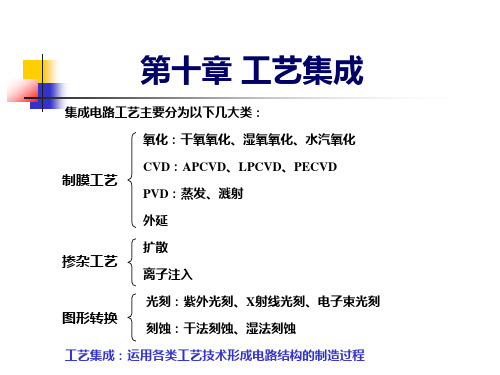

硅集成电路工艺基础10

4、自对准结构和接触

自对准技术是利用单一掩模版在硅片上形成多层自对准结构的技术, 不仅工艺简化,且消除了多块掩模版之间的对准容差。随着器件特征 尺寸的不断缩小,自对准技术已经成为一种常用的工艺方法。 最早发展起来和最常用的自对准技术是源漏的自对准注入(也称为 硅栅自对准),即在多晶硅栅的掩蔽下自对准地进行源漏区的杂质注 入,并同时完成多晶硅栅的杂质注入。 自对准的多晶硅栅避免了采用铝栅时多次光刻引起的栅极错位。

法在上面淀积一层SiO2。 各向异性腐蚀CVD SiO2层以后,只剩下侧墙部分。 在SiO2侧墙保护下腐蚀Si3N4和SiO2层直至露出硅,然后 再去除CVD SiO2侧墙 ,形成由Si3N4和SiO2层包围的平台。 进行沟道阻挡层注入和场SiO2层生长。 最后去除Si3N4和缓冲SiO2层。

10.1、集成电路中的隔离

10.1.1 MOS集成电路中的隔离 自隔离:MOSFET源、漏极的导电类型相同,并与衬底导电类型相反,

所以MOSFET本身就被pn结隔离,即自隔离(self-isolated)。 源漏电流只有在导电沟道形成后才能形成,只要相邻晶体管之间不存在 导电沟道,相邻晶体管间便不会存在显著的电流。 只要维持源-衬底pn结和漏-衬底pn结的反偏,MOSFET便能维持自隔离。 MOS集成电路的晶体管之间不需要pn结隔离,可大大提高集成度。

达到在硅片上选择性保留厚氧化层的目的。

10.1.2 双极集成电路中的隔离

在传统的双极集成电路中的隔离主要是采用结隔离,结隔离已经成为 双极集成电路的标准埋收集极工艺的重要组成部分。

在外延层上淀积SiO2并进行光刻和刻蚀,去除光刻胶露出隔离区上的Si, 随后进行硼扩散,形成p型隔离区。在硅衬底上形成了许多由反偏p-n结隔 离开的孤立的外延岛。 由于需要扩透整个n型层,因此硼的隔离扩散是双极工艺中最费时的。

浅谈现代集成电路28nm芯片制造工艺A(前端FEOL)

浅谈现代集成电路28nm芯片制造工艺A(前端FEOL) 全球90%以上集成电路都是CMOS工艺制造的,经历了半个多世纪发展进化,芯片集成度从一个芯片包含几十个器件进化到几十亿个器件。

从上世纪60年代MOS器件采用铝栅工艺,70年代采用了硅栅工艺,铝线互连,进化到现代集成电路采用高K金属栅、超低k介质多层铜线互连,以及FD-SOI和FinFET立体结构。

制造工艺也越来越复杂。

下面就纳米级体硅平面型CMOS集成电路工艺流程,展现芯片先进制程不断丰富现代集成电路制造工艺。

1)现将几种先进制程工艺简介如下:50多年发展,集成电路制造过程工艺越来越复杂,先进制程不断完善。

首先为了抑制短沟道效应,提高栅极对沟道的控制能力,提高栅极电容,栅氧化层厚度不断减薄。

对于厚度大于4nm的栅氧化层,SiO2是理想的绝缘体,不会形成栅漏电流。

当纯二氧化硅厚度小于3nm时,衬底的电子以量子形式穿过栅介质进入栅极,形成栅极漏电流。

(量子隧穿)栅极漏电导致功耗增加,IC 发热且阈值电压飘移,可靠性降低。

为提高介质绝缘特性,当特征尺寸达到0.18μm时采用氮氧化硅代替二氧化硅。

特征尺寸进入90nm节点,单纯缩小厚度不能满足器件性能的要求了,于是采用提高氮氧化硅含氮量以增加介电常数k,但SiON厚度低于14Å会严重遂穿,栅极漏电剧增。

45nm节点之后氮氧化硅已经不能满足mos器件正常工作的要求,开始使用高k介质HfO2代替SiON来改善栅极漏电问题,同时采用金属栅解决费米能级钉扎和多晶硅栅耗尽问题。

尽管在0.35μm技术节点开始采用掺杂多晶硅与金属硅化物(WSi)鈷(镍)多晶硅化物栅叠层代替多晶硅栅,降低了多晶硅栅的电阻。

但金属栅电阻要比金属硅化物还要小。

高k金属栅HKMG.采用高k介质材料替代SiO2。

二氧化硅k=3.9,氮氧化硅k=4~7,高K介质(HfO2和,HfSiON)=15~25。

同样等效氧化层厚度时,高k材料的物理厚度是SiO2的3~6倍。

PECVD淀积氮化硅薄膜性质研究

第25卷第3期2004年6月太阳能学报A(汀AENERGIAES()IARISSINICAVd.25.No.3July,2004文章编号:0254.O眇6f2004)03一0341.鹏PECVD淀积氮化硅薄膜性质研究王晓泉,汪雷,席珍强,徐进,崔(浙江大学硅材料国家重点实验室,杭州310027)灿,杨德仁摘要:使用等离子体增强化学气相沉积(PlasrIlaEnhancedCh鲫icalvapor决p商tion,P壬x:vD)在P型硅片上沉积了氮化硅(siNx)薄膜,使用薄膜测试仪观察了薄膜的厚度、折射率和反射光谱,利用扫描电子显微镜(sEM),原子力显微镜(越、M)观察了截面和表面形貌,使用傅立叶变换红外光谱仪(FTIR)和能谱仪(EI)x)分析了薄膜的化学结构和成分。

最后,考察了薄膜在经过快速热处理过程后的热稳定性,并利用霍尔参数测试仪(}h11)比较了薄膜沉积前后载流子迁移率的变化。

关键词:太阳电池;Hm;氮化硅中图分类号:n(511+.4文献标识码:A0引言由于有着良好的绝缘性,致密性,稳定性和对杂质离子的掩蔽能力,氮化硅薄膜作为一种高效器件表面的钝化层已被广泛应用在半导体工艺中。

人们同时发现,在多晶硅太阳电池表面生长高质量氮化硅薄膜不仅可以十分显著地提高多晶硅太阳电池的转换效率,而且还可以降低生产成本。

这是因为作为一种减反射膜,氮化硅不仅有着极好的光学性能(A=632.8m时折射率在1.8~2.5之间,而最理想的封装太阳电池减反射膜折射率在2.1~2.25之间)和化学性能,还能对质量较差的硅片起到表面和体内钝化作用,提高电池的短路电流。

因此,采用氮化硅薄膜作为晶体硅太阳电池的减反射膜已经成为光伏界的研究热点【卜3l。

1996年,Kyocera公司通过生长氮化硅薄膜作为太阳电池的减反射膜和钝化膜在15cm×15cm的多晶硅太阳电池上达到了17.1%的转换效率L41;A.HuKbner等人利用氮化硅钝化双面太阳电池的背表面使电池效率超过了20%【5J。

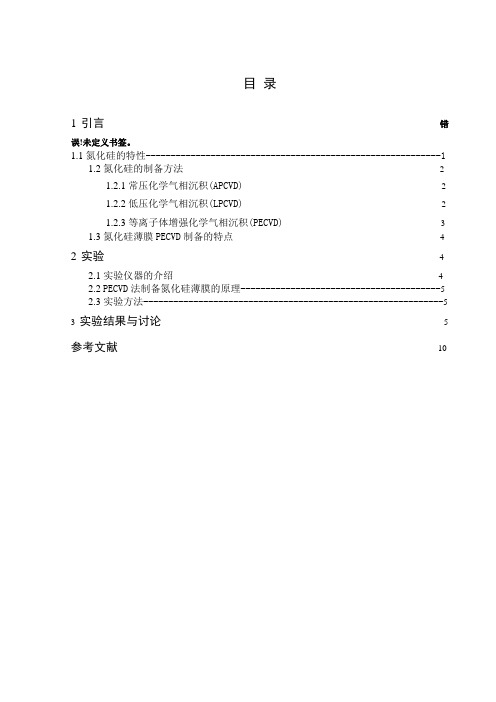

氮化硅薄膜材料的PECVD制备及其光学性质研究

目录1引言-------------------------------------------------------------------------------------------------------------------错误!未定义书签。

1.1氮化硅的特性-----------------------------------------------------------11.2氮化硅的制备方法----------------------------------------------------------------------------------------21.2.1常压化学气相沉积(APCVD)--------------------------------------------------------------------21.2.2低压化学气相沉积(LPCVD)--------------------------------------------------------------------21.2.3等离子体增强化学气相沉积(PECVD)------------------------------------------------------31.3氮化硅薄膜PECVD制备的特点-----------------------------------------------------------------------4 2实验-------------------------------------------------------------------------------------------------------------------42.1实验仪器的介绍-------------------------------------------------------------------------------------------42.2PECVD法制备氮化硅薄膜的原理----------------------------------------52.3实验方法------------------------------------------------------------53 实验结果与讨论-------------------------------------------------------------------------------------------------5 参考文献--------------------------------------------------------------------------------------------------------------10氮化硅薄膜材料的PECVD制备及其光学性质研究摘要:等离子增强型化学气相沉积(Plasma Enhanced Chemical Vapor Deposition , PECVD)是目前较为理想和重要的氮化硅薄膜制备方法,本文详细探讨了对氮化硅薄膜PECVD制备的方法、原理以及制备过程,成功生长了质量较好的氮化硅薄膜,并用紫外-可见光光谱仪研究了沉积薄膜的表面形貌及其光学带隙,得出氮化硅薄膜相关的光学特性,结果表明,氮气流量对薄膜的光学带隙影响较大,制备的薄膜主要为富硅氮化硅薄膜。

CMOS工艺流程.版图.剖面

– 离子注入硼,形成P管源漏区

精选课件

48

形成接触孔

– 化学气相淀积BPTEOS硼磷硅玻璃层 – 退火和致密 – 光刻8,接触孔版 – 反应离子刻蚀磷硅玻璃,形成接触孔

精选课件

49

形成第一层金属

– 淀积金属钨(W),形成钨塞

精选课件

50

形成第一层金属

– 淀积金属层,如Al-Si、Al-Si-Cu合金等 – 光刻9,第一层金属版,定义出连线图形 – 反应离子刻蚀金属层,形成互连图形

精选课件

1

1) 简化N阱CMOS 工艺演示

精选课件

2

氧化层生长

氧化层 P-SUB

光刻1,刻N阱掩膜版

精选课件

3

掩膜版

曝光

光刻胶 光刻1,刻N阱掩膜版

精选课件

4

氧化层的刻蚀

光刻1,刻N阱掩膜版

精选课件

5

N阱注入

光刻1,刻N阱掩膜版

精选课件

6

形成N阱

N阱 P-SUB

精选课件

7

氮化硅的刻蚀

二氧化硅

磷31P+

–砷75As+

P sub. 〈100〉

形成N阱

– 初始氧化,形成缓冲层,淀积氮化硅层

– 光刻1,定义出N阱

– 反应离子刻蚀氮化硅层

– N阱离子注入,先注磷31P+ ,后注砷75As+

精选课件

41

N阱 P sub. 〈100〉

形成P阱

– 在N阱区生长厚氧化层,其它区域被氮化硅层 保护而不会被氧化

精选课件

25

Si3N4淀积

Si3N4

N阱

P-Si SUB

缓冲用SiO2

MEMS工艺(5表面硅加工技术)

表面微加工

表面微加工技术主要靠在基底上逐 层添加材料而构造微结构

表面微加工器件是由三种典型的部 件组成:⑴牺牲层;⑵微结构层; ⑶绝缘层部分

基本概念

在微机械加工中,通常将两层薄膜中的下 面一层腐蚀掉,只保留上面的一层,这种 技术称为牺牲层腐蚀,又称为分离层腐蚀。 利用牺牲层腐蚀技术直接在衬底表面制作 微机械元件结构的技术被称为“硅表面微 机械加工技术”。

不同淀积方法生成的二氧化硅性质表

。)

PECVD 200℃ SiO1。9(H) 可变(Adams 说 不一致) 失氢 2.3 1.47 300(压)到300 (拉) 3到6

淀积类型 典型温度 成分 台阶覆盖率 热稳定性 密度(g/cm3) 折射率 应力(Mpa) 电介质强度 (106V/cm或 102V/μm) 腐蚀速率 (nm/min)(H2O: HF=100:1)

多晶硅材料的主要特点 (2)多晶硅薄膜对生长衬底的选择不 苛刻。衬底只要有一定的硬度、平整度 及能耐受住生长工艺温度即可。 (3)可以通过对生长条件及后工艺的 控制来调整多晶硅薄膜的电阻率,使它 成为绝缘体、导体或半导体,从而适应 不同器件或器件不同部分的需要。

多晶硅材料的主要特点

(4)多晶硅薄膜作为半导体材料 可以像单晶硅那样通过生长、扩散 或离子注入进行掺杂,形成N型或 P型半导体,制成p-n结;可以采用 硅平面工艺进行氧化、光刻、腐蚀 等加工。

二氧化硅当然是硅加工实验室中最常用的 介质。它可以自身生长,也可以淀积,有 无掺杂剂都行,既使掺杂后仍然绝缘。

热生长型SiO2常用作MOS门绝缘层。如 果淀积的SiO2 中掺入磷,那就叫做磷硅 玻璃、“P玻璃”或PSG,它常用作最终 钝化层;

如果掺入硼,那就叫做硼硅玻璃或BSG;如 果在玻璃中掺入磷和硼的混合物,则常称为 BPSG或低温氧化物(LTO),它具有良好 的低温回流特性,可使高深宽比表面结构 “光洁化”或平面化。 在IC工艺中,SiO2是一种多用途的基本材料, 它通过热氧化生长和为满足不同要求采用不 同工艺淀积获得。