基于VHDL的相位计设计开题报告

基于VHDL的频率计设计本科毕业设计

JIU JIANG UNIVERSITY毕业论文(设计)题目基于VHDL的频率计设计英文题目 The frequency meter based on VHDL design 院系电子工程学院专业电子信息工程九江学院学士学位论文摘要数字频率计是直接用十进制数字来显示被测信号频率的一种测量装置。

它不仅可以测量正弦波、方波、三角波、尖脉冲信号,而且还可以测量它们的周期。

经过改装,可以测量脉冲宽度,做成数字式脉宽测量仪;在电路中增加传感器,还可以做成数字脉搏仪、计价器等。

因此数字频率计在测量物理量方面应用广泛。

本设计用VHDL在CPLD器件上实现数字频率计测频系统,能够用十进制数码显示被测信号的频率,而且还能对其他多种物理量进行测量。

具有体积小、可靠性高、功耗低的特点。

采用VDHL编程设计实现的数字频率计,除被测信号的整形部分、键输入部分和数码显示部分以外,其余全部在一片FPGA芯片上实现,整个系统非常精简,而且具有灵活的现场可更改性。

关键字:VHDL语言;频率计;FPGA基于VHDL的频率计设计The frequency meter based on VHDL designAbstractDigital frequency meter is directly with a decimal number to display the measured signal frequency of a measuring device. It not only can measure the sine wave, square wave, triangle wave, pulse signal, but also can measure their cycle. Modified, and can measure pulse width, into a digital pulse width measuring instrument; Add the sensors in the circuit, but also can be made into digital pulse apparatus, meter, etc. So the digital frequency meter has been widely applied in measuring physical quantities. This design with VHDL on the CPLD device to realize digital frequency meter frequency measurement and control system, can use decimal digital display measured signal frequency, but also to measure a variety of other physical quantities. With the characteristics of small volume, high reliability, low power consumption. VDHL programming design was adopted to realize digital frequency meter, in addition to the measured signal of the plastic part and digital display, key input parts, all on a FPGA chip, the whole system is very compact, and with flexible field is modified.Key Words:VHDL language; Frequency meter; FPGA九江学院学士学位论文目录摘要 (I)The frequency meter based on VHDL design (II)Abstract (II)第一章绪论 (1)1.1课题的研究背景 (1)1.2频率计发展现状 (1)第2章数字频率计的要求 (3)2.1 主要技术指标 (3)2.2 课题的研究内容 (3)第3章数字频率计的方案设计 (4)3.1 基本原理 (4)3.1.1 频率计测量频率的设计原理 (4)3.1.2频率计测量频率的原理图 (4)3.2 设计流程图 (5)第4章数字频率计各模块功能介绍 (6)4.1频率控制模块的VHDL语言源程序 (6)4.1.1 频率控制模块的程序如下: (6)4.1.2 频率控制模块CNT12 (7)4.2十进制加法计数器CNT10的VHDL语言源程序 (7)4.2.1 十进制计数器的程序 (7)4.2.2 十进制计数器的顶层设计 (9)4.3系统模块的VHDL语言源程序 (9)4.3.1系统模块的设计 (9)4.3.2 系统模块的程序 (9)4.4 锁存器LOCK的VHDL语言源程序 (13)4.4.1 锁存器LOCK的程序 (13)4.4.2 锁存器LOCK顶层设计图 (14)4.5 译码模块DECODER的VHDL语言源程序 (15)4.5.1 译码模块DECODER的程序 (15)4.6四选一选择器MUX41的VHDL语言源程序 (16)4.6.1 MUX41程序 (16)4.7 四进制计数器CNT4的VHDL语言源程序 (17)基于VHDL的频率计设计4.7.1 四进制计数器CNT4的程序 (17)4.7.2 四进制计数器CNT4 (17)4.8 250分频器的VHDL语言源程序 (18)4.8.1 250分频器的程序 (18)4.8.2 250分频器 (18)九江学院学士学位论文第一章绪论在科技高度发展的今天,集成电路和计算机应用得到了高速发展。

基于VHDL的等精度频率计设计—毕业设计论文

摘要基于传统测频原理的频率计的测量精度将随被测信号频率的下降而降低,在实用中有较大的局限性,本设计采用单片机AT89C51作为主要的控制单元,用来完成电路的信号测试控制、数据运算处理、键盘扫描和控制数码管显示等功能,待测信号经过LM358放大后又经过74HC14形成系统需要的矩形波,然后送入复杂可编程逻辑器件(CPLD),最后由可编程逻辑器件CPLD进行各种时序控制及计数测频功能,并用8位8段LED进行显示。

关键词单片机可编程逻辑器件频率计AbstractBased on the traditional principle of measuring the frequency of the frequency of measurement accuracy will be tested with thefrequency and reduce the decline in the more practical limitations.SCM AT89C51 use this design as the main control unit, the signals used to complete the circuit test control, data processing, keyboard scanning and digital control of the show, and other functions, under test signal LM358 Larger then after a 74 HC14 system needs Rectangular waves, and then into the complex programmable logic devices (CPLD), programmable logic devices by the end CPLD various control and timing count frequency measurement functions, and with eight 8 of the LED display.Keywords: SCMC CPLD Cymometer目录1 引言 (1)1.1课题分析 (1)1.2等精度频率计在国内外发展概况 (1)1.3M AX+P LUS II简介及VHDL语言简介 (3)1.4课题要求 (6)2 等精度频率计的方案选择及原理分析 (7)2.1等精度频率计测频原理 (7)2.2系统原理框图 (9)2.3周期测量 (9)2.4脉冲宽度测量 (10)2.5周期脉冲信号占空比的测量 (10)3 等精度频率计硬件设计 (11)3.1键盘控制模块 (11)3.2显示模块 (12)3.3主控模块 (13)3.4信号输入放大和整形模块 (16)3.5音频输出电路 (17)3.6CPLD功能模块描述 (18)4 等精度频率计软件设计方案 (19)4.1VHDL语言 (19)4.2VHDL软件设计方案 (21)4.3所需VHDL文件及波形仿真结果 (22)4.4单片机的汇编语言编程 (24)5 电路系统调试 (28)6 结论 (29)致谢 (33)附录一:元器件清单 (34)附录二:程序清单 (36)附录三:原理图 (36)1 引言1.1 课题分析在现代电子系统中,数字系统所占的比例越来越大。

VHDL八位数码管频率计课程设计

5、时钟源。

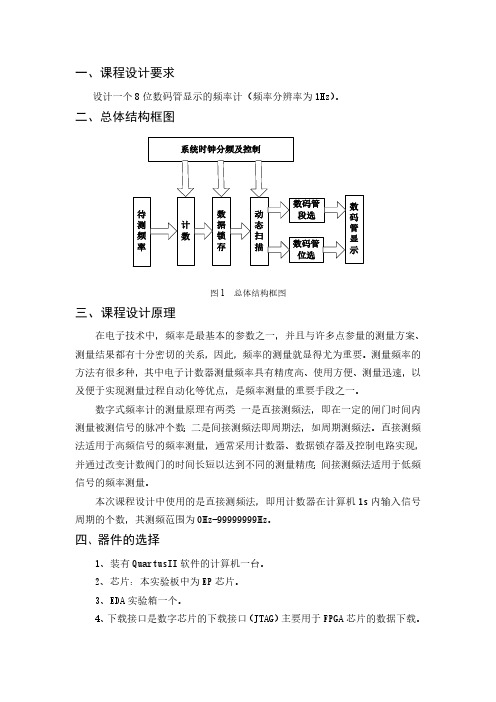

五、功能模块和信号仿真图以及源程序(1) 系统时钟分频及控制的功能模块图及其源程序图2 功能模块图作用:将试验箱上的50MHz的晶振分频,输出CLOCK为数码管提供1kHz的动态扫描频率。

CNT_EN输出为0.05s的信号,对频率计中的32位十进制计数器CNT10的ENA使能端进行同步控制,当TSTEN高电平时允许计数,低电平时停止计数,并保持其所计的脉冲数。

在停止计数期间,首先需要一个锁存信号LOAD的上跳沿将计数器在前一秒的计数值锁存进锁存器REG32B中,并由外部的十进制7段数码管显示计数值。

设置锁存器的好处是数据显示稳定,不会由于周期性的清零信号而不断闪烁。

锁存信号后,必须有一个清零信号RST_CNT对计数器进行清零,为下一秒的计数操作做准备。

该模块的信号仿真图如下:图3 仿真波形图源程序如下:--分频library ieee;use ieee.std_logic_1164.all;entity fdivwangzheng isport(clk0:in std_logic; --输入系统时钟clk1:out std_logic; --输出1hz时钟信号clk2:out std_logic); --输出显示扫描时钟信号end fdivwangzheng;architecture a of fdivwangzheng isbeginp1:process(clk0)variable cnt:integer range 0 to 49999999; --分频系数为24999999variable ff:std_logic;beginif clk0'event and clk0='1' thenif cnt<49999999 thencnt:=cnt+1;elsecnt:=0;ff:=not ff; --反向end if;end if;clk1<=ff;end process p1;p2:process(clk0)variable cnn:integer range 0 to 999; --分频系数为499variable dd:std_logic;beginif clk0'event and clk0='1' thenif cnn<999 thencnn:=cnn+1;elsecnn:=0;dd:=not dd; --反向end if;end if;clk2<=dd;end process p2;end a;--测频控制器(testctl.vhd)LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY TESTCTLwanzheng ISPORT ( CLKK : IN STD_LOGIC; -- 1HzCNT_EN,RST_CNT,LOAD : OUT STD_LOGIC);END TESTCTLwanzheng;ARCHITECTURE behav OF TESTCTLwanzheng ISSIGNAL DIV2CLK : STD_LOGIC;BEGINPROCESS( CLKK )BEGINIF CLKK'EVENT AND CLKK = '1' THEN DIV2CLK <= NOT DIV2CLK;END IF;END PROCESS;PROCESS (CLKK, DIV2CLK)BEGINIF CLKK='0' AND Div2CLK='0' THEN RST_CNT <= '1';ELSE RST_CNT <= '0'; END IF;END PROCESS;LOAD <= NOT DIV2CLK ; CNT_EN <= DIV2CLK;END behav;(2) 十进制计数器的功能模块图及其源程序图4 功能模块图作用:当使能端为高电平,清零端为低电平时,实现十进制计数功能。

基于VHDL的数字显示频率计的设计

EDA 课程设计报告书课题名称 基于VHDL 的数字显示频率计的设计 姓 名 学 号 院 系 专 业 指导教师※※※※※※※※※ ※※ ※※ ※※EDA 课程设计基于VHDL的数字显示频率计的设计1设计目的通过EDA的试验设计,加深我们对FPGA的了解,熟悉FPGA的工作原理和试验环境,知道FPGA的开发流程,熟悉各种软件如Quartus II 6.0的使用。

通过设计小型试验项目学会仿真和硬件测试的基本方法。

2设计的主要内容和要求在电子技术中,频率是最基本的参数之一,并且与许多电参量的测量方案、测量结果都有十分密切的关系,因此频率的测量就显得更加重要。

通过运用VHDL语言,实现4位数字频率计,并利用Quartus II 6.0集成开发环境进行编辑、综合、波形仿真,并下载到FPGA器件中,经实际电路测试,该系统性能可靠。

3 整体设计方案3.1四位十进制数据显示频率计设计在电子技术中,频率是最基本的参数之一,并且与许多电参量的测量方案、测量结果都有十分密切的关系,因此,频率的测量就显得更为重要。

测量频率的方法有多种,其中电子计数器测量频率具有精度高、使用方便、测量迅速,以及便于实现测量过程自动化等优点,是频率测量的重要手段之一。

数字式频率计的测量原理有两类:一是直接测频法,即在一定闸门时间内测量被测信号的脉冲个数;二是间接测频法即测周期法,如周期测频法。

直接测频法适用于高频信号的频率测量,通常采用计数器、数据锁存器及控制电路实现,并通过改变计数器阀门的时间长短在达到不同的测量精度;间接测频法适用于低频信号的频率测量,本设计中使用的就是直接测频法,即用计数器在计算1S内输入信号周期的个数。

数字频率计是数字电路中的一个典型应用,实际的硬件设计用到的器件较多,连线比较复杂,而且会产生比较大的延时,造成测量误差、可靠性差。

随着现场可编程门阵列FPGA的广泛应用,以EDA工具作为开发手段,运用VHDL等硬件描述语言,将使整个系统大大简化,提高了系统的整体性能和可靠性。

VHDL实验报告与代码毕业设计(论文)

实验一. 分频器设计一.实验目的1.熟悉QUARTUSII 软件的使用2.熟悉PLD设计流程3. 学习分频器的设计二.实验内容设计一个最大分频为225的分频器,将50MHz时钟作为输入三.实验框图四.管脚设定CLOCK_50 PIN_N2LEDR[0] PIN_AE23五.实验代码LIBRARY ieee;USE ieee.std_logic_1164.all;USE ieee.std_logic_UNSIGNED.all;ENTITY clk1 ISPORT(clk:IN STD_LOGIC;DIGIT:OUT STD_LOGIC);END clk1;ARCHITECTURE clk1 OF clk1 ISBEGINCOUNT: PROCESS(clk)V ARIABLE temp:STD_LOGIC_VECTOR(25 DOWNTO 0);BEGINIF(clk'EVENT AND clk = '1')THENtemp := temp+1;IF(temp(25)='1') THENtemp:=(OTHERS=>'0');END IF;END IF;DIGIT <= temp(24);END PROCESS count;END clk1;六.心得体会通过这次实验,我初步掌握了QUARTUSII 软件的使用,为今后的实验打下基础。

实验二. VHDL描述风格比较一.实验目的1.深入体会VHDL三种描述风格的区别2. 学习3输入表决器,异或门的实现3.设计一个5输入表决器。

二.实验内容以3输入表决器,异或门,通用寄存器等代码为例,深入体会VHDL描述风格。

1.学习已给的3输入表决器代码,完成3输入表决器的三种描述方式的验证比较。

在QUARTUS II中对程序进行编译,下载,验证。

使用拔码开关SW0,SW1,SW2作为三个输入,输出在LEDR0表示,亮表示‘1’,不亮表示‘0’2.学习已给的异或门代码,完成异或门的三种描述方式的验证比较。

基于VHDL语言的数字钟设计开题报告

吕梁学院2016届毕业论文(设计)开题报告

(学生用表)

11

2)具备的实验条件:FPGA开发板,Quartusll开发坏境

7•参考文献:

[1] 高锐•基于FPGA的数字钟电路设计[J].中国制造业信息化,2012,09:57-60+64.

[2] 纪欣然,丁一,梁致源.基于FPGA的多功能数字钟设计[J].电子设计工程,2012,16:177-179.

[3] 刘艳昌,王娜.基于FPGA的多功能数字钟设计[J].河南科技学院学报(自然科学版),2013,02:89-94.

[4] 王术群.基于FPGA数字钟的设计与实现[J].西南民族大学学报(自然科学版),2011,S1:104-107.

[5] 崔刚,陈文楷.基于FPGA的数字钟设计[J].现代电子技术,2004, 27(22):102-103.

⑹樊永宁,张晓丽.基于VHDL的多功能数字钟的设计[J].工矿自动化,2006(3):92-94.

[7] 万春迎.基于VHDL的数字时钟设计[J].科技信息,2008(27).

[8] 徐大诏.基于FPGA实现的数字钟设计[J].信息技术,2009, 33(12):101-104.

指导教师意见:

(签字)

年月日注:本表可根据内容续页。

vhdl课程设计设计模为 4、8、12、16的可变计数器实验报告总结

VHDL课程设计 - 可变计数器实验报告总结

一、设计概述

本课程设计的主要目标是设计并实现一个可变计数器,其模(Modulo)值可以在4、8、12、16之间进行选择。

计数器采用VHDL编程语言进行描述,并在FPGA开发板上进行测试验证。

二、设计实现

1. 硬件平台:我们选择了Xilinx的FPGA开发板作为硬件平台,它具有丰富的I/O资源和足够的逻辑单元,可以满足我们的设计需求。

2. VHDL编程:我们采用VHDL语言进行编程,实现了模4、模8、模12和模16的可变计数器。

通过选择不同的计数模式,计数器的模值可以在4、8、12、16之间进行切换。

3. 测试与验证:为了验证计数器的功能,我们编写了测试平台,并通过仿真和实际硬件测试对计数器进行了全面的测试。

三、实验结果与分析

1. 实验结果:通过仿真和实际硬件测试,我们验证了计数器的

功能正确性。

在不同的模值下,计数器都能正确地进行计数操作,并且在达到模值后能正确地回绕到0。

2. 结果分析:实验结果表明,我们的VHDL编程和FPGA开发技能得到了很好的应用和提升。

同时,通过这次课程设计,我们更深入地理解了可变计数器的设计和实现原理,提高了我们的硬件设计能力。

四、总结与展望

本次课程设计让我们深入了解了VHDL编程语言和FPGA开发技术,提高了我们的硬件设计能力。

通过实际的设计和测试,我们成功地实现了一个可变模值的计数器,达到了课程设计的要求。

在未来的学习和工作中,我们将继续深入学习FPGA设计和VHDL编程,不断提高自己的硬件设计能力。

同时,我们也期待将这种技术应用于更多的实际项目中,为工程实践做出贡献。

VHDL硬件课程设计实验报告

硬件课程设计实验报告一、全加器设计1、实验目的(1)了解四位全加器的工作原理。

(2)掌握基本组合逻辑电路的FPGA实现。

(3)熟练应用Quartus II进行FPGA开发。

2、实验原理全加器是由两个加数X i和Y i以及低位来的进位C i-1作为输入,产生本位和S i以及向高位的进位C i的逻辑电路。

它不但要完成本位二进制码X i和Y i相加,而且还要考虑到低一位进位C i-1的逻辑。

对于输入为X i、Y i和C i-1,输出为S i和C i的情况,根据二进制加法法则可以得到全加器的真值表如下表所示:全加器真值表由真值表得到S i和C i的逻辑表达式经化简后为:这仅仅是一位的二进制全加器,要完成一个四位的二进制全加器,只需要把四个级联起来即可。

i3、实验内容本实验要完成的任务是设计一个四位二进制全加器。

具体的实验过程就是利用实验系统上的拨动开关模块的K1~K4作为一个加数X输入,K5~K8作为另一个加数Y输入,用LED模块的LED1~LED8来作为结果S输出,LED亮表示输出‘1’,LED灭表示输出‘0’。

实验箱中的拨动开关、LED与FPGA的接口电路,以及拨动开关、LED 与FPGA的管脚连接在以前的实验中都做了详细说明,这里不在赘述。

4、实验现象与结果以设计的参考示例为例,当设计文件加载到目标器件后,拨动相应的拨动开关,输入两个四位的加数,则在LED灯上显示这两个数值相加的结果的二进制数。

5、实验报告(1)出不同的加数,绘仿真波形,并作说明。

(2)在这个程序的基础上设计一个八位的全加器。

(3)在这个程序的基础上,用数码管来显示相乘结果的十进制值。

(4)将实验原理、设计过程、编译仿真波形和分析结果、硬件测试结果记录下来。

二、七段数码显示设计1、七段显示基本原理七段显示器,在许多产品或场合上经常可见。

其内部结构是由八个发光二极管所组成,为七个笔画与一个小数点,依顺时针方向为A、B、C、D、E、F、G与DP等八组发光二极管之排列,可用以显示0~9数字及英文数A、B、C、D、E、F。

VHDL软件设计报告样本

南京邮电大学课程设计报告设计类别: EDA-VHDL专业名称: 电子信息工程班级学号: B08021717学生姓名: 付祥旭基本题: 数字时钟设计综合题: 数码管学号动态显示同小组成员:学号:姓名: 曾大千指导教师: 王奇、梅中辉、周晓燕、孔凡坤日期: 9月1日—9月21日第一章软件设计介绍一、各类设计环节的性质、目的与任务本课程设计是一门重要的专业基础实践课, 是《现代电子技术》或《EDA技术》等课程的后续实践课程, 未选前述课程的要求学生具备数字电路和C语言的基础。

本课程设计的目的和任务: 1.使学生全面了解如何应用该硬件描述语言进行高速集成电路设计; 2.经过软件设计环节与仿真环节使学生熟悉Quartus II设计与仿真环境; 3. 经过对基本题、综合题的设计实践, 使学生掌握硬件系统设计方法( 自底向上或自顶向下) , 熟悉VHDL语言三种设计风格, 熟悉其芯片硬件实现的过程。

二、实验内容软件设计课题共分基本课题、综合课题两档。

基本课题2题, 12个学时完成; 综合课题共4题, 20个学时完成。

四、考核办法学生软件设计成绩考核来源于以下方面:考勤及工作态度( 占10%)软件设计报告( 占40%)验收情况( 占50%)五、主要设备微型计算EDA-VHDL开发软件( QUARTUS2)ALtera CPLD硬件实验开发系统第二章软件开发平台简介1 Quartus II简介Quartus II 提供了完整的多平台设计环境, 能满足各种特定设计的需要, 也是单芯片可编程系统( SOPC) 设计的综合性环境和SOPC开发的基本设计工具。

Quartus II 设计工具完全支持VHDL、Verilog的设计流程, 其内部嵌有VHDL、Verilog逻辑综合器。

Quartus II 具备仿真功能, 同时也支持第三方的仿真工具, 如Modelsim。

Quartus II 包括模块化的编译器。

编译器包括的功能模块有分析/综合器( Analysis & Synthesis) 、适配器(Fitter)、装配器(Assembler)、时序分析器(Timing Analyzer)、设计辅助模块(Design Assistant)、EDA网表文件生成器(EDA Netlist Writer)、编辑数据接口(Compiler Database Interface)等。

广东工业大学VHDL实验报告

VHDL与集成电路设计实验报告时间:第7周周四实验一应用QuartusII完成基本组合电路设计一、实验目的:熟悉QuartusⅡ的VHDL文本设计流程全过程,学习简单组合电路的设计、多层次电路设计、仿真和硬件测试。

二、实验内容:首先利用QuartusⅡ完成2选1多路选择器(例1)的文本编辑输入(mux21a.vhd)和仿真测试等步骤,给出图1-1所示的仿真波形。

最后在实验系统上进行硬件测试,验证本项设计的功能。

三、实验程序:...COMPONENT MUX21APORT ( a,b,s : IN STD_LOGIC;y : OUT STD_LOGIC);END COMPONENT ;...u1 : MUX21A PORT MAP(a=>a2,b=>a3,s=>s0,y=>tmp);u2 : MUX21A PORT MAP(a=>a1,b=>tmp,s=>s1,y=>outy);END ARCHITECTURE BHV ;【例1】ENTITY mux21a ISPORT ( a, b, s: IN BIT;y : OUT BIT );END ENTITY mux21a;ARCHITECTURE one OF mux21a ISBEGINPROCESS (a,b,s)BEGINIF s = '0' THEN y <= a ; ELSE y <= b ;END IF;END PROCESS;END ARCHITECTURE one ;五、实验结果及分析仿真结果:仿真结果分析:这是一个选择输出功能,当s为高电平时,输出b;当s为低电平时,输出为a。

输出存在延迟。

VHDL与集成电路设计实验报告时间:第8周周四实验四:移位相加硬件乘法器设计一、实验目的:学习应用移位相加原理设计8位乘法器。

二、实验内容:(1) 实验内容1:根据给出的乘法器逻辑原理图及其各模块的VHDL描述,在QuartusII上完成全部设计,包括编辑、编译、综合和仿真操作等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2013届毕业设计(论文)开题报告

题 目 基于VHDL的相位计设计

学 院 电气信息工程学院

专 业

姓 名

班 级

指导教师

2013年 月 日

毕业设计(论文)开题报告

(课题目的意义;主要设计(研究)内容;设计(研究)方案;预期成果;进度安

排及主要参考文献等)

一、 课题目的与意义

本课题研究设计了一种基于VHDL的相位计设计。随着相位测量技术广泛应用

于国防、科研、生产等各个领域,对相位测量的要求也逐步向高精度、高智能化方

向发展,在低频范围内,相位测量在电力、机械等部门有着尤其重要的意义,对于

低频相位的测量,用传统的模拟指针式仪表显然不能够满足所需的精度要求,随着

电子技术以及微机技术的发展,数字式仪表因其高精度的测量分辨率以及高度的智

能化、直观化的特点得到越来越广泛的应用。基于这些要求, 本设计采用了功能

强大的可编程逻辑器件(FPGA)为主要的硬件载体,使用VHDL语言完成主要的逻辑

控制和数字处理,因所有的控制和数字处理都在FPGA内部完成。成本低,工作可靠,

外围电路简单。

二、 主要设计(研究)内容

设计了一个基于VHDL的相位计设计。利用相移网络产生两个具有一定相位差的

信号,经过信号调理电路对信号进行放大和变形,最后将两路信号送入FPGA进行

数据处理;由液晶屏显示信号的频率和两个信号的相位差。

系统设计包含相移网络设计、调理电路设计、液晶显示和VHDL语言的程序设

计。

主要研究内容如下:

1、系统原理框图设计

2、硬件电路的设计和制作

3、基于VHDL语言的程序代码的设计

三,设计(研究)方案:

首先完成硬件设计部分,然后在此基础上完成软件的设计和相应的测试。

研究步骤:

掌握可编程逻辑器件的工作原理和相位测量的原理。

确定相位计总体设计方案;

完成硬件电路的设计

完成软件设计

设计流程,并调试、验证等。

四,设计过程:

(1)第一阶段:可行性研究、需求分析。对项目进行分析和规划以及相关资

料的收集,从而确定系统的结构、功能、模块和数据,并制定具体的工作计划和方

案。

(2)第二阶段:总体设计。确定硬件系统结构及软件系统结构,进行模块划

分,确定FPGA模块的功能、接口以及模块间的调用关系,生成结构图及概要设计

说明书。

(3)第三阶段:详细设计。为每个模块设计实现细节,生成程序流程图及详

细设计说明书。

(4)第四阶段:硬件设计。根据设计要求选择合适的型号和电路来实现硬件

功能。

(5)第五阶段:编写代码。根据详细设计说明书编写代码,生成源程序代码、

内部文档。

(6)第六阶段:软件测试。尽可能多地发现软件中的错误和缺陷,经过不断

调试使所开发的软件更加完善。

(7)第七阶段:完善各项文档及毕业论文。从整个开发过程和以上文档中总

结经验和教训,罗列各种方法和技巧,并写好毕业论文。

五,预期成果:

1、提供一种基于VHDL的相位计设计装置1台;

2、通过设计,完成毕业论文

六,进度安排:

起止日期 内容

2013年3月1日 - 2013年3月7日 整理资料,书写开题报告

2013年3月8日 - 2013年3月31日 完成系统总体分析与设计

2013年4月1日 - 2013年4月9日 完成系统详细设计与硬件的

一些功能

2013年4月10日 - 2013年4月19日 完成硬件功能和编写代码,

2013年4月20日 - 2013年5月10日

调试软件、测试软件功能,

编写设计说明书

2013年5月11日 - 2013年6月10日

完善设计说明书,检查作品,

准备答辩

参考文献

1]张毅刚,彭喜源编著,MCS—51单片机应用设计,哈尔滨工业大学出版社,

1997.

[2]王武江,常用集成电路速查手册.北京:冶金工业出版社,2004.12.

[3]方佩敏,新编传感器原理应用电路详解.北京:电子工业出版社,1994.

[5]孙传友,孙晓斌编著,感测技术基础,电子工业出版社,2001.

[6]何希才编著,新型集成电路及其应用实例,科学出版社,2002.

[7]何立民编著,单片机应用技术选编,北京航空航天大学出版社,1995.

[8]王毅,单片机器件应用手册,人民邮电出版社,1995.

[9]秦增煌,电工学,高等教育出版社2003

指导教师意见(对课题设计(研究)内容的深度、广度及设计(研究)方案的意见

和对毕业设计(论文)结果的预测等)

指导教师签名:

年 月 日

系(教研室)审核意见:

系主任签名

:

年 月 日

注:开题报告应在指导教师指导下由学生填写,经指导教师及系审核后生效。