飞思卡尔8位单片机-第10章 IIC

飞思卡尔8位单片机MC9S08JM60开发板实践教程共40页word资料

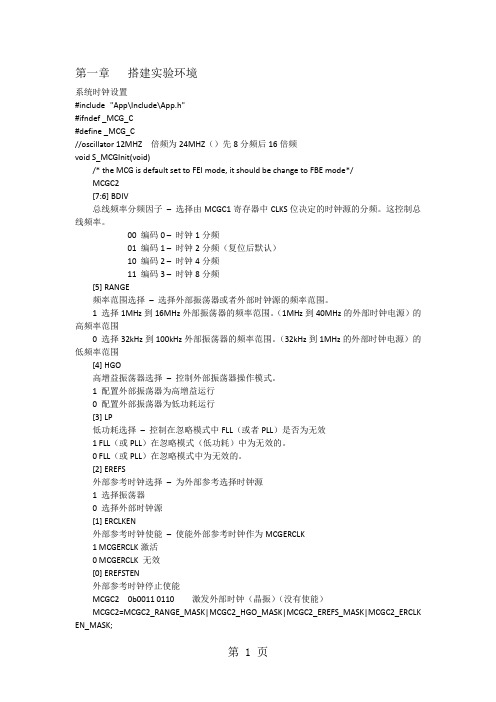

第一章搭建实验环境系统时钟设置#include "App\Include\App.h"#ifndef _MCG_C#define _MCG_C//oscillator 12MHZ 倍频为24MHZ()先8分频后16倍频void S_MCGInit(void)/* the MCG is default set to FEI mode, it should be change to FBE mode*/MCGC2[7:6] BDIV总线频率分频因子–选择由MCGC1寄存器中CLKS位决定的时钟源的分频。

这控制总线频率。

00 编码0 –时钟1分频01 编码1 –时钟2分频(复位后默认)10 编码2 –时钟4分频11 编码3 –时钟8分频[5] RANGE频率范围选择–选择外部振荡器或者外部时钟源的频率范围。

1 选择1MHz到16MHz外部振荡器的频率范围。

(1MHz到40MHz的外部时钟电源)的高频率范围0 选择32kHz到100kHz外部振荡器的频率范围。

(32kHz到1MHz的外部时钟电源)的低频率范围[4] HGO高增益振荡器选择–控制外部振荡器操作模式。

1 配置外部振荡器为高增益运行0 配置外部振荡器为低功耗运行[3] LP低功耗选择–控制在忽略模式中FLL(或者PLL)是否为无效1 FLL(或PLL)在忽略模式(低功耗)中为无效的。

0 FLL(或PLL)在忽略模式中为无效的。

[2] EREFS外部参考时钟选择–为外部参考选择时钟源1 选择振荡器0 选择外部时钟源[1] ERCLKEN外部参考时钟使能–使能外部参考时钟作为MCGERCLK1 MCGERCLK激活0 MCGERCLK 无效[0] EREFSTEN外部参考时钟停止使能MCGC2 0b0011 0110 激发外部时钟(晶振)(没有使能)MCGC2=MCGC2_RANGE_MASK|MCGC2_HGO_MASK|MCGC2_EREFS_MASK|MCGC2_ERCLK EN_MASK;while(!MCGSC_OSCINIT);//MCGSC寄存器中OSCINIT(第1位)为1,表示由EREFS位选择的晶振被初始化。

飞思卡尔单片机教学课件

和低功耗性能。

丰富的外设接口

飞思卡尔单片机集成了多种外 设接口,如UART、SPI、I2C、 ADC等,方便与外部器件进行 通信和控制。

易于开发

飞思卡尔单片机提供完善的开 发工具和文档,支持多种开发 语言,如C、汇编等,降低了开 发难度。

THANKS

感谢您的观看

无线通信

讨论无线通信技术在单片机网络通 信中的应用,如Wi-Fi、蓝牙等。

单片机与嵌入式系统

嵌入式系统概述

介绍嵌入式系统的基本概念、组成和特点,以及其在现代工业控 制、智能家居等领域的应用。

单片机与嵌入式系统的关系

阐述单片机在嵌入式系统中的地位和作用,以及如何将单片机应用 于嵌入式系统的开发。

嵌入式系统开发流程

智能家居控制系统主要涉及灯光、 空调、门窗、安防等家居设备的 控制,通过无线通信技术实现设 备间的互联互通。

工业自动化控制系统

工业自动化控制系统是利用飞思 卡尔单片机实现生产过程中的自

动化控制和监测的应用。

该系统可以实现生产线的自动化 运行、工艺参数的实时监测和调 整、设备故障的预警和诊断等功

能。

工业自动化控制系统主要涉及传 感器、执行器、人机界面等设备 的控制,提高生产效率和产品质

量。

智能交通系 统

智能交通系统是利用飞思卡尔单片机 实现交通信号灯的控制、车辆监测和 调度等功能的系统。

智能交通系统主要涉及交通信号灯、 摄像头、雷达等设备的控制,提高道 路通行效率和交通安全。

该系统可以实现交通信号的自适应调 整、车辆违章的自动识别和抓拍、路 况信息的实时发布等功能。

讨论如何根据实际需求, 为不同的任务分配优先级, 确保关键任务能够得到优 先处理。

飞思卡尔8位单片机—飞思卡尔8位单片机基础知识

2.2、单片机的命名规则及选择

2.2.1、单片机选型需要关心的事项

供电电压、速度及功耗 管脚数量、并口与串口、功能复用、外扩能力 存储器资源:ROM、RAM、是否分页 外设接口 定时器数量、PWM、捕捉、比较 SPI、IIC、UART、CAN、USB、YITAI 中断源 模拟量处理 特殊接口:VGA、LCD、MOTOR 封装

选型要学会查找资源差异表

Freescale的08系列单片机型号有一百多种。在 这些不同型号的单片机中,资源各不相同,即使 是同一种型号的单片机,也有多种封装形式,其 I/O引脚数目也不相同。如MC68HC908JB8就有 20脚的DIP、28脚的SOIC、44脚的QFP和20脚 的SOIC四种封装形式。

7〉 管脚的复用

注意: 0、管脚功能复用时的优先 级见右表,高优先级接管管 脚时,对低优先级模块会产 生杂乱信号,因此切换前应 先停止不使用的功能。 1、PTA5作为只能输入管脚 而言,输入电压不能超过 VDD。 2、IIC使用的端口可以通过 设置SOPT2 寄存器中的 IICPS位重新定位到PTB6和 PTB7,复位时缺省使用 PTA2 and PTA3。 3、如果ACMP和ADC被同 时使能,管脚PTA0和PTA1 可同时使用。

第二章 飞思卡尔8位单片机基础知识

2.1、飞思卡尔8位单片机系列简介 2.2、飞思卡尔单片机命名规则与单片机选型 2.3、 MC9S08QG8硬件结构

8bit 单片机的Core type

HC08系列、HCS08系列、RS08系列。 HC08是1999年开始推出的产品,种类多,针对不同场合 的应用都可以选到合适的型号。 HCS08是2004年左右推出的8位MCU,资源丰富,功耗 低,性价比高,是08系列单片机的发展趋势。HC08与 HCS08的最大区别是调试方法不同与最高频率的变化 。 RS08是HCS08架构的简化版本,2006年推出,其内核体 积比传统的内核小30%,带有精简指令集,满足用户对 体积更小、更加经济高效的解决方案的需求。RAM及 Flash空间大小差异、封装形式不同、温度范围不同、 频率不同、I/O资源差异等形成了不同型号,为嵌入式 应用产品的开发提供了丰富的选型。

飞思卡尔IIC的24c02程序

本程序是HCS系列都可以本人已通过实验下面是程序代码/*****************头文件*****************************************/#include <hidef.h> /* for EnableInterrupts macro */#include "derivative.h" /* include peripheral declarations */#include "iic24c02.h"/*********************延时函数************************************/ void delay(void){byte i;i=8;while(i>0){i--;}}/*********************ICC初始化************************************/ void Init_IIC(void){SOPT1_IICPS=0; //IIC 在PTA引脚上// IICF=0x0d; //设置波特率<100kbps// IICF=0X4B;IICF=0X24;IICC_IICEN=1;//使能IICIICC_TXAK=0; //当接收完一字节数据产生确认位IICC_IICIE=0;//禁止中断// IICA=0x38;}/*********************写函数************************************/void WRITE_IIC(uchar addres,uchar date){byte temp;IICC_IICEN = 0;IICC_IICEN = 1; //使能IICtemp = IICS; //清中断IICS_IICIF = 1;IICC_MST=0;IICS_SRW=0;IICC_TX=1; //写使能IICC_MST=1; //设为主模式delay();IICD=0xA0; //发送芯片地址,写命令while(!IICS_IICIF );temp = IICS;IICS_IICIF=1;IICD=addres; //发送寄存器地址while(!IICS_IICIF);temp = IICS;IICS_IICIF=1;IICD=date;//写第1个字节while(!IICS_IICIF);temp = IICS;IICS_IICIF=1;IICC1_TX=0;IICS_SRW=0;IICC1_MST=0;}/*********************读一个字节************************************/byte IIC_read_one_byte(byte address){byte temp;IICC_RSTA=0;IICC_IICEN = 0;IICC_IICEN = 1; //使能IICtemp = IICS; /* Clear any pending interrupt */IICS_IICIF = 1;IICC1_MST=0;IICS_SRW=0;IICC_TX=1; //写使能IICC_MST=1; //置为主模式delay();IICD=0xA0; //发送芯片地址,写命令while(!IICS_IICIF);temp = IICS;IICS_IICIF=1;IICD=address; //发送寄存器地址while(!IICS_IICIF);temp = IICS;IICS_IICIF=1;IICC_TXAK=1;IICC_RSTA=1; //重新启动IICD=0xA1; //读命令while(!IICS_IICIF);temp = IICS;IICS_IICIF=1;IICC_TX=0; //读使能temp=IICD;while(!IICS_IICIF);temp = IICS;IICS_IICIF=1;temp=IICD; //读一个字节IICC_MST=0;delay();return(temp);}。

飞思卡尔8位单片机—飞思卡尔8位单片机基础知识

7〉 管脚的复用

注意: 0、管脚功能复用时的优先 级见右表,高优先级接管管 脚时,对低优先级模块会产 生杂乱信号,因此切换前应 先停止不使用的功能。 1、PTA5作为只能输入管脚 而言,输入电压不能超过 VDD。 2、IIC使用的端口可以通过 设置SOPT2 寄存器中的 IICPS位重新定位到PTB6和 PTB7,复位时缺省使用 PTA2 and PTA3。 3、如果ACMP和ADC被同 时使能,管脚PTA0和PTA1 可同时使用。

管脚及其功能

6〉 管脚控制寄存器

位于高页面的管脚控制寄存器,可以独立设置每个管 脚的输出驱动强度、输出信号变化速度、输入脚的内部 上拉允许等。内部上拉的设置有些时候自动失效,比如 管脚设为输出、管脚被外设使用、管脚作为模拟电路使 用等。如果管脚被用于键盘中断KBI模块,,并设置上升 沿触发,则允许上拉时实际是配置了下拉电阻。 对输出管脚设置了输出变化速度控制后,可以减少 EMC辐射,变化速度控制对输入脚无效。 输出管脚的输出驱动强度控制,可以选择更大的驱 动电流,虽然每个输出管脚都可以设置成大电流驱动, 但总电流不能超出芯片的工作范围。同时大驱动电流对 EMC辐射也会有一定影响。

• EPROM

EPROM(Erasable Programmable ROM,可擦除可编 程ROM)芯片可重复擦除和写入,。EPROM芯片在其正 面的陶瓷封装上,开有一个玻璃窗口,透过该窗口,可以 看到其内部的集成电路, 紫外线透过该孔照射内部芯片 就可以擦除其内的数据,完成芯片擦除的操作要用到 EPROM擦除器。EPROM内资料的写入要用专用的编程 器,并且往芯片中写 内容时必须要加一定的编程电压( VPP=12—24V,随不同的芯片型号而定)。EPROM的型 号是以27开头的,如27C020(8*256K)是一片 2M Bits容 量的EPROM芯片。EPROM芯片在写入资料后,还要以 不透光的贴纸或胶布把窗口封住,以免受到周围的紫外线 照射而使资料受损

飞思卡尔8位单片机MC9S08JM60开发板实践教程

第一章搭建实验环境系统时钟设置#include "App\Include\App.h"#ifndef _MCG_C#define _MCG_C//oscillator 12MHZ 倍频为24MHZ()先8分频后16倍频void S_MCGInit(void){/* the MCG is default set to FEI mode, it should be change to FBE mode*//************************************************************************** ***********MCGC2[7:6] BDIV总线频率分频因子–选择由MCGC1寄存器中CLKS位决定的时钟源的分频。

这控制总线频率。

00 编码0 –时钟1分频01 编码1 –时钟2分频(复位后默认)10 编码2 –时钟4分频11 编码3 –时钟8分频[5] RANGE频率范围选择–选择外部振荡器或者外部时钟源的频率范围。

1 选择1MHz到16MHz外部振荡器的频率范围。

(1MHz到40MHz的外部时钟电源)的高频率范围0 选择32kHz到100kHz外部振荡器的频率范围。

(32kHz到1MHz的外部时钟电源)的低频率范围[4] HGO高增益振荡器选择–控制外部振荡器操作模式。

1 配置外部振荡器为高增益运行0 配置外部振荡器为低功耗运行[3] LP低功耗选择–控制在忽略模式中FLL(或者PLL)是否为无效1 FLL(或PLL)在忽略模式(低功耗)中为无效的。

0 FLL(或PLL)在忽略模式中为无效的。

[2] EREFS外部参考时钟选择–为外部参考选择时钟源1 选择振荡器0 选择外部时钟源[1] ERCLKEN外部参考时钟使能–使能外部参考时钟作为MCGERCLK1 MCGERCLK激活0 MCGERCLK 无效[0] EREFSTEN外部参考时钟停止使能MCGC2 0b0011 0110 激发外部时钟(晶振)(没有使能)*************************************************************************** ***********/MCGC2=MCGC2_RANGE_MASK|MCGC2_HGO_MASK|MCGC2_EREFS_MASK|MCGC2_ERCLK EN_MASK;while(!MCGSC_OSCINIT);//MCGSC寄存器中OSCINIT(第1位)为1,表示由EREFS位选择的晶振被初始化。

飞思卡尔8位单片机MC9S08 10 定时接口模块.ppt

10.4 定时器模块的输出比较功能

(3)T1通道1状态和控制寄存器(Timer1 Channel 1 Status and Control Register,T1SC1)

数据位 定义 复位

10.1 计数器/定时器的基本工作原理

10.1.2 MC68HC908GP32 MCU的定时接口的基本 原理的概述

MC68HC08系列的单片机可以提供多个独立的定时器,例如, MC68HC908GP32芯片有两个定时器,分别叫定时器1、定时器2,它们的 工作原理是一致的,下面的说明均以定时器1为例。

(2)输入捕捉的基本含义

输入捕捉功能是用来监测外部的事件和输入信号。当外部事件发 生或信号发生变化时,在指定的输入捕捉引脚上发生一个指定的沿跳 变(可以指定该跳变是上升沿还是下降沿)。定时器捕捉到特定的沿 跳变后,把计数寄存器当前的值锁存到通道寄存器。

10.3 定时器模块的输入捕捉功能

10.3.2 输入捕捉的寄存器

通道寄存器是一个16位的寄存器,分为高字节和低字节,在读取的 时候要分别读取。为了防止两次读取之间该寄存器的内容发生变化而产 生虚假的输入捕捉计数值,系统会在读取高字节时锁存低字节的内容, 这时即使又发生特定的沿跳变,通道寄存器的内容也不会改变。

所以,若要读取整个通道寄存器,必须先读高字节,再读低字节。

1

111

1

1

1

1

D7 :通道标志位,用来标志定时器1通道0发生了输入捕捉。 D6 :通道中断允许位,用来设置是否允许发生输入捕捉中断。 D5~ D4:模式选择位。每一个定时器都可以工作在输入捕捉,输出比较和 PWM输出模式,这两位用来选择这些工作模式。 D3~D2 :跳变沿/ 输出电平选择位。 D1 :溢出翻转控制标志位,定时器通道用做输入 捕捉时,此位无用。 D0 :通道最大占空比设置位 ,定时器通道用作 输入捕捉时,此位无用。

经典:飞思卡尔8位单片机-第10章-IIC

(4)STOP信号

• 在SCL为逻辑1时SDA的一个上升沿 • 主器件做下面两件事情之一,数据传输中止:

(3)数据传输

• 数节为8位,高位在前,低位在后。每传输一位数据都有 一个时钟脉冲相对应。

• SCL线为低电平时,SDA线上数据就被停止传送。接收器可 向SCL线输出低电平而箝住SCL(SCL=0),迫使SDA线处于 等待状态,直到接收器准备好接收新的数据/地址字节时, 再释放时钟线SCL(SCL)=1),使SDA线上数据传输得以 继续进行。

8、当主机发送寻址字节时,总线上所有器件都将该寻址字节中的高7位地址 与自己器件的地址比较,若两者相同,则该器件认为被主机寻址,并根据 读/写位确定是从发送器还是从接收器

9、具有I2C总线接口的单片机可以工作在上述4种工作状态中的任一状态,而 一些带有I2C总线接口的存储器(RAM或E2PROM)模块只能充当被控发送器 或被控接收器

Hale Waihona Puke 时钟分频与数 据保持时间表

时钟分频设置举例

• 前提:总线时钟4MHz,IIC的时钟为100KHz;

配置:

MULT = 01,对应 mul = 2;

ICR = 0; 对应 SCL分频数=20; SDA保持值= 7;

则波特率

= 总线频率(Hz)/ (mul * SCL分频数)

=4000000/(2*20) =100K; (周期10uS)

IIC Clock Rate — 该ICR数值用来定义总线分频得到IIC时钟的分频因子, 同时该ICR数值也用来定义数据线SDA的数据保持时间;

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

.

QG8的IIC特点

1. 与 标准的IIC协议兼容; 2. 支持多主操作; 3. 有64种不同的时钟频率可供选择; 4. Software selectable acknowledge bit; 5. 支持中断传输; 6. 在总线仲裁中失败方可自动由主切换到从模式; 7. 支持地址匹配中断; 8. 有S和P信号产生与检测功能; 9. 有“重新启动”(Repeated START)信号产生能力; 10. 支持Ack信号的产生与检测; 11. 具有总线忙检测能力;

.

图9-2 I2C总线的器件连接

.

I2C总线信号的时序

.

I2C协议

一个标准的通信由四部分组成:

– START信号 – 从地址传输 – 数据传输 – STOP信号

.

.

(1)START信号 一个START信号定义为SDA的一个下降沿,同时SCL

保持为高。由主机产生。

(2)从地址传输

7位呼叫地址,紧接着一个读/写位,读写位告诉从器件数据传 输的期望方向。 1 = 读传输,从发送数据给主。 0 = 写传输,主发送数据给从。 正好匹配主器件传输的呼叫地址的从器件通过送回一个应答位 响应。 从机地址由一个固定的和一个可编程的部分构成。例如,某些 器件有4个固定的位(高4位)和3个可编程的地址位(低3位), 那么同一总线上共可以连接8个相同的器件。

.

(3)数据传输

• 数节为8位,高位在前,低位在后。每传输一位数据都有 一个时钟脉冲相对应。

• SCL线为低电平时,SDA线上数据就被停止传送。接收器可 向SCL线输出低电平而箝住SCL(SCL=0),迫使SDA线处于 等待状态,直到接收器准备好接收新的数据/地址字节时, 再释放时钟线SCL(SCL)=1),使SDA线上数据传输得以 继续进行。

第十章 内部集成电路IIC原理及应用

第1节 IIC概述 第2节 IIC管脚及相关寄存器 第3节 IIC在系统扩展中的应用

.

9.1

I2C 概

述

• I2C总线是PHILIPS公司推出的串行总线。I2C 总线的应用非常广泛,在很多器件上都配备有 I2C总线接口,使用这些器件时一般都需要通 过I2C总线进行控制。这里简要介绍I2C总线的 工作原理及操作时序。

8、当主机发送寻址字节时,总线上所有器件都将该寻址字节中的高7位地址 与自己器件的地址比较,若两者相同,则该器件认为被主机寻址,并根据 读/写位确定是从发送器还是从接收器

9、具有I2C总线接口的单片机可以工作在上述4种工作状态中的任一状态,而 一些带有I2C总线接口的存储器(RAM或E2PROM)模块只能充当被控发送器 或被控接收器

IIC Clock Rate — 该ICR数值用来定义总线分频得到IIC时钟的分频因子, 同时该ICR数值也用来定义数据线SDA的数据保持时间;

(a)通过产生一个STOP信号放弃总线。

(b)通过产生重复的START信号发起一个新的呼叫。

.

(4) 重复的START信号 • 图10-8所示,一个重复的START信号是不用首先产生STOP信号终止通

信的START信号。 (5) 仲裁程序 • 如果两个或更多的主器件试图在同一时间控制总线,一个时钟同步程

.

QG8

SDA SCL

1、电气特性; 2、寻址无需片选; 3、多主和主从 4、MT、MR、ST、SR

.

I2C总线的特点

1、电气特性。各节点需共地,SDA和SCL需分别接上拉电阻。

2、寻址无需片选,主从方式中,从器件的地址包括器件编号地址和引脚地 址,器件编写地址由I2C总线委员会分配,引脚地址决定于引脚外接电平 的高低

.

10.2 、IIC管脚及相关寄存器

.

外部信号描述

.

寄存器

IIC Address Register (IICA)

7-1 ADDR 作为从模式时,存放被寻找的地址,对于主模式该寄存器无用。

IIC Frequency Divider Register (IICF)

7-6 MULT

5-0 ICR

用来定义波特率的乘数因子mul: 00 mul = 01;01 mul = 02;10 mul = 04;11 Reserved

• 当主控器作为接收器接收被控器送来的最后一个数据时, 必须给被控器发送一个非应答信号(A),令被控器释放 SDA线,以便主控器可以发送停止信号来结束数据的传输。 I2C总线上的应答信号比较重要,在编制程序时应该着重考 虑。

.

(4)STOP信号 • 在SCL为逻辑1时SDA的一个上升沿 • 主器件做下面两件事情之一,数据传输中止:

.

• 数据字节没有限制,但每个字节后都必须跟随一个应答位 应答信号在第9个时钟位上出现,主控发送器必须在被控 接收器发送应答信号前,预先释放对SDA线的控制。接收 器在SDA线上输出低电平为应答信号(A),输出高电平为 非应答信号(A)。

.ቤተ መጻሕፍቲ ባይዱ

• 主控器接收到应答信号后可进行下一字节的发送。但如果 被控器由于某种原因需要进行其他处理而无法继续接收SDA 线上数据时,便可向SDA线输出一个非应答信号(A),使 SDA线保持高电平,主控器据此便可产生一个停止信号来终 止SDA线上的数据传输。

3、多主和主从两种工作方式的总线

4、为主控发送器、主控接收器、被控发送器和被控接收器

5、起始和终止信号以及时钟信号都是由主控器提供

6、其总线传输速率为100 kb/s(改进后的规范为400 kb/s),总线驱动能 力为400 pF。QG8的最快速度为clock/20。

7、 I2C总线还具有仲裁功能,当一个以上的主器件同时试图控制总线时,只 允许一个有效,从而保证数据不被破坏

10、在多主方式中,通过硬件和软件的. 仲裁主控制器取得总线控制权

I2C总线的接口电路结构

1、数据线SDA和时钟线SCL都是双向传输线,平时均处于高 电平备用状态,只有当需要关闭I2C总线时,SCL线才会箝 位在低电平。

2、 SCL线上为高电平时,SDA线上的数据信号才会有效, SCL低时,SDA数据无效。因此,只有当SCL线为低电平时, SDA线上的电平状态才允许发生变化。