第二章_VHDL代码结构(2015 版)

vhdl 2

四、文件(1) 文件的定义:实体中用来传输大量数据的一种载体 对象,它是VHDL-93标准新通过的。 物理意义:无。 书写格式:

FILE 文件名 [,文件名…] :文件类型 IS [方向] 路径表达式;

文件类型的定义格式:

TYPE 文件类型名 IS FILE OF 数据类型;

文件说明的小例子:

四、文件(2)

二、用户定义的数据类型(1) 优点:为程序编写提供了自由度和灵活性。 遵循原则:先定义、后使用。 可枚举类型 1、作用:设计中方便数字逻辑的表示。 2、定义格式:

TYPE 枚举数据类型名 IS (枚举元素,枚举元素,…);

3、枚举类型举例:

TYPE boolean IS (false,true); TYPE bit IS (’0’,’1’); TYPE week IS (mon,tue,wed,thur,fri,sat,sun);

三、变量(2) 变量说明时可以不用赋初始值。这时它将取系统 默认值,即所属数据类型的最小值或者最左值。 变量使用的注意事项: a、初始赋值符号和程序中赋值符号均为“:= ”; b、变量所赋的值应与定义的数据类型一致; c、变量的定义和作用范围仅限于进程和子程序; d、变量的赋值是直接的、立即生效的,因此变量 赋值语句中不允许出现附加延迟。 如何将一个变量的值带出它的作用范围?

五、信号和变量的区别(2) P1: PROCESS VARIABLE a,b : integer; BEGIN WAIT UNTIL clk = ’1’; a : = 10; b : = 20; a : = b; b : = a; END PROCESS;

五、信号和变量的区别(3) SIGNAL a,b : integer; P2: PROCESS BEGIN a <= 10; b <= 20; WAIT FOR 10 ns; a <= b; b <= a; WAIT FOR 10 ns; END PROCESS;

第二章VHDL1

BCD

3、数据类型

VHDL预定义数据类型; IEEE预定义标准逻辑位与矢量; 用户自定义的数据类型; 数据类型的转换

VHDL预定义数据类型

数据类型 布尔量(Boolean) 位(Bit) 位矢量(Bit_Vector) 整数 实数 时间 简要说明 用于逻辑(关系)运算,取值FALSE(伪),TRUE (真)。 用于逻辑运算,取值0和1。 基于Bit的数组,用于逻辑运算。 取值范围-(231-1)~(231-1),可用32位有符号的二进制表示, 用于数值运算。 取值范围-1.0E38~1.0E38,仅用于仿真,不可综合。 完整的时间类型包括整数和物理量单位两部分,整数与 单位之间至少留一个空格,如20 μs。仅用于仿真,不能 综合。

信号(SIGNAL)

“信号”数据对象,代表电路内部信号或连接线路, 其在元件之间起互连作用(端口也是一种信号); 在实体说明、结构体描述和程序包说明中使用(不能 在进程、过程、函数中定义?),是全局量; 初始值只对仿真有用,对综合来说意义不大。 SIGNAL 信号名:数据类型[:=表达式];

VHDL预定义数据类型

(4)整数(Integer); a. 正整数(Positive) b. 自然数(Natural) type INTEGER is range –2147483648 to 2147483647;

subtype POSITIVE is range 1 to INTEGER‟High;

文件(FILE)

VHDL-93语法也把文件作为一种数据对象; 用于VHDL程序的仿真,不能通过复制更新文件的内 容,同时,文件对象不能被赋值; 作为参数向过程和函数传递,通过规定的过程对文件 对象进行读出和写作的操作。

第2章 VHDL语言基础

End 实体名;

端口名

端口模式

数据类型

(2)ENTITY

端口模式(MODE)有以下几种类型: IN ;OUT;INOUT ;BUFFER 端口模式可用下图说明:(黑框代表一个设计或模块)

IN

OUT

BUFFER

INOUT

二输入与门电路设计范例

Library std; Use std.standard.all;

(4)CONFIGURATION定义区

定义格式: Configuration 配置名 of 实体名 is for 选用的结构体名 end for; end configuration 配置名 ;

二输入与门电路设计范例

a c

b电Leabharlann 真值表abc

0

0

0

1

0

0

0

1

0

1

1

1

二输入与门电路设计范例

Architecture Na of and2 is

‘1’; 符号<=为信号直接赋值符。

End Na;

--结构体Na

Architecture Nb of and2 is

Begin

c <= a and b;

--and 为逻辑与操作

End Nb; --结构体Nb

Library ieee; Use ieee.std_logic_1164.all;

Entity half_adder is Port( x,y : in std_logic;sum,carry : out hlf_adder); End half_adder;

(4)CONFIGURATION定义区

一个完整VHDL电路设计必须有一个实体 和对应的结构体,即实体和结构体对构成一个 完整的VHDL设计。

第2章EDA技术

构造体部分

7 ARCHITECTURE behavior OF dff IS 8 BEGIN -- PROCESS为进程语句,内部为顺序语句 9 PROCESS (rst,clk) 括号内为敏感信号,敏感信号变化一次 10 BEGIN 进程执行一次。 11 IF (rst= ‘1’) THEN 12 q<=’0’; 13 ELSIF (clk’EVENT AND clk= ’1’) THEN -- “<=”为信号赋值语句 14 q<=d; 15 END IF; 16 END PROCESS; 17 END behavior;

注意,std库和work库在程序中都是默认“可见”的, 因此不再需要对它们进行声明;

2.3 实体 实体(ENTITY) 描述电路的所有输入/输出引脚。

声明方式: ENTITY entity_name IS PORT( port_name: signal_mode signal_type; port_name: signal_mode signal_type; …); END entity_name;

常使用3种包:std_logic_1164, standard, work LIBRARY ieee; USE ieee.std_logic_1164.all; LIBRARY std; USE std.standard.all; LIBRARY work ; USE work. Work.all ; 分号表示一个语句和声明的结束。当出现“--” 时,表示后续文字为注释。

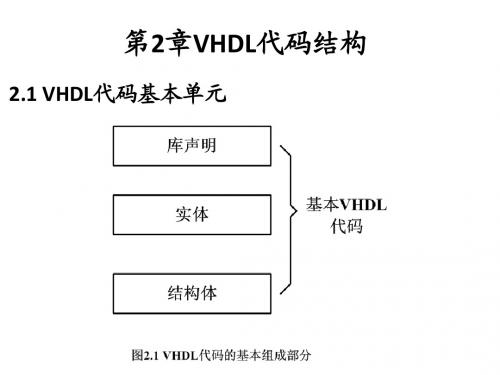

2.2 库声明 库(LIBRARY)的建立和使用有利于设计重用和代 码共享,同时可以使代码结构更加清晰。 2.2.1 库的种类 在VHDL设计中有3个常用的库: ieee库: 在ieee库中有一个IEEE正式认可的标准包集 std_logic_1164.ALL和其他常用包集合。

第二讲 VHDL基本结构

***双向电路设计 ***双向电路设计

在工程应用中,双向电路是设计者不得 在工程应用中 双向电路是设计者不得 不面对的问题.在实际应用中 在实际应用中,数据总线往往 不面对的问题 在实际应用中 数据总线往往 是双向的.如何正确处理数据总线是进行时 是双向的 如何正确处理数据总线是进行时 序逻辑电路设计的基础.在程序设计过程中 在程序设计过程中, 序逻辑电路设计的基础 在程序设计过程中 关键技术在于:实体部分必须对端口属性进 行申明,端口属性必须为inout类型,在构造体 需要对输出信号进行有条件的高阻控制.

双向电路的基本格式

ENTITY bidir_pin IS PORT( bidir : INOUT std_logic; oe, clk, from_core : IN std_logic; to_core : OUT std_logic; ……); END bidir_pin; ARCHITECTURE behavior OF bidir_pin IS BEGIN bidir <= from_core WHEN oe=‘1’ ELSE “ZZZZ”; to_core <= bidir; _ _ END behavior;

****PROCESS语句子结构 ****PROCESS语句子结构

[进程名 进程名:]PROCESS(信号 ,信号 ,…) 进程名 (信号1,信号2, ) [声明区 ;--局部变量、数据类型 声明区]; 局部变量 局部变量、 声明区 BEGIN 顺序执行语句; 顺序执行语句; END PROCESS[进程名 进程名] 进程名

例:二选一电路

ENTITY mux IS PORT (d0,d1,sel: IN BIT; q: OUT BIT); END mux; ARCHITECTURE connect OF mux IS SIGNAL tmp1,tmp2,tmp3: BIT; BEGIN cale: BLOCK BEGIN tmp1<=d0 AND sel; tmp2<=d1 AND (NOT sel); tmp3<=tmp1 OR tmp2; q<=tmp3; END BLOCK cale; connect; END connect;

VHDL2

2.1.1 短标识符

短标识符规则: 短标识符规则:

字符组成, 字母、 短标识符由字母、数字以及下划线字符组成,且具有以下特 征要求: 征要求: 第一个字符必须是字母; ● 第一个字符必须是字母; ● 最后一个字符不能是下划线; 最后一个字符不能是下划线; 不允许连续两个下划线; ● 不允许连续两个下划线; 在标识符中大、小写字母是等效的。 ● 在标识符中大、小写字母是等效的。 中的注释文字一律为2个连续的连接线 ● VHDL中的注释文字一律为 个连续的连接线 “ --”,可以出 中的注释文字一律为 个连续的连接线“ , 现在任一语句后面,也可以出现在独立行; 现在任一语句后面,也可以出现在独立行; 的保留字( ● VHDL的保留字(关键字)不能用于标识符; 的保留字 关键字)不能用于标识符;

2.1.2 扩展标识符

扩展标识符规则: 扩展标识符规则:

扩展标识符是VHDL’93版增加的标识符书写规则: 扩展标识符是VHDL’93版增加的标识符书写规则: VHDL’93版增加的标识符书写规则 扩展标识符用反斜杠来定界。例如: multi_screens\ (1) 扩展标识符用反斜杠来定界。例如:\multi_screens\, \eda_centrol\等都是合法的扩展标识符。 eda_centrol\等都是合法的扩展标识符。 允许包含图形符号、空格符。例如: $100\ (2) 允许包含图形符号、空格符。例如:\mode A, \$100\, p%name\ \p%name\等。 反斜杠之间的字符可以用保留字。例如: buffer\ (3) 反斜杠之间的字符可以用保留字。例如: \buffer\, entity\ end\ \entity\, \end\等。 (4) 扩展标识符的界定符两个斜杠之间可以用数字打头。如: 扩展标识符的界定符两个斜杠之间可以用数字打头。 100$\ 2chip\ 4screens\ \100$\, \2chip\, \4screens\等。 扩展标识符中允许多个下划线相连。例如: (5) 扩展标识符中允许多个下划线相连。例如: Four_screens\ TWO_Computer_sharptor\ \Four_screens\, \TWO_Computer_sharptor\等。 扩展标识符区分大小写。例如: EDA\ eda\不同。 (6) 扩展标识符区分大小写。例如: \EDA\ 与\eda\不同。 (7) 扩展标识符与短标识符不同。例如:\COMPUTER\ 与 扩展标识符与短标识符不同。例如: COMPUTER\ Computer不同 不同。 Computer不同。

第二部分 VHDL的模型

entity)

实体的组成:实体名、类属表、端口表、实体说明部 分、实体语句等部分。

根据IEEE标准,实体的一般格式为:

ENTITY 实体名 IS [GENERIC (类属表);] PORT (端口表); END 实体名;

2013-7-14

卢庆莉 编写

一、类属(GENERIC)

属类说明是实体中的可选项,放在端口之前, 其一般书写格式为:-----说明类属在可编程器件 的开发工具中一般都不支持,只有在EDA的工具 中才支持。 GENERIC [CONSTANT] 名字表 : [IN] 子类型标识 [ := 静态表达式 ,…..]

bit_vector (1 to n);

bit);

End

and_gate;

2013-7-14

卢庆莉 编写

2.1.2 结构体(ARCHITECTURE)

用VHDL语言描述结构体功能有三种方法: (1)行为描述法:以算法的形式来描述数据 变换。 (2)数据流描述法:是按照数据流动的方向 来进行描述的。 (3)结构描述法:是按照逻辑元件的连接进 行描述的。

一个通信模式;

一个数据类型。 端口说明一般格式:

PORT (端口名,端口名 :模式数据类型名; … 端口名,端口名 : 模式数据类型名);

2013-7-14 卢庆莉 编写

1、端口名

端口名是赋于每个外部引脚的名字,名字的 含义要与惯例接轨,例如:D开头的端口名表示数 据;A开头的端口名表示地址等。端口名通常用几 个英文字母或一个英文字母加数字表示。合法的 端口名: CLK,RESET,A0,D3

2013-7-14

卢庆莉 编写

②从计算机领域而言,行为描述和高级编程 语句相类似,所以计算机业内人士通常称之 为高级描述。

VHDL语言PPT课件

VHDL的设计单元

Entity(实体) 用来说明模型的外部输入输出特征

Architecture(构造体) 用来定义模型的内容和功能

每一个构造体必须有一个实体与它相对应,

所以两者一般成对出现,有时一个实体对应

多个构造

体

.

实体

类似一个“黑盒”,实体描述了“黑盒”的输 入输出口

黑盒

rst d[7:0] clk

q[7:0] co

实体举例

ENTITY black_box IS Generic ( m: TIME := 10ns;);

PORT (关键字

clk类, r属st:参量IN std_logic;

端d:口定义 IN std_logic_vector(width DOWNTO 0);

1996年,IEEE-1076.3成为VHDL综合标准

与其他的硬件描述语V言相H比D,LV特HD点L具有更强的行为描述能

力

VHDL丰富的仿真语句和库函数,使得在设计的早期就能查 验设计系统的功能可行性,随时可对设计进行仿真模拟

VHDL语句的行为描述能力和程序结构决定了他具有支持大 规模设计的分解和已有设计的再利用功能

第二章 VHDL 语言

2.1 VHDL概述 2.2 VHDL的设计单元 2.3 VHDL的基本语法结构 2.4 VHDL语言程序的高级特性 2.5 实例解析

2.1 VHDL概述

VHDL 概述

VHDL的含义

VHSIC (Very High Speed Integrated Circuit) Hardware Description Language

Place/Route

Test Vectors

课件:第02讲 VHDL结构和语法要素

以半加器的设计为例,给出不同的描述方法

第2讲 VHDL结构与要素

§2. 1.4 配置

可以为实体指定或配属一个结构体.

CONFIGURATION 配置名 OF 实体名 IS FOR 选配结构体名 END FOR; END 配置名;

txwy

第2讲 VHDL结构与要素

§2.2 VHDL的语法要素

➢2.2.1 VHDL的词法元素 ➢2.2.2 VHDL的数据对象 ➢2.2.3 VHDL的数据类型 ➢2.2.4 VHDL的操作符

std_logic_vector

CONV_INTEGER(A)

由signed\unsigned转为integer

Std_logic_unsi gned

CONV_INTEGER(A)

由std_logic_vector转为 integer

txwy

第2讲 VHDL结构与要素

§2.2.4 VHDL的操作符

txwy

第2讲 VHDL结构与要素

描述方式

优点

缺点

适用场合

结构化 描述

数据流 描述 行为 描述

txwy

连接关系 电路不易理解、 清晰,电路 繁琐、复杂 模块化清晰

布尔函数 不易描述复杂电 定义明白 路,修改不易

电路层次 化设计

小门数 设计

电路特性 清楚明了

进行综合效率 大型复杂的电

相对较低

路模块设计

•architecture rt1 of var is •begin •process •variable a,b : std_logic; •begin • a:=b; • b:=a; •end process; •end architecture rtl;

第2-2讲VHDL语言的基本结构

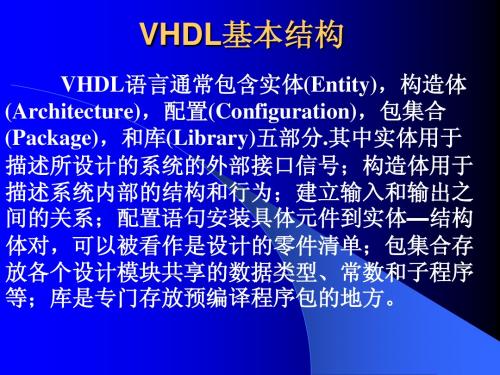

第2-2讲VHDL语言的基本结构第2-2讲VHDL语言的基本结构EDA技术实用教程第2-2讲VHDL语言的基本结构第2-2讲VHDL语言的基本结构VHDL源文件基本格式实体(Entity)五个部分结构体(Architecture) 配置(Configuration) 程序包(Package) 库(Library)可选第2-2讲VHDL语言的基本结构VHDL源文件基本格式__ 库名; USE 库名.程序包名.; ENTITY 实体名IS PORT(。

); END 实体名; --库--程序包--实体__CTURE 结构体名OF 实体名(。

) END 结构体名;--结构体第2-2讲VHDL语言的基本结构例:4选1数据选择器__ IEEE; --库USE IEEE.STD_LOGIC_1164.ALL; --程序包ENTITY ex2 IS --实体PORT(i0,i1,i2,i3,a,b:IN STD_LOGIC; q:OUT STD_LOGIC); END ex2;__CTURE ex2_a OF ex2 IS --结构体SIGNAL sel:STD_LOGIC_VECTOR(1 DOWNTO 0); BEGIN sel=b q= i0 WHEN sel=“00” ELSE i1 WHEN sel=“01” ELSE i2 WHEN sel=“10” ELSE i3 WHEN sel=“11” ELSE x ; END ex2_a;第2-2讲VHDL语言的基本结构1、实体格式:ENTITY 实体名与程序文件名相同IS[__ ( 类属表);] [PORT ( 端口表);] END 实体名; 说明所设计的逻辑电路的输入输出信号及其特性(输入、输出、双向) 第2-2讲VHDL语言的基本结构2选1多路选择器的VHDL实体描述ENTITY mux21a IS PORT( a, b : IN BIT ; s : IN BIT; y : OUT BIT ) ; END mux21a ;实体第2-2讲VHDL语言的基本结构PORT(端口)说明PORT说明语句是对一个设计实体界面的说明及对设计实体与外部电路的接口通道的说明,其中包括对每一接口的输入输出模式和数据类型的定义。