DDS_PLL短波频率合成器设计

射频前端设计中的频率合成器调节方法

射频前端设计中的频率合成器调节方法在射频前端设计中,频率合成器是非常重要的部件,它负责产生稳定的输出信号以满足系统的频率要求。

频率合成器的调节方法对于整个系统的性能和稳定性都至关重要。

下面将介绍几种常见的频率合成器调节方法。

1. 直接数字频率合成器(Direct Digital Synthesizer,DDS):DDS是一种采用数字方式直接合成频率的技术,具有快速调节、低相位噪声和高频率分辨率等优点。

通过控制DDS的相位累加器和频率控制字,可以实现对频率的精确调节。

DDS在射频前端设计中应用广泛,特别是在需要频率快速切换和精确控制的应用中。

2. 锁相环(Phase Locked Loop,PLL):PLL是一种经典的频率合成器调节方法,通过比较参考信号和反馈信号的相位差来调节输出频率,从而实现频率的稳定。

PLL在射频前端设计中常用于产生稳定的局部振荡频率或时钟信号,特别是在无线通信系统中广泛应用。

3. 频率合成器电路的调谐器:频率合成器电路的调谐器可以通过改变电路中的电感或电容来调节输出频率。

调谐器一般采用电容二极管或压控振荡器(Voltage Controlled Oscillator,VCO)来实现频率的调节,通过改变电压或电流来改变频率。

调谐器的优点是调节范围大、响应速度快,适用于一些频率跨度比较大的应用。

4. 数字控制的晶体振荡器(Digitally Controlled Crystal Oscillator,DCXO):DCXO是一种结合了晶体振荡器和数字控制技术的频率合成器调节方法。

通过控制DCXO内部的数字逻辑电路,可以实现对晶体振荡器的频率调节,提高了频率稳定性和精度。

DCXO广泛应用于高性能无线通信系统和频谱分析仪等领域。

总的来说,对于射频前端设计中的频率合成器调节方法,选择合适的调节方式对系统性能至关重要。

不同的应用场景需要选择合适的调节方法,根据频率要求、调节范围、稳定性和成本等因素进行综合考虑。

DDS激励PLL方式的频率合成器设计

科技与创新┃Science and Technology & Innovation·120·文章编号:2095-6835(2016)11-0120-02DDS 激励PLL 方式的频率合成器设计武志敏(河北诺亚人力资源开发有限公司,河北 石家庄 050081)摘 要:DDS+PLL 是目前频率合成技术的常用组合方式之一。

首先就DDS+PLL 的几种常用合成方式的特点进行了简单介绍,然后重点利用DDS 激励PLL 的方式,实现了一种低杂散低相噪的频率合成器的设计。

在自己的工作中证明了该方案的可实现性。

关键词:DDS ;PLL ;低杂散;低相位噪声;频率合成器中图分类号:TN97 文献标识码:A DOI :10.15913/ki.kjycx.2016.11.120现代通信技术的发展迅猛,使得电子对抗领域对频率源的准确度、换频时间以及杂散相位噪声等技术指标的要求越来越高。

一般我们经常使用DDS+PLL 的方法来实现高频率、小步进、低相噪的频率合成器设计。

以下是对DDS+PLL 的常见组合方式作一简介。

1 DDS+PLL 的频率合成方式 1.1 DDS 内插于PLL这种方式是把DDS 看作分频器插入PLL 。

正是因为DDS 的频率的分辨率是非常高的,因而可以实现宽频带、小步进频率的合成。

但是因为DDS 还可实现小数分频,所以会有部分频段出现杂散现象。

1.2 DDS 倍频于PLL此种方式是将DDS 作为PLL 倍频的参考信号,PLL 就成了N 倍频环。

此方式的优点是:电路设计简单,可以得到较高的频率输出。

因而适合应用在相对杂散、指标要求不是很高的分机以及系统中。

缺点是:因为PLL 用于直接倍频,所以在环路噪声带宽内的输出信号,相位噪声以及杂散指标,都将恶化20 dB 。

1.3 DDS 和PLL 直接混频此方式是将PLL 信号作为本振信号,将DDS 信号做上变频、混频后,再通过一级带通滤波器将信号输出。

基于DDS驱动PLL结构的Ka波段频率合成器

基于DDS驱动PLL结构的Ka波段频率合成器摘要:随着通信技术与信息技术的不断发展,为了使频率资源能够得到充分的应用,现代通信、雷达以及导航系统等,其工作频率已逐渐由微波波段向毫米波波段发展,而毫米波频率合成器作为这些系统的主要部分,其性能好坏与系统的整体性能息息相关。

另外,随着上述各系统的工作频段逐渐向毫米波波段发展,毫米波频率合成器的需求也得到了急剧的增长。

文章将介绍一种单片机控制的主要由直接数字频率合成器(DDS)、锁相环(PLL)以及倍频器等组成的频率合成技术来实现Ka波段频率合成器的方案,以及其电路仿真的设计。

关键词:Ka波段频率合成器;DDS;PLL;相位噪声;间接模拟式频率合成法毫米波频率合成器在雷达、制导、电子对抗、毫米波通信以及遥感遥测等领域得到了广泛的应用,而其性能的好坏也直接影响着整个系统的性能。

获得高性能毫米波频率源的一种重要方法就是直接模拟式频率合成法,而采用该方式来获取高性能毫米波频率合成器的缺点是体积大、设备较为复杂、价格昂贵。

为了解决这些问题,在数字锁相集成器件出现以后,研究出了一种锁相式频率合成器,然而在需要窄频率步进时,环路带宽的需要又降低了,从而导致锁定时间变长,因而不能满足快速跳频的要求。

之后,由于DDS的出现得以这一问题的解决,可同时又伴随着另外的一些问题,例如输出频率上限较低、带宽内杂散大等。

本文介绍的通过单片机控制的直接数字频率合成器(DDS)、锁相环(PLL)以及倍频器等组成的频率合成技术能够很好地解决上述问题。

下面,根据实际工程应用中毫米波雷达对频率源的技术要求,采用单片机控制的直接数字频率合成器(DDS)、锁相环(PLL)、倍频器等组成的频率合成技术对该频率合成器提出了设计方案,并对电路进行仿真设计与分析。

1 技术指标Ka波段频率合成器的基本电气指标主要包括以下几个方面:频率分辨率:不小于 1 MHz;相位噪声不大于—100dBc/Hz@1kHz,不大于—106dBc/Hz@10kHz;杂散抑制不大于—60 dBc;跳频时间不大于50 us。

DDS信号发生器设计

DDS信号发生器设计DDS(直接数字频率合成)信号发生器是一种数字技术制造高质量频率合成信号的装备。

本文将介绍DDS信号发生器的设计原理、关键技术和性能评估。

一、设计原理:DDS信号发生器的设计原理基于数字频率合成技术,其核心是数字信号处理器(DSP)和数字锁相环(PLL)。

DDS信号发生器通过频率控制字(FTW)和相位控制字(PTW)控制DDS芯片的输出频率、波形和相位。

在DDS芯片中,数字频率合成器通过数模转换器将较高的待合成信号转换为模拟信号,进而通过滤波器、放大器等模拟电路产生高质量的输出信号。

二、关键技术:1.高精度的频率合成:DDS信号发生器需要具备高精度的频率合成能力。

此需求需要DDS芯片具备较高的分辨率和较低的相位噪声。

分辨率是DDS芯片产生频率变化最小步进的能力,通常用位数来表示。

较高的分辨率可以确保DDS信号发生器输出的频率表现更加连续平滑。

相位噪声则与DDS芯片的时钟抖动、量化噪声等因素有关,较低的相位噪声能够保证信号在频谱中的纯净度。

2.高动态范围的输出:DDS信号发生器通常需要提供广泛的频率范围和大范围内的输出功率调节。

此需求需要DDS芯片具备高动态范围的输出能力。

动态范围包括频率动态范围和幅度动态范围。

频率动态范围是指DDS信号发生器能够合成的频率范围,幅度动态范围则指DDS信号发生器能够调节的输出功率范围。

通过优化DDS芯片的设计,可以提高输出的动态范围。

3.高速的输出信号更新:DDS信号发生器需要具备快速更新输出信号的能力。

通常,DDS芯片具备更高的时钟频率和更大的内存储存能力可以实现更高的输出信号更新速率。

高速更新输出信号可以保证DDS信号发生器能够满足实时调节信号的需求。

三、性能评估:DDS信号发生器的性能评估包括频率稳定度、相位噪声、调制信号质量等几个方面。

频率稳定度是指DDS信号发生器输出频率的稳定性,通常通过测量短期和长期的频率漂移来评估。

相位噪声则是度量DDS信号发生器输出信号相位纯净度的参数,使用杂散频谱测量方法和相位噪声密度谱评估。

DDS_PLL组合系统及实例

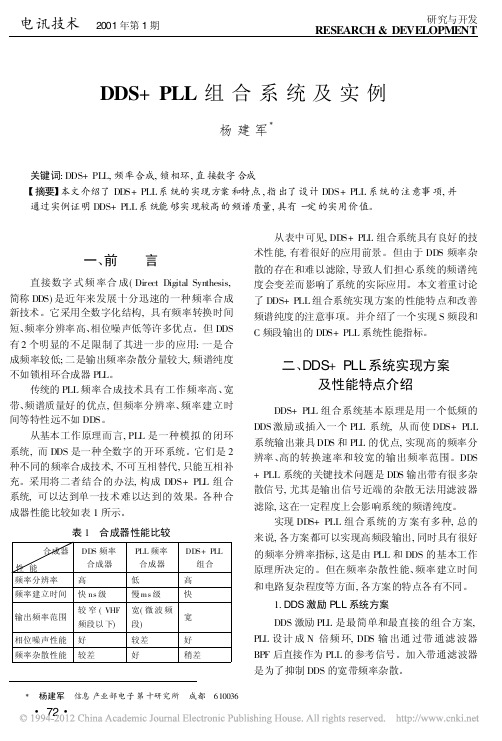

DDS+PLL组合系统及实例杨建军关键词:DDS+PLL,频率合成,锁相环,直接数字合成摘要 本文介绍了DDS+PLL系统的实现方案和特点,指出了设计DDS+PLL系统的注意事项,并通过实例证明DDS+PLL系统能够实现较高的频谱质量,具有一定的实用价值。

一、前 言直接数字式频率合成(Direct Digital Synthesis,简称DDS)是近年来发展十分迅速的一种频率合成新技术。

它采用全数字化结构,具有频率转换时间短、频率分辨率高、相位噪声低等许多优点。

但DDS有2个明显的不足限制了其进一步的应用:一是合成频率较低;二是输出频率杂散分量较大,频谱纯度不如锁相环合成器PLL。

传统的PLL频率合成技术具有工作频率高、宽带、频谱质量好的优点,但频率分辨率、频率建立时间等特性远不如DDS。

从基本工作原理而言,PLL是一种模拟的闭环系统,而DDS是一种全数字的开环系统。

它们是2种不同的频率合成技术,不可互相替代,只能互相补充。

采用将二者结合的办法,构成DDS+PLL组合系统,可以达到单一技术难以达到的效果。

各种合成器性能比较如表1所示。

表1 合成器性能比较性能合成器DDS频率合成器PLL频率合成器DDS+PLL组合频率分辨率高低高频率建立时间快ns级慢ms级快输出频率范围较窄(VHF频段以下)宽(微波频段)宽相位噪声性能好较差好频率杂散性能较差好稍差从表中可见,DDS+PLL组合系统具有良好的技术性能,有着很好的应用前景。

但由于DDS频率杂散的存在和难以滤除,导致人们担心系统的频谱纯度会变差而影响了系统的实际应用。

本文着重讨论了DDS+PLL组合系统实现方案的性能特点和改善频谱纯度的注意事项。

并介绍了一个实现S频段和C频段输出的DDS+PLL系统性能指标。

二、DDS+PLL系统实现方案及性能特点介绍DDS+PLL组合系统基本原理是用一个低频的DDS激励或插入一个PLL系统,从而使DDS+PLL 系统输出兼具DDS和PLL的优点,实现高的频率分辨率、高的转换速率和较宽的输出频率范围。

基于AD9858的DDS+PLL频率合成器

基于AD9858的DDS+PLL频率合成器

徐媛媛

【期刊名称】《实验科学与技术》

【年(卷),期】2009(007)005

【摘要】基于锁相频率合成技术(PLL)和直接数字频率合成技术(DDS)各有其优缺点,文章将两者结合,提出设计方案,并给出了主要的硬件电路设计,以产生符合预期要求的雷达信号.设计以AD9858为核心器件,输出DDS频率信号,为PLL提供参考输入信号.PLL中的鉴相器采用ADF4107,同时利用FPGA对两者进行方便的控制,可以获得较快的频率转换时间,相位噪声为-90 dBc/Hz且杂散优于-70 dBc的雷达信号.最终得到一个综合指标较高的系统.

【总页数】4页(P4-6,28)

【作者】徐媛媛

【作者单位】西南石油大学计算机科学学院,成都,610500

【正文语种】中文

【中图分类】TN74

【相关文献】

1.基于DDS+PLL频率合成器的设计 [J], 毛光军;邓仕鑫

2.基于AD9858的锁相环频率合成器电路的设计和实现 [J], 熊建林

3.基于DDS+PLL的低相噪频率合成器设计 [J], 宋雪莹;崔永俊;张祥;刘坤

4.基于AD9858的快速捷变频频率合成器的设计 [J], 夏永祥;郭德淳;余军;费元春

5.基于AD9858的小型宽带高分辨率频率合成器设计 [J], 张冰;钱时祥

因版权原因,仅展示原文概要,查看原文内容请购买。

DDS激励PLL频率合成器的设计与实现

DDS激励PLL频率合成器的设计与实现

王锐

【期刊名称】《信息技术》

【年(卷),期】2009(000)006

【摘要】介绍了DDS(直接数字式频率合成器)激励PLL(锁相环)频率合成器的主要设计过程和设计参数.它的硬件设计是由控制器部分、DDS部分和锁相环路部分三部分的设计组成.跳频序列选择m序列,将之写入到DDS的PIR(相位增量寄存器)中,完成软件控制DDS输出的频率跳变过程.给出了实测数据表明满足设计要求.

【总页数】4页(P197-200)

【作者】王锐

【作者单位】黑龙江省电子信息产品监督检验院,哈尔滨,150090

【正文语种】中文

【中图分类】TN914

【相关文献】

1.DDS激励PLL方式的频率合成器设计 [J], 武志敏;

2.DDS激励PLL高性能频率合成器设计 [J], 付钱华;易淼

3.基于DDS激励PLL宽带低杂散频率合成器 [J], 杨杰;杨光;蒋国琼;宋烨曦

4.基于DDS激励PLL宽带低杂散频率合成器 [J], 杨杰;杨光;蒋国琼;宋烨曦;

5.DDS激励PLL方式的频率合成器设计 [J], 武志敏

因版权原因,仅展示原文概要,查看原文内容请购买。

频率合成器设计

摘要频率合成器是利用一个或多个标准信号,通过各种技术途径产生大量离散频率信号的设备。

本文系统地阐述了锁相环频率合成器的基本工作原理,较深入地分析了锁相环路的组成和工作过程,建立其相位模型以及动态方程,并且对环路滤波器和各组成部分进行了详细的分析。

在此基础上,针对CD4046系统的技术特点,以集成数字锁相芯片为核心精心设计了频率合成电路,构成了多频点输出频率合成器。

为了改善环路的捕获性能,进一步抑制鉴相器输出电压中的载频分量和高频噪声,降低由VCO控制电压的不纯而引起的寄生输出以及其他各种杂散噪声,对环路滤波器进行了重点设计,合理选择和计算了环路的参数,进而使得集成锁相环频率合成电路的功能得到了充分发挥,为CD4046系统提供了良好的本振源。

关键词:频率合成器锁相环路CD4046目录引言 (3)第一章频率合成基本原理 (4)1.1 频率合成的概念 (4)1.2 频率合成器的主要技术指标 (5)1.3 锁相频率合成器 (5)第二章锁相环路的基本工作原理和CD4046的介绍 (6)2.1 锁相环路的工作原理 (6)2.2 锁相环路各组成部分的作用 (6)2.3 数字式锁相环路CD4046 (7)2.4 CD4046的介绍 (8)2.5 CD4046工作原理 (9)2.6 CD4046典型应用电路 (9)第三章频率合成器的设计与制作 (11)3.1 实验的设计指标和要求 (11)3.2 设计步骤 (11)3.3 设计电路图 (12)3.4 电路板制作 (12)总结 (14)参考文献 (15)引言频率合成是以一个或少量的高准确度和高稳定度的标准频率作为参考频率,由此导出多个或大量的输出频率,这些输出频率的准确度与稳定度与参考频率是一致的。

频率合成在通信、雷达、测控、仪器仪表等电子系统中有广泛的应用,频率合成器有直接式频率合成器、直接数字式频率合成器及锁相频率合成器三种基本模式。

前两种属于开环系统,具有频率转换时间短,分辨率较高等优点。

数字频率合成器的设计

数字频率合成器的设计频率合成是通信、测量系统中常用的一种技术,它是将一个或若干个高稳定度和高准确度的参考频率经过各种处理技术生成具有同样稳定度和准确度的大量离散频率的技术。

频率合成的方法很多,可分为直接式频率合成器、间接式频率合成器、直接式数字频率合成器( DDS)。

直接合成法是通过倍频器、分频器、混频器对频率进行加、减、乘、除运算,得到各种所需频率。

该方法频率转换时间快(小于100ns)。

锁相式频率合成器是利用锁相环(PLL)的窄带跟踪特性来得到不同的频率。

该方法结构简化、便于集成,且频谱纯度高,目前使用比较广泛。

直接数字频率合成器(Direct Digital Frequency Synthesis简称: DDS)是一种全数字化的频率合成器,由相位累加器、波形ROM,D/A转换器和低通滤波器构成,DDS技术是一种新的频率合成方法,它具有频率分辨率高、频率切换速度快、频率切换时相位连续、输出相位噪声低和可以产生任意波形等优点。

但合成信号频率较低、频谱不纯、输出杂散等。

这里将重点研究锁相式频率合成器。

4.1 数字频率合成器的设计任务利用锁相环和中小规模集成电路设计并制作一个数字频率合成器,设计要求如下: 1、设计指标:(1)要求频率合成器输出的频率范围fo?1kHz~99kHz;(2)频率间隔为?f?1kHz;(3)基准频率采用晶体振荡频率,要求用数字电路设计,频率稳定度应优于10;(4)数字显示输出频率;(5)频率调节采用计数方式,电路设计中要求有消抖动设计。

2、设计要求:(1)要求设计出数字锁相式频率合成器的电路。

(2)数字锁相式频率合成器的各部分参数计算和器件选择。

(3)数字锁相式频率合成器的仿真与调试。

3、制作要求:自行装配和调试,并能发现问题解决问题。

测试主要参数:包括晶体振荡器输出频率;1/M分频器输出频率;1/N可编程分频器的测试;锁相环的捕捉带和同步带测试。

4、设计报告的撰写写出设计与制作的全过程,具体要求详见4.4电子产品设计报告的撰写。

基于DDS+PLL频率合成器的设计与实现

基于DDS+PLL频率合成器的设计与实现

李俊俊;刘珩;吴丹

【期刊名称】《电子测量技术》

【年(卷),期】2009(0)4

【摘要】本文介绍了一种针对某跳频通信系统频率合成器的设计方案。

在ADS软件环境下进行设计及仿真,并对结果进行了系统分析。

设计方案经测试,该频率合成器可以输出200~270MHz范围内的高精度频率信号,频率步进为25kHz,跳频时间小于200μs,技术指标均达到预期要求。

能够满足VHF和UHF波段跳频系统的需求,具有较高的使用价值。

【总页数】5页(P26-30)

【关键词】直接数字频率合成器;锁相环;压控振荡器;低噪声放大器;低通滤波器【作者】李俊俊;刘珩;吴丹

【作者单位】中国农业大学信息与电气工程学院

【正文语种】中文

【中图分类】TN92

【相关文献】

1.基于DDS+PLL频率合成器的设计分析 [J], 张中天;

2.DDS+PLL高性能频率合成器的设计与实现 [J], 吴士云;叶建芳;石燚

3.基于DDS+PLL的低相噪频率合成器设计 [J], 宋雪莹;崔永俊;张祥;刘坤

4.基于DDS+PLL技术频率合成器的设计与实现 [J], 陈科;叶建芳;马三涵

5.DDS+PLL宽带频率合成器的设计与实现 [J], 宋庆华;徐正芳

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

20MHz

放军信息工程大学信息工程学院教授,主要研究方 向: 基于软件无线电的无线通信信号分析。 #$%&’( )(*+, *-%(’.$/%*’-FQ)ILGRH+ S0#:#== T5 8IL LI,+MLIJ+,U5 NH +- I VKI>)I,H -,)>HL, +L ,NH >HWIK,AHL, MX YLXMKAI,+ML ’?+HL?H I, 23! YLXMKAI,+ML BLV+LHHK+LV Z" L+[HK-+,U5 ,NH AI*MK KH-HIK?N >+KH?,+ML +- ,NH -+VLIJ IL> +LXMKAI,+ML WKM?H--+LV7 \H53+L>MLV S0#;E == T 8IL LI" ,+MLIJ+,U5 WKMXH--MK MX YLXMKAI,+ML BLV+LHHK+LV ZL+[HK-+,U MX 23!5 ,NH AI*MK KH-HIK?N >+KH?,+ML +- ,NH -MX,]IKH KI" >+M IL> ]+KHJH-- ?MAA)L+?I,+ML -+VLIJ WKM?H--+LV7 ("01112 河南郑州信息工程大学信息工程学院) 袁 伟 葛临东 34-,’(56%*’- 7-8*-++(*-8 /’99+8+, 4-,’(56%*’- 7-8*! -++(*-8 :-*;+(<*%= ’, >?#, @&+-8A&’$BC+-6-D "0EEEFDG&*-6H I$6-DJ+* K+D?*-.’-8 通信地址: 3"0EEEF 郑州 LEEM 信箱 N!0 分箱H 袁 伟

传感器与仪器仪表

您的论文得到相关企业家品评

!!"#$%% 短波频率合成器设计

! ""#$%&& ’()*+),-. #.,/0)123)( 45( 6’ 78,9

!郑州信息工程大学" 袁

伟 葛临东

Y uan ,W ei G e ,Li ndong

频频率定在 JE?KHI;<因此要求合成器能够提供 JJ?L" MN?KHI; 频段的频率作为本振信号; " 频率步进为 EI;; #频率稳定度达到 EOPQ; $杂波抑制优于 FO2R4; %相位噪声能够达到无线通信系统的一般要求 !在偏 离载频 EOSI; 时为PQO"PEEO2R4TI;"。 围绕着上述指标要求, 实际设计中我们重点考虑 下面几个问题。 -89:;<=:!()*+ ,-,./ *+ *01.02.2 13 2*+45++ 1). *++5.+ 430+*2./.2 E? 频段的设定 *0 2.+*60*06 1). )-/27-/. 4*/45*1 38 8/.95.04*.+ +:01).+*;./ 7*1) 频率合成系统的最终输出频率是从压控振荡器 &’’ -02 ##$< -+ 7.== -+ 13 ,/3>*2. 1). 43//.+,302*06 2.+*60 末端得到的, 因此压控振荡器的调谐范围必须能够覆 ,/*04*,=.+? @ +.1 38 +)3/17->. 8/.95.04*.+ +:01).+*;./ A-+.2 30 盖合成器的工作频段, 而且还要留有一定的富余以便 1). ,/*04*,=.+ B.01*30.2 -A3>. *+ *B,=.B.01.2? C*0-==: 1). 8.-+*! 在实际应用中进行调试。从降低设计难度角度出发实 A*=*1: *+ >./*8*.2 A: 1). .D,./*B.01-= /.+5=1+? >?@AB;C9,""#’ %&&’ D;?EF?G=@ H?9BIF:JBG 际中我们将合成器的输出划分成三个频段分别实现。 三 个 频 段 对 应 的 输 出 频 率 范 围 分 别 为 JJ?LHI; " JG?KHI;、 JG?KHI;"ME?KHI; 和 ME?KHI;"MN?KHI;。频 . ""#K%&& 结 构 频 率 合 成 器 概 述 段的电路结构图略可向作者索取。 ##$%&’’ 结构频率合成器具有输出信号频带宽、 这种 U3=,*11+ 共集电极三点振荡器的槽路是一个 频率分辨率高、 低相噪、 低杂散等优点, 广泛应用于电 并联谐振电路, 通过电感 ’ 或压控电容 UV@W 的变化来 子测量、 雷达、 通信系统等技术领域。它的设计思想 改变电路的振荡频率, 可调电容 UV 可以对电路状态进 是: 用 ##$ 的输出频率作为 &’’ 系统的参考信号, 通 行微调。不考虑分布参数的影响, 谐振电路的振荡频 过较高的鉴相频率来缩短 &’’ 的锁定时间,并利用 率 (8O) 和品质因数 (X() 可按下式计算: ##$ 的高频率分辨率来保证 &’’ 系统输出信号的频 ! 率间隔, 同时依靠 &’’ 的可编程变频能力拓宽频合系 统输出信号的频率范围,另外 &’’ 中的环路滤波对 " ##$ 输出信号中的杂散分量还有一定的抑制作用。用 这种方式实现的频率合成系统, 结构简单, 便于集成, # 易于控制。 式中 U(# 总谐振电容; UV@W$ 压变电容; UV$ 可调电 W ¡¢£¤ ¡¢£ ¡¢£¤ ¡¢£¤ 容; fout WYX$谐振电路等效并联电阻。之所以采用分段式 DDS ¡A ¢R PD ¡LPF ¡VCO VUZ 出于三方面的考虑: &有限的可变电容限制了频 率的调谐范围。我们知道频段的频率覆盖系数 (最高 ¡¢£¤ ¡¢£¤ ¡B ¢M 输出频率与最低输出频率之比) 大小决定了 VUZ 实现 的难易, 覆盖系数越大就要求变容管的容值变化范围 图 E ##$ 激励 &’’ 方式频率合成原理图 越大, 而大变化范围的变容管实现起来难度较大。’ 很宽的调谐范围要求压变电容必须通过一个很大的 4 ""#K%&& 结 构 频 率 合 成 器 设 计 电容耦合到谐振电路。这样会严重降低谐振电路的品 在某短波电台的研发项目中< 我们需要设计一款 质因数, 导致输出相位噪声的增大, 并给滤波器的设 高性能的频率合成系统作为电台前端的本振源, 对其 计带来很大困难。(调谐电压范围有限也会限制可变 主要技术指标有如下要求: !输出频率范围。该电台 电容的变化范围从而限制频率调谐范围。 主要针对 E?F"EGHI; 短波波段信号进行接收解调, 中 按照上面的结构来实现所划分的每个频段使实 际设计的难度得到了大大简化,图 J 中给出了 袁 伟: 硕士研究生

技 术 创 新

《 嵌入式系统应用精选 200 例》

中国自控网 !ht t p: / / www. aut ocont rol . cn 邮局订阅号 !82-946 120 元 / 年 P P EML

您的论文得到两院院士关注

中文核心期刊 《 微计算机信息》(测控自动化 )2005 年第 21 卷第 7-1 期

中国自控网 !ht t p: / / www. aut ocont rol . com . cn 元 年 邮局订阅Байду номын сангаас 120 / 82-946 !!! ! G G *$/

图!

从谱图中我们看出第一个镜像分量 A8,GA001 最靠 近输出信号且幅度最大。在时钟频率确定的情况下, 为了降低 0HC 后低通滤波器的制作难度应尽量降低 001 的输出频率,使该镜像分量远离滤波器的带宽。 但 001 输出频率又不能选择过低, 那样的话要满足合 成器的输出范围, 就要求增大 ,33 的分频比。对于一 个分频比为 6 的标准 ,33, 由于其倍频作用, 在闭环 带宽内相位噪声将增加 !/IJK6?@, 如果分频比 6 增大 会使输出相位噪声恶化, 带内部分杂散分量的能量也 会增加。而且 ,33 参考频率的降低, 也会降低锁相环 的锁定速度。

电话 !010-62132436 "62192616 #T / F$

《 P LC 技术应用 200 例》

传感器与仪器仪表

您的论文得到相关企业家品评

遵照上述设计原则, 以 !" 公司的 !"#$%& (""’) 和 ()*+,-) 公司的 ./0&1& (233) 为核心, 我们设计了 一套 ""’4233 结构频率合成器,其功能框图如图 % 所示:

短 ,33 的锁定时间, 还要尽量提高鉴相频率。,33 鉴 相频率的选择也是设计人员需要精心权衡的一个参 数。设计中可以按下面的经验公式来估算环路捕捉时 间: 它的取值越高, 捕捉时间越短。 A,0 为鉴相频率, .5 芯片选型 选择合成器主功能模块(001 芯片和 ,33 芯片) 的基本原则是要满足合成器的设计指标, 其中首要的 两个指标是输出频率范围和频率分辨率, 所以选择芯 片时应该首先考虑满足这两项指标。其次选择芯片还 需要考虑芯片的内部结构对输出的影响,选择 B9% 表容量较大、 0C8 位数较多的 001 芯片和线性性能 较好的 ,33 芯片可以降低输出信号中的杂散分量, 提 高频谱纯度。此外根据实际情况还应尽可能选择功耗 小、 成本低的芯片。 另外在制作频率合成器的过程中还应注意以下 两点: !001 输入时钟的选择。主要考虑两方面因素: 一是时钟频率的大小, 受限于 001 芯片允许的最高工 作频率;二是时钟信号的稳定度, 0012,33 结构频率 合成器输出信号的频率稳定度等同于 001 时钟信号 的稳定度D 因此要根据合成器对稳定度的要求选择合 适的时钟。 ’根据输出频率范围选择合适的 001 输出频率 和 ,33 的分频比。 001 信号是由正弦波的离散采样值 的数字量经 0EC 转换为阶梯形模拟波形的, 当时钟频 率为 A8,, 输出正弦波的频率为 A001 时, 存在着以采样频 率为折叠频率的一系列镜像频率分量, 这些镜像频率 值为 ;A8,"A001D它们的幅度沿 1<;=F>EF 包络滚降, 频率如 图 ! 所示。