Generating Minimal k-Vertex Connected Spanning Subgraphs

Tektronix MDO3000 Series 数字多功能作业仪用户指南说明书

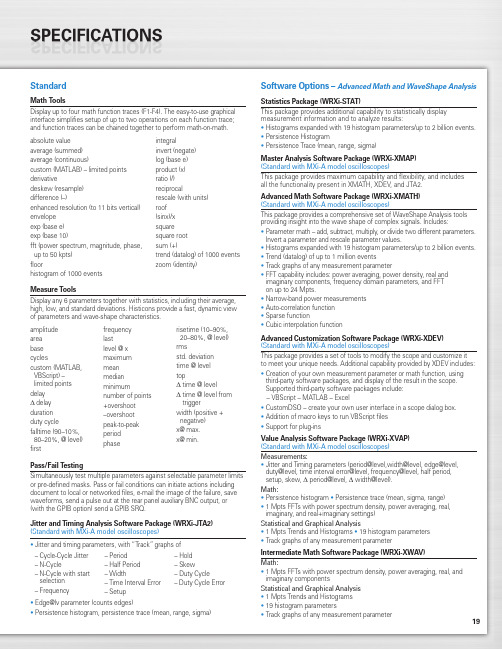

19StandardMath ToolsDisplay up to four math function traces (F1-F4). The easy-to-use graphical interface simplifies setup of up to two operations on each function trace;and function traces can be chained together to perform math-on-math.absolute value integralaverage (summed)invert (negate)average (continuous)log (base e)custom (MATLAB) – limited points product (x)derivativeratio (/)deskew (resample)reciprocaldifference (–)rescale (with units)enhanced resolution (to 11 bits vertical)roof envelope (sinx)/x exp (base e)square exp (base 10)square root fft (power spectrum, magnitude, phase,sum (+)up to 50 kpts) trend (datalog) of 1000 events floorzoom (identity)histogram of 1000 eventsMeasure ToolsDisplay any 6 parameters together with statistics, including their average,high, low, and standard deviations. Histicons provide a fast, dynamic view of parameters and wave-shape characteristics.Pass/Fail TestingSimultaneously test multiple parameters against selectable parameter limits or pre-defined masks. Pass or fail conditions can initiate actions including document to local or networked files, e-mail the image of the failure, save waveforms, send a pulse out at the rear panel auxiliary BNC output, or (with the GPIB option) send a GPIB SRQ.Jitter and Timing Analysis Software Package (WRXi-JTA2)(Standard with MXi-A model oscilloscopes)•Jitter and timing parameters, with “Track”graphs of •Edge@lv parameter (counts edges)• Persistence histogram, persistence trace (mean, range, sigma)Software Options –Advanced Math and WaveShape AnalysisStatistics Package (WRXi-STAT)This package provides additional capability to statistically display measurement information and to analyze results:• Histograms expanded with 19 histogram parameters/up to 2 billion events.• Persistence Histogram• Persistence Trace (mean, range, sigma)Master Analysis Software Package (WRXi-XMAP)(Standard with MXi-A model oscilloscopes)This package provides maximum capability and flexibility, and includes all the functionality present in XMATH, XDEV, and JTA2.Advanced Math Software Package (WRXi-XMATH)(Standard with MXi-A model oscilloscopes)This package provides a comprehensive set of WaveShape Analysis tools providing insight into the wave shape of complex signals. Includes:•Parameter math – add, subtract, multiply, or divide two different parameters.Invert a parameter and rescale parameter values.•Histograms expanded with 19 histogram parameters/up to 2 billion events.•Trend (datalog) of up to 1 million events•Track graphs of any measurement parameter•FFT capability includes: power averaging, power density, real and imaginary components, frequency domain parameters, and FFT on up to 24 Mpts.•Narrow-band power measurements •Auto-correlation function •Sparse function• Cubic interpolation functionAdvanced Customization Software Package (WRXi-XDEV)(Standard with MXi-A model oscilloscopes)This package provides a set of tools to modify the scope and customize it to meet your unique needs. Additional capability provided by XDEV includes:•Creation of your own measurement parameter or math function, using third-party software packages, and display of the result in the scope. Supported third-party software packages include:– VBScript – MATLAB – Excel•CustomDSO – create your own user interface in a scope dialog box.• Addition of macro keys to run VBScript files •Support for plug-insValue Analysis Software Package (WRXi-XVAP)(Standard with MXi-A model oscilloscopes)Measurements:•Jitter and Timing parameters (period@level,width@level, edge@level,duty@level, time interval error@level, frequency@level, half period, setup, skew, Δ period@level, Δ width@level).Math:•Persistence histogram •Persistence trace (mean, sigma, range)•1 Mpts FFTs with power spectrum density, power averaging, real, imaginary, and real+imaginary settings)Statistical and Graphical Analysis•1 Mpts Trends and Histograms •19 histogram parameters •Track graphs of any measurement parameterIntermediate Math Software Package (WRXi-XWAV)Math:•1 Mpts FFTs with power spectrum density, power averaging, real, and imaginary componentsStatistical and Graphical Analysis •1 Mpts Trends and Histograms •19 histogram parameters•Track graphs of any measurement parameteramplitude area base cyclescustom (MATLAB,VBScript) –limited points delay Δdelay duration duty cyclefalltime (90–10%, 80–20%, @ level)firstfrequency lastlevel @ x maximum mean median minimumnumber of points +overshoot –overshoot peak-to-peak period phaserisetime (10–90%, 20–80%, @ level)rmsstd. deviation time @ level topΔ time @ levelΔ time @ level from triggerwidth (positive + negative)x@ max.x@ min.– Cycle-Cycle Jitter – N-Cycle– N-Cycle with start selection – Frequency– Period – Half Period – Width– Time Interval Error – Setup– Hold – Skew– Duty Cycle– Duty Cycle Error20WaveRunner WaveRunner WaveRunner WaveRunner WaveRunner 44Xi-A64Xi-A62Xi-A104Xi-A204Xi-AVertical System44MXi-A64MXi-A104MXi-A204MXi-ANominal Analog Bandwidth 400 MHz600 MHz600 MHz 1 GHz 2 GHz@ 50 Ω, 10 mV–1 V/divRise Time (Typical)875 ps500 ps500 ps300 ps180 psInput Channels44244Bandwidth Limiters20 MHz; 200 MHzInput Impedance 1 MΩ||16 pF or 50 Ω 1 MΩ||20 pF or 50 ΩInput Coupling50 Ω: DC, 1 MΩ: AC, DC, GNDMaximum Input Voltage50 Ω: 5 V rms, 1 MΩ: 400 V max.50 Ω: 5 V rms, 1 MΩ: 250 V max.(DC + Peak AC ≤ 5 kHz)(DC + Peak AC ≤ 10 kHz)Vertical Resolution8 bits; up to 11 with enhanced resolution (ERES)Sensitivity50 Ω: 2 mV/div–1 V/div fully variable; 1 MΩ: 2 mV–10 V/div fully variableDC Gain Accuracy±1.0% of full scale (typical); ±1.5% of full scale, ≥ 10 mV/div (warranted)Offset Range50 Ω: ±1 V @ 2–98 mV/div, ±10 V @ 100 mV/div–1 V/div; 50Ω:±400mV@2–4.95mV/div,±1V@5–99mv/div,1 M Ω: ±1 V @ 2–98 mV/div, ±10 V @ 100 mV/div–1 V/div,±10 V @ 100 mV–1 V/div±**********/div–10V/div 1 M Ω: ±400 mV @ 2–4.95 mV/div, ±1 V @5–99 mV/div, ±10 V @ 100 mV–1 V/div,±*********–10V/divInput Connector ProBus/BNCTimebase SystemTimebases Internal timebase common to all input channels; an external clock may be applied at the auxiliary inputTime/Division Range Real time: 200 ps/div–10 s/div, RIS mode: 200 ps/div to 10 ns/div, Roll mode: up to 1,000 s/divClock Accuracy≤ 5 ppm @ 25 °C (typical) (≤ 10 ppm @ 5–40 °C)Sample Rate and Delay Time Accuracy Equal to Clock AccuracyChannel to Channel Deskew Range±9 x time/div setting, 100 ms max., each channelExternal Sample Clock DC to 600 MHz; (DC to 1 GHz for 104Xi-A/104MXi-A and 204Xi-A/204MXi-A) 50 Ω, (limited BW in 1 MΩ),BNC input, limited to 2 Ch operation (1 Ch in 62Xi-A), (minimum rise time and amplitude requirements applyat low frequencies)Roll Mode User selectable at ≥ 500 ms/div and ≤100 kS/s44Xi-A64Xi-A62Xi-A104Xi-A204Xi-A Acquisition System44MXi-A64MXi-A104MXi-A204MXi-ASingle-Shot Sample Rate/Ch 5 GS/sInterleaved Sample Rate (2 Ch) 5 GS/s10 GS/s10 GS/s10 GS/s10 GS/sRandom Interleaved Sampling (RIS)200 GS/sRIS Mode User selectable from 200 ps/div to 10 ns/div User selectable from 100 ps/div to 10 ns/div Trigger Rate (Maximum) 1,250,000 waveforms/secondSequence Time Stamp Resolution 1 nsMinimum Time Between 800 nsSequential SegmentsAcquisition Memory Options Max. Acquisition Points (4 Ch/2 Ch, 2 Ch/1 Ch in 62Xi-A)Segments (Sequence Mode)Standard12.5M/25M10,00044Xi-A64Xi-A62Xi-A104Xi-A204Xi-A Acquisition Processing44MXi-A64MXi-A104MXi-A204MXi-ATime Resolution (min, Single-shot)200 ps (5 GS/s)100 ps (10 GS/s)100 ps (10 GS/s)100 ps (10 GS/s)100 ps (10 GS/s) Averaging Summed and continuous averaging to 1 million sweepsERES From 8.5 to 11 bits vertical resolutionEnvelope (Extrema)Envelope, floor, or roof for up to 1 million sweepsInterpolation Linear or (Sinx)/xTrigger SystemTrigger Modes Normal, Auto, Single, StopSources Any input channel, External, Ext/10, or Line; slope and level unique to each source, except LineTrigger Coupling DC, AC (typically 7.5 Hz), HF Reject, LF RejectPre-trigger Delay 0–100% of memory size (adjustable in 1% increments, or 100 ns)Post-trigger Delay Up to 10,000 divisions in real time mode, limited at slower time/div settings in roll modeHold-off 1 ns to 20 s or 1 to 1,000,000,000 events21WaveRunner WaveRunner WaveRunner WaveRunner WaveRunner 44Xi-A 64Xi-A 62Xi-A104Xi-A 204Xi-A Trigger System (cont’d)44MXi-A64MXi-A104MXi-A204MXi-AInternal Trigger Level Range ±4.1 div from center (typical)Trigger and Interpolator Jitter≤ 3 ps rms (typical)Trigger Sensitivity with Edge Trigger 2 div @ < 400 MHz 2 div @ < 600 MHz 2 div @ < 600 MHz 2 div @ < 1 GHz 2 div @ < 2 GHz (Ch 1–4 + external, DC, AC, and 1 div @ < 200 MHz 1 div @ < 200 MHz 1 div @ < 200 MHz 1 div @ < 200 MHz 1 div @ < 200 MHz LFrej coupling)Max. Trigger Frequency with400 MHz 600 MHz 600 MHz 1 GHz2 GHzSMART Trigger™ (Ch 1–4 + external)@ ≥ 10 mV@ ≥ 10 mV@ ≥ 10 mV@ ≥ 10 mV@ ≥ 10 mVExternal Trigger RangeEXT/10 ±4 V; EXT ±400 mVBasic TriggersEdgeTriggers when signal meets slope (positive, negative, either, or Window) and level conditionTV-Composite VideoT riggers NTSC or PAL with selectable line and field; HDTV (720p, 1080i, 1080p) with selectable frame rate (50 or 60 Hz)and Line; or CUSTOM with selectable Fields (1–8), Lines (up to 2000), Frame Rates (25, 30, 50, or 60 Hz), Interlacing (1:1, 2:1, 4:1, 8:1), or Synch Pulse Slope (Positive or Negative)SMART TriggersState or Edge Qualified Triggers on any input source only if a defined state or edge occurred on another input source.Delay between sources is selectable by time or eventsQualified First In Sequence acquisition mode, triggers repeatedly on event B only if a defined pattern, state, or edge (event A) is satisfied in the first segment of the acquisition. Delay between sources is selectable by time or events Dropout Triggers if signal drops out for longer than selected time between 1 ns and 20 s.PatternLogic combination (AND, NAND, OR, NOR) of 5 inputs (4 channels and external trigger input – 2 Ch+EXT on WaveRunner 62Xi-A). Each source can be high, low, or don’t care. The High and Low level can be selected independently. Triggers at start or end of the patternSMART Triggers with Exclusion TechnologyGlitch and Pulse Width Triggers on positive or negative glitches with widths selectable from 500 ps to 20 s or on intermittent faults (subject to bandwidth limit of oscilloscope)Signal or Pattern IntervalTriggers on intervals selectable between 1 ns and 20 sTimeout (State/Edge Qualified)Triggers on any source if a given state (or transition edge) has occurred on another source.Delay between sources is 1 ns to 20 s, or 1 to 99,999,999 eventsRuntTrigger on positive or negative runts defined by two voltage limits and two time limits. Select between 1 ns and 20 sSlew RateTrigger on edge rates. Select limits for dV, dt, and slope. Select edge limits between 1 ns and 20 s Exclusion TriggeringTrigger on intermittent faults by specifying the normal width or periodLeCroy WaveStream Fast Viewing ModeIntensity256 Intensity Levels, 1–100% adjustable via front panel control Number of Channels up to 4 simultaneouslyMax Sampling Rate5 GS/s (10 GS/s for WR 62Xi-A, 64Xi-A/64MXi-A,104Xi-A/104MXi-A, 204Xi-A/204MXi-A in interleaved mode)Waveforms/second (continuous)Up to 20,000 waveforms/secondOperationFront panel toggle between normal real-time mode and LeCroy WaveStream Fast Viewing modeAutomatic SetupAuto SetupAutomatically sets timebase, trigger, and sensitivity to display a wide range of repetitive signalsVertical Find ScaleAutomatically sets the vertical sensitivity and offset for the selected channels to display a waveform with maximum dynamic range44Xi-A 64Xi-A 62Xi-A104Xi-A 204Xi-A Probes44MXi-A 64MXi-A104MXi-A 204MXi-AProbesOne Passive probe per channel; Optional passive and active probes available Probe System; ProBus Automatically detects and supports a variety of compatible probes Scale FactorsAutomatically or manually selected, depending on probe usedColor Waveform DisplayTypeColor 10.4" flat-panel TFT-LCD with high resolution touch screenResolutionSVGA; 800 x 600 pixels; maximum external monitor output resolution of 2048 x 1536 pixelsNumber of Traces Display a maximum of 8 traces. Simultaneously display channel, zoom, memory, and math traces Grid StylesAuto, Single, Dual, Quad, Octal, XY , Single + XY , Dual + XY Waveform StylesSample dots joined or dots only in real-time mode22Zoom Expansion TracesDisplay up to 4 Zoom/Math traces with 16 bits/data pointInternal Waveform MemoryM1, M2, M3, M4 Internal Waveform Memory (store full-length waveform with 16 bits/data point) or store to any number of files limited only by data storage mediaSetup StorageFront Panel and Instrument StatusStore to the internal hard drive, over the network, or to a USB-connected peripheral deviceInterfaceRemote ControlVia Windows Automation, or via LeCroy Remote Command Set Network Communication Standard VXI-11 or VICP , LXI Class C Compliant GPIB Port (Accessory)Supports IEEE – 488.2Ethernet Port 10/100/1000Base-T Ethernet interface (RJ-45 connector)USB Ports5 USB 2.0 ports (one on front of instrument) supports Windows-compatible devices External Monitor Port Standard 15-pin D-Type SVGA-compatible DB-15; connect a second monitor to use extended desktop display mode with XGA resolution Serial PortDB-9 RS-232 port (not for remote oscilloscope control)44Xi-A 64Xi-A 62Xi-A104Xi-A 204Xi-A Auxiliary Input44MXi-A 64MXi-A104MXi-A 204MXi-ASignal Types Selected from External Trigger or External Clock input on front panel Coupling50 Ω: DC, 1 M Ω: AC, DC, GND Maximum Input Voltage50 Ω: 5 V rms , 1 M Ω: 400 V max.50 Ω: 5 V rms , 1 M Ω: 250 V max. (DC + Peak AC ≤ 5 kHz)(DC + Peak AC ≤ 10 kHz)Auxiliary OutputSignal TypeTrigger Enabled, Trigger Output. Pass/Fail, or Off Output Level TTL, ≈3.3 VConnector TypeBNC, located on rear panelGeneralAuto Calibration Ensures specified DC and timing accuracy is maintained for 1 year minimumCalibratorOutput available on front panel connector provides a variety of signals for probe calibration and compensationPower Requirements90–264 V rms at 50/60 Hz; 115 V rms (±10%) at 400 Hz, Automatic AC Voltage SelectionInstallation Category: 300 V CAT II; Max. Power Consumption: 340 VA/340 W; 290 VA/290 W for WaveRunner 62Xi-AEnvironmentalTemperature: Operating+5 °C to +40 °C Temperature: Non-Operating -20 °C to +60 °CHumidity: Operating Maximum relative humidity 80% for temperatures up to 31 °C decreasing linearly to 50% relative humidity at 40 °CHumidity: Non-Operating 5% to 95% RH (non-condensing) as tested per MIL-PRF-28800F Altitude: OperatingUp to 3,048 m (10,000 ft.) @ ≤ 25 °C Altitude: Non-OperatingUp to 12,190 m (40,000 ft.)PhysicalDimensions (HWD)260 mm x 340 mm x 152 mm Excluding accessories and projections (10.25" x 13.4" x 6")Net Weight7.26kg. (16.0lbs.)CertificationsCE Compliant, UL and cUL listed; Conforms to EN 61326, EN 61010-1, UL 61010-1 2nd Edition, and CSA C22.2 No. 61010-1-04Warranty and Service3-year warranty; calibration recommended annually. Optional service programs include extended warranty, upgrades, calibration, and customization services23Product DescriptionProduct CodeWaveRunner Xi-A Series Oscilloscopes2 GHz, 4 Ch, 5 GS/s, 12.5 Mpts/ChWaveRunner 204Xi-A(10 GS/s, 25 Mpts/Ch in interleaved mode)with 10.4" Color Touch Screen Display 1 GHz, 4 Ch, 5 GS/s, 12.5 Mpts/ChWaveRunner 104Xi-A(10 GS/s, 25 Mpts/Ch in interleaved mode)with 10.4" Color Touch Screen Display 600 MHz, 4 Ch, 5 GS/s, 12.5 Mpts/Ch WaveRunner 64Xi-A(10 GS/s, 25 Mpts/Ch in interleaved mode)with 10.4" Color Touch Screen Display 600 MHz, 2 Ch, 5 GS/s, 12.5 Mpts/Ch WaveRunner 62Xi-A(10 GS/s, 25 Mpts/Ch in interleaved mode)with 10.4" Color Touch Screen Display 400 MHz, 4 Ch, 5 GS/s, 12.5 Mpts/Ch WaveRunner 44Xi-A(25 Mpts/Ch in interleaved mode)with 10.4" Color Touch Screen DisplayWaveRunner MXi-A Series Oscilloscopes2 GHz, 4 Ch, 5 GS/s, 12.5 Mpts/ChWaveRunner 204MXi-A(10 GS/s, 25 Mpts/Ch in Interleaved Mode)with 10.4" Color Touch Screen Display 1 GHz, 4 Ch, 5 GS/s, 12.5 Mpts/ChWaveRunner 104MXi-A(10 GS/s, 25 Mpts/Ch in Interleaved Mode)with 10.4" Color Touch Screen Display 600 MHz, 4 Ch, 5 GS/s, 12.5 Mpts/Ch WaveRunner 64MXi-A(10 GS/s, 25 Mpts/Ch in Interleaved Mode)with 10.4" Color Touch Screen Display 400 MHz, 4 Ch, 5 GS/s, 12.5 Mpts/Ch WaveRunner 44MXi-A(25 Mpts/Ch in Interleaved Mode)with 10.4" Color Touch Screen DisplayIncluded with Standard Configuration÷10, 500 MHz, 10 M Ω Passive Probe (Total of 1 Per Channel)Standard Ports; 10/100/1000Base-T Ethernet, USB 2.0 (5), SVGA Video out, Audio in/out, RS-232Optical 3-button Wheel Mouse – USB 2.0Protective Front Cover Accessory PouchGetting Started Manual Quick Reference GuideAnti-virus Software (Trial Version)Commercial NIST Traceable Calibration with Certificate 3-year WarrantyGeneral Purpose Software OptionsStatistics Software Package WRXi-STAT Master Analysis Software Package WRXi-XMAP (Standard with MXi-A model oscilloscopes)Advanced Math Software Package WRXi-XMATH (Standard with MXi-A model oscilloscopes)Intermediate Math Software Package WRXi-XWAV (Standard with MXi-A model oscilloscopes)Value Analysis Software Package (Includes XWAV and JTA2) WRXi-XVAP (Standard with MXi-A model oscilloscopes)Advanced Customization Software Package WRXi-XDEV (Standard with MXi-A model oscilloscopes)Spectrum Analyzer and Advanced FFT Option WRXi-SPECTRUM Processing Web Editor Software Package WRXi-XWEBProduct Description Product CodeApplication Specific Software OptionsJitter and Timing Analysis Software Package WRXi-JTA2(Standard with MXi-A model oscilloscopes)Digital Filter Software PackageWRXi-DFP2Disk Drive Measurement Software Package WRXi-DDM2PowerMeasure Analysis Software Package WRXi-PMA2Serial Data Mask Software PackageWRXi-SDM QualiPHY Enabled Ethernet Software Option QPHY-ENET*QualiPHY Enabled USB 2.0 Software Option QPHY-USB †EMC Pulse Parameter Software Package WRXi-EMC Electrical Telecom Mask Test PackageET-PMT* TF-ENET-B required. †TF-USB-B required.Serial Data OptionsI 2C Trigger and Decode Option WRXi-I2Cbus TD SPI Trigger and Decode Option WRXi-SPIbus TD UART and RS-232 Trigger and Decode Option WRXi-UART-RS232bus TD LIN Trigger and Decode Option WRXi-LINbus TD CANbus TD Trigger and Decode Option CANbus TD CANbus TDM Trigger, Decode, and Measure/Graph Option CANbus TDM FlexRay Trigger and Decode Option WRXi-FlexRaybus TD FlexRay Trigger and Decode Physical Layer WRXi-FlexRaybus TDP Test OptionAudiobus Trigger and Decode Option WRXi-Audiobus TDfor I 2S , LJ, RJ, and TDMAudiobus Trigger, Decode, and Graph Option WRXi-Audiobus TDGfor I 2S LJ, RJ, and TDMMIL-STD-1553 Trigger and Decode Option WRXi-1553 TDA variety of Vehicle Bus Analyzers based on the WaveRunner Xi-A platform are available.These units are equipped with a Symbolic CAN trigger and decode.Mixed Signal Oscilloscope Options500 MHz, 18 Ch, 2 GS/s, 50 Mpts/Ch MS-500Mixed Signal Oscilloscope Option 250 MHz, 36 Ch, 1 GS/s, 25 Mpts/ChMS-500-36(500 MHz, 18 Ch, 2 GS/s, 50 Mpts/Ch Interleaved) Mixed Signal Oscilloscope Option 250 MHz, 18 Ch, 1 GS/s, 10 Mpts/Ch MS-250Mixed Signal Oscilloscope OptionProbes and Amplifiers*Set of 4 ZS1500, 1.5 GHz, 0.9 pF , 1 M ΩZS1500-QUADPAK High Impedance Active ProbeSet of 4 ZS1000, 1 GHz, 0.9 pF , 1 M ΩZS1000-QUADPAK High Impedance Active Probe 2.5 GHz, 0.7 pF Active Probe HFP25001 GHz Active Differential Probe (÷1, ÷10, ÷20)AP034500 MHz Active Differential Probe (x10, ÷1, ÷10, ÷100)AP03330 A; 100 MHz Current Probe – AC/DC; 30 A rms ; 50 A rms Pulse CP03130 A; 50 MHz Current Probe – AC/DC; 30 A rms ; 50 A rms Pulse CP03030 A; 50 MHz Current Probe – AC/DC; 30 A rms ; 50 A peak Pulse AP015150 A; 10 MHz Current Probe – AC/DC; 150 A rms ; 500 A peak Pulse CP150500 A; 2 MHz Current Probe – AC/DC; 500 A rms ; 700 A peak Pulse CP5001,400 V, 100 MHz High-Voltage Differential Probe ADP3051,400 V, 20 MHz High-Voltage Differential Probe ADP3001 Ch, 100 MHz Differential Amplifier DA1855A*A wide variety of other passive, active, and differential probes are also available.Consult LeCroy for more information.Product Description Product CodeHardware Accessories*10/100/1000Base-T Compliance Test Fixture TF-ENET-B †USB 2.0 Compliance Test Fixture TF-USB-B External GPIB Interface WS-GPIBSoft Carrying Case WRXi-SOFTCASE Hard Transit CaseWRXi-HARDCASE Mounting Stand – Desktop Clamp Style WRXi-MS-CLAMPRackmount Kit WRXi-RACK Mini KeyboardWRXi-KYBD Removable Hard Drive Package (Includes removeable WRXi-A-RHD hard drive kit and two hard drives)Additional Removable Hard DriveWRXi-A-RHD-02* A variety of local language front panel overlays are also available .† Includes ENET-2CAB-SMA018 and ENET-2ADA-BNCSMA.Customer ServiceLeCroy oscilloscopes and probes are designed, built, and tested to ensure high reliability. In the unlikely event you experience difficulties, our digital oscilloscopes are fully warranted for three years, and our probes are warranted for one year.This warranty includes:• No charge for return shipping • Long-term 7-year support• Upgrade to latest software at no chargeLocal sales offices are located throughout the world. Visit our website to find the most convenient location.© 2010 by LeCroy Corporation. All rights reserved. Specifications, prices, availability, and delivery subject to change without notice. Product or brand names are trademarks or requested trademarks of their respective holders.1-800-5-LeCroy WRXi-ADS-14Apr10PDF。

JUMO 402050压力传感器用户指南说明书

Data Sheet 402050Page 1/7JUMO dTRANS p31Pressure transmitter for elevated media temperaturesGeneral applicationPressure transmitters are used for measuring the relative (gauge) and absolute pressures in li-quids and gases. The pressure transmitter operates on the piezo-resistive measuring principle.The pressure is converted into an electrical signal.Type 402050Technical dataReference conditions To DIN 16086 and IEC 770/5.3Ranges See order details Overload limit All ranges 3× full scale Bursting pressureAll ranges 4× full scaleParts in contact with medium Standard: stainless steel 316Ti/316LOutput0to 20mA, two-wire (output 402)Burden ≤(U B -12V)÷0.02A 4to 20mA, two-wire (output 405)Burden ≤(U B -10V)÷0.02A 4to 20mA, three-wire (output 406)Burden ≤(U B -12V)÷0.02A 0,5to 4,5V, three-wire (output 412)Burden ≥50k Ω0to 10V, three-wire (output 415)Burden ≥10k Ω1to 5V, three-wire (output 418)Burden ≥10k Ω1to 6V, three-wire (output 420)Burden ≥10k ΩBurden error <0.5% max.Zero offset ≤0.3% MSP (measuring span)Thermal hysteresis ≤±0.5% MSP (within compensated temperature range)Ambient temperature error Within range 0to 100°C (compensated temperature range)Zero≤0.02%/K typical, ≤0.04%/K max.Measuring span≤0.02%/K typical, ≤0.04%/K max.Deviation from characteristic ≤0.5% MSP (limit point setting)For basic type extension 023≤0.2% MSP (limit point setting)Hysteresis ≤0.1% MSPData Sheet 402050Page 2/7Repeatability≤0.05% MSPResponse timeCurrent output0to20mA, two-wire (output 402)≤3msec max.4to20mA, two-wire (output 405)≤3msec max.4to20mA, three-wire (output 406)≤3msec max.Voltage output0,5to4,5V, three-wire (output 412)≤10msec max.0to10V, three-wire (output 415)≤10msec max.1to5V, three-wire (output 418)≤10msec max.1to6V, three-wire (output 420)≤10msec max.Stability over 1 year≤0.5% MSPVoltage supply a0to20mA, two-wire (output 402)DC11,5to30V4to20mA, two-wire (output 405)DC10to30V4to20mA, three-wire (output 406)DC11,5to30V0,5to4,5V, three-wire (output 412)DC5V0to10V, three-wire (output 415)DC11,5to30V1to5V, three-wire (output 418)DC10to30V1to6V, three-wire (output 420)DC10to30VMax. current drawn Approx. 25mAVoltage supply influence≤0.02%/V, nominal voltage supply DC24Vratiometric with voltage supply DC5V (±0.5V)-20to+125︒CPermissible ambient temperature(max. housing temperature)Storage temperature-40to+125︒CPermissible temperature of medium-30to+200°CElectromagnet compatibility EN 61326Interference emission Class BInterference immunity Industrial requirementsMechanical shock b100g/1msecMechanical vibration c Max. 20g at 15to2000HzProtection type dTerminal box (electrical connection 12)IP67Round plug M12×1IP67(electrical connection 36)Cable socket (electrical connection 61)IP65 (connecting cable diameter min. 5mm, max. 7mm)Housing Stainless steel, mat. ref. 1.4301Polycarbonate GFPressure connection See order details; other connections on requestElectrical connection See order detailsTerminal box (electrical connection 12)4-pole, PVC cable, length 2m, other length on request4-poleRound plug M12×1(electrical connection 36)Cable socket (electrical connection 61)To DIN EN 175301-803, conductor cross-section upt ot max. 1.5mm2Nominal position AnyWeight200ga Ripple: The voltage spikes must not go above or below the values specified for the supply.b DIN IEC 68-2-27c DIN IEC 68-2-6d EN 60529Data Sheet 402050Page 3/7Connection diagramThe connection diagram in the data sheet provides preliminary information about the connection options. For the electrical connection only use the installation instructions or the operating manual. The knowledge and the correct technical execution of the safety information/instructions contained in these documents are mandatory for installation, electrical connection, startup, and for safety during operation.ConnectionTerminal assignment 123661Fixed cableRound plug M12×1Cable socket Voltage supply DC 10to 30V DC 11,5to 30V DC 5V White Grey1+3- 1 L+2 L-Output 1to 6V 0to 10V 0,5to 4,5VGrey Yellow 3-4+ 2 -3 +Output 4to 20mA, two-wireWhite Grey 1+3- 1 +2 -Proportional current 4to 20mA in voltage supplyOutput 0(4)to 20mA, three-wireGrey Yellow3-4+2 -3 +Protection conductor Screen Black2Caution:Earth device(pressure connection and/oror screen)!Data Sheet 402050Page 4/7DimensionsElectrical connection Process conntection, front-flushBO-ringBO-ringData Sheet 402050Page 5/7Process connection DNØD1ØD2ØD3ØD4L1L2ProcessconnectionDNDIN 32676DN(Zoll)Nominal SizeISO 2852ØD1ØD26032036.530RD44×1/6541321612201227.534 604254435RD52×1/663151512.7605325041RD58×1/67017.2606405648RD65×1/67821.36075068.561RD78×1/6921622613251“2543.550.532 1.5“33.74038616502“4056.56451see data sheet 409711Data Sheet 402050Page 6/7Order details(1)Basic type402050/000JUMO dTRANS p31 – Pressure transmitter for elevated media temperatures402050/023JUMO dTRANS p31 – Pressure transmitter for elevated media temperatures, reduced deviation from characteristic a 402050/999JUMO dTRANS p31 – Pressure transmitter for elevated media temperatures, special version(2)Input4540to1bar relative pressure4550to1,6bar relative pressure4560to2,5bar relative pressure4570to4bar relative pressure4580to6bar relative pressure4590to10bar relative pressure4600to16bar relative pressure4610to25bar relative pressure4620to40bar relative pressure4630to60bar relative pressure478-1to0bar relative pressure479-1to+0,6bar relative pressure480-1to+1,5bar relative pressure481-1to+3bar relative pressure482-1to+5bar relative pressure483-1to+9bar relative pressure484-1to+15bar relative pressure485-1to+24bar relative pressure4880to1bar absolute pressure4890to1,6bar absolute pressure4900to2,5bar absolute pressure4910to4 bar absolute pressure4920to6bar absolute pressure4930to10bar absolute pressure4940to16bar absolute pressure4950to25bar absolute pressure998Sondermessbereich absolute pressure999Sondermessbereich relative pressure(3)Output4020to20mA, three-wire4054to20mA, two-wire4064to20mA, three-wire4120,5to4,5V, three-wire4150to10V, three-wire4181to5V, three-wire4201to6V, three-wire(4)Process connection550Aseptic to DIN 11864-1A, DN20551Aseptic to DIN 11864-1A, DN25552Aseptic to DIN 11864-1A, DN32553Aseptic to DIN 11864-1A, DN40554Aseptic to DIN 11864-1A, DN50570G11/2 front-flush, DIN EN ISO 228-1571G3/4 front-flush, DIN EN ISO 228-1575G3/4 front-flush with double sealData Sheet 402050Page 7/7576G1 with double seal584SMS, DN1585SMS, DN11/2586SMS, DN2603Taper socket with grooved union nut DN20, to DIN 11851 (dairy pipe fitting)604Taper socket with grooved union nut DN25, to DIN 11851 (dairy pipe fitting)605Taper socket with grooved union nut DN32, to DIN 11851 (dairy pipe fitting)606Taper socket with grooved union nut DN40, to DIN 11851 (dairy pipe fitting)607Taper socket with grooved union nut DN50, to DIN 11851 (dairy pipe fitting)612Clamping socket (clamp) DN10, DN15, DN20b to DIN 32676613Clamping socket (clamp) DN25, DN40b to DIN 32676616Clamping socket (clamp) DN50 (2“)b to DIN 32676619Clamping socket (clamp) DN15 (3/4“)b to DIN 32676623Small flange DN25, to DIN 28403652Tank connection with grooved union nut DN25661Clamping flange (DRD), Ø65mm684VARIVENT® connection, DN15/10685VARIVENT® connection, DN32/25686VARIVENT® connection, DN50/40997JUMO-PEKA with EHEDG certification c(5)Process connection material20CrNi (stainless steel)(6)Electrical connection12Terminal box, screened, 2m (other length on request)36Round plug M12×161Cable socket DIN EN 175301-803, form A(7)Extra codes000None452Parts in contact with the medium are electropolished, surface roughness Ra 0.8µm631Improved moisture and vibration protectiona A reduced deviation from characteristic is not available for ± ranges; it is available only in conjunction with 4to20mA, two-wire (output 405).b These process connections are only suitable with measuring spans up to 25bar.c Suitable process connection adapter, see data sheet 409711(1)(2)(3)(4)(5)(6)(7) Order code-----/Order example402050/000-459-405-571-20-61/000AccessoriesArticle Part no.Cable box (straight) with control cable, screen, 4-pole, 5m PVC cable, pressure compensation00512341。

Random trees

C T τ (s)

2

1

¤

¤

¤ ¤

¤h ¤ ¤ h ¤ ¤ h ¤ ¤ h¤

¤h ¤h ¤ h ¤ h ¤ h ¤ h ¤ h¤ h

h ¤h h ¤ h h ¤ h h¤ h

h

1 2 3

¤h h ¤h h ¤ h s h¤ h E

2p

A plane tree τ with p edges (or p + 1 vertices)

Göteborg

7 / 40

Important special cases

Geometric distribution µ(k) = 2−k −1 Then, if |τ | = number of edges of τ , P(θ = τ ) = 2−2|τ |−1. Consequence: The conditional distribution of θ given |θ| = p is uniform over {plane trees with p edges}. e−1 k! The conditional distribution of θ given |θ| = p is uniform over {Cayley trees on p + 1 vertices}. (Needs to view a plane tree as a Cayley tree by “forgetting” the order and randomly assigning labels 1, 2, . . . to vertices) µ(k) =

Jean-François Le Gall (Université Paris-Sud)

Random treesare we aiming at?

output-shifting

such as SDL, Estelle or Statecharts 18, 15, 12, 11]. While speci cations in these languages are usually extended nite state machines ( nite state machines with data) rather than FSMs, these may be converted to FSMs by either applying some abstraction or expanding out the data (after making the ranges nite). This has lead to interest in the automatic generation of tests from FSMs (see, for example, 1, 24, 9, 10, 22]). Traditionally, the interest in FSM based testing has largely been limited to protocol conformance testing and the testing of embedded control system. However, the use of Statecharts within the UML has recently widened the interest in this topic. When testing a system with multiple ports, there is one (local) tester at each port. Suppose testing involves the input of x at port p and then x0 at port p0 (p 6= p0 ). In order for the tester at p0 to know when to input x0 it must know when x has been input. If the tester at p0 does know when x has been input, because it has received output from the transition triggered by x, these two tests are synchronised. Sometimes there is no synchronised test that satis es the test criterion 19]. When this is the case, it may be possible to allow the testers to communicate: local testers may send synchronisation messages to one another. It is then possible to produce a synchronised test sequence. Naturally, when considering test minimisation, the cost of the synchronisation messages should be included. Thus, approaches that produce test sequences and then add synchronising messages may be suboptimal. Normally the testing problem is further complicated by the absence of a global clock 16]. In the presence of multiple ports, this reduces the ability of the test system to determine the global order of the input and output. It will be assumed that there is no global clock. When there are multiple ports, the lack of a global clock may make it di cult to determine which input triggered a particular output value. This makes it di cult to detect output being shifted between adjacent transitions in a test. Faults that shift output between adjacent tests are called output-shifting faults. Suppose, for example, that the tester at port p1 is to input x, this is expected to lead to a2 and a3 being output at ports p2 and p3 respectively, the tester at port p2 is then to input x0 and this is expected to lead to output of a4 at port p4 . This test sequence is synchronised as the tester at port p2 inputs x0 after it has received output a2 . However, it is possible that the input values trigger the wrong output but no fault is detected. For example, if the input of x leads to the output of a2 and a4 at p2 and p4 respectively and the input of x0 leads to the output of a3 at p3, the correct behaviour is seen at each port. The sequencing of these two transitions has allowed the faults to mask one another. While these faults are not detected in testing they might lead to problems when the system is used. Other authors have considered related problems. 16] introduce the term output-shifting fault and note that a synchronised test sequence need not detect output-shifting faults. 3] show how a minimalset of messages may be added to a given test sequence to produce a synchronised test sequence that detects outputshifting faults. However, where the initial test sequence has been produced to 2

Ladder图和M

Ladder图和M bius Ladder图的彩虹点连通数(英文)刘慧敏;毛亚平【期刊名称】《数学季刊:英文版》【年(卷),期】2016(31)4【摘要】A vertex-colored graph G is said to be rainbow vertex-connected if every two vertices of G are connected by a path whose internal vertices have distinct colors, such a path is called a rainbow path. The rainbow vertex-connection number of a connected graph G, denoted by rvc(G), is the smallest number of colors that are needed in order to make G rainbow vertex-connected. If for every pair u, v of distinct vertices, G contains a rainbow u-v geodesic, then G is strong rainbow vertex-connected. The minimum number k for which there exists a k-vertex-coloring of G that results in a strongly rainbow vertex-connected graph is called the strong rainbow vertex-connection number of G, denoted by srvc(G). Observe that rvc(G) ≤ srvc(G) for any nontrivial connected graph G. In this paper, for a Ladder L_n,we determine the exact value of srvc(L_n) for n even. For n odd, upper and lower bounds of srvc(L_n) are obtained. We also give upper and lower bounds of the(strong) rainbow vertex-connection number ofM bius Ladder.【总页数】7页(P399-405)【关键词】vertex-coloring;rainbow vertex-connection;(strong) rainbow vertex-connection number;Ladder;M bius Ladder【作者】刘慧敏;毛亚平【作者单位】Department of Mathematics,Qinghai Normal University【正文语种】中文【中图分类】O【相关文献】1.三类特殊图的(强)彩虹连通数 [J], 赵燕;柴航2.一些特殊图的Mycielskian图的彩虹顶点连通数 [J], 张璐;边红3.小直径二连通外平面图的彩虹连通数 [J], 邓兴超;宋贺;苏贵福;田润丽4.一些特殊定向图及其Mycielskian图的彩虹连通数 [J], 刘敏;边红;于海征;赵菲菲5.关于有限群幂图的强彩虹连通数 [J], MA Xuan-long;SU Hua-dong因版权原因,仅展示原文概要,查看原文内容请购买。

automesh子面板详细解释

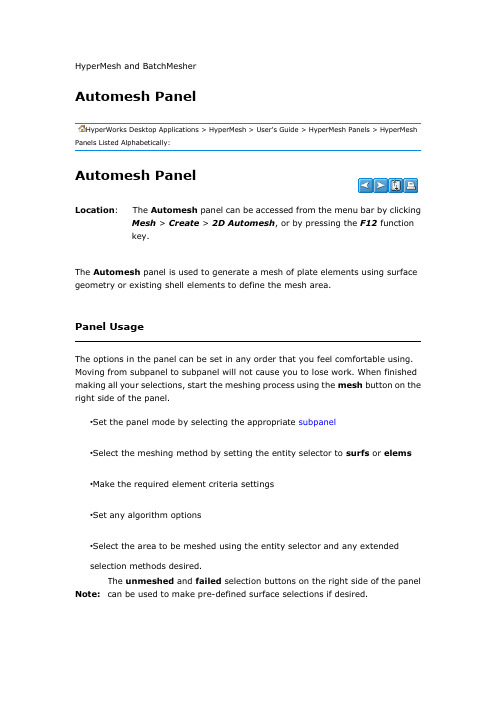

HyperMesh and BatchMesherAutomesh PanelHyperWorks Desktop Applications > HyperMesh > User's Guide > HyperMesh Panels > HyperMesh Panels Listed Alphabetically:Automesh PanelLocation: The Automesh panel can be accessed from the menu bar by clicking Mesh > Create > 2D Automesh, or by pressing the F12 functionkey.The Automesh panel is used to generate a mesh of plate elements using surface geometry or existing shell elements to define the mesh area.Panel UsageThe options in the panel can be set in any order that you feel comfortable using. Moving from subpanel to subpanel will not cause you to lose work. When finished making all your selections, start the meshing process using the mesh button on the right side of the panel.•Set the panel mode by selecting the appropriate subpanel•Select the meshing method by setting the entity selector to surfs or elems•Make the required element criteria settings•Set any algorithm options•Select the area to be meshed using the entity selector and any extendedselection methods desired.Note:The unmeshed and failed selection buttons on the right side of the panel can be used to make pre-defined surface selections if desired.Subpanels and InputsThe Automesh panel contains the following subpanels:Size and BiasSize and bias meshing is a very flexible and powerful meshing method. A minimum of inputs are required for the element criteria settings. The algorithm options can set preferences on how to handle certain situations when encountered in the geometry. When using existing finite elements as the basis for mesh generation, feature recognition settings allow the mesher to break up the areas defined by the selected elements into logical groupings with mesh controls set for each group boundary.This meshing mode works interactively or automatically. In interactive mode, a great deal of manual control is presented via the Secondary Automesh panel during the mesh generation stage. Interactive meshing allows you to control mesh size and element type, and to set different mesh generation algorithms and test element quality on a surface-by-surface basis. The resulting modified mesh can be updated at any time, giving immediate feedback as to the effectiveness of the change. When meshing in the automatic mode, the mesh will be generated using only the settings, criteria and options set in the Automesh panel.Size and biasing produces a mesh with consistent element size. If meshed interactively, the number of elements (element density) node spacing (biasing), element type and mesh style can be modified for each surface face and edge.Panel Inputs•Quads attempts to use quads only--however, at least one triaelement must be created if the sum of the element densities around the perimeter of the face or surface is odd.The sum of element densities on the perimeter of thelower surface is odd, resulting in a tria as indicated.Adjusting the element densities while meshing interactively can usually elimate all tria elements.Adjusting the bottom edge density from 11 to 10 makesthe sum even and allows all-quads to be generated.•Quads only uses a subdividing routine that tends to generate more orthogonal quad elements.Tria elements may still be introduced depending on thedensity settings as with the quads type.•Tria elements uses all-trias to mesh.•R-trias are right-angle triangular elements.If you select Advanced, choose any of the other types individually for mapped elements (elements on surfaces that can be mapped to simple geometric shapes) and free elements (those that cannot easily map to simple shapes).tAmap as circle - free map as circle - mapped map as rectangle - free map as rectangle - mapped map as pentagon - free map as pentagon - mappedAny time two adjacent elements’ normals would e xceed this angle HyperMesh creates a new set of nodes between them to maintain clean feature lines. Using a higher value results in elements spanning the feature line:With an appropriate value, the features lines are preserved.If feature angle = is too high, the feature lines are blurred.Produce a more orthogonal quad-dominant mesh. Only applies to mixed element type.Here, there is no flow alignmentFlow alignment is used, producing straighter rows of elementsMesh without link opposite edges Mesh with link oppositeedgesMesh with link oppositeedgesQI OptimizeQuality Index meshing is an iterative automatic mesh generation method driven by element quality criteria. During the mesh generation process, the quality index of the mesh is determined by evaluating each element against a set of element quality tests. If all required element quality criteria are passed, then that element has a perfect quality index of zero. As the element quality deteriorates, the quality index value increases; so a lower quality index score indicates an element more closely meets the ideal quality requirements.The compound quality index sum of the quality index values for each of the elements that are included in the current meshing area. The quality index value itself has no direct physical meaning; it is a way to compare one generated mesh pattern against another pattern generated for that same area. The quality index based mesh optimization routine attempts modify the mesh pattern and apply node smoothing routines to obtain a lower overall quality index value.For more on element quality index, see the Quality Index panel.Panel InputsSelect quads, trias, mixed, or Quads only to specify the type of element to use in building meshes.•Mixed uses quads primarily, but inserts trias whenmaking density transitions, resulting in improved mesh quality.•Quads attempts to use quads only--however, at leastone tria element must be created if the sum of theelement densities around the perimeter of the face orsurface is odd.Adjusting the element densities while meshinginteractively can usually eliminate all tria elements.•Quads only uses a subdividing routine that tends to generate more orthogonal quad elements.Tria elements may still be introduced depending onthe density settings as with the quads type.•Tria elements uses all-trias to mesh.Specify a maximum angle across which elements can be maintained.Any time two adjacent elements’ normals would exceed this angle HyperMesh creates a new set of nodes between them to maintain clean feature lines. Using a higher value results in elements spanning the feature line:With an appropriate value, the features lines are preserved.If feature angle = is too high, the feature lines are blurred.Produce a more orthogonal quad-dominant mesh. Only applies to mixed element type.Here, there is no flow alignmentFlow alignment is used, producing straighter rows of elements•flow: align produces a more orthogonal quad dominated mesh•flow: size appears only when align is active, andEdge DeviationUse the Edge Deviation subpanel to set specific meshing parameters to limit how far the mesh elements can deviate from the actual edges of the surfaces meshed, or when in the case of re-meshing elements, deviation from inferred edges based on features.Controls for the minimum and maximum allowable element size, edge deviation and maximum angle are introduced with this method. Edge deviation normally occurs on curved edges, because individual elements have straight edges and therefore can only approximate a curve.When meshing curved surfaces as shown here, the planar elements (tan color) can deviate from the curved greygeometry.Edge deviation applies to both surface geometry and when re-meshing elements. Automeshing on the edge deviation subpanel automatically selects the best element size to approximate a curve, within the limits that you specify. The max deviation and max angle settings are the primary controls for this effect.This method can produce a mesh in which the element size varies, even within the same surface. Areas of high curvature will tend to have smaller elements than areas of low or no curvature. The element size boundaries allow you to control this effect.Edge deviation control when meshing creates smaller elements and spaces nodes closer together to limit how much the elements can deviate from the surface edges.Panel Inputs•Quads attempts to use quads only--however, at least one triaelement must be created if the sum of the element densities around the perimeter of the face or surface is odd.Adjusting the element densities while meshing interactively can usually eliminate all tria elements.•Quads only uses a subdividing routine that tends to generate more orthogonal quad elements.Tria elements may still be introduced depending on thedensity settings as with the quads type.•Tria elements uses all-trias to mesh.•R-trias are right-angle triangular elements.If you select Advanced, choose any of the other types individually for mapped elements (elements on surfaces that can be mapped to simple geometric shapes) and free elements (those that cannot easily map to simple shapes).map as circle - free map as circle - mappedmap as pentagon - free map as pentagon - mappedSpecify a maximum angle across which elements can be maintained.Any time two adjacent elements’ normals would exceed this angle HyperMesh creates a new set of nodes between them to maintain clean feature lines. Using a higher value results in elements spanning the feature line:With an appropriate value, the features lines are preserved.If feature angle = is too high, the feature lines are blurred.Produce a more orthogonal quad-dominant mesh. Only applies to mixed element type.Here, there is no flow alignmentFlow alignment is used, producing straighter rows of elements•flow: align produces a more orthogonal quad dominated mesh•flow: size appears only when align is active, and enforces theglobal mesh element size with minimal min/max element size variation.Mesh without link opposite edges with AR < selected.Mesh with link oppositeedgeswith AR < set to auto.Mesh with link oppositeedgeswith AR < set to 8.0.Surface Deviation (surface meshing only)This subpanel is only accessible when meshing surfaces. Use the Surface Deviation subpanel to mesh within limits of element deviation from a surface.Similarly to the edge deviation subpanel, meshing behavior on this subpanel is driven by distances between flat elements and model geometry. When flat elements are used to approximate a curved surface, there is always a discrepancy between each element and the actual curve of the surface, because the element uses a straight line between two nodes:A gap is visible between the curved edge of the surface and the element edges.The surface deviation automesh method chooses the mesh density based on the severity of this deviation. Where the threshold deviation would be exceeded, smaller elements are used to reduce the deviation:With surface deviation meshing, smaller elements are used to accuratelyrepresent curved surfaces. Larger elements are used where the geometry showsless curvature.The surface deviation meshing works only in an automatic mode; interactive meshing with the secondary automesh panel is not possible. However, the refine function can be used to set a specific desired mesh size for a point, line or surface face. This option accesses another temporary subpanel that is slaved to the surface deviation subpanel, and allows you to select fixed points, lines, or surfaces to define an area in which you desire a more refined mesh. You can specify a different element size for these areas, which displays as a color-coded numeric value: yellow for points, green for lines, or red for surfaces. An option to show all or show active toggles the view of these numeric values; show active displays only the refinement value for the most recently selected point, line or surface, while show all shows all values for all selected entities.After specifying refinement options, clicking mesh causes the meshing engine to create a smoothly-scaled mesh from your base element size to the size specified inthe refine options.Here, the mesh is not refined, but the colored numbers indicate refinement targets: point (yellow), line (green), and surface (red)Here, refinement is applied. You can see that the mesh is finer near the point (yellow), along the line/edge (green), and on the surface (red).Panel InputsDetermines how rapidly elements can increase in size as they are created further and further away from features.Elements further from the features grow larger with each row.maintain clean feature lines. Using a higher value results in elements spanning the feature line:With an appropriate value, the features lines are preserved.If feature angle = is too high, the feature lines are blurred.Select quads, trias, mixed, R-trias, Quads only, or advanced to specify the type of element to use in building meshes.•Mixed uses quads primarily, but inserts trias when making density transitions, resulting in improved mesh quality.•Quads attempts to use quads only--however, at least onetria element must be created if the sum of the element densities around the perimeter of the face or surface is odd.Adjusting the element densities while meshinginteractively can usually eliminate all tria elements.•Quads only uses a subdividing routine that tends to generate more orthogonal quad elements.Tria elements may still be introduced depending on the density settings as with the quads type.•Tria elements uses all-trias to mesh.•R-trias are right-angle triangular elements.If you select Advanced, choose any of the other types individually for mapped elements (elements on surfaces that can be mapped to simple geometric shapes) and free elements (those that cannot easily map to simple shapes).map as circle - free map as circle - mappedmap as pentagon - free map as pentagon - mappedUse the Rigid Body Mesh subpanel to create a quick mesh to represent the topology of a rigid object. Only the automatic meshing mode is available.Rigid bodies are surfaces that are expected to be treated as undeformable in the solution. One example of a rigid body is in metal-forming. When modeling the results of a die pressing down on a metal sheet, it’s important to model the shape of the die because that determines the shape of the metal sheet after being pressed. However, during a forming analysis the stresses and deformations of thedie itself are not of interest, only those of the formed metal sheet. Otherapplications for rigid bodies include the impactors used in vehicle crash simulation.A mesh that accurately represents the rigid geometry is important for such simulations to allow the solver collision detection routines to work effectively and accurately. Since stress and deformation of the rigid body are not calculated by the solver, the rigid body mesh focuses on accurately modeling the shape of the body rather than on producing a high-quality mesh. To this end, it uses the same faceting and shading routines that are used for drawing the model graphics. The resulting mesh may have high aspect ratio or extremely tapered elements that would not be suitable for solution, but can accurately represent the geometry.The images below illustrate the differences between surface deviation meshing and rigid body meshing. Both meshes were generated using the same parameters in terms of min/max element size, maximum deviation and feature angle, and mesh type.When creating a surface deviation based mesh on this cone, many small elements are required to capture the geometry, even so, the elements exhibit a lot of warpage and those at the tip are distorted and do not accurately represent the geometry.With the rigid body mesh, the shape of the object can be accurately modeled using fewer larger elements since the element shape is not a concern.Panel InputsSpecify a maximum allowable break angle between adjacent elements. The element size is adjusted such that the angle between the normals of adjacent elements does not exceed this value.In these examples, the minimum and maximum element sizes are 3 and50 respectively. In this first image, the mesh is constrained by the max deviation value set to 0.5. The element size is set such that the maximum distance between the element and the spherical surface does not exceed this setting.In this second example, the deviation setting is relaxed to 3.0, and the mesh is bound by the maximum feature angle setting of 45 degrees.•Tria elements uses all-trias to mesh.See Also:HM-3100: AutoMeshingHM-3120: 2-D Mesh in Curved Surfaces HM-3130: QI Mesh CreationQuality Index panelAn Alphabetical List of HyperMesh Panels An Alphabetical List of HyperForm Panels。

《群论》部分习题答案

《群论》部分习题解答版权所有人:Wu TS,2006年4月第一章.预备知识(Chapter1.Preliminary) 4.(Page28)Let S be the set of all n×n symmetric real matrices and in S we define a binary relation∼in the followingA∼B if and only if there exists an invertible matrix C such that B=C AC,where C is the transpose matrix of C.Prove that∼defines an equivalent relation in pute|S/∼|.解答:(1)直接验证∼是S的一个等价关系。

(2)根据线性代数理论,对于任意实对称矩阵A,存在可逆矩阵Q 使得Q AQ是对角矩阵diag{1,1,···,−1,···,−1,0,···,0},简记为Q AQ=E r000−E s0000=Dr,s,其中r+s=r(A).根据惯性定理,其中的r也是由A唯一确定的。

因此,两个n阶实对称矩阵A与B合同的充分必要条件是r(A)=r(B)且正惯性指数相同。

所以我们得到S/∼={D r,s|0≤r,s and r+s≤n},其中,D r,s={P D r,s P|P∈GL n(R)}.下面计算|S/∼|.(1)满足r=0的D r,s共有n+1个,它们分别是D0,0,D0,1,D0,2,···,D0,n.(2)满足r=1的D r,s共有n个,它们分别是D1,0,D1,1,D1,2,···,D1,n−1.···(n+1)满足r=n的D r,s共有1个,即为D n,0.因此,|S/∼|=n+1j=1j=(n+1)(n+2)2.1第二章.群论(Chapter2.Group Theory)1.(Page49)Prove that both G1={(a ij)n×n|a ij∈Z,det(A)=1}and G2= {(a ij)n×n|a ij∈Q,det(A)=1}are groups under the matrix multiplication.证明:只证明G1是子群。

Memory bandwidth bottleneck and its amelioration by a compiler