Layout_PCB实例讲解

电容按键PCB layout规则

电容按键PCB layout规则一、 布局1、芯片的位置在PCB 板空间允许的情况下,应尽量将触摸芯片放置在触摸板的中间,使IC的每个感应通道的引脚到感应盘的距离差异最小。

2、稳压电路的放置稳压电路和滤波电路放在触摸板上,在VDD与VSS间并接退耦电容104,靠近IC 放置。

3、通道匹配电阻的放置Sensor通道增加300Ω-2K匹配电阻Rs,Rs靠近IC管脚放置。

4、Cs和Rmod靠近IC放置。

5、复位电路靠近IC放置。

6、按键感应盘(电容传感器)形状、大小和间隙根据手指触摸的习惯,按键盘一般选择圆形和方形。

以圆形为例,按键盘的大小建议在5mm-15mm之间。

按键间隙保持在3mm以上,滑条和滚轮可以缩小到0.5mm。

二、 走线1、遵循数模混合电路设计原则芯片内部集成了精密电容测量的模拟电路,因此进行PCB 设计时应该把它看成一个独立的模拟电路对待。

遵循通常的数模混合电路设计的基本原则。

2、双面板走线如果直接使用PCB板上的铜箔作触摸感应盘,应使用双面PCB板。

触摸芯片和感应盘到IC引脚的连线放在底层(BOTTOM),感应盘放在顶层(TOP)。

3、单面板走线如果采用单面PCB板,并用弹簧或其它导电物体做感应盘,感应盘到IC引脚的连线不走或少走跳线。

4、sensor走线感应盘到IC 的连线应尽量细,双面板采用8-15mil 的线宽,单面板板线宽15-20mil,sensor走线避开大电流和高频信号线,感应盘到触摸芯片的连线周围0.5mm不要走其他信号线。

各sensor走线间距保持在20mil以上,以免交互干扰。

sensor走线长度尽量短,最长不超过30cm。

5、电源走线触摸芯片最好用一根独立的走线从板子的供电点取电,不要和其他的电路(如LED回路)共用电源回路。

触摸IC的供电从滤波电路输入,保持VDD与VSS并行,输入路径短而粗(40mil左右)。

6、采用星形接地触摸芯片的地线不要和其他电路共用,应该单独连到板子电源输入的接地点,也就是通常说的采用“星形接地”。

PCB LAYOUT基础知识

BULK-

PFC Circuit

BULK-

五,1, 环路

經Bulk(VB)+ ; Q1 "D"極從"S"極出至R14回Bulk-此回 路面积须小,尽量不与其它回路共地

五,1,环路

一次侧TOP SWITCH回路尽量短.如下图

五,1,环路

PWM IC 如:384X Rt及Ct尽量靠近IC.且PWM IC Driver (如M9 PIN6 至Main switch 距离最 短)

一个好的PCB外观更能打动客户的心

一个好的产品就是一件艺术品。 好的线路设计,好的功能表现,整齐的零件排

列,美的PCB外观

The end

谢谢大家!

方便生产

文字无叠加,模糊不清 零件无挤压,冲突 贴片零件方向一致,距离合理,方便SMT生产 零件摆放时有考虑过锡炉的方向 PAD密的地方有加阻焊层 孔的小大,PAD的大小合理 大的散热器件拆装方便

节约

正确的线路,节约电子工程师调试的时间 合理的布局,节约测试EMI的成本 优秀的排版,节约生产线的人力物力

二,PCB的分类

按线路走线层数 按板材 其它分类法

二,1. 按线路的层数分

单面板 双面板 多层板

二,2,按材质分:

P.P 纸质酚醛树脂基板 也称之为FR-1 CEM-1 玻璃布表面+绵纸+环氧树脂 CEM-3 玻璃布表面+不织布+环氧树脂 FR-4 玻璃布+环氧树脂

二,3,其它分类法

五,1,环路

两个三极管的基极尽量靠近

五,1,环路

Output Loop 从变压器出經二极管從第一個濾 波電容回变压器. 见下图

loop1

PCBLAYOUT利用技术大全

PCB LAYOUT技术大全2020-06-08 10:24PCB LAYOUT技术大全2020-03-12 11:48PCB LAYOUT技术大全1.原理图常见错误:(1)ERC报告管脚没有接入信号:a. 创建封装时给管脚概念了I/O属性;b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;c. 创建元件时pin方向反向,必需非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部份调入pcb:生成netlist时没有选择为global。

(4)当利用自己创建的多部份组成的元件时,万万不要利用annotate.中常见错误:(1)网络载入时报告NODE没有找到:a. 原理图中的元件利用了pcb库中没有的封装;b. 原理图中的元件利用了pcb库中名称不一致的封装;c. 原理图中的元件利用了pcb库中pin number不一致的封装。

如三极管:sch中pin number 为e,b,c, 而pcb中为1,2,3。

(2)打印时老是不能打印到一页纸上:a. 创建pcb库时没有在原点;b. 多次移动和旋转了元件,pcb板界外有隐藏的字符。

选择显示所有隐藏的字符,缩小pcb, 然后移动字符到边界内。

(3)DRC报告网络被分成几个部份:表示那个网络没有连通,看报告文件,利用选择CONNECTED COPPER查找。

另外提示朋友尽可能利用WIN2000, 减少蓝屏的机遇;多几回导出文件,做成新的DDB 文件,减少文件尺寸和PROTEL僵死的机遇。

若是作较复杂得设计,尽可能不要利用自动布线。

在PCB设计中,布线是完成产品设计的重要步骤,能够说前面的预备工作都是为它而做的,在整个PCB中,以布线的设计进程限定最高,技术最细、工作量最大。

PCB布线有单面布线、双面布线及多层布线。

布线的方式也有两种:自动布线及交互式布线,在自动布线之前,能够用交互式预先对要求比较严格的线进行布线,输入端与输出端的边线应幸免相邻平行,以避免产生反射干扰。

pcb layout指导书

pcb layout指导书pcb layout指导书一、概述⑴目的本pcb layout指导书的目的是为了提供一个详细的指南,帮助设计人员进行pcb布局。

⑵背景pcb布局是电路设计的重要环节之一,它涉及到电路板上元件的布置、连线的规划以及电磁兼容性等问题。

合理的pcb布局可以提高电路性能和可靠性。

二、设计准备⑴系统规格在进行pcb布局之前,需要明确系统规格,包括电路功能、性能要求以及信号传输速率等。

⑵系统拓扑根据系统规格,确定电路板的拓扑结构,包括电路板的层数和板型。

⑶元件选型根据系统规格选定合适的元件,并注意元件的尺寸和布局形式。

⑷连接件选型选定合适的连接件,包括电路板与外部接口的连接器、接线端子等。

三、布局规划⑴元件布置根据系统规格和元件尺寸,选择合适的元件布置方式,确保元件之间的间距和连接线长度符合设计要求。

⑵电源和地线布置合理布置电源和地线,确保电路板上各个元件的供电和地线连接畅通。

⑶敏感信号布置敏感信号的布置需要与其他信号相隔一定距离,并采取屏蔽措施,以减少对敏感信号的干扰。

⑷时钟信号布置时钟信号的布置需要考虑时钟传输的稳定性和抗干扰能力。

⑸热管理合理布置散热器、散热孔和风扇等,确保电路板的温度控制在可接受范围内。

四、连线规划⑴信号层定义根据系统规格和布局需求,将电路板划分为不同的信号层,包括功耗层、地层、电源层和信号层等。

⑵信号线宽度和间距根据信号传输速率和电流要求,确定信号线的宽度和层间间距。

⑶信号线走向根据电路功能和信号传输路径,规划信号线的走向,尽量缩短信号线长度。

⑷差分信号布局差分信号需要保持相等长度,并与其他信号相隔一定距离,以减少互相之间的干扰。

五、电磁兼容性措施⑴地线分割根据电路板的信号层划分和布局需求,采取地线分割策略,减少地线回路的面积。

⑵绕线方式对于高频信号和敏感信号,采用绕线方式减少辐射和串扰。

六、文档附件本指导书相关附件包括:附件1:系统规格说明书附件2:pcb布局图附件3:连线规划图七、法律名词及注释⒈电路板:也称印刷线路板(Printed Circuit Board,PCB),是用于连接和支持电子元件的载体。

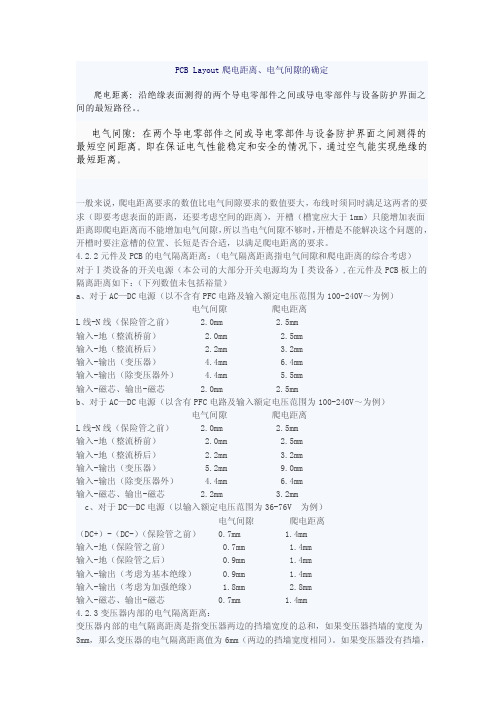

PCB Layout爬电距离、电气间隙的确定

PCB Layout爬电距离、电气间隙的确定爬电距离:沿绝缘表面测得的两个导电零部件之间或导电零部件与设备防护界面之间的最短路径。

电气间隙:在两个导电零部件之间或导电零部件与设备防护界面之间测得的最短空间距离。

即在保证电气性能稳定和安全的情况下,通过空气能实现绝缘的最短距离。

一般来说,爬电距离要求的数值比电气间隙要求的数值要大,布线时须同时满足这两者的要求(即要考虑表面的距离,还要考虑空间的距离),开槽(槽宽应大于1mm)只能增加表面距离即爬电距离而不能增加电气间隙,所以当电气间隙不够时,开槽是不能解决这个问题的,开槽时要注意槽的位置、长短是否合适,以满足爬电距离的要求。

4.2.2元件及PCB的电气隔离距离:(电气隔离距离指电气间隙和爬电距离的综合考虑)对于Ⅰ类设备的开关电源(本公司的大部分开关电源均为Ⅰ类设备),在元件及PCB板上的隔离距离如下:(下列数值未包括裕量)a、对于AC—DC电源(以不含有PFC电路及输入额定电压范围为100-240V~为例)电气间隙爬电距离L线-N线(保险管之前) 2.0mm 2.5mm输入-地(整流桥前) 2.0mm 2.5mm输入-地(整流桥后) 2.2mm 3.2mm输入-输出(变压器) 4.4mm 6.4mm输入-输出(除变压器外) 4.4mm 5.5mm输入-磁芯、输出-磁芯 2.0mm 2.5mmb、对于AC—DC电源(以含有PFC电路及输入额定电压范围为100-240V~为例)电气间隙爬电距离L线-N线(保险管之前) 2.0mm 2.5mm输入-地(整流桥前) 2.0mm 2.5mm输入-地(整流桥后) 2.2mm 3.2mm输入-输出(变压器) 5.2mm9.0mm输入-输出(除变压器外) 4.4mm 6.4mm输入-磁芯、输出-磁芯 2.2mm 3.2mmc、对于DC—DC电源(以输入额定电压范围为36-76V为例)电气间隙爬电距离(DC+)-(DC-)(保险管之前)0.7mm 1.4mm输入-地(保险管之前)0.7mm 1.4mm输入-地(保险管之后)0.9mm 1.4mm输入-输出(考虑为基本绝缘)0.9mm 1.4mm输入-输出(考虑为加强绝缘) 1.8mm 2.8mm输入-磁芯、输出-磁芯0.7mm 1.4mm4.2.3变压器内部的电气隔离距离:变压器内部的电气隔离距离是指变压器两边的挡墙宽度的总和,如果变压器挡墙的宽度为3mm,那么变压器的电气隔离距离值为6mm(两边的挡墙宽度相同)。

第九章ARES PCB Layout设计基本概念

9

9.2

ARES PCB Layout设计基本概念

ARES PCB Layout的主要特性

Proteus 8.0 PCB Layout主要特点有: (8) 封装库包含通孔式(through hole)和表面粘贴式(surface mount,简称 SMT,包括SM782和IPC7351标准的SMT的封装)。具有多样式的焊盘/过孔, 丰富的二维图形符号库。 (9) 输出到打印机和绘图仪,包括了Valor的ODB++格式和传统的Gerber / Excellon的范围广泛。还可以输出DXF,PDF格式,EPS,WMF和BMP图形格 式。 (10) 利用Gerber浏览器, 可以预览、查看Gerber输出文件。 (11) 3D 可视化预览,可以输出STL、3D DXF和3DS格式。

9

ARES PCB Layout设计基本概念

9.1.1

PCB板层结构及术语

图

PCB板

9

ARES PCB Layout设计基本概念

9.1.2

PCB 板层结构

印制电路板包括刚性、揉性和刚揉结合的单面板(SSB)、双面板(DSB) 和多层板(MLB)。 (1)单面板 单面板是指仅一面有导电图形的印制板,即电路板一面覆铜,覆铜面用 来布线(设计电路导线)和元件焊接,则另一面用于放置直插式封装元器件。 单面板用于设计比较简单的电路。 (2) 双面板 顶层(Top Layer)和底层(Bottom Layer)都有铜模导线(Track)的 电路板,双面布线。元器件一般放在顶层,所以顶层也称为元件面 (Component Side),底层为焊接面(Solder side)。顶层与底层中间为 一层绝缘层,顶层与底层通过过孔(Via)和焊盘(Pad)实现电器连接。 用于设计较为复杂电路。 (3) 多层板 由交替的导电图形层和绝缘材料层叠压粘合而成而成的电路板,除了顶 层和底层外,内部还有一层或者多层相互绝缘的导电层。各层之间通过金属 氧化物过孔(Via,简称金属化孔)实现电气连接。

PCB-LAYOUT流程图

PCB-LAYOUT流程图

准备:A原理图分析、标准元件库建立、特殊元件封装制作;

B依据结构图绘制所需的简单二维.DXF文件(封闭板框、TOP/BOTTOM元件示意)

网表输入(.asc文件):硬工设计完成原理图-DRC检查-输出正确的.asc文件 网标转换到PCB设计中-导入.DXF结构(处理板框、结构件丝印)规则设置:进行线宽、线距、层定义、过孔、全局参数的设置等

手工布局:根据结构丝印放置结构件,参照原理图进行布局

A生成板框,放置结构件并固定-限制元件-关键-大元件-零散元件

B参照原理图 结合结构 进行布局

C布局检查:固定件、限高、有序整齐、方便维修、敏感元件放置、信号流畅等

手工布线:预布线看连通性,根据原理图实际调整最优布线

检查走线:信号线处理差分、等长、包地等,P,G线宽,FB最短,丝印整齐,补铜皮、丝印标示、白油、禁布铜、去绿油等优化处理,多层板内层内缩,Mark点等

ECO同步比较、PCB检查列表核对一遍并输出.DXF给结构核对

覆铜项目检查:孤铜,地完整,连通性-间距检查

PCB评审(硬件、结构、SMT、产测等)

覆铜CAM输出:偏移尺寸一致,部分元件(PAST)丝印不显示处理,丝印放置(禁放去绿油区)(背面插件元件引脚花焊盘接地)

CAM输出-拼版尺寸控制在285*240MM,做到防呆,考虑是否加工艺边等

发出拼好的CAM文件-完成

原理图出差或更换元件封装重新输出网表.asc文件-新

建.PCB文件导入-原件与新文件ECO比较生产ECO文件,然后导入原文件(禁止PCB 中直接使用ECO状态下大动作更改)。

PCB Layout 设计需知及要领

修正圖面

詳細流程圖及說明:

每日16:00繪制草圖 給工程師核對, 並隔日回饋問題

工程師檢查是否錯誤

工程師檢查是否錯誤

機種 LAYOUT

核對原始LAYOUT 有無錯誤

開始LAYOUT

完成草圖 (繪制草圖核對)

完成正式圖 (繪制正式圖核對)

繪製各層別圖 檢察是否錯誤

出圖 樣品:12:00前 發行:10:00前

1.3.6 雙面SMD布置者,為避免錫膏印刷機之夾爪 夾到零件,零件與板邊需保持10mm距离

1.3.7 Guid Line p45 螺絲孔至SMD零件之規範,修訂如下

避免鎖螺絲時對周邊產生之應力損壞SMD零件,所有螺絲 孔附近之半徑以內,不得佈置SMD,如下表。

螺絲孔周圍佈置限制

條件 ❖二極體、電容 ❖其餘零件 ❖螺柱≧螺絲頭

(2)將變更: REVISION, CODE。 請保留:REVISION ,CODE 。

a.若須變更REVISION在其 內打勾,變更CODE在其 內打勾。

b.須保留前面板本之PCB請將保留板本之REVISION

,CODE

填入。

(3)客戶名稱:

請將客戶名稱填入,若為標準品請填寫 Standard 。

PWB instead of PCB

主要原因為: PCB(PRINT CIRCIT BOARD 板名稱(Polychlorinated bipheny)多氯聯苯(有 毒),改為 PWB(Print Wire Board印刷線路 版),此項變更對爾後客戶(SONY))來稽核時較不會 有爭議.所有規格及表格PCB字樣須改為PWB;資 料中心審核組會作規格的卡關

E.此項變更: 需, 不需 報備安規。

F.此次變更要: 製做樣品(

PCB专业词汇解释和Layout技巧

假时钟: 假时钟是指时钟越过阈值(threshold)无意识地改变了状态(有时 在 VIL 或 VIH 之间)。通常由于过分的起。

37.电源完整性(Power Integrity): 指电路系统中的电源和地的质量。 38.同步开关噪声(Simultaneous Switch Noise):指当器件处于开关状态, 产生瞬间变化的电流(di/dt),在经过回流途径上存在的电感时,形成交流压降, 从而引起噪声,简称 SSN。也称为 Δi 噪声。 39.地弹(Ground Bounce):指由于封装电感而引起地平面的波动,造成芯 片地和系统地不一致的现象。同样,如果是由于封装电感引起的芯片和系统电源 差异,就称为电源反弹(Power Bounce)。

布线就是在布局之后,通过设计铜铂的走线图,按照原理图连通所有的走线。 显然,布局的合理程度直接影响布线的成功率,往往在布线过程中还需要对布局 作适当的调整。布线设计可以采用双层走线和单层走线,对于极其复杂的设计也 可以考虑采用多层布线方案,但为了降低产品的造价,一般应尽量采用单层布线 方案。对于个别无法布通的走线,可以采用标准间距短跳线或长跳线(软线)连 通。

3.集总电路(Lumped circuit):在一般的电路分析中,电路的所有参数, 如阻抗、容抗、感抗都集中于空间的各个点上,各个元件上,各点之间的信号是瞬 间传递的,这种理想化的电路模型称为集总电路。

4.分布式系统(Distributed System):实际的电路情况是各种参数分布于电 路所在空间的各处,当这种分散性造成的信号延迟时间与信号本身的变化时间相 比已不能忽略的时侯,整个信号通道是带有电阻、电容、电感的复杂网络,这就是 一个典型的分布参数系统。

19.屏蔽效率(SE):是对屏蔽的适用性进行评估的一个参数,单位为分贝。 吸收损耗:吸收损耗是指电磁波穿过屏蔽罩的时候能量损耗的数量。 20.反射损耗:反射损耗是指由于屏蔽的内部反射导致的能量损耗的数量, 他随着波阻和屏蔽阻抗的比率而变化。 21.校正因子:表示屏蔽效率下降的情况的参数,由于屏蔽物吸收效率不高, 其内部的再反射会使穿过屏蔽层另一面的能量增加,所以校正因子是个负数,而 且只使用于薄屏蔽罩中存在多个反射的情况分析。 22.差模 EMI:传输线上电流从驱动端流到接收端的时候和它回流之间耦合 产生的 EMI,就叫做差模 EMI。 23.共模 EMI:当两条或者多条传输线以相同的相位和方向从驱动端输出到 接收端的时候,就会产生共模辐射,既共模 EMI。 24.发射带宽:即最高频率发射带宽,当数字集成电路从逻辑高低之间转换的 时候,输出端产生的方波信号频率并不是导致 EMI 的唯一成分。该方波中包含频 率范围更宽广的正弦谐波分量,这些正弦谐波分量是工程师所关心的 EMI 频率成 分,而最高的 EMI 频率也称为 EMI 的发射带宽。 25.电磁环境:存在于给定场所的所有电磁现象的总和。 26.电磁骚扰:任何能引起装置、设备或系统性能降低或者对有生命或者无 生命物质产生损害作用的电磁现象。 27.电磁干扰:电磁骚扰引起设备、传输通道和系统性能的下降。 28.电磁兼容性:设备或者系统在电磁环境中能正常工作且不对该环境中任 何事物构成不能承受的电磁骚扰的能力。 29.系统内干扰:系统中出现由本系统内部电磁骚扰引起的电磁干扰。 30.系统间干扰:有其他系统产生的电磁干扰对一个系统造成的电磁干扰。 31.静电放电:具有不同静电电位的物体相互接近或者接触时候而引起的电 荷转移。 建立时间(Setup Time):建立时间就是接收器件需要数据提前于时钟沿稳 定存在于输入端的时间。 32.保持时间(Hold Time):为了成功的锁存一个信号到接收端,器件必须 要求数据信号在被时钟沿触发后继续保持一段时间,以确保数据被正确的操作。 这个最小的时间就是我们说的保持时间。 33.飞行时间(Flight Time):指信号从驱动端传输到接收端,并达到一定 的电平之间的延时,和传输延迟和上升时间有关。 34.Tco:是指器件的输入时钟边缘触发有效到输出信号有效的时间差,这是 信号在器件内部的所有延迟总和,一般包括逻辑延迟和缓冲延迟。缓冲延迟 (buffer delay):指信号经过缓冲器达到有效的电压输出所需要的时间 35.时钟抖动(Jitter):时钟抖动是指时钟触发沿的随机误差,通常可以用 两个或多个时钟周期之间的差值来量度,这个误差是由时钟发生器内部产生的, 和后期布线没有关系。 36.时钟偏移(Skew):是指由同样的时钟产生的多个子时钟信号之间的延 时差异。

PCB相关设计软件LayoutPlus介绍

01

相对于其他PCB设计软件,Layoutplus的学习曲线较为陡峭,

需要一定时间适应和掌握。

价格较高

02

Layoutplus的授权价格相对较高,可能会增加一些中小型企

业的成本压力。

技术支持有限

03

相对于其他大型PCB设计软件,Layoutplus的技术支持和社区

讨论相对较少。

与其他软件的对比分析

元件编辑功能

LayoutPlus允许用户创建和编辑自己的元件,包括封装、引脚、属性等,以满足 特定的设计需求。

自动布线和手动布线功能

自动布线

LayoutPlus的自动布线功能能够快速有效地将元件连接起来 ,大大提高了设计效率。

手动布线

对于需要精细调整的布线,LayoutPlus也支持手动布线功能 ,让用户能够根据需要自由地布置线路。

通过灵活的布局布线工具,用户能够快速完成 多层板、多器件、高密度布线的PCB设计。

LayoutPlus还支持对复杂PCB设计进行仿真分 析,以进一步优化设计质量。

案例展示三:多层pcb设计

在多层PCB设计中,LayoutPlus提供了强大的3D建 模和视图管理功能。

通过3D模型,用户可以直观地查看和管理不同层之 间的信号和电源分布。

应用领域与案例展示

应用领域介绍

01

LayoutPlus是一款功能强大的PCB设计软件,广泛应用于通信、医疗、工业控 制、汽车电子等领域。

02

尤其在通信领域,LayoutPlus凭借其高效稳定的设计能力,为众多企业提供了 从原理图到PCB一站式解决方案。

03

LayoutPlus还支持多种EDA工具的导入和导出,方便用户进行数据交互和项目 管理。