《数字集成电路》期末试卷A(含答案)

数电期末试卷及答案(共4套)

##大学信息院《数字电子技术根底》期终考试试题〔110分钟〕(第一套)一、填空题:〔每空1分,共15分〕1.逻辑函数Y AB C=+的两种标准形式分别为〔〕、〔〕。

2.将2004个“1〞异或起来得到的结果是〔〕。

3.半导体存储器的结构主要包含三个局部,分别是〔〕、〔〕、〔〕。

4.8位D/A转换器当输入数字量10000000为5v。

假设只有最低位为高电平,那么输出电压为〔〕v;当输入为10001000,那么输出电压为〔〕v。

5.就逐次逼近型和双积分型两种A/D转换器而言,〔〕的抗干扰能力强,〔〕的转换速度快。

6.由555定时器构成的三种电路中,〔〕和〔〕是脉冲的整形电路。

7.与PAL相比,GAL器件有可编程的输出结构,它是通过对〔〕进展编程设定其〔〕的工作模式来实现的,而且由于采用了〔〕的工艺结构,可以重复编程,使它的通用性很好,使用更为方便灵活。

二、根据要求作题:〔共15分〕1.将逻辑函数P=AB+AC写成“与或非〞表达式,并用“集电极开路与非门〞来实现。

2.图1、2中电路均由CMOS门电路构成,写出P、Q 的表达式,并画出对应A、B、C的P、Q波形。

三、分析图3所示电路:〔10分〕1)试写出8选1数据选择器的输出函数式;2)画出A2、A1、A0从000~111连续变化时,Y的波形图;3)说明电路的逻辑功能。

四、设计“一位十进制数〞的四舍五入电路〔采用8421BCD码〕。

要求只设定一个输出,并画出用最少“与非门〞实现的逻辑电路图。

〔15分〕五、电路与CP、A的波形如图4(a) (b)所示,设触发器的初态均为“0〞,试画出输出端B和C的波形。

〔8分〕BC六、用T触发器和异或门构成的某种电路如图5(a)所示,在示波器上观察到波形如图5(b)所示。

试问该电路是如何连接的?请在原图上画出正确的连接图,并标明T的取值。

〔6分〕七、图6所示是16*4位ROM和同步十六进制加法计数器74LS161组成的脉冲分频电路。

数电期末试卷及答案(共4套)

XX大学信息院《数字电子技术基础》期终考试试题(110分钟)(第一套)一、填空题:(每空1分,共15分)1.逻辑函数Y AB C=+的两种标准形式分别为()、()。

2.将2004个“1”异或起来得到的结果是()。

3.半导体存储器的结构主要包含三个部分,分别是()、()、()。

4.8位D/A转换器当输入数字量10000000为5v。

若只有最低位为高电平,则输出电压为()v;当输入为10001000,则输出电压为()v。

5.就逐次逼近型和双积分型两种A/D转换器而言,()的抗干扰能力强,()的转换速度快。

6.由555定时器构成的三种电路中,()和()是脉冲的整形电路。

7.与PAL相比,GAL器件有可编程的输出结构,它是通过对()进行编程设定其()的工作模式来实现的,而且由于采用了()的工艺结构,可以重复编程,使它的通用性很好,使用更为方便灵活。

二、根据要求作题:(共15分)1.将逻辑函数P=AB+AC写成“与或非”表达式,并用“集电极开路与非门”来实现。

2.图1、2中电路均由CMOS门电路构成,写出P、Q 的表达式,并画出对应A、B、C的P、Q波形。

三、分析图3所示电路:(10分)1)试写出8选1数据选择器的输出函数式;2)画出A2、A1、A0从000~111连续变化时,Y的波形图;3)说明电路的逻辑功能。

四、设计“一位十进制数”的四舍五入电路(采用8421BCD码)。

要求只设定一个输出,并画出用最少“与非门”实现的逻辑电路图。

(15分)五、已知电路及CP、A的波形如图4(a) (b)所示,设触发器的初态均为“0”,试画出输出端B和C的波形。

(8分)BC六、用T触发器和异或门构成的某种电路如图5(a)所示,在示波器上观察到波形如图5(b)所示。

试问该电路是如何连接的?请在原图上画出正确的连接图,并标明T的取值。

(6分)七、图6所示是16*4位ROM和同步十六进制加法计数器74LS161组成的脉冲分频电路。

《数字集成电路》期末试卷B(含答案)

浙江工业大学 / 学年第一学期 《数字电路和数字逻辑》期终考试试卷B姓名 学号 班级 任课教师一、填空题(本大题共10小题,每空格1分,共10分)请在每小题的空格中填上正确答案。

错填、不填均无分。

1.(1011111.01)2=( )102.若10010110是82421BCD 码的一组代码,则它对应的十进制数是________。

3.逻辑函数B A AB F +=的反函数F =________。

4.不会出现的变量取值所对应的最小项叫做 。

5.组合逻辑电路任何时刻的稳定输出仅仅只决定于__________各个输入变量的取值。

6.描述时序逻辑电路的逻辑表达式有驱动方程、________________和输出方程。

7.1K ×4位ROM ,有 位地址输入。

8.要把模拟量转化成数字量一般要经过四个步骤,分别称为采样、保持、________、编码。

9.D/A 转换器的主要参数有 、转换时间和转换精度。

10.集成单稳态触发电路的暂稳态维持时间取决于 。

二、选择题(本大题共10小题,每小题2分,共20分)在每小题列出的四个备选项中只有一个是符合题目要求的,请将其代码填写在题后的括号内。

错选、多选或未选均无分。

11.若已知Y XY YZ Z Y XY +=++,判断等式=+++))()((Z Y Z Y Y X Y Y X )(+成立的最简单方法是依据 规则。

【 】A .代入规则B .对偶规则C .反演规则D .互补规则12.F (A ,B ,C )的任意两个最小项之积等于 。

【 】 A .0 B .1 C .ABC D .ABC13.+0+1A A A ⋅⋅等于 。

【 】 A .0 B .1 C . A D .A 14.将TTL 与非门正常使用时,多余的输入端应 。

【 】 A .全部接高电平 B .部分接高电平,部分接地 C .全部接地 D .部分接地,部分悬空 15. S R 触发器不具有 功能。

数字集成电路习题答案

1.5 115 106

0.63 3 0.06 0.1

30 106

1.0

21.05

VIL

VM

VDD VM g

1.25 2.5 1.25 21.05

1.19V

VIH

VM

VM g

1.25 1.25 21.05

1.31V

NVH VDD VIH 2.5 1.31 1.19 NM L VIL 1.19

115 (2.072 2.072 )(1 0.06 2.5) 2

283.3A

(2) pmos :

VGT VGS VT 0 0.5 0.4 0.1 VDS

pmos处于饱和区,Vmin 0.1v

ID

kn'

(W L

) (VGTVm in

Vm2in 2

)(1

VDS

)

30 (0.1 0.05) 0.1 (1 0.11.25)

VT0(V) 0.43 -0.4

(V0.5) 0.4 -0.4

VDSAT(V) 0.63 -1

k’(A/V2) 115×10-6 -30×10-6

(V-1) 0.06 -0.1

1.假设设计一个通用0.25m CMOS工艺的反相器,其中PMOS晶体管的 最小尺寸为(W=0.75m,L=0.25m,即W/L=0.75/0.25) , NMOS晶体管

2.如下图所示,由NMOS组成的反相器,输出电容 CL=3pF,W/L=1.5um/0.5um,求tpHL,tpLH和tp

t pHL

ln 2ReqnCL

0.69 13k 3

3 pF

8.97ns

t pLH ln 2RLCL 0.69 75k 3 pF 155.25ns

数字集成电路设计专业考试试卷及答案

广东工业大学考试试卷答案(A卷)课程名称:数字集成电路设计试春满分100分考试时间:2014年1月13日(第19周星期二)一、名词释义(共20分)摩尔定律:当价格不变时,集成电路上可容纳的晶体管数目,约每隔18个月便会増加一倍,性能也将提fl—倍。

(4分)传播延时:tpHL,输岀由高变低翻转的响应时间,50%Vin->50%Vout5 tpLH,輸岀由低变高翩转的响应肘间,50%Vin->50%Vout^(4分)扇岀:连接到驱动门描岀端负載门的数目。

(4分)寄存器:存放二进制数据器件,由锁存器构成,一般为边沿触发。

(4分)时钟抖动:同一点上相继的时钟沿随时间的变动。

(4分)二、埴空(共40分)1.电感憫合噪声(2分)电容福合噪声(2分)电源地噪声(2分)2.扩散电容(2分)覆盖电容(2分)沟道电容(2分)3.全比例缩小(2分)电压恒定按比例缩小(2分)一般化缩小(2分)4.动态功耗(2分)短路功耗(2分)静态功耗(2分)5.2N (2分)N+1 (2分)N+2 (2分)6.同或F I~.IB^A3(2 分)异或Fl -.45-^5 (2分)7.全定制(2分)半定制(2分)8. a (2 分)三、分析设计(共40分)1.组合逻辑a. r = U*scD;b・若以最小尺寸反相器为参考,在该电路中,串联器件尺寸増大两倍,并联器件尺寸维持不变。

如图所示。

C.输入中最后穏定的信号为关铤信号,保证关键信号路径上的晶体管靠近输岀,可减小延时。

如图所示。

2.时序逻辑a.上升沿触发;工作原理:若理想时钟,当CLK=O时,T1导通,T2截止, 数据D通过T1保存到Ch当CLK=1时,T1截止,T2导通,数据D通过II, T2, 12传输到Q。

b.大于T1的传播延时;4:近似为0; ”切大于II, T2, 13的总传播延时。

3.系统时钟a.优点I H树时钟分布技术,理,想情况下的时钟偏差为零;缺点I易受工艺影响,实际几何形态不重要,电气上的对称更重要。

数字集成电路模拟集成电路考试题库

1、在数字集成电路中,以下哪个元件常用于存储二进制信息?A、电阻B、电容C、触发器D、电感(答案:C)2、模拟集成电路中,用于放大电信号的主要元件是?A、二极管B、晶体管C、电阻D、电容(答案:B)3、以下哪种逻辑门电路可以实现“与”运算?A、NOT门B、OR门C、AND门D、XOR门(答案:C)4、在数字电路中,时钟信号的主要作用是?A、提供电源B、控制信号同步C、放大信号D、转换信号格式(答案:B)5、模拟集成电路中,常用于稳定输出电压的元件是?A、运算放大器B、比较器C、稳压二极管D、晶体管(答案:C)6、数字集成电路中,D触发器的输出在何时更新?A、时钟信号上升沿B、时钟信号下降沿C、随时更新D、根据输入信号变化(答案:A,注:也可能是B,具体取决于触发器类型,但此题通常按常见上升沿触发考虑)7、以下哪种电路常用于将模拟信号转换为数字信号?A、放大器B、滤波器C、模数转换器(ADC)D、数模转换器(DAC)(答案:C)8、在模拟集成电路中,用于产生稳定电流源的元件或电路是?A、电流镜B、电压源C、电阻网络D、电容器(答案:A)9、数字集成电路中,用于实现计数功能的电路是?A、加法器B、寄存器C、计数器D、译码器(答案:C)10、以下哪种电路或元件在模拟集成电路中常用于信号的滤波?A、放大器B、比较器C、滤波器D、振荡器(答案:C)。

数字电路期末试卷(含答案哦)

《数字电路》试卷一、填空题(每空1分,共20分)1. 有一数码10010011,作为自然二进制数时,它相当于十进制数( ),作为8421BCD 码时,它相当于十进制数( )。

2.三态门电路的输出有高电平、低电平和( )3种状态。

3.TTL与非门多余的输入端应接( )。

4.TTL 集成JK 触发器正常工作时,其d R 和d S 端应接( )电平。

5. 已知某函数⎪⎭⎫ ⎝⎛+⎪⎭⎫ ⎝⎛++=D C AB D C A B F ,该函数的反函数F =( )。

6. 如果对键盘上108个符号进行二进制编码,则至少要( )位二进制数码。

7. 典型的TTL 与非门电路使用的电路为电源电压为( )V ,其输出高电平为( )V ,输出低电平为( )V , CMOS 电路的电源电压为( ) V 。

8.74LS138是3线—8线译码器,译码为输出低电平有效,若输入为A 2A 1A 0=110时,输出 01234567Y Y Y Y Y Y Y Y 应为( )。

9.将一个包含有32768个基本存储单元的存储电路设计16位为一个字节的ROM 。

该ROM 有( )根地址线,有( )根数据读出线。

10. 两片中规模集成电路10进制计数器串联后,最大计数容量为( )位。

11.);Y 3 =( )。

12. 某计数器的输出波形如图1所示,该计数器是( )进制计数器。

13.驱动共阳极七段数码管的译码器的输出电平为( )有效。

二、单项选择题(本大题共15小题,每小题2分,共30分)(在每小题列出的四个备选项中只有一个是最符合题目要求的,请将其代码填写在题后的括号内。

错选、多选或未选均无分。

)1. 函数F(A,B,C)=AB+BC+AC 的最小项表达式为( ) 。

A .F(A,B,C)=∑m (0,2,4) B. (A,B,C)=∑m (3,5,6,7) C .F(A,B,C)=∑m (0,2,3,4) D. F(A,B,C)=∑m (2,4,6,7)2.8线—3线优先编码器的输入为I 0—I 7 ,当优先级别最高的I 7有效时,其输出012Y Y Y ••的值是( )。

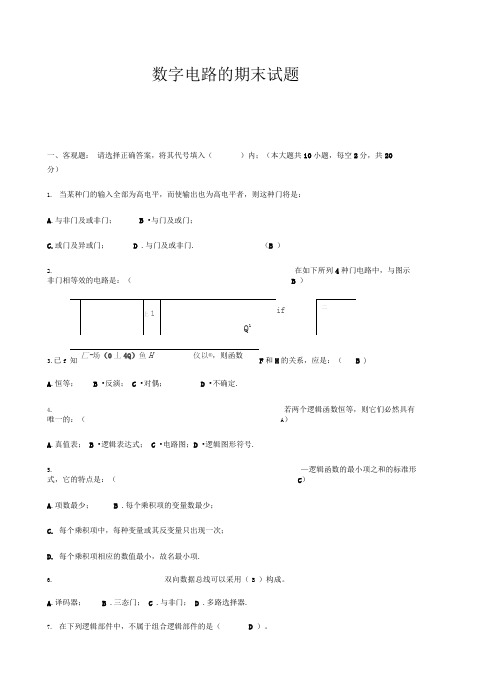

数字电路的期末试题及标准答案

数字电路的期末试题一、客观题:请选择正确答案,将其代号填入()内;(本大题共10小题,每空2分,共20分)1.当某种门的输入全部为高电平,而使输出也为高电平者,则这种门将是:A.与非门及或非门; B •与门及或门;C.或门及异或门; D .与门及或非门. (B )2.在如下所列4种门电路中,与图示非门相等效的电路是:( B )A.恒等; B •反演;C •对偶; D •不确定.4.若两个逻辑函数恒等,则它们必然具有唯一的:(A)A.真值表;B •逻辑表达式; C •电路图;D •逻辑图形符号.5.—逻辑函数的最小项之和的标准形式,它的特点是:(C)A.项数最少; B .每个乘积项的变量数最少;C.每个乘积项中,每种变量或其反变量只出现一次;D.每个乘积项相应的数值最小,故名最小项.6.双向数据总线可以采用(B )构成。

A.译码器; B .三态门;C .与非门; D .多路选择器.7.在下列逻辑部件中,不属于组合逻辑部件的是( D )。

A.译码器; B .编码器;C .全加器; D .寄存器.8.八路数据选择器,其地址输入端(选择控制端)有( C )个。

8个 B . 2个 C)DQ)CABC1001BD01解T LIB►i(b)三、非客观题(本题两小题,共20分)1.如图所示为三输入变量的或门和与门的逻辑图。

根据两种不同的输入波形 (见图b ),画出Y i 、Y 2的波形。

(本题共 8分,每个Y i 、丫2各2分) 1用公式法化简逻辑函数: 给定约束条件为 m )+m 5+ m io +m i5 =09.为将D 触发器转换为T 触发器,如图所示电路的虚线框内应是(、化简下列逻辑函数(每小题5分,共10分)2.用卡诺图法化简逻辑函数:Y(A,B,C,D)=刀m(2 ,3,7,8,11,14)A . A .或非门B .与非门C •异或门D •同或门 10.为产生周期性矩形波,应当选用( A .施密特触发器 B •单稳态触发器 C.多谐振荡器 D .译码器 =(*十劝十個十歹)+旷=1(1分)解乙蚀J 询卡诺图(3分人』 优简得:Y = AC^BD + CD 口分”2 •某一组合逻辑电路如图所示,试分析其逻辑功能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1 浙江工业大学/学年第一学期 《数字电路和数字逻辑》期终考试试卷 A

姓名 ___________ 学号 ____________ 班级 ___________ 任课教师 _________ 题序 -一一 -二二 -三 四 总评 记分 一、填空题(本大题共 10小题,每空格1分,共10分) 请在每小题的空格中填上正确答案。错填、不填均无分。 1 •十进制数(68) io对应的二进制数等于 __________________ ; 2•描述组合逻辑电路逻辑功能的方法有真值表、逻辑函数、卡诺图、逻辑电路图、波形图 和硬件描述语言(HDL )法等,其中 ______________________ 描述法是基础且最直接。 3. A二1可以简化为 _______________ 。 4•图1所示逻辑电路对应的逻辑函数 L等于 _________________ 。

5•如图2所示,当输入 C是(高电平,低电平) ____________ 时,丫二AB。 6. 两输入端TTL与非门的输出逻辑函数 Z =AB,当A=B=1时,输出低电平且 VZ=0.3V , 当该与非门加上负载后,输出电压将 (增大,减小) ___________ 。 7. ___________________________________________________ Moore型时序电路和 Mealy型时序电路相比, ____________________________________________ 型电路的抗干扰能力更强。 &与同步时序电路相比,异步时序电路的最大缺陷是会产生 _______________ 状态。 9. ________________________________________________ JK触发器的功能有置 0、置1、保持和 ___________________________________________________ 。 10. _____________________________________________________________________ 现有容量为210用位的SRAM2114 ,若要将其容量扩展成 211X

8位,则需要 ______________________ 片这样

的 RAM。 二、选择题(本大题共 10小题,每小题2分,共20分) 在每小题列出的四个备选项中只有一个是符合题目要求的,请将其代码填写在题后的 括号内。错选、多选或未选均无分。 11. 十进制数(172) 10对应的8421BCD编码是 ________ 。 【 】 A . ( 11110 1 0) 8421BCD B . ( 10111010) 8421BCD

B C

A

图1 2

C. (000101110010) 8421BCD D . ( 101110010) 8421BCD

12. ____________________________________ 逻辑函数 Z(A, B, C^AB AC包含 个最小项。 ____________________________________________ 【 】 3 C. 4 13. 设标准TTL与非门Z =AB的电源电压是+5V,不带负载时输出高电平电压值等于 +3.6V ,

输出低电平电压值等于 0.3V。当输入端 A、B电压值VA=0.3V, VB=3.6V和VA=VB=3.6V两 种情况下,输出电压值 VZ分别为 ________ 。 【 】

B . 3.6V , 3.6V

14•图3所示电路的输出逻辑函数乙等于 A. ABCD C. AB CD

20.某十位D/A转换器满量程输出电压为 5.115V,则当输入 D= ( 0100100000) 2时,输出 电压为( )伏。 【 】

6小题,21-26每小题6分,27小题12分,共48分) 21.已知逻辑函数 Z (A,B,C,D)=刀m (0,2,3,7,8,9) + 刀d (10,11,12,13,14,15),求逻辑函数

A. 5V, 5V C. 3.6V, 0.3V D. 0.3V , 3.6V

B. AB+CD D. AB CD

2-4译码器 A Ao

丫

3 B—— A1

丫

2 丫

1 r S

丫

0

Z2

15. 图3 图4电路是由二进制译码器组成的逻辑电路,输出 Z2等于 A. AB AB B.

AB AB

C. AB AB D. AB AB

16.

17.最能直观反映时序电路状态变化关系的是 _________ A .逻辑电路图 B.时序图 C.状态真值表 18 .可以对脉冲波形整形的电路是 ( A .施密特触发器 B . T触发器 同样分辨率和时钟脉冲下,并行比较型

D .状态转移图

19. )。 C .多谐振荡器 A/D转换型A/D转换器中完成一次模数转换时间最长的是 _ A .双积分型 B .逐次逼近型 C.并行比较型

D .译码器 逐次逼近型 A/D转换器和双积分 一转换器。 【 D .都一样

A . 5.115V B . 1.44V C. 2.34V D . 0.44V 三、分析题(本大题共

VCC

ZI

【 】 o

C A B D 图5

A CP

n 1 图5所示所示时序电路中,实现 Q =Qn的电路是 4

Z的最简"与或”表达式。 22•分析图6所示电路输出Z的最简与或逻辑函数表达式。

23.图7是用4选1数据选择器设计的一个逻辑电路, 试写出输出逻辑函数 Z的最简与或表 达式。 表14选1数据选择器功能表 Ai A0

E W

XX 1 0

0 0 0 D0

0 1 0 Di

1 0 0 D2

1 1 0 D3

— Tlr —Tlr —r I IF I —r I

十

■1_|

C 5

图8 25. 移位寄存器 CC40194功能如表2所示。设CC40194初态为Q3Q2QIQO= 0000,电路如 图9,试画出十个以上 CP脉冲作用下移位寄存器的状态转移图。

Z r Ai W A0 MUX

E D0 Di D2 D3

1 1 -----

A B

1 6 图9 表2 CC40194功能表 输入 输出 RD S1 S0 DIR D IL CP D0 D1 D2 D3 Q0 Q1 Q2 Q3

L XXXXXXXX X L L L L H H H X X f d0 d1 d2 d3

d0 d1 d2 d

3

H L L XXX XXX X

Q0 Q1 Q2 Q

3

H L H A X f X X X X A Q0 Q1 Q

2

H H L X B f X X X X Q1 Q2 Q3 B

26. CMOS集成定时器555组成的电路如图10所示,试问: (1) 说出电路的名称; (2) 画出VC和vo输出电压波形(设输入 VI低电平宽度足够窄)。

+6V 6V

0 VO

+6V

0 图10

27•已知某同步时序电路如图 11所示,试: (1 )分析电路的状态转移图,并要求给出详细分析过程。 (2) 电路逻辑功能是什么,能否自启动? (3) 若计数脉冲fcp频率等于700Hz,从Q2端输出时的脉冲频率是多少

RD VC

亠

RD DISC TH UDD

OUT VO

0 L

VC i

+6V

TR

0 1 1

X X X X

GND CO p. F 7

四、设计题(本大题共 3小题,第28小题10分,第29小题12分,共22分) 28.如图12所示,为一工业用水容器示意图,图中虚线表示水位, A、B、C电极被水浸没 时会有信号输出,试用 与非门构成的电路来实现下述控制作用:水面在 A、B间,为正常状 态,亮绿灯G;水面在B、C间或在A以上为异常状态,点亮黄灯 Y;面在C以下为危险状 态,点亮红灯 R。要求写出设计过程。

29.某四位二进制加/减计数器的逻辑符号如图 13 (a)所示,功能表如表 3所示。 (1 )用该集成计数器和少量与非门计一个 8421BCD编码的6进制加法计数器。 (2)分析图13 ( b)电路的逻辑功能,并画出完整的状态转移图。

(a) (b) 图13 表3 CP+ CP- CR LD D3 D2 D1 D0 Q3 Q2 Q1 Q0

丨丨1 L

L Q0 Q1 Q2 Q3

—/ CP+ LD —

—> CP- CR D0 D1 D2 D3

1 1 1

CP > cp+Qo Q1 > CP- D0 D1 Q2 Q3 LD CR D2 D3

Qo Q

i Q

2

图11