高速缓存工作原理

cache工作原理

cache工作原理

Cache是一种高速缓存,它用于存储常用数据的副本以便快速访问。

Cache工作原理如下:

1. 当一个请求到达计算机时,Cache会检查这个请求是否已经有缓存数据。

如果有,它将直接返回缓存数据,而不是从原始数据源(如数据库或磁盘)获取数据。

2. 如果请求的数据不在Cache中,则Cache会从原始数据源获取数据,并将其存储在Cache中,以便今后的访问。

3. Cache有一个容量限制。

一旦超过容量限制,Cache将根据一定的规则(例如最近最少使用)删除最不常用的数据。

4. 当数据源上的数据发生更改时,Cache中存储的数据将不再有效。

此时,Cache将需要更新或重新获取数据。

Cache工作原理的优势在于它能够显著提高应用程序的性能,因为它提供了快速的访问速度,减少了对慢速数据源(如数据库)的依赖。

同时,由于Cache存储数据的方式可以提高数据的访问速度,可以在大多数情况下减少网络流量和减轻数据源的负载。

cpu高速缓存的工作原理

cpu高速缓存的工作原理CPU高速缓存的工作原理概述:CPU高速缓存是为了解决CPU与主存之间速度不匹配的问题而设计的,其主要作用是提高CPU的访问速度。

本文将从以下几个方面来详细介绍CPU高速缓存的工作原理。

一、什么是CPU高速缓存?二、为什么需要CPU高速缓存?三、如何实现CPU高速缓存?四、CPU高速缓存的工作原理五、常见的CPU高速缓存类型六、如何优化CPU高速缓存性能一、什么是CPU高速缓存?简单来说,CPU高速缓存就是位于CPU内部的一块小型且容量较小的内存,它用于暂时保存最近使用过的数据和指令,以便在下次访问时可以更快地获取到这些数据和指令。

二、为什么需要CPU高速缓存?由于主板与内存之间存在较大的距离,因此在处理器需要访问内存时会有一定延迟。

而且随着计算机技术不断发展,处理器运行频率越来越快,但内存读写速度却没有相应提升。

这就导致了一个问题:处理器运行时需要等待内存读写操作完成,从而浪费了大量的时间。

为了解决这个问题,CPU高速缓存被设计出来。

三、如何实现CPU高速缓存?CPU高速缓存一般都是由SRAM(静态随机存储器)组成的。

与DRAM(动态随机存储器)不同,SRAM具有更快的访问速度和更低的功耗。

但是,SRAM价格比DRAM贵得多,因此高速缓存容量相对较小。

四、CPU高速缓存的工作原理当处理器需要访问内存时,它首先会检查高速缓存中是否已经存在所需数据或指令。

如果存在,则直接从高速缓存中读取;如果不存在,则需要从内存中读取,并将数据或指令保存到高速缓存中以备下次使用。

CPU高速缓存在工作时分为以下几个步骤:1.地址映射当处理器发出访问请求时,高速缓存会首先将请求地址映射到相应的高速缓存块上。

这个过程一般通过哈希算法来实现。

2.检索数据如果所请求的数据已经存在于高速缓存中,则可以直接从其中读取;否则就需要从主内存中获取数据并将其保存到高速缓存中以便下次使用。

3.替换数据当高速缓存中的空间不足时,就需要将一些数据替换出去以腾出空间。

cache相关概念及工作原理介绍

cache相关概念及工作原理介绍【原创版】目录一、Cache 的概念二、Cache 的作用三、Cache 的工作原理四、Cache 的类型与结构五、Cache 的应用场景正文一、Cache 的概念Cache,即高速缓存,是一种存储技术,它位于主存与 CPU 之间,作用是提高 CPU 访问存储器的速度。

Cache 可以看作是主存的一个高速副本,它将主存中频繁访问的数据复制到自身,当 CPU 需要再次访问这些数据时,可以直接从Cache 中获取,从而减少了 CPU 与主存之间的访问延迟。

二、Cache 的作用Cache 的主要作用是提高 CPU 的运行效率。

随着 CPU 处理速度的提升,主存的访问速度逐渐成为系统性能的瓶颈。

通过使用 Cache,可以减少 CPU 等待主存读写完成的时间,从而提高 CPU 的执行效率。

三、Cache 的工作原理Cache 的工作原理主要包括两个方面:一是缓存策略,即如何判断哪些数据需要被缓存;二是替换策略,即当 Cache 空间不足时,如何选择淘汰哪些缓存数据。

1.缓存策略缓存策略主要根据程序的访问模式来判断。

一般来说,缓存策略可以分为以下三种:- 时域局部性(Temporal Locality):程序在一段时间内多次访问相同的数据。

这种局部性可以通过缓存来提高访问速度。

- 空间局部性(Spatial Locality):程序在访问一个数据时,很可能还会访问其附近的数据。

这种局部性可以通过缓存来提高访问速度。

- 随机访问(Random Access):程序访问的数据与缓存中存储的数据无关,这种访问模式无法通过缓存来提高访问速度。

2.替换策略当 Cache 空间不足时,需要选择一些缓存数据进行替换。

替换策略主要有以下几种:- 最近最少使用(Least Recently Used,LRU):选择最近最少使用的数据进行替换。

- 时间戳(Timestamp):记录每个数据在 Cache 中的时间,选择最早进入Cache 的数据进行替换。

计算机基础知识认识计算机存储器中的高速缓存

计算机基础知识认识计算机存储器中的高速缓存计算机存储器是计算机系统中的一个重要组成部分,用于存储和读取数据和指令。

而在计算机存储器中,高速缓存起着至关重要的作用。

它是一种特殊的存储器,通过存储临时数据来提高计算机的运行效率。

本文将介绍计算机存储器中高速缓存的定义、特点、类型以及工作原理等内容。

1. 高速缓存的定义高速缓存(Cache)是计算机存储器的一种,它是位于CPU内部或者靠近CPU的一个小容量存储器,用于存储最近被访问或者即将被访问的数据和指令。

它的存在可以减少CPU访问内存的次数,提高计算机系统的运行速度。

2. 高速缓存的特点(1)快速访问:高速缓存位于CPU内部或者靠近CPU,因此具有很高的访问速度,可以迅速响应CPU的请求。

(2)小容量:相比主存储器或者硬盘等大容量存储器,高速缓存的容量较小,一般只有几十KB到几十MB。

这是为了提高缓存的命中率,并保持其快速访问的特点。

(3)自动管理:高速缓存的管理由硬件来完成,而不需要用户或者软件干预。

硬件可以根据缓存的策略来自动决定是否将数据从主存储器加载到缓存中,以及何时将缓存中的数据写回主存储器。

3. 高速缓存的类型根据在计算机系统中的位置和层次结构,高速缓存可以分为多级缓存。

常见的高速缓存类型包括一级缓存(L1 Cache)、二级缓存(L2 Cache)和三级缓存(L3 Cache)。

一级缓存位于CPU内部,速度最快;而二级缓存和三级缓存则通常位于CPU外部或者与主存储器相连,速度相对较慢。

4. 高速缓存的工作原理高速缓存的工作原理可以简单描述为以下几个步骤:(1)当CPU需要访问数据或指令时,首先会在高速缓存内进行搜索。

如果搜索成功,并且缓存中的数据是最新的,即命中缓存(Cache Hit)。

(2)如果搜索失败,即缓存中不存在所需的数据或指令,就会发生缓存未命中(Cache Miss)。

(3)当发生缓存未命中时,CPU会从主存储器中加载所需的数据或指令,并将其存储到高速缓存中。

cache工作原理

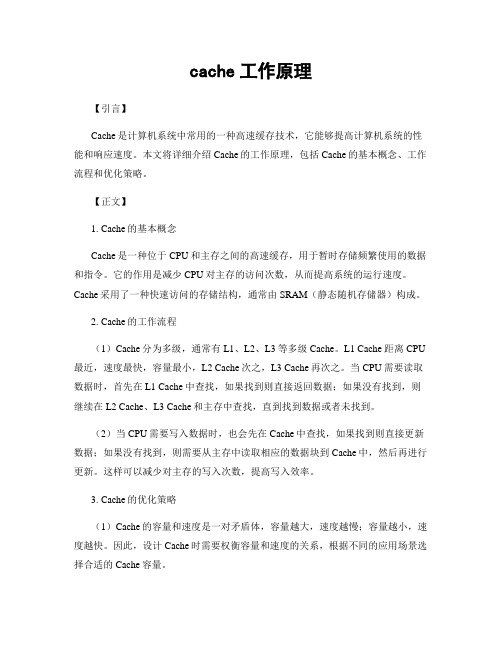

cache工作原理【引言】Cache是计算机系统中常用的一种高速缓存技术,它能够提高计算机系统的性能和响应速度。

本文将详细介绍Cache的工作原理,包括Cache的基本概念、工作流程和优化策略。

【正文】1. Cache的基本概念Cache是一种位于CPU和主存之间的高速缓存,用于暂时存储频繁使用的数据和指令。

它的作用是减少CPU对主存的访问次数,从而提高系统的运行速度。

Cache采用了一种快速访问的存储结构,通常由SRAM(静态随机存储器)构成。

2. Cache的工作流程(1)Cache分为多级,通常有L1、L2、L3等多级Cache。

L1 Cache距离CPU 最近,速度最快,容量最小,L2 Cache次之,L3 Cache再次之。

当CPU需要读取数据时,首先在L1 Cache中查找,如果找到则直接返回数据;如果没有找到,则继续在L2 Cache、L3 Cache和主存中查找,直到找到数据或者未找到。

(2)当CPU需要写入数据时,也会先在Cache中查找,如果找到则直接更新数据;如果没有找到,则需要从主存中读取相应的数据块到Cache中,然后再进行更新。

这样可以减少对主存的写入次数,提高写入效率。

3. Cache的优化策略(1)Cache的容量和速度是一对矛盾体,容量越大,速度越慢;容量越小,速度越快。

因此,设计Cache时需要权衡容量和速度的关系,根据不同的应用场景选择合适的Cache容量。

(2)Cache的替换策略是指当Cache已满时,如何选择替换哪些数据块。

常用的替换策略有随机替换、最近至少使用替换(LRU)等。

LRU替换策略是指替换最长期未被访问的数据块,以保证Cache中存储的是最常用的数据。

(3)Cache的预取策略是指在Cache中预先加载可能被使用到的数据块。

常用的预取策略有预取一致性(PC)和预取非一致性(NPC)。

PC策略是在访问一个数据块时,将其相邻的数据块一并加载到Cache中;NPC策略是根据程序的访问模式,预先加载可能被使用到的数据块。

简述高速缓存的工作原理

简述高速缓存的工作原理嘿,朋友们!今天咱来聊聊高速缓存这个神奇的玩意儿。

你说它像不像一个特别会来事儿的小机灵鬼呀!想象一下,你正在电脑上疯狂操作,一会儿打开这个软件,一会儿又要点那个文件。

这时候,如果每次都要从慢悠悠的大仓库(硬盘)里去拿东西,那得多费劲呀,得等半天呢!但有了高速缓存就不一样啦。

高速缓存就像是一个在前线的小仓库,它把你经常会用到的一些数据呀、指令呀啥的,先悄悄地藏起来一部分。

这样,当你下一次要用的时候,它就能快速地给你拿出来,根本不用再大老远地跑去硬盘那里找啦!这多方便呀,就好比你每天出门要带的东西,你直接放在门口的小柜子里,而不是每次都去房间最里面的大衣柜里翻找,对吧?你看啊,高速缓存它很聪明呢,它知道哪些东西是你经常用的,然后就把这些宝贝留下来。

而且它还会不断地更新,把不那么重要的给替换掉,腾出地方来放新的重要的东西。

这就好像你整理自己的小包包,把不常用的东西拿出来,再把常用的放进去。

高速缓存的速度那可是杠杠的!比硬盘快多啦。

它就像是短跑冠军,而硬盘就是慢悠悠的散步者。

有了它在,你的电脑才能跑得飞快呀,不然就会像老牛拉车一样慢吞吞的。

比如说你玩游戏的时候,那些画面呀、操作呀,要是没有高速缓存帮忙,那得卡成啥样呀!说不定你正玩得起劲呢,突然就卡住不动了,那多扫兴呀!高速缓存可不会让这种事情发生,它总是能在关键时刻给你提供最及时的支持。

再想想,要是没有高速缓存,我们每天得浪费多少时间在等待电脑反应上呀!那我们的工作效率得低成啥样呀!所以说呀,高速缓存可真是我们的好帮手呢!它虽然小小的,但是作用可大了去啦!它就像是一个默默无闻的幕后英雄,一直在为我们的电脑顺畅运行默默地付出着。

我们真应该好好感谢它呀!总之,高速缓存就是电脑世界里的一个神奇存在,让我们的电脑使用体验变得更加流畅和愉快。

它就像是给电脑装上了一双翅膀,让它能够自由翱翔!你说它是不是很棒呢?。

高速缓存的工作原理

高速缓存的工作原理

嘿,咱今儿来唠唠高速缓存的工作原理哈!你说这高速缓存啊,就好比是一个特别机灵的小助手。

咱平时用电脑或者手机的时候,是不是经常要反复用到一些东西呀,比如你喜欢的那张照片,或者经常玩的那个游戏。

这高速缓存呢,就会悄悄地把这些东西先藏起来一部分。

就好像你出门总喜欢在兜里揣几块糖,随时能拿出来吃一样。

它特别会瞅准时机,在你需要之前就把那些常用的数据啊、程序啊什么的准备好。

你想啊,要是每次你想用个啥都得慢悠悠地从大老远的地方去取,那得多耽误事儿啊!高速缓存可不会让这种情况发生,它就像个聪明的小管家,帮你把常用的东西放在最容易拿到的地方。

比如说你玩游戏,每次进入游戏的那一小段动画,高速缓存就把它记住了,等你下次再玩的时候,“唰”的一下就给你调出来了,快得很呢!这不就省了你好多等待的时间嘛。

而且啊,它还很会挑重要的东西存起来。

就跟你整理书包似的,把最重要的书和文具放在最上面,方便随时拿出来用。

高速缓存也是这样,把那些你最常用的信息放在最前面,让你的操作更流畅。

你想想,如果没有高速缓存,那得多麻烦呀!每次都得从头开始找东西,那得多耽误时间啊!高速缓存就像是你的贴心小棉袄,默默地为你服务,让你的生活更加便捷。

它真的是太重要啦!你说要是没有它,我们得浪费多少时间在等待上啊!所以啊,可别小瞧了这个小小的高速缓存,它可是有着大作用呢!它能让你的设备运行得更快,让你的体验更好。

咱平时用手机或者电脑的时候,可得好好感谢这个默默付出的小助手呀!它一直在那里,为我们的便捷生活努力着。

是不是很厉害?是不是很神奇?反正我是觉得它超棒的!你呢,是不是也这么觉得呀?

原创不易,请尊重原创,谢谢!。

cache工作原理

cache工作原理1. 概述Cache是计算机系统中的一种高速缓存存储器,用于提高数据访问速度。

它位于主存和CPU之间,用于存储最常用的数据和指令。

Cache工作原理是通过在高速缓存中存储最常访问的数据,以便CPU能够更快地访问这些数据,从而提高系统的整体性能。

2. Cache的结构Cache通常由多级结构组成,其中包括L1、L2、L3等多级缓存。

每一级缓存都有不同的大小和访问速度,越靠近CPU的缓存级别越小且速度越快。

一般来说,L1缓存是最小且最快的,L3缓存是最大且最慢的。

3. Cache的工作原理当CPU需要访问数据时,它首先会检查L1缓存。

如果数据在L1缓存中找到,CPU就可以直接从缓存中读取数据,这样可以大大提高访问速度。

如果数据不在L1缓存中,CPU会继续检查更大的L2缓存,以此类推,直到找到数据或者最后一级缓存。

如果数据在任何一级缓存中找到,CPU会将数据加载到更靠近CPU的缓存级别中,并从缓存中读取数据。

如果数据在所有缓存中都找不到,CPU将从主存中读取数据,并将其加载到L1缓存中,以备将来的访问。

4. Cache的命中和未命中当CPU在缓存中找到所需的数据时,称为“命中”。

如果数据不在缓存中,称为“未命中”。

命中率是衡量缓存性能的重要指标。

高命中率意味着大部分数据都能够从缓存中读取,从而提高系统性能。

未命中率高则意味着缓存无法满足CPU的需求,导致频繁从主存中读取数据,降低系统性能。

5. Cache的替换策略当缓存满时,如果需要将新的数据加载到缓存中,就需要替换掉一部分已有的数据。

常用的替换策略有最近最少使用(LRU)、随机替换等。

LRU策略是指替换最近最长时间未被访问的数据,以便为新的数据腾出空间。

6. Cache的写策略Cache的写策略包括写回(Write Back)和写直达(Write Through)两种方式。

写回策略是指当CPU修改缓存中的数据时,只会更新缓存数据,不会立即写回主存,而是等到缓存被替换出去时才写回主存。

cache工作原理

cache工作原理一、概述Cache是计算机系统中常用的一种高速缓存技术,用于提高数据访问速度。

它是位于CPU和主内存之间的一层存储,通过存储最常用的数据和指令,减少CPU等待数据的时间,从而提高系统的整体性能。

本文将详细介绍Cache的工作原理。

二、Cache的组成1. Cache结构Cache由多个Cache行组成,每一个Cache行包含一个标记(Tag)、一组数据(Data)和一些控制位(Valid、Dirty等)。

2. Cache层次结构计算机系统中通常存在多级Cache,如L1 Cache、L2 Cache等。

L1 Cache位于CPU内部,速度最快,容量较小;L2 Cache位于CPU外部,速度较慢,容量较大。

多级Cache的目的是在速度和容量之间进行平衡。

三、Cache的工作流程1. 访问过程当CPU需要读取数据时,首先会在Cache中查找。

如果数据在Cache中命中(Hit),则直接从Cache中读取;如果未命中(Miss),则需要从主内存中读取数据,并将数据存入Cache中。

2. 命中率命中率是衡量Cache性能的重要指标,表示CPU在访问时命中Cache的比例。

命中率越高,Cache的效果越好。

命中率可以通过统计命中次数和访问次数来计算。

3. 替换策略当Cache已满且需要存储新数据时,需要进行替换操作。

常见的替换策略有随机替换、先进先出(FIFO)替换和最近至少使用(LRU)替换等。

其中,LRU替换策略根据数据的访问情况来选择替换的数据,通常能够获得较好的性能。

4. 写操作Cache支持读写操作,当CPU进行写操作时,有两种方式:写回(Write Back)和写直达(Write Through)。

写回方式先将数据写入Cache,当Cache行被替换时才写回主内存;写直达方式直接将数据写入Cache和主内存。

写回方式可以减少主内存的写操作,提高性能。

四、Cache的优化技术1. Cache块大小Cache块大小的选择对性能有重要影响。

cache工作原理

cache工作原理1. 介绍Cache(高速缓存)是计算机系统中的一种关键组件,用于提高数据访问速度和系统性能。

它位于CPU与主内存之间,作为临时存储器,存储最常用的数据和指令。

本文将详细介绍Cache的工作原理及其相关概念。

2. Cache的层次结构Cache的层次结构通常由L1、L2和L3三级组成。

L1 Cache位于CPU内部,速度最快但容量最小;L2 Cache位于CPU与主内存之间,速度较快,容量适中;L3 Cache位于CPU外部,速度较慢但容量较大。

数据从L1 Cache开始查找,如果未找到,则继续在L2和L3 Cache中查找,直到找到或者在主内存中找到。

3. Cache的工作原理当CPU需要访问数据时,首先会在Cache中进行查找。

如果数据在Cache中找到(命中),则称为Cache命中,CPU可以直接从Cache中读取数据,避免了访问主内存的时间延迟。

如果数据未在Cache中找到(未命中),则需要访问主内存,将数据加载到Cache中,并返回给CPU。

Cache的目标是尽可能提高命中率,减少对主内存的访问次数,从而提高系统性能。

4. Cache的替换策略当Cache已满时,需要替换一部分数据以腾出空间来存储新的数据。

常见的替换策略有:最近最少使用(LRU)、先进先出(FIFO)和随机替换等。

LRU策略将最近最少使用的数据替换,FIFO策略将最早进入Cache的数据替换,随机替换则随机选择一部分数据进行替换。

替换策略的选择需要根据具体应用场景和性能需求来确定。

5. Cache的写策略Cache的写策略决定了数据何时写回主内存。

常见的写策略有:写回(Write Back)和写直达(Write Through)。

写回策略在Cache中修改数据时,不立即写回主内存,而是等到Cache中的数据被替换时才写回。

写直达策略则在Cache中修改数据时立即写回主内存。

写回策略可以减少对主内存的写操作次数,提高性能,但也增加了数据一致性的复杂性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

程序访问内存地址: cpu送来一个访存地址时 送来一个访存地址时, (3)程序访问内存地址:当cpu送来一个访存地址时,系统查寻映射表判断该地址所 在内存块是否在cache cache中 若在,则可直接访问cache 这种情况称为cache命中; cache, cache命中 在内存块是否在cache中,若在,则可直接访问cache,这种情况称为cache命中;若 不然,则直接访问内存,并把地址所在的主存块移入cache块中。 cache块中 不然,则直接访问内存,并把地址所在的主存块移入cache块中。

中国科学院上海微系统与信息技术研究所

Shanghai Institute of Microsystem and Information Technology, Chinese Academy of Sciences, China

Cache写操作: 写操作: 写操作 不必把地址单元所在的整块内容调入Cache中; (1)不命中:只向主存写入信息 不必把地址单元所在的整块内容调入 )不命中:只向主存写入信息,不必把地址单元所在的整块内容调入 中 与主存的一致性问题,三种处理方式 (2)命中:保持 )命中:保持Cache与主存的一致性问题 三种处理方式 与主存的一致性问题 三种处理方式: 1、直写式:CPU在向 、直写式: 在向Cache写入数据时 也把数据写入主存以保证 写入数据时,也把数据写入主存以保证 在向 写入数据时 也把数据写入主存以保证Cache和主存中相应 和主存中相应 单元数据的一致性。 单元数据的一致性。 简单可靠,更新时对主存写入 速度受影响。 更新时对主存写入,速度受影响 简单可靠 更新时对主存写入 速度受影响。 2、缓写式:CPU更新 、缓写式: 更新Cache时不直接更新主存中的数据 把更新数据送入一个缓存器暂 时不直接更新主存中的数据,把更新数据送入一个缓存器暂 更新 时不直接更新主存中的数据 在适当的时候再把缓存器中的内容写入主存。 存,在适当的时候再把缓存器中的内容写入主存。 在适当的时候再把缓存器中的内容写入主存 CPU不必等待主存写入而造成的时延 提高了速度 但缓存器容量有限 只锁存一次写 不必等待主存写入而造成的时延,提高了速度 但缓存器容量有限,只锁存一次写 不必等待主存写入而造成的时延 提高了速度,但缓存器容量有限 入的数据,如果是连续写入 如果是连续写入,CPU仍需要等待。 仍需要等待。 入的数据 如果是连续写入 仍需要等待 3、回写式:CPU只向 、回写式: 只向Cache写入 并用标记加以注明 直到 写入,并用标记加以注明 直到Cache中被写过的块要被进入 只向 写入 并用标记加以注明,直到 中被写过的块要被进入 的信息块取代时,才一次写入主存 才一次写入主存。 的信息块取代时 才一次写入主存。 写入的是中间结果,速度快 避免了不必要的冗余写操作,但结构上较复杂 速度快,避免了不必要的冗余写操作 但结构上较复杂。 写入的是中间结果 速度快 避免了不必要的冗余写操作 但结构上较复杂。

中国科学院上海微系统与信息技术研究所

Shanghai Institute of Microsystem and Information Technology, Chinese Academy of Sciences, China

1.全相联方式 全相联方式

地址映象规则:主存的任意一块可以映象到 地址映象规则:主存的任意一块可以映象到Cache中的任意一块 中的任意一块 (1) 主存与缓存分成相同大小的数据块。 主存与缓存分成相同大小的数据块。 (2) 主存的某一数据块可以装入缓存的任意一块空间中。 主存的某一数据块可以装入缓存的任意一块空间中。

Cache提高存储器的平均访问速度的原因 提高存储器的平均访问速度的原因: (4)Cache提高存储器的平均访问速度的原因: 时间局部性:如果一个存储项被访问,则可能很快被再次访问。 时间局部性:如果一个存储项被访问,则可能很快被再次访问。 空间局部性:如果一个存储项被访问, 空间局部性:如果一个存储项被访问,则它邻近的项也可能很快被访问

中国科学院上海微系统与信息技术研究所

Shanghai Institute of Microsystem and Information Technology, Chinese Academy of Sciences, China

高速缓存

Cache工作原理 工作原理 Cache一致性问题 一致性问题 Cache与主存地址映射 与主存地址映射

中国科学院上海微系统与信息技术研究所

Shanghai Institute of Microsystem and Information Technology, Chinese Academy of Sciences, China

现代计算系统的存储器通常为层次体系结构, 现代计算系统的存储器通常为层次体系结构, CPU 使用了高速 缓冲系统来平衡芯片上寄存器的高速计算速度与芯片外其他层次存储 器之间较低的数据存取速度之间的差距。 器之间较低的数据存取速度之间的差距。

主存到cache映射: 存和Cache是由同样大小的块组成,主存以块为单位映象到 cache映射 是由同样大小的块组成, (2)主存到cache映射:主存和 是由同样大小的块组成 Cache中。地址映射方式有全相联映射、直接映射、组相联映射。工作原理相似,映 中 地址映射方式有全相联映射、直接映射、组相联映射。工作原理相似, 射关系被记录在映射相表中,cache的每一块都拥有一个表项 的每一块都拥有一个表项。 射关系被记录在映射相表中,cache的每一块都拥有一个表项。

中国科学院上海微系统与信息技术研究所

Shanghai Institute of Microsystem and Information Technology, Chinese Academy of Sciences, China

全相联映射地址转换

当一块主存调入cache中时,同时在一个存储主块号和cache块号映射表的相联存 当一块主存调入cache中时,同时在一个存储主块号和cache块号映射表的相联存 cache中时 cache 储器中进行登记。 储器中进行登记。 送来一个访存地址时, 当cpu送来一个访存地址时,首先根据主存地址中的主存块号M在像关存储器中查 送来一个访存地址时 首先根据主存地址中的主存块号M cache块号 若找到,直接将对于的cache块号取出,并送访cache 块号, cache块号取出 cache地址的块内字 找cache块号,若找到,直接将对于的cache块号取出,并送访cache地址的块内字 字段,从而形成一个访问cache的地址,完成对cache单元的访问。 cache的地址 cache单元的访问 号W字段,从而形成一个访问cache的地址,完成对cache单元的访问。 特点:cache空间利用率高 但相联存储器庞大,电路复杂,适用于小容量cache 空间利用率高, 特点:cache空间利用率高,但相联存储器庞大,电路复杂,适用于小容量cache

中国科学院上海微系统与信息技术研究所

Shanghai Institute of Microsystem and Information Technology, Chinese Academy of Sciences, China

Cache工作原理 工作原理

利用程序的时间局部性和空间局部性特征来优化系统性能, 时间局部性和空间局部性特征来优化系统性能 (1)利用程序的时间局部性和空间局部性特征来优化系统性能,平衡处理器与存储器 之间的数据存取差距,cache的访存速度接近cpu而容量接近主存 的访存速度接近cpu而容量接近主存。 之间的数据存取差距,cache的访存速度接近cpu而容量接近主存。

中国科学院上海微系统与信息技术研究所

Shanghai Institute of Microsystem and Information Technology, Chinese Academy of Sciences, China

Cache替换策略及一致性问题 替换策略及一致性问题

Cache和存储器一样具有两种基本操作 即读操作和写操作。 和存储器一样具有两种基本操作,即读操作和写操作 和存储器一样具有两种基本操作 即读操作应单元中读取信息到数据总线; (1)Cache命中:直接访问 ) 中 直接访问Cache,从对应单元中读取信息到数据总线 从对应单元中读取信息到数据总线 (2)Cache未命中:数据尚未装入Cache,CPU需从主存中读取信息,同时Cache替 ) 中 数据尚未装入 需从主存中读取信息,同时 替 需从主存中读取信息 换部件把该地址所在的那块存储内容从主存拷贝到Cache中;若Cache中相应位置已被字 换部件把该地址所在的那块存储内容从主存拷贝到 中若 中相应位置已被字 块占满,就必须去掉旧的字块 常见的替换策略有两种: 就必须去掉旧的字块。 块占满 就必须去掉旧的字块。常见的替换策略有两种 1、先进先出策略 、先进先出策略(FIFO) :替换最先调入的 替换最先调入的Cache字块 不需要随时记录各个字块的使用 字块,不需要随时记录各个字块的使用 字块 情况,较容易实现 较容易实现。 情况 较容易实现。 2、最近最少使用策略 中使用次数最少的字块,需要随时 、最近最少使用策略(LRU)是:替换当前近期 是 替换当前近期Cache中使用次数最少的字块 需要随时 中使用次数最少的字块 记录Cache中字块的使用情况。LRU的平均命中率比 中字块的使用情况。 的平均命中率比FIFO高,在组相联映像方式中 当分 在组相联映像方式中,当分 记录 中字块的使用情况 的平均命中率比 高 在组相联映像方式中 组容量加大时,LRU的命中率也会提高。 的命中率也会提高。 组容量加大时 的命中率也会提高

中国科学院上海微系统与信息技术研究所

Shanghai Institute of Microsystem and Information Technology, Chinese Academy of Sciences, China