基于锁相环的频率合成器解读

高频电子线路(第五版)课件:锁相技术及频率合成

锁相技术及频率合成

图8.3 常用正弦鉴相器模型

锁相技术及频率合成

锁相技术及频率合成 在同频率上对两个信号的相位进行比较,可得输入信号

ui(t)的总相

式中,φi(t)是以ωrt 为参考的输入信号瞬时相位;Δωi 称为环路 的固有频差,又称起始 频差。

锁相技术及频率合成

锁相技术及频率合成

图8.4 正弦鉴相器的鉴相特性及其电路模型

锁相技术及频率合成

图8.13 一阶锁相环路的相图

锁相技术及频率合成

由图8.13可以看出,环路并不是对任意大小的固有频差 Δωi 都能进行捕捉锁定的。当 Δωi >A= AdA0 时,相轨迹与横 轴没有交点,即没有平衡点,环路失锁,如图8.13(b)所 示,这时 相点总是向右移动(若 Δωi <-A=- AdA0,则相点总是向左移动)。 当| Δωi |≤ AdA0时,相轨迹与横轴有交点,环路可以进入锁定状 态。由图8.13(a)可以看出,当| Δωi |≤ AdA0 时,相轨迹与横轴有 两个交点,环路可以进行捕捉锁定。

锁相技术及频率合成

当环路未加输入信号ui(t)时,VCO 上没有控制电压,它的 振荡频率为ωr。若将频率 ωi 恒定的输入信号加到环路上去, 固有频差(起始频差)Δ ωi = ωi - ωr,因而在接入ui(t)的 瞬间,加 到鉴相器的两个信号的瞬时相位差

锁相技术及频率合成

下面分三种情况进行讨论: (1)Δωi(t)较小,即 VCO 的固有振荡频率ωr 与输入信号频 率ωi 相差较小。 (2)Δωi较大,即ωr与ωi相差较大,使 Δωi超出环路滤波器 的通频带,但仍小于捕捉 带 Δωp。

锁相技术及频率合成 压控振荡器的输出反馈到鉴相器上,对鉴相器输出误差

基于MC145151-2PPL频率合成器的设计

一

频 率 合 成 器 的 频 率分 辨 率 。 改 变 R数值 的 大 小 ,

准 频率源相组合 ,就能产生与标准信号源有相 同的频率稳定度、准确度的众多频率点。

可改变频率合成器的分辨率。由以上可以看 出 当环路锁定后,压控振荡器的输出频率严格 与 输入 频率 行相等 。同时在 一定 范围 内跟踪 输 入信号频率变化 ,具有 良好 的跟踪特性 。只要 L P F通频带设计合理,整个环路就具有 良好的

窄带滤波特性。

1 M C 1 4 5 1 5 1 - 2 锁相环 简介

MC1 4 5 1 5 1 - 2是 一 块 双 列 直 插 式 C M OS大 规 模 集 成 电路 , 由 4位 总 线 输 入 、 锁 存 器 选 通

个 高 稳 定度 的 标 准 频 率 f s , 经 参 考 分 频 器 进

:

R A 2 R A 1 R A o M c 1 4 5 1 5 1 — 2

: : M A X 3 0 8

;

随 着 移 动 通 信 、雷 达 技 术 以及 遥 测 、 遥

感测控技术不断发展 ,各种 系统对频 率源 的要 求越来越高 , 不但 要求频率稳定度和准确度高, 而且还要求能方便 的改变 收发频率。特别是无

图一 1 基 本锁相 环 频率合 成 器组 成框 图

【 关键词 】频率合成 V C O 锁相环 频率 源 分

频 器

广 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 1 广 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 1

锁相环频率合成器的设计

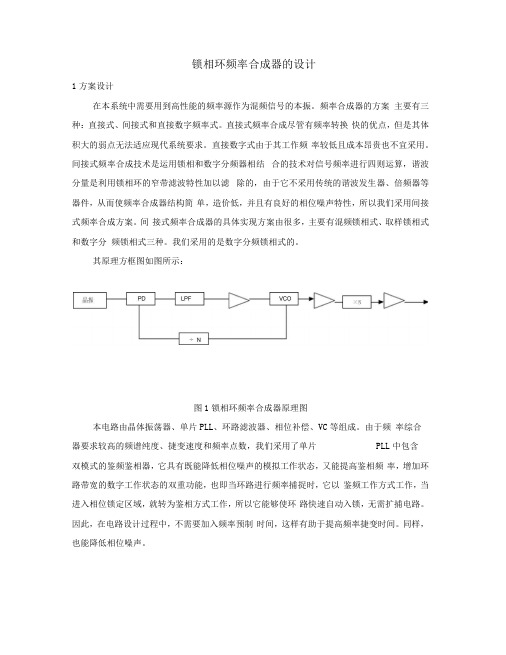

锁相环频率合成器的设计1方案设计在本系统中需要用到高性能的频率源作为混频信号的本振。

频率合成器的方案主要有三种:直接式、间接式和直接数字频率式。

直接式频率合成尽管有频率转换快的优点,但是其体积大的弱点无法适应现代系统要求。

直接数字式由于其工作频率较低且成本昂贵也不宜采用。

间接式频率合成技术是运用锁相和数字分频器相结合的技术对信号频率进行四则运算,谐波分量是利用锁相环的窄带滤波特性加以滤除的,由于它不采用传统的谐波发生器、倍频器等器件,从而使频率合成器结构简单,造价低,并且有良好的相位噪声特性,所以我们采用间接式频率合成方案。

间接式频率合成器的具体实现方案由很多,主要有混频锁相式、取样锁相式和数字分频锁相式三种。

我们采用的是数字分频锁相式的。

其原理方框图如图所示:图1锁相环频率合成器原理图本电路由晶体振荡器、单片PLL、环路滤波器、相位补偿、VC等组成。

由于频率综合器要求较高的频谱纯度、捷变速度和频率点数,我们采用了单片PLL中包含双模式的鉴频鉴相器,它具有既能降低相位噪声的模拟工作状态,又能提高鉴相频率,增加环路带宽的数字工作状态的双重功能,也即当环路进行频率捕捉时,它以鉴频工作方式工作,当进入相位锁定区域,就转为鉴相方式工作,所以它能够使环路快速自动入锁,无需扩捕电路。

因此,在电路设计过程中,不需要加入频率预制时间,这样有助于提高频率捷变时间。

同样,也能降低相位噪声。

另外,对于输出频率大于2GHZ勺本振源,我们采用倍频法来得到微波毫米波段的输出信号。

需要在锁相环的输出后附加微波毫米波倍频组件,以得到更高的频率。

2 各电路部件勺实现2.1单片PLL为了满足小体积的要求,我们采用单片PLL频率合成技术,单片PLL频率合成技术是现代频率合成技术的一大革命,它使得P、L、S波段实现小型化、低相位噪声频率合成器成为可能。

在本方案中,我们采用Q323睐实现。

美国QUALCO公司推出的Q3236单片PLL 芯片,其性能优良,工作频率在0〜2GHz除此之外,Q3236还具有以下特性:1)内设前置十10/11分频器2)输入灵敏度范围-10dBm〜+10dBm3)鉴相器增益高达302mv4)输入驻波比小于2:15)程序控制端口TTL/CMO兼容,8bit串行的或并行的数据线6)锁定指示7)参考分明比在1 〜16之间8)2〜128分频器的工作频率可达300MHz,90〜1295分频比的工作频率可达2GHzQ3236还包括以下几个功能部件:1)高速参考信号线性接收管和高速VCO的输出信号的线性接收器2)可以高频工作的十10/11双模前置分频器3)由M和A计数器组成的吞脉冲计数分频器4)可编程的参考分频器5)数字鉴频/鉴相器6)锁定/失锁检测电路7)TTL/CMO兼容的并行接口和8位数据总线接口使用Q323睐实现锁相环路,只需外加一阶环路滤波器和VCO参考分频比和分频比均采用外部控制模式。

基于ADF4157的Σ-△小数分频锁相环频率合成器设计

图 3 示 为 芯 片原 理 框 图 ,L D T 、E为 串行 输 入 时 所 C K、 A E L

相对较差 , 成度低 , 集 越来 越不能满足现代低成本 、 高一致性 、

钟数据和使能控制 ; X U MU O T为输 出信号锁定检测脚 ; P为电 C 荷泵输出。 中, S 其 C R为快锁功能控制 , 它可 以在小频率范围内 信号变换时 陕速锁定 ,它的原理是通过控制 C P输出电流来降

为 (R C2% v。 F A /2XFm

∞ m RⅡ s

式 ( 中第 一 项 为 所需 频 率 , 二 项 为 由小数 分频 形 成 的 1 ) 第

阶调 制 的量 化误 差 。

它将 前 一 级 的 量 化误 差作 为下 一 级 调制 器 的输 入 , 而把 从

噪声推 向远端 , 噪声在信号近端受到很大抑制 , 以被环路 使 可 滤波器滤除 , 从而达到更好的噪声整形效果 。因此 , 采用多阶调

快 速 发 展 , 高 频 率 、 定 度 的要 求 就 越 高 。 对 高稳

荡器输 出信号相位 , 出 两个信号相 位差成正 比的电压作为 取

误 差 电压 来 控 制 V O输 出频 率 , C 实现 稳 定 信 号 输 出 。

整数 分频锁相环频率 合成器存在 高分 辨率 低 噪声 之间

锁 相 式 、 锁 相 式 和 数字 分频 锁 相 式 三 种 。数 字 分 频 锁 相 环 取样

∑一 △小数分频锁相环频率合成器具有很高 的开关速度以 及通过 F G P A控制可以迅速 变频 ,有效地 抑制 了输 出杂散 , 有 效地解决了高鉴相频率和高分辨率的矛盾 , 降低 了输出信号的 相位噪声。 三阶 ∑一 b Al 数分频锁相环的结构 如图 l 所示 。

基本锁相环与锁相式数字频率合成器

基本锁相环与锁相式数字频率合成器一、实验目的1、掌握VCO压控振荡器的基本工作原理。

2、加深对基本锁相环工作原理的理解。

3、熟悉锁相式数字频率合成器的电路组成与工作原理。

二、实验内容1、观察锁相环的同步态。

2、在程序分频器的分频比N=1、10、99情况下:①测量输入参考信号的波形。

②测量频率合成器输出信号的波形。

③检查并观察输出频率(或分频比)的置换功能。

④测量并观察最小分频比与最大分频比。

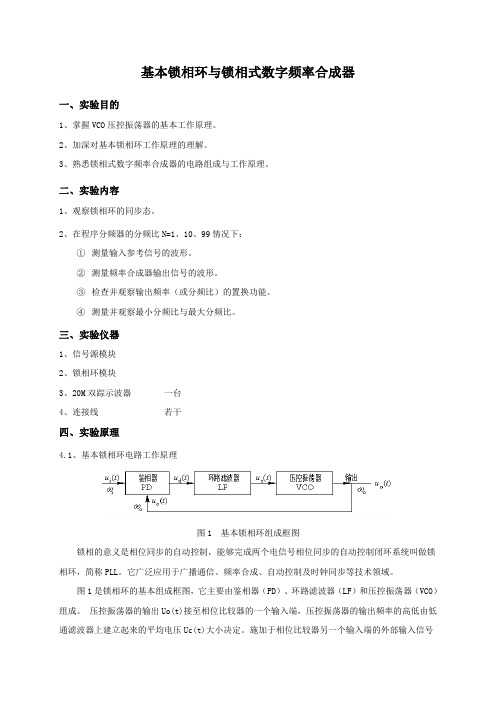

三、实验仪器1、信号源模块2、锁相环模块3、20M双踪示波器一台4、连接线若干四、实验原理4.1、基本锁相环电路工作原理图1 基本锁相环组成框图锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。

它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。

图1是锁相环的基本组成框图,它主要由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)组成。

压控振荡器的输出Uo(t)接至相位比较器的一个输入端,压控振荡器的输出频率的高低由低通滤波器上建立起来的平均电压Uc(t)大小决定。

施加于相位比较器另一个输入端的外部输入信号Ui(t)与来自压控振荡器的输出信号Uo(t)相比较,比较结果产生的误差输出电压Ud(t)正比于Ui(t)和Uo(t)两个信号的相位差,经过低通滤波器滤除高频分量后,得到一个平均值电压Uc(t)。

这个平均值电压Uc(t)朝着减小VCO输出频率和输入频率之差的方向变化,直至VCO输出频率和输入信号频率获得一致。

这时两个信号的频率相同,两相位差保持恒定(即同步),称作相位锁定。

当环路锁定后,如果输入信号频率ωi或VCO振荡频率ωo发生变化,则VCO振荡频率ωo跟踪ωi而变化,维持ωo=ωi的锁定状态,这个过程称为跟踪过程或同步过程。

相应地,能够维持环路锁定所允许的最大固有频差|Δωi|,称为锁相环路的同步带或跟踪带,用ΔωH表示。

超出此范围,环路则失锁。

基于DDS的锁相频率合成器设计

基于DDS的锁相频率合成器设计李俊;施颂生【摘要】提出一种基于直接频率合成技术(DDS)的锁相环(PLL)频率合成器,该合成器利用DDS输出与PLL反馈回路中的压控振荡器(VCO)输出混频,替代多环锁相频率合成器中的低频率子环,使合成器输出频率在89.6~110.4 MHz之间分辨率达1 Hz,并保持DDS相噪、杂散水平不变.结合DDS的快速频率切换和PLL环路跟踪能力,实现信号的快速跳频.本文给出了技术方案,讨论部分电路设计,并对主要技术指标进行理论分析,最后给出了实验结果.【期刊名称】《现代电子技术》【年(卷),期】2007(030)023【总页数】3页(P74-76)【关键词】直接数字式频率合成;锁相环;混频;带通滤波器【作者】李俊;施颂生【作者单位】湘潭大学,信息工程学院,湖南,湘潭,411105;湘潭大学,信息工程学院,湖南,湘潭,411105【正文语种】中文【中图分类】TN741 引言现代频率合成源对频率精度、分辨率、转换时间和频谱纯度等指标提出了越来越高的要求。

甚高频(VHF)频率合成器通常采用多锁相环路(PLL)结构,多环合成器将单环中的巨大分频比用多个环路来负担,同时各环,尤其是主环的鉴相频率大幅度提高,从而满足了鉴相频率高、分频比小和分辨率高等要求。

但是由于多环组合的固有特性,尤其是分辨率每提高1个数量级,就要增加一级子环路,使得其频率转换速度低、线路复杂、可靠性差。

直接数字式频率合成技术(DDS)的频率分辨率高、频率转换速度快。

DDS/PLL混合频率合成是一项新兴技术。

DDS激励PLL倍频的方式能发挥DDS高分辨率的特点,但DDS信号中的相噪与杂散一旦落入环路内将会恶化lg N。

采用DDS内插PLL混频,即DDS输出与PLL反馈回路中的压控振荡器(VCO)输出混频,相当于用DDS取代多环频率合成器中的低(细)频率子环,电路结构简单,在频率转换速度、分辨率等方面性能优良,并且不存在DDS相噪与杂散恶化的问题。

CPT铷原子钟锁相环频率合成器设计和分析

第43卷第1期2020年2月电子器件ChineseJournalofElectronDevicesVol 43㊀No 1Feb.2020项目来源:科技部国家重点研发计划项目(2017YFB0503200)ꎻ山西省自然基金项目(201701D121065)ꎻ国家高分辨率对地观测系统重大专项项目(67-Y20A07-9002-16/17)ꎻ山西省 1311工程 重点学科建设计划项目ꎻ山西省高等学校131领军人才项目ꎻ山西省高等学校中青年拔尖创新人才项目ꎻ山西省留学回国人员科技活动择优项目收稿日期:2019-03-11㊀㊀修改日期:2019-04-28DesignandAnalysisofPLLFrequencySynthesizerforRbAtomicClock∗MOUShihaoꎬZHANGKaifangꎬSUHaoꎬZHANGLuꎬLIUZhaojunꎬZHANGYanjunꎬYANShubin∗(NorthuniversityofChinaꎬKeyLaboratoryofInstrumentationScienceandDynamicMeasurementꎬTaiyuan030051ꎬChina)Abstract:Aphaselockedloopfrequencysynthesizerwithanoutputfrequencyof3417MHzisdesignedbasedonCPT(CoherentPopulationTrapping)87RbatomicclockꎬADIsimPLLisusedtosimulatetheoptimalloopbandwidthꎬloopfilterparametersandphasenoiseꎬSTM32isusedtocontrolthePLLchip.Thefrequencysynthesizeristestedꎬthecircuitsizeis40mmˑ40mmꎬtheoutputsignalpowerrangeisadjustable(-4dBm~+5dBm)ꎬtheoutputsignalnoisemeetstherequirements-88.65dBc/Hz@1kHzꎬ-92.31dBc/Hz@10kHzꎬ-104.63dBc/Hz@100kHzꎬthespurioussignalsandharmonicaresuppressed.ThedesignedfrequencysynthesizercanbewellappliedtotheRFsignalsourceofatomicclock.Keywords:frequencysynthesizerꎻatomicclockꎻPLLꎻADIsimPLLꎻphasenoiseEEACC:1230Bꎻ1250㊀㊀㊀㊀doi:10.3969/j.issn.1005-9490.2020.01.006CPT铷原子钟锁相环频率合成器设计和分析∗牟仕浩ꎬ张开放ꎬ苏㊀浩ꎬ张㊀璐ꎬ刘召军ꎬ张彦军ꎬ闫树斌∗(中北大学仪器科学与动态测试教育部重点实验室ꎬ太原030051)摘㊀要:基于CPT(相干布局囚禁)87铷原子钟设计出输出频率为3417MHz的锁相环频率合成器ꎬ通过ADIsimPLL仿真出最佳环路带宽ꎬ环路滤波器参数以及相位噪声等ꎬ并通过STM32对锁相环芯片进行控制ꎮ对频率合成器进行了测试ꎬ电路尺寸为40mmˑ40mmꎬ输出信号功率范围为-4dBm~+5dBm可调ꎬ输出信号噪声满足要求-88.65dBc/Hz@1kHzꎬ-92.31dBc/Hz@10kHzꎬ-104.63dBc/Hz@100kHzꎬ杂散和谐波得到抑制ꎬ设计的频率合成器能很好的应用于原子钟的射频信号源ꎮ关键词:频率合成器ꎻ原子钟ꎻ锁相环ꎻADIsimPLLꎻ相位噪声中图分类号:TN742㊀㊀㊀㊀文献标识码:A㊀㊀㊀㊀文章编号:1005-9490(2020)01-0025-05㊀㊀被动型相干布局囚禁(CPT)原子钟因为不存在微波谐振腔ꎬ因此体积和功耗大幅度降低ꎬ为原子钟实现微型化创造了条件[1]ꎬCPT原子钟于是变得非常有吸引力ꎮCPT原子钟主要包括射频信号源㊁物理系统和外围控制电路ꎬ特别是射频信号源ꎬ决定了输出频率的短期稳定性和精度[2]ꎮ而CPT现象是通过在外部磁场作用下ꎬ87Rb原子能级分裂成超精细能级ꎬ能级差为精准的6.835GHzꎬ采用半宽调制ꎬ即利用能级差的一半3.417GHz来对VCSEL激光器驱动电流进行幅度调制ꎬ产生频率为3.417GHz的调频光场ꎬ该光场的ʃ1级边带频率差就刚好等于原子超精细能级差ꎬ由此来制备CPT态[3]ꎬ本文利用的是锁相环(PLL)频率合成器来实现射频信号源输出3.417GHz的频率ꎬ锁相环在相位噪声和杂散抑制方面都可以满足原子钟的需求ꎬ并且锁相环也是许多仪器设备中的核心部件[4]ꎮ1㊀基本原理锁相环是由温度补偿晶体振荡器㊁鉴相器㊁环路滤波器㊁压控振荡器组成一个闭环反馈系统[5]ꎬ其电㊀子㊀器㊀件第43卷中鉴相器包括相位比较器㊁电荷泵㊁R分频器和N分频器四部分ꎬ晶体振荡器采用的是10MHz温度补偿晶振ꎬ因为鉴相器PD的输出不仅包含直流控制信号ꎬ还有一些高频谐波成分ꎬ这些高频谐波成分会影响VCO电路的工作ꎬ因此环路滤波器采用的是一个三阶环路低通滤波器ꎬ采用低通滤波器能够滤除这些高频成分ꎬ以防止对VCO造成干扰ꎮ如图1所示锁相环的工作原理图:fo是输出频率ꎬfr是输入参考信号的频率ꎬ输入参考频率通过鉴相器后产生一个直流信号ꎬ直流信号通过三阶低通滤波器产生一个误差控制电压来控制压控振荡器的输出频率ꎬ其中输出的一部分经由N分频器后返回到鉴相器与输入参考信号进行鉴相[6]ꎬ由此形成一个负反馈ꎬ通过输入参考信号fr和输出频率fo经过N分频后的信号一直不断的比较ꎬ使得二者保持一致ꎬ并且使相位差保持在固定的范围内ꎮ图1㊀锁相环频率合成器原理图2㊀方案设计基于数字锁相环小数分频频率合成原理设计了CPT原子钟微波信号源倍频方案ꎬ选用的锁相环芯片ADF4351集成了R分频器㊁鉴相器㊁N分频器㊁电荷泵以及压控振荡器ꎬ具有占用电路体积小的优势ꎬ并且锁相环路好的噪声指标是建立在优良的噪声基底的基础上的ꎬADF4351具有良好的相位噪声基底ꎮ整个系统方案核心为锁相环芯片以及STM32单片机ꎬADF4351通过外接10MHz参考晶振和环路滤波器ꎬ压控振荡器是内置于锁相环芯片的ꎬSTM32-LQFP48主控芯片通过SPI协议控制ADF4351ꎬ配置锁相环芯片寄存器ꎬ输出指定频率的信号ꎬ并且可以通过程序来改变输出信号的频率以及幅度ꎮ如图2所示ꎬ晶振的主要技术指标:晶振型号是CFPT-9003ꎬ体积为7.0mmˑ5.0mmˑ2.0mmꎬ频率稳定度为@25ħɤʃ0.5ˑ10-6ꎮ滤波器是三阶无源环路滤波器ꎬ具有体积小ꎬ电路简单的优势ꎬ相比有源环路滤波器ꎬ有源环路滤波器会引入额外的噪声ꎮ系统控制是通过stm32芯片配置锁相环芯片ADF4351的寄存器来改变锁相环参数ꎬADF4351是ADI公司的具有小数N分频和整数N分频的频率合成器ꎬ具有低相位噪声的VCOꎬVCO灵敏度为40MHz/Vꎬ输出频率范围为2200MHz~4400MHzꎬ归一化的相位噪底为-220dBc/Hzꎬ带内相位噪声在偏移3kHz处载波为2111.28MHz-图2㊀系统方案从图3可以很直观的看到锁相环芯片的外部硬件电路ꎬ包括环路滤波器㊁外部参考频率REFin的输入和电源去耦电路ꎬ数据传输接口连接到STM32芯片ꎮ锁相环芯片寄存器接口CLK㊁DATA㊁LEꎬLE是通过控制SPI协议的通断来控制数据传输ꎬCLK接口接收的是来自外部提供的时钟信号ꎬDATA接口是待写入数据ꎮDATA中的待写入数据在时钟上升沿到来时ꎬ传输至移位寄存器ꎬ并按照最高有效位优先的方式ꎬ最后三位是地址位ꎬ不同地址位的数据分别进入不同的锁存器ꎬ到LE上升沿到来时ꎬ移位寄存器中的数据将分别传输至锁存器中[7]ꎬ完成对芯片寄存器的配置ꎮ式(1)是输出频率的关系式:RFout=[INT+(FRAC/MOD)]ˑ(fPFD/RFdivider)(1)式中:RFOUT是锁相环电路的输出频率ꎬINT是整数分频系数ꎬFRAC是小数分频系数ꎬMOD是小数模数(2~4095)ꎬ模数设置的越大分辨率就越高ꎬfPFD是鉴相频率ꎬRFdivider细分VCO的输出分频器ꎮfPFD=REFINˑ[(1+D)/(Rˑ(1+T))](2)式中:REFIN是参考输入频率ꎬD是参考输入频率的倍频器位(0或1)ꎬR是参考分频系数(1到1023)ꎬT是参考二分频位(0或1)ꎮ根据锁相环频率合成器设计要求以及ADF4351相关资料最终设定寄存器值为:寄存器5(0X00580005)ꎬ寄存器4(0X00EC803C)ꎬ寄存器3(0X000004B3)ꎬ寄存器2(0X00010E42)ꎬ寄存器1(0X00008029)ꎬ寄存器0(0X00AD8018)ꎮ时序图如图4所示ꎮ62第1期牟仕浩ꎬ张开放等:CPT铷原子钟锁相环频率合成器设计和分析㊀㊀图3㊀ADF4351电路图图4㊀时序图3㊀硬件和软件设计3.1㊀硬件电路的仿真通过利用ADI公司提供的PLL专用设计软件ADIsimPLL来辅助硬件电路的设计ꎬ通过选择芯片类型㊁参考频率㊁输出频率㊁环路滤波器的类型㊁压控振荡器来仿真锁相环得到环路滤波器的各项参数并且可以对锁相环各部分的相位噪声进行分析ꎮ选择芯片ADF4351ꎬ参考输入频率10MHzꎬ输出频率设置为3.417GHzꎬ相位裕度设为45ʎꎬ环路带宽过宽会导致相噪曲线整体很差ꎬ过窄的环路带宽又会导致相噪曲线后端有凸起ꎬ因此经过多次仿真后选择设置带宽为相位噪声表现最优的20kHz处ꎬ既保持了低杂散也使信号具有良好的相位噪声性能ꎬ仿真电路如图5所示ꎮADIsimPLL是一个综合性的锁相环频率合成器设计和仿真软件ꎬ具有极好的的仿真设计能力ꎬ基于ADI公司的锁相环芯片的设计背景ꎬ尽可能完美地利用ADISIMPLL来设计环路滤波器的相关参数以及尽可能真实地仿真电路的相位噪声ꎮ采用的滤波器是三阶无源滤波器ꎬ是只采用RC的滤波器ꎬ相对于有源环路滤波器带来噪声和零点漂移ꎬ它的成本低ꎬ噪声小ꎬ结构简单并且更加稳定ꎬ仿真出的环路滤波器的参数为C1=7.66nFꎬC2=104nFꎬR1=214Ω图5㊀仿真电路图图6是是通过ADISIMPLL仿真锁相环系统输出频率的相位噪声ꎬ可以得出在频偏100kHz处相位噪72电㊀子㊀器㊀件第43卷声为-110.143dBc/Hzꎬ这是一个理想情况下的值ꎬ实际情况下存在电磁干扰等ꎬ相位噪声会高于理论值ꎮ并且锁相环的器件中分频器㊁倍频器对信号进行分频㊁倍频操作时ꎬ相位噪声也进行了同样的变化ꎮ在实际应用中用公式来估算相位噪声的大小ꎮPNOUT=PNNORM+20lgfLO-10lgfPD(3)式中:PNOUT是锁相环输出频率的相位噪声ꎬPNNORM是锁相环的归一化带内相噪基底ꎬ主要由器件自身决定ꎬfLO是锁相环的输出频率ꎬ是一个常数ꎬfPD是锁相环鉴相频率ꎬ公式中只有这个参数可以改变ꎬ因此鉴相频率每增加10倍相位噪声的值就降低10dBꎬ因此在保证一定频率分辨率的情况下ꎬ尽量提高鉴相频率会改善相位噪声的情况ꎮ外围电路设计中10MHz晶振和环路滤波器对相位噪声的贡献可以通过选择更好的器件或者优化电路设计来降低ꎮ图6㊀频偏100kHz处相位噪声仿真结果ADF4351芯片的数字模块包括R分频器㊁N分频器㊁小数计数器和模数计数器ꎬ另外一共有6个寄存器从寄存器0到寄存器5ꎬ寄存器0控制16位整数分频值和12位小数分频值ꎬ二者与频率倍频倍数有关ꎬ寄存器1控制12位相位值和12位模数值ꎬ模数值与输出频率分辨率有关ꎬ寄存器2控制10位R计数器的值和电荷泵电流的设定等ꎬ寄存器3控制12位时钟分频器等参数ꎬ寄存器4控制频段选择时钟分频器和输出功率调节等参数ꎬ寄存器5是锁定检测ꎮ因为篇幅原因下面只给出程序的一部分ꎬ以下是数据传输程序:voidWriteToADF4351(u8countꎬu8∗buf){㊀u8ValueW=0ꎻ㊀u8m=0ꎻ㊀u8n=0ꎻ㊀ADF_Output_GPIOInit()ꎻ㊀ADF4351_CE=1ꎻ㊀delay_us(1)ꎻ㊀ADF4351_CLK=0ꎻ㊀ADF4351_LE=0ꎻ㊀delay_us(1)ꎻ㊀for(m=countꎻm>0ꎻm--)㊀{㊀㊀ValueW=∗(buf+m-1)ꎻ㊀㊀for(n=0ꎻn<8ꎻn++)㊀㊀{㊀㊀㊀if(0x80==(ValueW&0x80))㊀㊀㊀{㊀㊀㊀㊀ADF4351_OUTPUT_DATA=1ꎻ㊀㊀㊀}㊀㊀㊀else㊀㊀㊀{㊀㊀㊀㊀ADF4351_OUTPUT_DATA=0ꎻ㊀㊀㊀}㊀㊀㊀delay_us(1)ꎻ㊀㊀㊀ADF4351_CLK=1ꎻ㊀㊀㊀delay_us(1)ꎻ㊀㊀㊀ValueW<<=1ꎻ㊀㊀㊀ADF4351_CLK=0ꎻ㊀㊀}㊀}㊀ADF4351_OUTPUT_DATA=0ꎻ㊀delay_us(1)ꎻ㊀ADF4351_LE=1ꎻ㊀delay_us(1)ꎻ㊀ADF4351_LE=0ꎻ}4㊀性能测试及分析经测试信号源尺寸为40mmˑ40mmꎬ输出功率范围为-4dBm~+5dBmꎬ输出频率达到3.417GHz准确度较高ꎬ在3.417GHz频偏1kHz处测得相位噪声为-88.65dBc/Hz@1kHzꎬ10kHz处为-92.31dBc/Hz@10kHzꎬ100kHz处为-104.63dBc/Hz@100kHzꎬ相位噪声表现良好ꎬ杂散抑制达到60dB以上ꎬ图7为输出信号频谱图ꎬ图8为相噪测试图ꎬ利用的是频谱仪PXASignalAnalyzerN9030A进行的测试ꎮ图7㊀信号频谱图参考频率㊁分频器㊁鉴相器的噪声在低频段ꎬ高频段的噪声主要来源于压控振荡器ꎮ因为频率是从晶振82第1期牟仕浩ꎬ张开放等:CPT铷原子钟锁相环频率合成器设计和分析㊀㊀图8㊀频偏100kHz处相位噪声测试图输入的10MHz的频率倍频到3417MHzꎬ倍频了3417/10=341.7倍ꎬ相位噪声恶化20lgN(N为频率倍频的倍数)即恶化20lg341.7=50.67dBꎬ杂散和相位噪声有相似的传输特性ꎬ在任何一个环节都有可能引入杂散ꎬ在锁相环电路设计中ꎬ通过设计合理的电源电压去耦㊁合理的PCB布局布线㊁合理的环路滤波器阶数以及利用更窄的带宽来很好地抑制杂散ꎬ但是带宽太低会造成频率锁定时间过长㊁甚至无法锁定ꎬ太高又会带来杂散ꎮ因此ꎬ需要平衡这二者选取一个折中的值ꎮ仿真出的环路滤波器的参数在实际调试过程中会发生变化ꎬ这取决于实际电路本身ꎬ因为实际电路中存在外界环境的干扰ꎬ元件的误差等ꎬ环路滤波器的电阻值和电容值要按调试中的表现来定ꎮ从图8中可以看到分辨率带宽为2.0kHzꎬ根据对相位噪声的分析ꎬ可以利用公式计算出频谱图中相位噪声的大小:L(fm)=(PSSB-Po)-10lgB+2.5(dBc/Hz)B=1.2B3dB(4)式中:PSSB代表偏移载波fm处的测量边带功率ꎬPo表示载波功率ꎬB3dB表示分辨率带宽ꎬ单位Hzꎬ在偏移载波100kHz处的相位噪声为:L(fm)=-72-10lg2400+25=-103.30dBc/Hz@100kHz通过理论验证后的结果与实际仪器测出的相位噪声相比相差不大ꎮ5㊀结束语利用锁相环小数分频技术设计的射频信号源ꎬ基于STM32进行控制ꎬ运用高集成度的锁相环芯片ADF4351外加三阶无源环路滤波器ꎬ尺寸小ꎬ易调试ꎬ便于批量化生产ꎬ为之后实现2FSK调制以及频率伺服环路打下基础ꎮ通过测试分析ꎬ电路的各项相关技术指标满足CPT铷原子钟信号源的要求ꎮ参考文献:[1]㊀杨坦ꎬ廉吉庆ꎬ王剑祥ꎬ等.CPT铷原子钟微波信号源设计[J].电子器件ꎬ2018ꎬ41(2):421-424.[2]石红.芯片级原子钟激光调制及CPT信号解调研究[D].苏州:苏州大学ꎬ2014.[3]赵劼成.相干布居数囚禁原子钟性能研究[D].武汉:中国科学院研究生院(武汉物理与数学研究所)ꎬ2013.[4]周阳ꎬ王春晖ꎬ金小军ꎬ等.新型皮卫星星载接收机设计[J].传感技术学报ꎬ2011ꎬ24(5):694-699.[5]赵亚妮.低相噪低杂散650MHz点频源的设计[J].电子元件与材料ꎬ2016ꎬ35(7):77-79.[6]张刚.CMOS集成锁相环电路设计[M].北京:清华大学出版社ꎬ2013:1-10.[7]林辉.低杂散㊁低噪声锁相倍频信号源设计[D].成都:电子科技大学ꎬ2018.[8]远坂俊昭.锁相环(PLL)电路设计与应用[M].何希才ꎬ译.北京:科学出版社ꎬ2006:229-270.[9]任小红ꎬ闫树斌ꎬ刘俊ꎬ等.Rb87微型CPT原子钟信号源的设计[J].通信技术ꎬ2010ꎬ43(11):167-168.[10]CaoHuiꎬQuYu.AMiniaturizedFrequencySynthesizersystemDesignBasedonADF4350[C]//IEEEInternationalConferenceonSignalProcessing.HongKongꎬChina.IEEEꎬ2016:1-4. [11]廉吉庆ꎬ陈大勇ꎬ翟浩.CPT铯原子钟微波信号源设计与分析[J].宇航计测技术ꎬ2014(1):25-28.[12]刘类骥ꎬ赵海清ꎬ曹远洪.一种芯片原子钟专用锁相倍频器研究与设计实现[J].宇航计测技术ꎬ2014(1):37-41.[13]韩文革.基于三阶锁相环频率合成技术的时钟源设计[D].太原:中北大学ꎬ2018.[14]JiLeiꎬTangLiangꎬZhangZhongshan.Developmentof4.596GHzRFSourceforChip ̄ScaleAtomicClock[J].HighPowerLaser&ParticleBeamsꎬ2015ꎬ27(2):27024130.[15]李海华.小步进㊁低相噪频率合成器的设计与实现[D].武汉:华中科技大学ꎬ2016.[16]徐建.被动型相干布居数囚禁原子钟系统关键技术研究[D].武汉:华中科技大学ꎬ2011.[17]夏江林ꎬ邹传云.基于ADF4350的锁相环频率合成器设计与实现[J].通信技术ꎬ2018ꎬ51(3):734-740.牟仕浩(1995-)ꎬ男ꎬ汉ꎬ四川雅安人ꎬ中北大学在读硕士生ꎬ主要从事原子钟射频信号源的研究ꎬ251037712@qq.comꎻ闫树斌(1975-)ꎬ男ꎬ汉ꎬ山西交城人ꎬ中北大学教授ꎬ博士生导师ꎬ主要从事微纳光学器件㊁微机电系统方面研究ꎬshubin_yan@nuc.edu.cnꎮ92。

锁相技术及频率合成

第7章 锁相技术及频率合成

第7章

反馈控制电路

(锁相环路与频率合成技术)

7.1 自动增益控制电路 7.2 自动频率控制电路 7.3 锁相环路(PLL)

第7章 锁相环路与频率合成技术

7.2 自动频率控制电路

7.2.1 工作原理

图7.2.1 AFC电路原理框图

第7章 锁相环路与频率合成技术

7.2.2 应用举例

锁相环路基本组成框图如图所示。锁相环路是由鉴 相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三 个基本部件构成的闭合环路。

参考晶体 振荡器

u i(t) ωi

鉴相器 PD

u d(t)

环路滤波器 LF

u c(t)

压控振荡器 VCO

输出 u o(t) ωo

ωo

u o(t)

压控振荡器的控制特性

第7章 锁相环路与频率合成技术

7.3.5

锁相环路的应用

一、锁相鉴频电路

ωi

输入调 频信号

鉴相器

环路 滤波器

uc 解调 输出

ωo

压控 振荡器

图7.3.13 调频波锁相解调电路组成

第7章 锁相环路与频率合成技术

鉴相器

u i(t) 输入电压

环路 滤波器

压控 振荡器

π/ 2 移相器

同步 检波器

输出电压

图7.3.15 采用锁相环路的同步检波电路框图

图7.2.2 调幅接收机中的AFC系统

图7.2.3

具有AFC电路的调频发射机框图

第7章 锁相环路与频率合成技术

7.3 锁相环路(PLL)

( Phase-Locked Loop)

7.3.1 锁相环路的基本工作原理

两个信号的频率和相位之间的关系

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

综合课程设计频率合成器的设计与仿真前言现代通信系统中,为确保通信的稳定与可靠,对通信设备的频率准确率和稳定度提出了极高的要求. 随着电子技术的发展,要求信号的频率越来越准确和越来越稳定,一般的振荡器已不能满足系统设计的要求。

晶体振荡器的高准确度和高稳定度早已被人们认识,成为各种电子系统的必选部件。

但是晶体振荡器的频率变化范围很小,其频率值不高,很难满足通信、雷达、测控、仪器仪表等电子系统的需求,在这些应用领域,往往需要在一个频率范围内提供一系列高准确度和高稳定度的频率源,这就需要应用频率合成技术来满足这一需求。

本次实验利用SystemView实现通信系统中锁相频率合成器的仿真,并对结果进行了分析。

一、频率合成器简介频率合成是指以一个或少量的高准确度和高稳定度的标准频率作为参考频率,由此导出多个或大量的输出频率,这些输出频率的准确度与稳定度与参考频率是一致的。

用来产生这些频率的部件就成为频率合成器或频率综合器。

频率合成器通过一个或多个标准频率产生大量的输出频率,它是通过对标准频率在频域进行加、减、乘、除来实现的,可以用混频、倍频和分频等电路来实现。

其主要技术指标包括频率范围、频率间隔、准确度、频率稳定度、频率纯度以及体积、重量、功能和成本。

频率合成器的合成方法有直接模拟合成法、锁相环合成法和直接数字合成法。

直接模拟合成法利用倍频、分频、混频及滤波,从单一或几个参数频率中产生多个所需的频率。

该方法频率转换时间快(小于100ns),但是体积大、功耗大,成本高,目前已基本不被采用。

锁相频率合成器通过锁相环完成频率的加、减、乘、除运算,其结构是一种闭环系统。

其主要优势在于结构简化、便于集成,且频率纯度高,目前广泛应用于各种电子系统。

直接式频率合成器中所固有的那些缺点,在锁相频率合成器中大大减少。

本次实验设计的是锁相频率合成器。

二、锁相环频率合成器原理2.1 锁相环路设计基础这一部分首先阐明了锁相环的基本原理及构成,导出了环路的相位模型和基本方程,概述了环路的工作过程, 2.1.1锁相环基本原理锁相环(PLL )是一个相位跟踪系统。

最基本的锁相环方框图如图1所示。

它包括三个基本部件,鉴相器(PD ) 环路滤波器(LF )和压控振荡器(VCO )图1 锁相环的基本构成设参考信号()sin[()]r r r r u t U t t ωθ=+ (1)式中 Ur 为参考信号的幅度 ωr 为参考信号的载波角频率θr (t)为参考信号以其载波相位ωr t 为参考时的瞬时相位 若参考信号是未调载波时,则θr (t)= θ1=常数。

设输出信号为 0()cos[()]o o o u t U t t ωθ=+ (2) 式中 U o 为输出信号的振幅,ω0为压控振荡器的自由振荡角频率θ0 (t)为参考信号以其载波相位ω0t 为参考时的瞬时相位, 在VCO 未受控制 它是常数,受控之后他是时间函数。

则两信号之间的瞬时相位差为0000()(())(())()()e r r r r t t t t t θωθωθωωθθ=+-+=-+- (3)由频率和相位之间的关系可得两信号之间的瞬时频差为(4)鉴相器是相位比较器,它把输出信号u o (t)和参考信号u r (t)的相位进行比较,()()e r d t d t dtdtθθωω=--产生对应于两信号相位差θe (t)的误差电压u d (t)。

环路滤波器的作用是滤除误差电压u d (t)中的高频成分和噪声,以保证环路所要求的性能,提高系统的稳定性。

压控振荡器受控制电压u c (t )的控制,u c (t)使压控振荡器的频率向参考信号的频率靠近,于是两者频率之差越来越小,直至频差消除而被锁定。

因此,锁相环的工作原理可简述如下:首先,鉴相器把输出信号u o (t)和参考信号u r (t)的相位进行比较,产生一个反应两信号的相位差θe (t)大小的误差电压u d (t),u d (t)经过环路滤波器的过滤得到控制电压u c (t)。

u c (t)调整VCO 的频率向参考信号的频率靠拢,直至最后两者频率相等而相位同步实现锁定。

锁定后两信号之间的相位差表现为一固定的稳态值。

即(5)此时,输出信号的频率已偏离了原来的自由频率ω0[控制电压u c (t)=0时的频率],其偏移量由式(4)和式(5)得到为这时输出信号的工作频率已变为00()(())c c r d t dt t dt dtθωθωω+=+= (6) 由此可见,通过锁相环路的相位跟踪作用,最终可以实现输出信号与参考信号同步,两者之间不存在频差而只存在很小稳态相差。

2.1.2 基本环路方程为了建立锁相环路的数学模型,首先建立鉴相器、环路滤波器、压控振荡器的数学模型。

1. 鉴相器鉴相器(PD)又称相位比较器,它是用来比较两个输出信号之间的相位差 θe (t)。

鉴相器输出的误差信号u d (t)是相差θe (t)的函数。

鉴相器按其鉴相特性分为正弦型,三角形和锯齿波形。

作为原理分析,通常使用正弦型,较为典型的正弦鉴相器可用模拟乘法器与低通滤波器的串接构成。

其模型如图2所示:()lim 0e t d t dtθ→∞=00()r d t dtθωω=-图2 正弦鉴相器模型若以压控振荡器的载波相位ω0t 作为参考,讲输出信号u 0(t)与参考信号u r (t)变形,有:0002()cos[()]u t U t t ωθ=+01()sin[()]sin[()]r r r r r u t U t t U t t ωθωθ=+=+式中,θ2 (t)= θ0 (t),100()()()()r r r t t t t t t θωωθωθ=++=∆+将u 0(t)与u r (t)相乘,滤波2ω0分量,可得:12()sin[()()]()d d d e u t U t t U t θθθ=-=式中,U d (t)= K m U r U o /2,K m 为相乘器的相乘系数,单位为[1/V],U d 越大,在同样的θe (t)下,鉴相器的输出就越大。

因此,U d 在一定程度上反映了鉴相器的灵敏度。

θe (t)= θ1 (t)- θ2 (t)为相乘器输入电压的瞬时相位差。

下图是正弦鉴相器的数学模型和鉴相特性。

图3 正弦鉴相器的数学模型图4 正弦鉴相器的鉴相特性)2.环路滤波器环路滤波器(LF )是一个线性低通滤波器,用来滤除误差电压u d (t)中的高频分量和噪声,更重要的是它对环路参数调整起到决定性作用。

环路滤波器由线性原件电阻、电容、和运算放大器组成。

它是一个线性系统。

常用的环路滤波器有RC 积分滤波器、无源比例积分滤波器和有源积分滤波器三种。

下面以介绍有源比例积分滤波器为主。

有源比例积分滤波器有源比例积分滤波器由运算放大器组成。

当运放器开环电压增益A 为有限值时,它的传递函数为(7)式中'111222();R AR R C R C ττ=++=由图5可见,它也具有低通特性与比例作用。

相频特性也有超前校正的作用。

图5 有源比例积分滤波器及其特性3.压控振荡器压控振荡器(VCO )是一个电压-频率变换器,再换路政作为被控振荡器,它的振荡频率应随输入控制电压u c (t)的线性的变化,即(8)式中ωv (t)是VCO 的瞬时角频率,K 0是线性特性斜率,表示单位控制电压,可使VCO 角频率变化的数值。

因此又称为VCO 的控制灵敏度与增益系数,单位为[/rad s v ∙].在锁相环路中,VCO 的输出对鉴相器起作用的不是瞬时角频率,R度)0-42-9(a )度)21()1()()1c d U s s F s AU s s ττ+==-'+0()()v d c t k u t ωω=+而是瞬时相位,即12()()()c t t t θθθ=-(9)将此式与u o (t )=U o cos [ω0t +θ2(t )],比较,可以知ω0t 为参考时的输出瞬时相位为2()sin ()()dd e K t U t F p pθθ= (10) 由此可见,VCO 在锁相环中起了一次积分作用,因此也称他为环路中的固有积分环节。

上式就是压控振荡器相位控制的模型,若对上式进行拉氏变换,可得到在复频域的表示式为VCO 的传递函数为 (11)下图为VCO 的复频域的数学模型。

图6 VCO 的复频域模型2.1.3 环路相位模型和基本方程上面分别得到了鉴相器,环路滤波器和压控振荡器的模型,将三个模型连接起来,就可以得到锁相环路的模型。

如下图7所示图7 锁相环路相位模型复时域分析时可用一个传输算子F(p)来表示。

其中(p=d/dt )是微分算子。

由22()()()cddc Us k ss k U s sθθ==上图可以得出锁相环路的基本方程。

(12) (13)将(9)代入(8)得(14) 设环路输入一个频率ωr 和相位θr 均为常数的信号,即式中,ω0是控制电压u c (t)=0时VCO 的固有振荡频率,θr 是参考输入信号的相位。

令则 (15) 将式(11)代入式(10)可得固有频率输入时的环路基本方程(16) 在闭环之后的任何时刻存在着如下关系:瞬时频差=固有频差-控制频差,记为0()v ωωω∆=∆-∆,即00()()r v r v ωωωωωω-=--- 2.1.4 锁相环工作过程的定性分析式(12)是锁相环路的基本方程,求解此方程,就可以获得锁相环路的各种性能指标,如锁定、跟踪、捕获、失锁等。

但要严格的求解基本方程式往往是比较困难的。

式中已认为压控振荡器的控制为线性,但因鉴相特性的非线性,基本方程是非线性方程。

又因为压控振荡器的固有积分作用,基本方程至少是一阶非线性微分方程。

若在考虑环路滤波器的积分作用,方程可能是高阶的。

1.锁定状态当在环路作用下,调整控制频差等于固有频差时,瞬间相差θe (t)趋向于一个固定值,并一直保持下去,即满足(17)此时认为锁相环路进入锁定状态。

2.跟踪过程122()()()()sin ()()c dd e t t t Kt U t F p pθθθθθ=-=101()()sin ()()()sin ()()e d e e p t p t K U t F p p t K t F p θθθθθ=-=-00()sin[]sin[()r r r r r r ru t U t U t t ωθωωωθ=+=+-+10100()()()r rr t t p t θωωθθωωω=-+=-=∆00()sin ()()e d e p t K U t F p θωθ=∆-lim ()0e t p t θ→∞=跟踪是在锁定的前提下,输入参考频率和相位在一定的范围内,以一定的速率发生变化时,输出信号的信号与相位以同样的规律跟随变化,这一过程称为环路的跟踪过程。