锁相环电路设计

锁相环(PLL)基本原理

压控振荡器的输出信号为:

第 19 页

在一般情况下,ωi 不一定等于ωo ,所以为了便于比较两者 之间的相位差,现都以ωo t 为参考相位。这样 ui(t) 的瞬时相位 为:

it i (t ) ot i o t i (t )

ot i (t )

其中:

第六节 锁相环路的应用

一、集成锁相环芯片 二、 方波发生器 三、PLL在调制解调技术中的应用 四、PLL在空间技术上的应用 五、PLL在稳频技术中的应用 六、PLL在频率合成器中的应用

第 3 页

第一节 锁相环路(PLL)及其反馈控制电路简介

在无线电技术中,为了改善电子设备的性能,广泛采用各种 的反馈控制电路。常用的有自动相位控制(APC)电路,也称为锁 相环路(PLL-Phase Locked Loop),自动增益控(AGC)电路以 及自动频率控制(AFC)电路。

第 27 页

3.压控振荡器VOC

压控振荡器受环路滤波器输出电压uc(t) 的控制,使振荡频 率向输入信号的频率靠拢,直至两者的频率相同,使得VCO输 出信号的相位和输入信号的的相位保持某种关系,达到相位锁定 的目的。

压控振荡器: 指输出频率与输入控制电压有对应关系的振荡电路(VCO),频率是 式中C0是零反向偏压时 输入信号电压的函数的振荡器VCO,振荡器的工作状态或振荡回 变容二极管的电容量;φ 路的元件参数受输入控制电压的控制,就可构成一个压控振荡器 是变容二极管的结电压; γ 是结电容变化指数。

三、锁相环的基本原理

第 5 页

AGC电路接收方框图如图2-1所示。

图2-1 AGC电路的接收方框图

第 6 页

工作原理: 它的工作过程是输入信号 经放大、变频、再放大后,到 中频输出信号,然后把此输出电压经检波和滤波,产生控制电压 , 反馈回到中频、高频放大器,对他们的增益进行控制。所以这种增 益的自动调整主要由两步来完成:第一,产生一个随输入 信号而变 化的直流控制电压 (叫AGC电压);第二,利用AGC电压去控制某些 部件的增益, 使接收机的总增益按照一定规律而变化。

电荷泵锁相环四阶无源环路滤波器的设计

电荷泵锁相环四阶无源环路滤波器的设计1. 绪论1.1 研究背景1.2 研究目的与意义1.3 现有研究综述2. 无源环路滤波器原理2.1 电荷泵2.2 锁相环2.3 无源滤波器2.4 四阶环路滤波器3. 设计方案3.1 系统框图3.2 电路设计流程3.3 具体电路设计4. 实验验证4.1 实验设备与方法4.2 实验结果与分析5. 结论与展望5.1 结论总结5.2 研究展望及不足参考文献1. 绪论1.1 研究背景滤波器是电子系统中重要的信号处理器件,用于滤除噪声、干扰等非期望信号,提高系统性能和可靠性。

传统的滤波器通常包括有源滤波器和无源滤波器,有源滤波器具有较高的增益和带宽,但容易产生交叉耦合、不稳定性等问题,不适合高灵敏度和高可靠性的系统应用。

相对地,无源滤波器不需要功率放大器,具有低噪声、低失真、高工作稳定性等优点,因此受到广泛关注。

环路滤波器是一种无源滤波器,它利用环路反馈结构实现信号滤波,可以用于时钟恢复、PLL电路、模数转换器、数字信号处理等领域。

环路滤波器的特点是抑制抖动频率和高频噪声,同时保持信号相位不变,因此能够有效地减少电子系统中时钟服从误差、干扰等问题。

而四阶环路滤波器是基于二阶滤波器级联实现的,具有更高的阻带深度和抑制量,因此适用于对要求更高的滤波应用领域。

1.2 研究目的与意义目前,环路滤波器的设计研究已经相对成熟,但在实际应用中,仍然存在一些问题,如:滤波器带宽、抑制深度、相位噪声等方面的指标需要进一步优化,同时还需要提高滤波器的环路稳定性和抗噪声干扰能力。

因此,本文旨在设计一种基于电荷泵锁相环的四阶无源环路滤波器,通过优化电路设计与参数选择,提高滤波器的性能指标和工作稳定性,实现滤波效果更加优异的无源滤波器。

1.3 现有研究综述电荷泵锁相环作为一种广泛应用于频率合成和时钟恢复领域的锁相环,其具有结构简单、工作稳定、精度高等优点,目前已经在许多应用领域中得到推广应用。

同时,环路滤波器也是一种常用的滤波器结构,在信号处理、相位锁定等领域被广泛应用。

基于CD4046锁相环的电压隔离采样电路设计

便后级电路进行控制。

关键词:锁相环;压控振荡器;电压采样

中图分类号:TN432

文献标识码:A

文章编号:1674-7976-(2019)03-228-04

Design of Voltage Isolation Sampling Circuit Based on CD4046 Phase Locked Loop

convenient rear level circuit for control. Key words: Phase-Locked Loop; Voltage-Controlled Oscillator; Voltage Sampling

0 引言

随着电子技术的不断发展,闭环控制系统由于 具有优良的自动控制特性被大量的应用在精密系 统中,这就要求电路能够准确的采样当前输出的各 种信号,通过反馈进行闭环控制。电子电路中常用 的反馈信号为电压信号,采样的方式大多为电阻分 压采样。但由于前级电路应用的场合不同,采样出 来的电压地电位与反馈系统的地电位不同,使得采 样信号不能直接作用于反馈系统中。本文利用锁相 环 CD4046 芯片良好的 V–F 特性及频率跟踪技术来 实现电压的隔离采样。

2 各模块设计

2.1 电阻分压采样电路

串联电阻分压电路可以将电压降低并进行取 样,合理的选择阻值能够保证采样的精度。本文中 采样电路原理图见图 2。

+9kV 输入

+9kV 输出

5MΩ

5MΩ

5MΩ 取样+

20kΩ 取样-

(-12kV 地电位)

图 2 电阻分压采样电路

选用 3 个 5MΩ 电阻和 1 个 20KΩ 电阻串联分 压,其分压比约为 1:1000。采用差模传输结构, 保证采样电压的稳定性。

基于FPGA的数字锁相环的设计

目录第一章绪论...................................... 错误!未定义书签。

1.1锁相环技术的发展及研究现状................................................... 错误!未定义书签。

1.2课题研究意义 .............................................................................. 错误!未定义书签。

1.3本课题的设计内容....................................................................... 错误!未定义书签。

第二章 FPGA的设计基础............................. 错误!未定义书签。

2.1硬件设计语言-Verilog HDL..................................................... 错误!未定义书签。

2.2 FPGA的设计流程 ......................................................................... 错误!未定义书签。

第三章锁相环的原理. (2)3.1全数字锁相环基本结构 (3)3.2全数字锁相环的工作原理 (4)第四章数字锁相环的设计 (5)4.1基于FPGA的数字锁相环总体设计方案 (5)4.2数字鉴相器的设计 (6)4.3 K变模可逆计数器的设计 (7)4.4脉冲加减器的设计 (10)4.5 N分频器的设计 (12)第五章实验仿真与调试 (14)5.1数字锁相环的仿真 (14)5.2数字锁相环的系统实验 (15)结束语 (19)参考文献 (20)附录 (21)第一章锁相环的原理许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。

2_125_3_125GHz高速CMOS锁相环电路设计_邢立冬 (1)

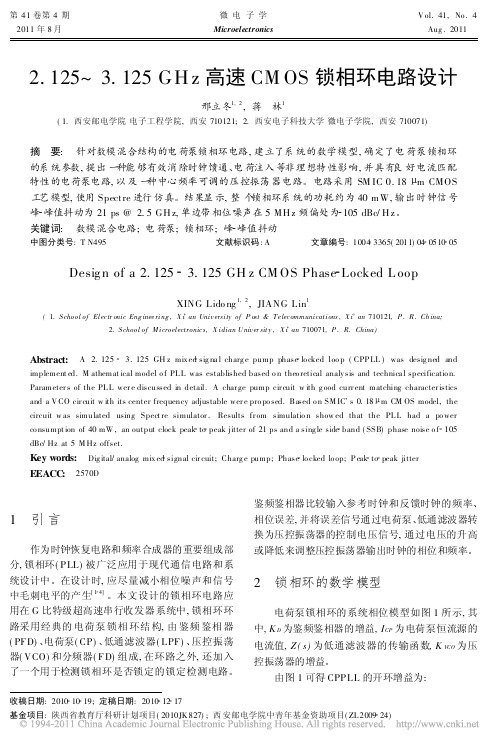

第41卷第4期2011年8月微电子学MicroelectronicsV ol.41,No.4Aug.2011收稿日期:2010 10 19;定稿日期:2010 12 17基金项目:陕西省教育厅科研计划项目(2010JK 827);西安邮电学院中青年基金资助项目(ZL 2009 24)2.125~3.125GH z 高速CM OS 锁相环电路设计邢立冬1,2,蒋 林1(1.西安邮电学院电子工程学院,西安710121; 2.西安电子科技大学微电子学院,西安710071)摘 要: 针对数模混合结构的电荷泵锁相环电路,建立了系统的数学模型,确定了电荷泵锁相环的系统参数,提出一种能够有效消除时钟馈通、电荷注入等非理想特性影响,并具有良好电流匹配特性的电荷泵电路,以及一种中心频率可调的压控振荡器电路。

电路采用SM IC 0.18 m CMOS 工艺模型,使用Spectre 进行仿真。

结果显示,整个锁相环系统的功耗约为40m W,输出时钟信号峰 峰值抖动为21ps @ 2.5GH z,单边带相位噪声在5MH z 频偏处为 105dBc/H z 。

关键词: 数模混合电路;电荷泵;锁相环;峰 峰值抖动中图分类号:T N495文献标识码:A文章编号:1004 3365(2011)04 0510 05Desig n of a 2.125 3.125GH z CM O S Phase Locked L oopXING Lido ng 1,2,JIANG Lin 1(1.S chool of Elec tr onic Eng inee ring ,X i an Univ ersity of P ost &Te lec ommunications ,X i an 710121,P.R.Ch ina;2.S chool of M icroelectronic s,X idian Univ er sity ,X i an 710071,P.R.China)Abstract: A 2.125 3.125GH z mix edsig na l charg e pump phase lo cked loo p (CPP LL )was desig ned and implement ed.M athemat ical model o f PL L was established based o n theo retical analy sis and technica l specificatio n.Parameter s of the PL L wer e discussed in detail.A char ge pump cir cuit w ith g ood curr ent matching character istics and a V CO cir cuit w ith its center frequency adjustable wer e pro po sed.Based o n SM IC s 0.18 m CM OS model,the circuit w as simulated using Spect re simulator.Results fr om simulatio n show ed that the PL L had a po wer co nsumpt ion of 40mW ,an output clock peak to peak jitter of 21ps and a sing le side band (SSB)phase noise o f 105dBc/Hz at 5M Hz offset.Key words: Dig ital/analog mix ed signal cir cuit;Charg e pump;Phase lo cked lo op;P eak to peak jitter EEACC : 2570D1 引言作为时钟恢复电路和频率合成器的重要组成部分,锁相环(PLL)被广泛应用于现代通信电路和系统设计中。

锁相环

锁相环(PLL)讲义1、相环的分类锁相环可分为模拟锁相环和数字锁相环。

本篇主要介绍3种锁相环器件:模拟:低频LM567(NE567)、高频NE564数字:CD4046此外,由于模拟锁相环与数字锁相环在原理上的区别不是很大,因此我们以数字锁相环为主来论述锁相环的基本原理。

2、锁相环的基本原理锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。

它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。

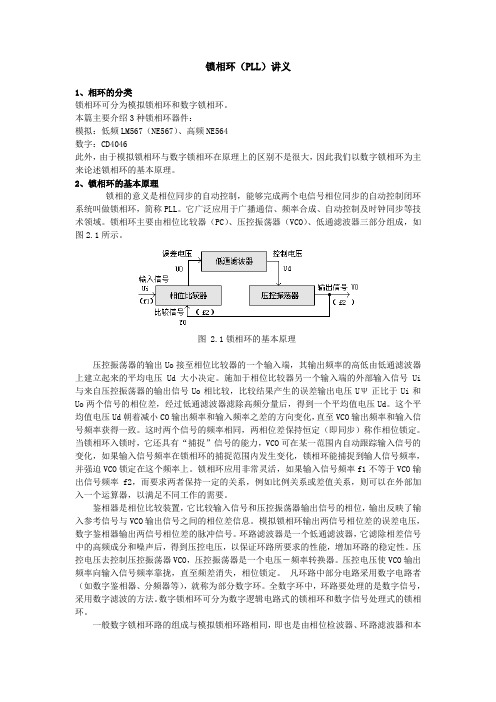

锁相环主要由相位比较器(PC)、压控振荡器(VCO)、低通滤波器三部分组成,如图2.1所示。

图 2.1锁相环的基本原理压控振荡器的输出Uo接至相位比较器的一个输入端,其输出频率的高低由低通滤波器上建立起来的平均电压Ud大小决定。

施加于相位比较器另一个输入端的外部输入信号Ui 与来自压控振荡器的输出信号Uo相比较,比较结果产生的误差输出电压UΨ正比于Ui和Uo两个信号的相位差,经过低通滤波器滤除高频分量后,得到一个平均值电压Ud。

这个平均值电压Ud朝着减小CO输出频率和输入频率之差的方向变化,直至VCO输出频率和输入信号频率获得一致。

这时两个信号的频率相同,两相位差保持恒定(即同步)称作相位锁定。

当锁相环入锁时,它还具有“捕捉”信号的能力,VCO可在某一范围内自动跟踪输入信号的变化,如果输入信号频率在锁相环的捕捉范围内发生变化,锁相环能捕捉到输人信号频率,并强迫VCO锁定在这个频率上。

锁相环应用非常灵活,如果输入信号频率f1不等于VCO输出信号频率f2,而要求两者保持一定的关系,例如比例关系或差值关系,则可以在外部加入一个运算器,以满足不同工作的需要。

鉴相器是相位比较装置,它比较输入信号和压控振荡器输出信号的相位,输出反映了输入参考信号与VCO输出信号之间的相位差信息。

模拟锁相环输出两信号相位差的误差电压,数字鉴相器输出两信号相位差的脉冲信号。

环路滤波器是一个低通滤波器,它滤除相差信号中的高频成分和噪声后,得到压控电压,以保证环路所要求的性能,增加环路的稳定性。

3VCO锁相电路

实验三VCO锁相环电路1一、实验目的:1、掌握VCO压控振荡器的基本工作原理,加深对基本锁相环工作原理的理解。

2、熟悉锁相环数字频率合成器的电路组成与工作原理。

3、掌握锁相环的基本原理4、掌握锁相式数字频率合成器的设计二、实验电路工作原理:锁相环是无线电发射中使用频率较为稳定的一种方法,主要有VCO(压控振荡器)和PLL集成电路,压控振荡器给出一个信号,一部分作为输出,另一部分通过分频与PLL 集成电路所产生的本振信号作相位比较,为了保持频率不变,就要求相位差不发生改变,如果有相位差的变化,则PLL集成电路的电压输出端的电压发生变化去控制VCO,直到相位差恢复,图3-1 VCO电路原理图达到锁频的目的,能使受控振荡器的频率和相位均与输入信号保持确定关系的闭环电子电路。

VCO电路原理图如图3-1所示。

1、4046锁相环芯片介绍4046锁相环的功能框图如图2所示,外线排列管脚功能简要介绍:第1引脚(PD03):相位比较器2输出的相位差信号,为上升沿控制逻辑。

第2引脚(PD01):相位比较器1输出的相位差信号,它采用异或门结构,即鉴相特性,为PD01=PD11 PD12第3引脚(PD12):相位比较器输入信号,通常PD为来自VCO参考信号。

第4引脚(VCO0):压控振荡器的输出信号。

第5引脚(INH):控制信号输入,若INH为低电平,则允许VCO工作和源极跟随器输出:若INH为高电平,则相反,电路将处于功耗状态。

第6引脚(CI):与第7引脚之间接一电容,以控制VCO的振荡频率。

第7引脚(CI):与第6引脚之间接一电容,以控制VCO的振荡频率。

第8引脚(GND):接地。

第9引脚(VCO1):压控振荡器的输入信号。

2第10引脚(SF0):源极跟随器输出。

第11引脚(R1):外接电阻至地,分别控制VCO的最高和最低振荡频率。

第12引脚(R2):外接电阻至地,分别控制VCO的最高和最低振荡频率。

第13引脚(PD02):相位比较器输出的三态相位差,它采用PD11、PD12上升沿控制逻辑。

CMOS集成锁相环电路设计

参考文献

[ 1 】 h t t p : / / n e w s . x i n h u a n e t . c o m / 2 0 1 3 一O 4 /1 1 / c _ 1 1 5 5 5 7 7 6 5 . h i m . 教 育

供 实 际操 作 与理 论 知识 相 结 合的学 习平 台 ,并 且能 突 出重 点 ,培养他们的重点技能 ,迎合 当地 照明产业的重 点需 求 ;与此 同 时 ,我 们也 能够 发挥 高校 在 科研 上 的优 势 ,寻 求 与 企业 合 作研 发 的契 合 点 ;总 之 ,通 过产 学 研 的结 合 ,

通知 . 人 民 网一时政 频 道 . 2 0 1 5 # - 5 月1 6 E l

年级本科 和研 究生教材 同时可作为模拟 混合 电路设计 、射频

通信 电路系统设计人员的参考 书。 张刚,美 国卡耐基梅隆大学 电子与计算机工程博 士 .清 华 大学 电子工程微 电子专业学 士。近十年来在美国加 卅 I 圣地亚哥 高通公司射频模拟 集成 电路部 工作 ,任资深高级工程师 ,主持 设计 多款大规模生产的射频频率合成器 .现有 9 项 已获批美国 专利。在加州大学圣地 亚哥分校任兼职助理教授 .讲授射频频 率合成和时钟恢复的研 究生课程 。曾应邀于清华大学和北京 大 学微 电子所讲授短期高级锁相环课程 。

题 ,达 到 三方 共赢 的结 果 。

所属分类 :

图 书 > 电子 与 通信 > 微 电子 学、 集成 电路 ( I C )

5 结语

当前 ,半 导 体 照 明产业 作 为 战 略新 兴产 业 正 迅猛 向前 发 展 ,对 专 业 人才 的需 求 紧 迫 而 旺 盛 ,我 们 作 为 地 方 高 校 ,建 设光 源 与 照 明专 业方 向 结合 了当地 的 重 点产业 发 展 需求 ,能够 做 到 人才 培 养与 人 才需 求 的对 接 ,从 而 为地 方 经济 和社 会 发展提 供 有效 服务 。

锁相环

如今,数字电路,特别是大规模集成数字电路技术的发展,给通信技术领域的发展提供了更有力的支持。

各种电子产品潮水般涌现入各个领域。

电子线路以其制作简单、易于控制、可靠性强、体积小、成本低廉等优点,以广泛应用于各个行业,电子产品无处不在,电子技术无处不用。

随着新器件的不断面市,新电路出现了更多的新功能,新的设计如雨后春笋般涌现!电子系统设计的多样化和复杂化的发展趋势,推动着EDA(电子设计自动化)软件的发展和完善进程。

传统的实现载波提取的部件通常是由CMOS 集成电路构成4046数字锁相环,中小规模TTL 集成电路74系列构成平方律部件和分频电路。

这类的载波提取部件工作频率低,可靠性差。

正因为大规模数字电路的发展,现在可将数字锁相环,平房律部件以及分频器直接写入FPGA,完成载波提取的功能。

现场可编程门阵列(FPGA)的出现是超大规模集成电路技术和计算机辅助设计技术发展的结果。

FPGA 器件集成度高、体积小,具有通过用户编程实现专门应用的功能。

他允许电路设计者利用基于计算机的开发平台,经过设计输入、仿真、测试和校验,直到达到预期的结果。

使用FPGA 器件可以大大缩短系统的研制周期,减少资金投入。

更吸引人的是,采用FPGA 器件可以将原来的电路板级产品集成为芯片级产品,从而降低了功耗,提高了可靠性,同时还可以很方便地对设计进行在线修改。

FPGA 器件成为研制开发的理想器件,特别适合产品地样机开发和小批量生产,因此有时人们也把FPGA 称为可编程的ASIC。

另一方面,20世纪90年代以后高精密度PLD 在生产工艺、器件地编程和测试技术等方面都有了飞速的发展。

例如CPLD 的集成度一般可达数千甚至上万门,ALTERA 公司推出的EPM9560,其单密度达到12000个可用门,包括多达50个宏单元,216个用户I/O 引脚,并能提供15ns 的脚至脚延时,16位计数器的最高工作频率为118MHZ。

可编程逻辑器件的技术的高速发展。

锁相环计算方法

2、理论分析计算与电路设计2.1 锁相环2.1.1 锁相环原理为了使系统产生稳定的载波,本系统设计中采用锁相环路。

锁相环路是一种反馈控制电路,将参考信号与输出信号之间的相位进行比较,产生相位误差电压来调整输出信号的相位以达到与参考信号同频的目的。

由MC145152、MC12022及压控振荡器组成的锁相环路产生的载波的稳定度达到4×10-5,准确度达到3×10-5。

锁相环的总体框图如下:2.1.2 锁相环分频锁相环分频由参考分频和可编程分频组成,由MC145152及MC12022实现。

分频框图如下:图中PD 为数字鉴相器,f o 为压控振荡的输出频率(即发射频率)。

由于压控振荡器输出信号的频率比较大,MC145152无法对它直接分频,必须用MC12022芯片先进行预分频获得频率较小的信号。

MC12022内有64和63两种分频系数 本设计中采用64分频,即P=64。

MC12022输出的信号进入MC145152进行再次分频后与参考信号进行相位比较,使载波达到与参考信号相同的稳定度。

本设计中参考信号通过晶振分频得到。

参考晶振(10.24MHz晶体振荡器,频率稳定度可达10-5~10-6)从MC145152芯片的OSCIN 、OSCOUT 接入,MC145152中的÷R 计数器对参考信号进行参考分频。

本设计中设置R =1024,即R A0R A1R A2=101,对晶振频率进行1024分频得到10KHz 的参考频率信号。

用4位拨码开关设置R 的值,MC145152的参考分频系数如下:MC145152芯片集分频、鉴相于一体,内有÷A 减法计数器,÷N 减法计数器进行可编程分频。

分频系数N 、A 由并行输入的数据控制,本设计中通过单片机来控制N 、A,改变N 、A 的值即可实现频道的选择。

可编程分频的原理及计算如下:根据吞咽脉冲计数的原理:吞咽脉冲计数器开始计数时,M的初值为1,÷A和÷N两个计数器被置入预置数并同时计数,当计到A(P+1)个输入脉冲(f o)时,÷A计数器计完A个预置数,M变为0;此时÷A计数器被控制信号关闭,停止计数;而÷N计数器中还有N -A个数,它继续计(N-A)P个输入脉冲后,输出一个脉冲到鉴相器PD。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

锁相环电路设计:让你的电路更稳定

锁相环(PLL)电路是一种常用的控制电路,可以用来实现频率合成、时钟与信号恢复等功能。

在电子设备中,PLL电路的使用非常广泛,因为它能够使电路的频率更加精确、稳定,使电路的性能更优秀。

本

文将介绍PLL电路的基本原理、设计方法和应用技巧。

一、PLL电路的基本原理

PLL电路的基本构成包括:相锁环(Phase-Locked Loop,PLL)模块、反馈电路和指令电路。

根据反馈信号的不同,又可以将PLL电路

分为:模拟PLL和数字PLL两类。

模拟PLL是指使用模拟电路实现的PLL电路,适用于处理频率较低、波形较简单的信号。

数字PLL是把PLL电路中的关键部分数字化,使用数字处理技术实现PLL电路,适用于对高速、复杂信号的处理。

PLL电路的基本原理是通过比较两个不同频率的信号,调节反馈电路的传递函数,使输出信号与参考信号保持同步,最终达到同步稳定

的效果。

二、PLL电路的设计方法

设计PLL电路时需要注意以下几点:

1. 选择适合的锁相范围

锁相范围一般是指锁相环能够自动跟踪的信号频率范围。

选择适

合的锁相范围可以使PLL电路更加灵活、稳定。

2. 选择适合的环路带宽和相位裕度

环路带宽是锁相环的工作频带范围,它决定了PLL电路的速度和

稳定性。

相位裕度是指锁相环输出信号相位与参考信号相位的差值,

它直接影响锁相环的稳定性。

选择适合的环路带宽和相位裕度可以使PLL电路更加稳定、可靠。

3. 选择合适的滤波器

为了降低PLL电路输出信号中的噪声和抖动,需要在反馈电路中

添加合适的滤波器。

选择合适的滤波器可以使PLL电路的性能更加优秀。

三、PLL电路的应用技巧

1. 尽量避免信号功率幅度过大或过小

PLL电路对信号功率幅度很敏感,过大或过小的信号功率都会对

PLL电路的稳定性产生不良影响。

因此,在设计和应用时,应尽量避免信号功率偏离正常值。

2. 注意环路稳定性

PLL电路不同于普通反馈电路,它需要有信号的引导才能正常工作。

因此,需要对PLL电路的环路稳定性进行严格的检测和分析,确保其

稳定性和可靠性。

3. 注意相位噪声

PLL电路中的相位噪声对于信号质量的影响非常大。

因此,在设计和应用中,需要注意减少PLL电路的相位噪声,以保证输出信号质量。

总之,PLL电路是一种功能强大、使用广泛的控制电路,能够使电路的频率更加精确、稳定。

在设计和应用中,需要注意选择适合的锁

相范围、环路带宽和相位裕度,以及注意信号功率幅度、环路稳定性

和相位噪声等问题。

只有做好这些方面的工作,才能使PLL电路发挥

更佳的性能,让你的电路更加稳定。