2015年杭州电子科技大学微机原理与接口技术2015考研真题/研究生入学考试试题

微机原理(杭州电子科技大学【4】8086系统结构[2-3]

![微机原理(杭州电子科技大学【4】8086系统结构[2-3]](https://img.taocdn.com/s3/m/3b8cd1f4f90f76c661371a65.png)

15:28

22

二、系统的复位与启动

【8086CPU时序】

① 复位信号:通过RESET引脚上的触发信号来引起8086系统复位和启

动,RESET至少维持4个时钟周期的高电平。

② 复位操作:当RESET信号变成高电平时,8086/8088CPU结束现行

操作,各个内部寄存器复位成初值。

标志寄存器

清零

指令寄存器 CS寄存器 DS寄存器 SS寄存器 ES寄存器

的比例倍频后得到CPU的主频,即: CPU主频 = 外频 × 倍频系数

⑥ PC机各子系统时钟(存储系统,显示系统,总线等)是由系统频率按 照一定的比例分频得到。

15:28

5

内频 550MHz Pentium III

倍频系数5.5

L1 Cache

L2 550MHz Cache

处理机总线 100MHz

微机原理与接口技术

第四讲

15:28

第二章 8086系统结构

内容提要

z微型计算机的发展概况 z8086CPU内部结构 z8086CPU引脚及功能 z8086CPU存储器组织 z8086CPU系统配置 z8086CPU时序

15:28

2

※有关概念介绍

z 主频,外频,倍频系数 z T状态 z 总线周期 z 指令周期 z 时序 z 时序图

总线操作

读存储器操作 (取操作数)

写存储器操作 (将结果存放到内存)

读 I/O 端口操作 (取 I/O 端口中的数)

写 I/O 端口操作 (往 I/O 端口写数)

中断响应操作

总线周期

存储器读周期 存储器写周期 I/O 端口读周期 I/O 端口写周期 中断响应周期

15:28

2015年计算机真题及解析.

2015年全国硕士研究生入学统一考试计算机学科专业基础综合试题一、单项选择题:140小题,每小题2分,共80分。

下列每题给出的四个选项中,只有一个选项符合题目要求。

请在答题卡上将所选项的字母涂黑。

1.已知程序如下:int s(int n){ return (n<=0) ? 0 : s(n-1) +n; }void main(){ cout<< s(1); }程序运行时使用栈来保存调用过程的信息,自栈底到栈顶保存的信息一次对应的是A.main()->S(1)->S(0) B.S(0)->S(1)->main()C.m ain()->S(0)->S(1) D.S(1)->S(0)->main()D.先序序列为a,b,c,d的不同二叉树的个数是A.13 B.14 C.15 D.163.下列选项给出的是从根分别到达两个叶节点路径上的权值序列,能属于同一棵哈夫曼树的是A.24,10,5和24,10,7 B.24,10,5和24,12,7C.24,10,10和24,14,11 D.24,10,5和24,14,64.现在有一颗无重复关键字的平衡二叉树(A VL树),对其进行中序遍历可得到一个降序序列。

下列关于该平衡二叉树的叙述中,正确的是A.根节点的度一定为2 B.树中最小元素一定是叶节点C.最后插入的元素一定是叶节点D.树中最大元素一定是无左子树5.设有向图G=(V,E),顶点集V={V0,V1,V2,V3},边集E={<v0,v1>,<v0,v2>,<v0,v3>,<v1,v3>},若从顶点V0 开始对图进行深度优先遍历,则可能得到的不同遍历序列个数是A.2 B.3 C.4 D.56.求下面带权图的最小(代价)生成树时,可能是克鲁斯卡(kruskal)算法第二次选中但不是普里姆(Prim)算法(从V4开始)第2次选中的边是A.(V1,V3) B.(V1,V4) C.(V2,V3) D.(V3,V4)7.下列选项中,不能构成折半查找中关键字比较序列的是A.500,200,450,180 B.500,450,200,180C.180,500,200,450 D.180,200,500,4508.已知字符串S为“abaabaabacacaabaabcc”. 模式串t为“abaabc”, 采用KMP算法进行匹配,第一次出现“失配”(s[i] != t[i]) 时,i=j=5,则下次开始匹配时,i和j的值分别是A.i=1,j=0 B.i=5,j=0 C.i=5,j=2 D.i=6,j=29.下列排序算法中元素的移动次数和关键字的初始排列次序无关的是A.直接插入排序B.起泡排序C.基数排序D.快速排序10.已知小根堆为8,15,10,21,34,16,12,删除关键字8之后需重建堆,在此过程中,关键字之间的比较数是A.1 B.2 C.3 D.411.希尔排序的组内排序采用的是()A.直接插入排序B.折半插入排序 C.快速排序D.归并排序12.计算机硬件能够直接执行的是()Ⅰ.机器语言程序Ⅱ.汇编语言程序Ⅲ.硬件描述语言程序A.仅ⅠB.仅ⅠⅡC.仅ⅠⅢD.ⅠⅡⅢ13.由3个“1”和5个“0”组成的8位二进制补码,能表示的最小整数是()A.-126 B.-125 C.-32 D.-314.下列有关浮点数加减运算的叙述中,正确的是()Ⅰ. 对阶操作不会引起阶码上溢或下溢Ⅱ. 右规和尾数舍入都可能引起阶码上溢Ⅲ. 左规时可能引起阶码下溢Ⅳ. 尾数溢出时结果不一定溢出A.仅ⅡⅢB.仅ⅠⅡⅣC.仅ⅠⅢⅣD.ⅠⅡⅢⅣ15.假定主存地址为32位,按字节编址,主存和Cache之间采用直接映射方式,主存块大小为4个字,每字32位,采用回写(Write Back)方式,则能存放4K字数据的Cache 的总容量的位数至少是()A.146k B.147K C.148K D.158K16.假定编译器将赋值语句“x=x+3;”转换为指令”add xaddt, 3”,其中xaddt是x 对应的存储单元地址,若执行该指令的计算机采用页式虚拟存储管理方式,并配有相应的TLB,且Cache使用直写(Write Through)方式,则完成该指令功能需要访问主存的次数至少是()A.0 B.1 C.2 D.317.下列存储器中,在工作期间需要周期性刷新的是()A.SRAM B.SDRAM C.ROM D.FLASH18.某计算机使用4体交叉存储器,假定在存储器总线上出现的主存地址(十进制)序列为8005,8006,8007,8008,8001,8002,8003,8004,8000,则可能发生发生缓存冲突的地址对是()A.8004、8008 B.8002、8007 C.8001、8008 D.8000、800419.下列有关总线定时的叙述中,错误的是()A.异步通信方式中,全互锁协议最慢B.异步通信方式中,非互锁协议的可靠性最差C.同步通信方式中,同步时钟信号可由多设备提供D.半同步通信方式中,握手信号的采样由同步时钟控制20.若磁盘转速为7200转/分,平均寻道时间为8ms,每个磁道包含1000个扇区,则访问一个扇区的平均存取时间大约是( )A.8.1ms B.12.2ms C.16.3ms D.20.5ms21.在采用中断I/O方式控制打印输出的情况下,CPU和打印控制接口中的I/O端口之间交换的信息不可能是( )A.打印字符B.主存地址C.设备状态D.控制命令22.内部异常(内中断)可分为故障(fault)、陷阱(trap)和终止(abort)三类。

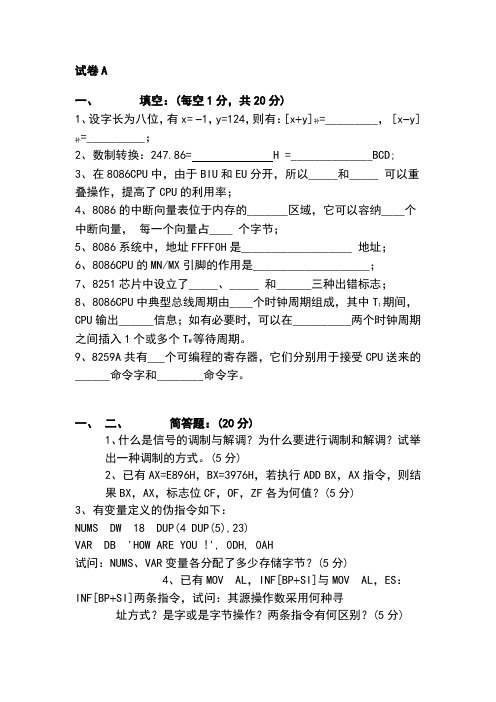

微机原理与接口技术考试试题及答案

微机原理与接⼝技术考试试题及答案《微机原理与接⼝技术》课程期末考试试卷(A卷,考试)⼀、单项选择(在备选答案中选出⼀个正确答案,并将其号码填在题⼲后的括号内。

每题2分,共30分)1 .某微机最⼤可寻址的内存空间为16MB,其CPU地址总线⾄少应有()条。

A. 32B. 16C. 20D. 242 .⽤8088CPU组成的PC机数据线是()。

A. 8条单向线B. 16条单向线C. 8条双向线D. 16条双向线3 .微处理器系统采⽤存储器映像⽅式编址时存储单元与I/O端⼝是通过()来区分的。

A. 不同的地址编码B. 不同的读控制逻辑C. 不同的写控制逻辑D. 专⽤I/O指令4 .要禁⽌8259A的IR0的中断请求,则其中断屏蔽操作指令字OCW1应为()。

A. 80HB. 28HC. E8HD. 01H5 .在8086环境下,对单⽚⽅式使⽤的8259A进⾏初始化时,必须放置的初始化命令字为()。

A. ICW1,ICW2,ICW3B. ICW1,ICW2,ICW4C.ICW1,ICW3,ICW4 D. ICW2,ICW3,ICW46 .6166为2Kx8位的SRAM芯⽚,它的地址线条数为()。

A. 11B. 12C. 13D. 147 .在计算机系统中,可⽤于传送中断请求和中断相应信号的是()。

A. 地址总线B. 数据总线C. 控制总线D. 都不对8 .段寄存器装⼊2300H,该段的最⼤结束地址是()。

A. 32FFFHB. 23000HC. 33FFFHD. 33000H9 .在进⼊DMA⼯作⽅式之前,DMA控制器当作CPU总线上的⼀个()。

A. I/O设备B. I/O接⼝C. 主处理器D. 逻辑⾼10 .在8086宏汇编过程中不产⽣指令码,只⽤来指⽰汇编程序如何汇编的指令是()。

A. 汇编指令B. 宏指令C. 机器指令D. 伪指令11 .中断向量表占⽤内存地址空间为()。

A. 00000H~003FFHB. 00000H~000FFHC. 00000H~00100HD. FFF00H~FFFFFH12 .实现CPU与8259A之间信息交换是()。

(完整word版)微机原理与接口技术期末考试复习试题

微机原理与接口技术》试题(第一套) 、选择题(每题 3 分,共 30 分)8288 在 8086/8088 组成的计算机中的作用是 ( ② )。

提供系统时钟 CLK式为 ( ② )。

④ 变址寻址该存储单元的物理地址为 (④ 3AAA8H38060+2A48=3AAA8H片的存储容量为 ( ③ )。

④ 32KX 85.某存储器芯片容量为2KX 1 bit 、若用它组成 16KX 8bit存储器组, 所用芯片数以及用于组内寻址的地址线为 ( ② )。

① 32 片、 11 根 ② 64 片、14 根 ③ 8 片、 14 根 ④ 16 片、 8 根1. 数据缓冲器② 总线控制器 ③ 地址锁存器2. 指令 MOV 0283H[BX][SI] , AX中目标操作数的寻址方① 寄存器寻址② 基址变址相对寻址 ③ 基址寻址3.某存储单元的段基址为3806H ,段内偏移地址为 2A48H ,① 4100H3AA08H ③ 3B008H4.某存储器芯片有地址线13 根,数据线 8 根、该存储器芯① 15K X 832K X 256 ③ 8K X 8程序段④ 三个独立通道预置方式。

2、具有三种基本的传输方式:单字节传送、数 据块传送、 请求传送。

3、具有存储器到存储器的传送功能并行输入输出端口。

并行输入输出端口。

并行输入输出端口。

端口。

6. ADD AX ,[BX+8] ”的源操作数在当前(② )。

堆栈段② 数据段③ 代码段7. DMAC 8237 具有 ( ② ) 。

八个独立通道四个独立通道③ 二个独立通DMAC8237A 的主要性能:1、有 4 个独立的 DMA 通道,每 个通道都充许开放或禁止DMA 请求,都可以独立控制自动4、 具有正常时序和压缩时序两种基本时序。

5、 8257A 级联可扩充任意个 DMA 通道。

6、有两种优先管理方式: 固定优先级和循环优先级。

7、有较高的数据传输速率。

8.可编程并行接口 8255A 具有 ( ①)① 两个 8 位 (A 口、 口)和两个 4 位 (C 口的高、 低各 ② 两个 8 位 (A 口、 口) 和两个 4 位 (B 口的高、 低各③ 两个 8 位 (B 口、 口) 和两个 4 位 (A 口的高、 低各④ 两个 4 位 (A 口、 B口)和一个8位(C 口)并行输入输出9.8259分别有( ③ )个 ICW 和 OCW 。

微机原理与接口技术AB卷试题与答案.概要

试卷A一、填空:(每空1分,共20分)1、设字长为八位,有x= -1,y=124,则有:[x+y]补=_________, [x-y];补=__________2、数制转换:247.86= H =______________BCD;3、在8086CPU中,由于BIU和EU分开,所以_____和_____ 可以重叠操作,提高了CPU的利用率;4、8086的中断向量表位于内存的_______区域,它可以容纳____个中断向量,每一个向量占____ 个字节;5、8086系统中,地址FFFF0H是___________________ 地址;6、8086CPU的MN/MX引脚的作用是____________________;7、8251芯片中设立了_____、_____ 和______三种出错标志;8、8086CPU中典型总线周期由____个时钟周期组成,其中T1期间,CPU输出______信息;如有必要时,可以在__________两个时钟周期之间插入1个或多个T W等待周期。

9、8259A共有___个可编程的寄存器,它们分别用于接受CPU送来的______命令字和________命令字。

一、二、简答题:(20分)1、什么是信号的调制与解调?为什么要进行调制和解调?试举出一种调制的方式。

(5分)2、已有AX=E896H,BX=3976H,若执行ADD BX,AX指令,则结果BX,AX,标志位CF,OF,ZF各为何值?(5分)3、有变量定义的伪指令如下:NUMS DW 18 DUP(4 DUP(5),23)VAR DB 'HOW ARE YOU !', 0DH, 0AH试问:NUMS、VAR变量各分配了多少存储字节?(5分)4、已有MOV AL,INF[BP+SI]与MOV AL,ES:INF[BP+SI]两条指令,试问:其源操作数采用何种寻址方式?是字或是字节操作?两条指令有何区别?(5分)二、三、读图 (10分)下图中,AB7~AB0为8086CPU低八位地址总线试问:1、8259A占用______个端口地址,分别为____________,其中ICW1的设置地址为_________________;2、8255A占用_____个端口地址,分别为__________________,其中控制寄存器的地址为_______。

微机控制与接口技术_2015_2017年考试卷汇总

微机控制与接口技术作业(二)一、填空题1.8086是16 位的微处理器,其内部数据通路为16 位,其对外数据总线为16 位;8088内部数据通路为16 位, 其对外数据总线为8 位。

2一个微计算机应包含: 微处理器, 存储器, I/O接口电路,系统总线基本功能部件。

3 EU 是8086/8088微处理器的执行部件,BIU 是8086/8088微处理器的总线接口部件。

二、判断下列论述是否正确,不正确的请加以改正。

(1)INT指令执行后,堆栈顶部三个栈单元(SP)、(SP)+2、(SP)+4依次保存FLAGS、断点IP值、断点CS值。

不对,堆栈顶部三个栈单元(SP)、(SP)+2、(SP)+4依次保存的应是断点IP值、断点CS 值、FLAGS。

(2)中断类型号是中断向量表中存放相应中断向量的首地址。

不对,中断类型号×4才是相应中断向量的首地址。

三、分析以下程序回答问题XOR A X, AX (1)程序段完成什么工作?MOV BX, M 答:将X数组中的n个元素之和存放在RESULT单元中。

SUB BX, 2 (2)定义一个适合这段程序的数据段。

LOP1: ADD AX , X[BX] DATA SEGMENTSUB BX, 2 X DW n DUP(?)JGE LOP 1 M DW 2nMOV RESULT, AX N DW nRET RESULT DW ?DATA ENDS四、8086/8088在什么时候及什么条件下可以响应一个外部INTR中断请求?中断向量表在存储器的什么位置?向量表的内容是什么?8086如何将控制转向中断服务程序?答:(1)8086/8088在当前指令执行完且IF=1的情况下可以响应一个外部INTR中断请求。

(2)中断向量表在存储器的0段0000—03FFH区域,向量表存放中断处理程序的入口地址。

(3)8086/8088响应INTR中断请求时,首先在连续的两个总线周期中发出INTA#负脉冲,在第二个INTA#信号期间,中断源经数据总线向8086/8088送出一字节中断向量“类型码”。

杭州电子科技大学2023年《891微机原理与接口技术》考研专业课考试大纲

杭州电子科技大学全国硕士研究生招生考试业务课考试大纲考试科目名称:微机原理与接口技术科目代码:891 一、微型计算机概论●冯.诺依曼型计算机系统的组成、特点和工作原理;●计算机的分类,微机技术的两大分支;●微控制器基本结构及其特点;指令、指令体系、程序和软件的基本概念。

二.STC15注系列微控制器结构和原理●STC15系列微控制器的结构和工作原理;●微控制器内部组成及信号引脚;存储器配置情况;●并行输入/输出电路结构;●时钟电路与时序、系统复位。

三.基于C语言的程序设计●C51数据类型;●基本运算符的应用;●C51程序结构及语法特点;●常用程序的设计流程和调试方法。

四.微控制器存储器扩展●微控制器存储器的扩展结构和实现方法●存储器扩展的编址技术;五. 中断系统●微控制器中断的概念、功能、中断源、处理流程;●STC15系列微控制器中断系统结构、中断处理过程;●STC15系列微控制器中断控制方法和编程技术。

六. 定时器与计数器●STC15微控制器定时器/计数器的结构与工作原理;●STC15微控制器定时器/计数器的控制方法和编程技术;七.模拟接口技术●数/模转换器的工作原理、技术指标、结构特点;●TLC5615接口芯片的内部结构与工作方式;●TLC5615与STC15系列51微控制器的连接电路的设计与应用;●模/数转换器的工作原理、技术指标、结构特点;八.串行数据通信●微控制器串行通信的基本知识;●STC15微控制器串口的内部结构、控制寄存器的结构、工作方式设置;●异步串行通信编程方法;●RS-232C和RS-485的概念;九.人机接口技术●矩阵键盘的行列式扫描法工作原理及编程方法。

●动态数码管显示工作原理及编程方法。

十.单片机应用系统设计●能够结合日常生活,描述单片机的具体应用。

参考书目:注:学生只需掌握和经典MCS51兼容部分的相关知识即可。

●《单片微型计算机原理及接口技术》,陈桂友编高等教育出版社2017.7。

2015年全国硕士研究生计算机考研真题

2015年全国硕士研究生计算机考研真题一、单项选择题:140小题,每小题2分,共80分。

下列每题给出的四个选项中,只有一个选项符合题目要求。

请在答题卡上将所选项的字母涂黑。

1.已知程序如下:int s(int n){return(n<=0)?0:s(n-1)+n;}void main(){cout<<s(1);}程序运行时使用栈来保存调用过程的信息,自栈底到栈顶保存的信息一次对应的是A.main()->S(1)->S(0)B.S(0)->S(1)->main()main()->S(0)->S(1)D.S(1)->S(0)->main()先序序列为a,b,c,d的不同二叉树的个数是A.13B.14C.15D.163.下列选项给出的是从根分别到达两个叶节点路径上的权值序列,能属于同一棵哈夫曼树的是A.24,10,5和24,10,7B.24,10,5和24,12,7C.24,10,10和24,14,11D.24,10,5和24,14,64.现在有一颗无重复关键字的平衡二叉树(AVL树),对其进行中序遍历可得到一个降序序列。

下列关于该平衡二叉树的叙述中,正确的是A.根节点的度一定为2B.树中最小元素一定是叶节点C.最后插入的元素一定是叶节点D.树中最大元素一定是无左子树5.设有向图G=(V,E),顶点集V={V0,V1,V2,V3},边集E={,,,},若从顶点V0开始对图进行深度优先遍历,则可能得到的不同遍历序列个数是A.2B.3C.4D.56.求下面带权图的最小(代价)生成树时,可能是克鲁斯卡(kruskal)算法第二次选中但不是普里姆(Prim)算法(从V4开始)第2次选中的边是A.(V1,V3)B.(V1,V4)C.(V2,V3)D.(V3,V4)7.下列选项中,不能构成折半查找中关键字比较序列的是A.500,200,450,180B.500,450,200,180C.180,500,200,450D.180,200,500,4508.已知字符串S为“abaabaabacacaabaabcc”.模式串t为“abaabc”,采用KMP算法进行匹配,第一次出现“失配”(s[i]!=t[i])时,i=j=5,则下次开始匹配时,i和j的值分别是A.i=1,j=0B.i=5,j=0C.i=5,j=2D.i=6,j=29.下列排序算法中元素的移动次数和关键字的初始排列次序无关的是A.直接插入排序B.起泡排序C.基数排序D.快速排序10.已知小根堆为8,15,10,21,34,16,12,删除关键字8之后需重建堆,在此过程中,关键字之间的比较数是A.1B.2C.3D.411.希尔排序的组内排序采用的是()A.直接插入排序B.折半插入排序C.快速排序D.归并排序12.计算机硬件能够直接执行的是()Ⅰ.机器语言程序Ⅱ.汇编语言程序Ⅲ.硬件描述语言程序A.仅ⅠB.仅ⅠⅡC.仅ⅠⅢD.ⅠⅡⅢ13.由3个“1”和5个“0”组成的8位二进制补码,能表示的最小整数是()A.-126B.-125C.-32D.-314.下列有关浮点数加减运算的叙述中,正确的是()Ⅰ.对阶操作不会引起阶码上溢或下溢Ⅱ.右规和尾数舍入都可能引起阶码上溢Ⅲ.左规时可能引起阶码下溢Ⅳ.尾数溢出时结果不一定溢出A.仅ⅡⅢB.仅ⅠⅡⅣC.仅ⅠⅢⅣD.ⅠⅡⅢⅣ15.假定主存地址为32位,按字节编址,主存和Cache之间采用直接映射方式,主存块大小为4个字,每字32位,采用回写(Write Back)方式,则能存放4K字数据的Cache的总容量的位数至少是()A.146k B.147K C.148K D.158K16.假定编译器将赋值语句“x=x+3;”转换为指令”add xaddt,3”,其中xaddt是x对应的存储单元地址,若执行该指令的计算机采用页式虚拟存储管理方式,并配有相应的TLB,且Cache使用直写(Write Through)方式,则完成该指令功能需要访问主存的次数至少是()A.0B.1C.2D.317.下列存储器中,在工作期间需要周期性刷新的是()A.SRAM B.SDRAM C.ROM D.FLASH18.某计算机使用4体交叉存储器,假定在存储器总线上出现的主存地址(十进制)序列为8005,8006,8007,8008,8001,8002,8003,8004,8000,则可能发生发生缓存冲突的地址对是()A.8004、8008B.8002、8007C.8001、8008D.8000、800419.下列有关总线定时的叙述中,错误的是()A.异步通信方式中,全互锁协议最慢B.异步通信方式中,非互锁协议的可靠性最差C.同步通信方式中,同步时钟信号可由多设备提供D.半同步通信方式中,握手信号的采样由同步时钟控制20.若磁盘转速为7200转/分,平均寻道时间为8ms,每个磁道包含1000个扇区,则访问一个扇区的平均存取时间大约是()A.8.1ms B.12.2ms C.16.3ms D.20.5ms21.在采用中断I/O方式控制打印输出的情况下,CPU和打印控制接口中的I/O端口之间交换的信息不可能是()A.打印字符B.主存地址C.设备状态D.控制命令22.内部异常(内中断)可分为故障(fault)、陷阱(trap)和终止(abort)三类。

《微机原理与接口技术》在线测试题

《微机原理与接口技术》在线测试题、单选题(共40 道试题,共80 分。

)1. 微机总线的位数指的是()的位数。

A. 地址线B. 控制线C. 数据线D. 并行线满分:2 分2. 在8086宏汇编过程中不会产生指令码,只用来指示汇编程序如何汇编的指令是()A. 汇编指令B. 伪指令C. 机器指令D. 宏指令满分:2 分3. INT 8259中断屏蔽寄存储器的作用是( ).A. 禁止CPU响应外设的中断请求B. 禁止外设向CPU发中断请求C. 禁止软中断请求D. 禁止NMI中断请求满分:2 分4. CPU执行OUT DX,AL指令时,()的值输出到地址总线上。

A. AL寄存器B. AX寄存器C. DL寄存器D. DX寄存器满分:2 分5. 当存储器读写速度较慢时,需产生一个READY信号以实现与CPU的同步,CPU将在总线周期的时候采样该信号。

()A. T2下降沿B. T3下降沿C. T2上升沿D. T3上升沿满分:2 分6. CPU响应可屏蔽中断请求时,其中断向量号由()提供A. CPU内部B. 中断指令C. 向量号固定D. 中断控制器满分:2 分7. 对于开关型设备的控制,适合采用的I/O传送方式是( )A. 无条件B. 查询C. 中断D. DMA满分:2 分8. 设x=-46,y=117,则[x-y]补和[x+y]补分别等于。

()A. D2H和75HB. 5DH和47HC. 2EH和7lHD. 47H和71H满分:2 分9. 中断控制器8259A所管理的是()A. 指令中断B. 非屏蔽中断C. 可屏蔽中断D. 单步中断满分:2 分10. 执行下列程序后,(AL)=()。

MOV AL,92H SUBAL,7lH DASA. 21B. 11C. 21HD. 11H满分:2 分11. 8086CPU在执行MOV AL,[BX]指令的总线周期内,若BX存放的内容为1011H,则和A0的状态是。

()A. 0,0B. 0,1C. 1,0D. 1,1满分:2 分12. 8086CPU通过M/控制线来区分是存储器访问,还是I/O访问,当CPU执行INAL,DX 指令时,该信号线为()电平。

【真题】2015上交820微机原理真题

更多最新考研咨询关注微信公众号 renrenkaoyan

【真题】2015上交820微机原理真题

第二题简答题5个,一个8分。

1)程序执行的时间是否是各指令执行时间之和

2)LENGTH和SIZE的返回值的规定

3)为什么Cache能降低CPU对存储器速度要求,不降低存储器性能

4)为什么要外设和主机系统相连要接口电路

5)建一个中断向量

第三题程序题2个,1个10分。

1)读程序题,程序给出,要求写出功能和结果,是一个将BX里数据按16位二进制形式输出的程序

2)填程序题,是一个把GROUP1和GROUP数组求和并存放的程序

第四题考8253,20分。

初始化程序给出

1)写出通道0-2的方式和初值

2)画出OUT0-OUT2的波形,并标出周期

第五题考存储器,20分。

给了一个存储器连接图

1)写出单个存储器和整个系统的容量

2)写出各存储器的地址

3)什么选址方式,有没有地址重复

第六题考8255和键盘,30分。

给了一个8255、矩阵键盘和一位数码管(BCD输出,1110显示E)

1)写出8255的各口地址

2)写程序,要求矩阵键盘按下,数码管显示所表示的数字

更多最新考研资讯请扫描上方二维码

爱考机构 中国保过保录高端考研第一品牌! 每年每校每专业限招1‐3人 报名电话010‐51283340 QQ:744569778。