1.2 kV Trench Insulated Gate Bipolar Transistors (IGBT’s) with Ultralow On-Resistance

变频器AFE培训教程

西门子变频器简介3

MASTERDRIVES装置可以做成以下形式产品: 接到交流三相电网上的变频器, 接到直流母线上的逆变器, 向直流母线提供电源的整流单元。 多种系统元件和附件扩展了产品的应用范围。 顶驱电控系统因功率较大故采用整流单元+逆变器结构。

Compact PLUS 紧凑加强型

Compact 紧凑型

Isolated Supplies

Control Boards

Power Section

Vector and PWM Processor

IGBT(Insulated Gate Bipolar Transistors)

电 压

电 流

一 毫 秒

开 关 损 耗

开 关

IGBTs 是 可 靠 ,高 效 和 快 速 的 电 力 电 子器 件

08

整流单元的组成

整流单元结构图

单 相 相 整流示意图

DC 电 压

相

输 入 电 压

单 相

整 流 二 极 管

极 管 电 流

逆变模块(IGBT)

01

散热板

02

触发电路板(IGD)

03

控制电源板(PSU)

04

主控板(CUVC)

05

主回路保险(熔芯)

06

中间回路电容.

07

散热风机

SIMOVERT MASTERDRIVES矢量控制系列变频器是全系列通用型和模块化的产品: 标准装置功率范围从0.55 kW~ 2300 kW。 覆盖全球的三相交流电网电压,380 V~ 690 V。 按照使用场合及所需功率,可做成4种结构,即增强书 本型、书本型、装机装柜型及变频调速柜。 模块化的硬件、软件使其能够达到精确配合、最经 济的解决方案。

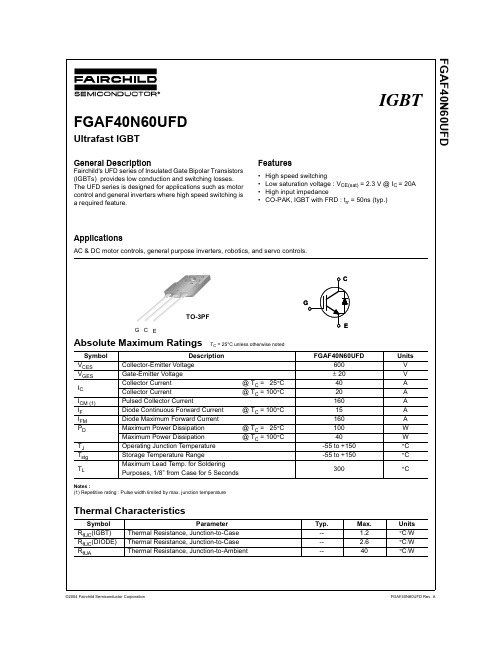

FGAF40N60UFD中文资料

Electrical Characteristics of DIODE TC = 25°C unless otherwise notedI GES G-E Leakage Current V GE = V GES, V CE = 0V ----± 100nAOn CharacteristicsV GE(th)G-E Threshold Voltage I C = 20mA, V CE = V GE 3.5 5.1 6.5VV CE(sat)Collector to EmitterSaturation VoltageI C = 20A, V GE = 15V-- 2.3 3.0VI C = 40A, V GE = 15V-- 3.1--VDynamic CharacteristicsC ies Input CapacitanceV CE = 30V, V GE = 0V,f = 1MHz --1075--pFC oes Output Capacitance--170--pF C res Reverse Transfer Capacitance--50--pFSwitching Characteristicst d(on)Turn-On Delay TimeV CC = 300 V, I C = 20A,R G = 10Ω, V GE = 15V,Inductive Load, T C = 25°C --15--nst r Rise Time--30--ns t d(off)Turn-Off Delay Time--65130ns t f Fall Time--35100ns E on Turn-On Switching Loss--470--uJ E off Turn-Off Switching Loss--130--uJ E ts TotalSwitchingLoss--6001000uJt d(on)Turn-On Delay TimeV CC = 300 V, I C = 20A,R G = 10Ω, V GE = 15V,Inductive Load, T C = 125°C --30--nst r Rise Time--37--ns t d(off)Turn-Off Delay Time--110200ns t f Fall Time--80250ns E on Turn-On Switching Loss--500--uJ E off Turn-Off Switching Loss--310--uJ E ts TotalSwitchingLoss--8101200uJQ g Total Gate ChargeV CE = 300 V, I C = 20A,V GE = 15V --77150nCQ ge Gate-Emitter Charge--2030nC Q gc Gate-Collector Charge--2540nC L e Internal Emitter Inductance Measured 5mm from PKG--14--nHSymbol Parameter Test Conditions Min.Typ.Max.UnitsV FM Diode Forward Voltage I F = 15A T C = 25°C-- 1.4 1.7V T C = 100°C-- 1.3--t rr Diode Reverse Recovery TimeI F = 15A,di/dt = 200A/us T C = 25°C--5095ns T C = 100°C--74--I rr Diode Peak Reverse RecoveryCurrentT C = 25°C-- 4.5 6.0AT C = 100°C-- 6.5--Q rr Diode Reverse Recovery Charge T C = 25°C--80180nC T C = 100°C--220--DISCLAIMERFAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN;NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.As used herein:1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body,or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.PRODUCT STATUS DEFINITIONS Definition of TermsDatasheet Identification Product Status DefinitionAdvance InformationFormative or In Design This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.PreliminaryFirst ProductionThis datasheet contains preliminary data, andsupplementary data will be published at a later date.Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.No Identification Needed Full ProductionThis datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.Obsolete Not In ProductionThis datasheet contains specifications on a product that has been discontinued by Fairchild semiconductor.The datasheet is printed for reference information only.TRADEMARKSThe following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.FACT Quiet Series™FAST ®FASTr™FPS™FRFET™GlobalOptoisolator™GTO™HiSeC™I 2C™ImpliedDisconnect™ISOPLANAR™LittleFET™MICROCOUPLER™MicroFET™MicroPak™MICROWIRE™MSX™MSXPro™OCX™OCXPro™OPTOLOGIC ®OPTOPLANAR™PACMAN™POP™Power247™PowerSaver™PowerTrench ®QFET ®QS™QT Optoelectronics™Quiet Series™RapidConfigure™RapidConnect™SILENT SWITCHER ®SMART START™SPM™Stealth™SuperFET™SuperSOT™-3SuperSOT™-6SuperSOT™-8SyncFET™TinyLogic ®TINYOPTO™TruTranslation™UHC™UltraFET ®VCX™ACEx™ActiveArray™Bottomless™CoolFET™CROSSVOLT ™DOME™EcoSPARK™E2CMOS™EnSigna™FACT™Across the board. Around the world.™The Power Franchise™Programmable Active Droop™。

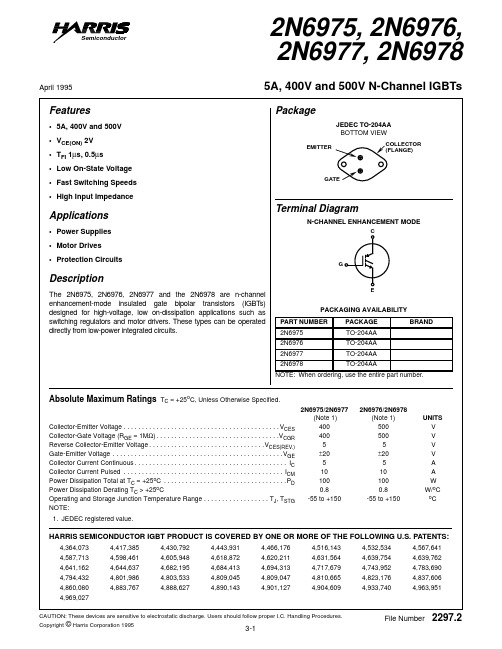

2N6975中文资料

HARRIS SEMICONDUCTOR IGBT PRODUCT IS COVERED BY ONE OR MORE OF THE FOLLOWING U.S. PATENTS:

4,364,073 4,587,713 4,641,162 4,794,432 4,860,080 4,969,027

2N6975/2N6977 (Note 1) 400 400 5 ±20 5 10 100 0.8

-55 to +150

1. JEDEC registered value.

2N6976/2N6978 (Note 1) 500 500 5 ±20 5 10 100 0.8

-55 to +150

UNITS V V V V A A W

ICE, COLLECTOR CURRENT (A)

10 PULSE TEST, VCE = 10V PULSE DURATION = 80µs

DUTY CYCLE = 0.5% MAX

7.5

5.0

+125oC

10 VGE = +10V VGE = +8V

EFFECTIVE TRANSIENT THERMAL IMPEDANCE (NORMALIZED)

ZθJC(t) = r(t)RθJC D CURVES APPLY FOR POWER PULSE

TRAIN SHOWN READ TIME AT t1 10 TJ(PEAK) - TC = P(PEAK)ZθJC(t)

Absolute Maximum Ratings TC = +25oC, Unless Otherwise Specified.

Collector-Emitter Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . VCES Collector-Gate Voltage (RGE = 1MΩ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .VCGR Reverse Collector-Emitter Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .VCES(REV.) Gate-Emitter Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .VGE Collector Current Continuous . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . IC Collector Current Pulsed . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ICM Power Dissipation Total at TC = +25oC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . PD Power Dissipation Derating TC > +25oC Operating and Storage Junction Temperature Range . . . . . . . . . . . . . . . . . . TJ, TSTG NOTE:

Zero-Voltage and Zero-Current-Switching Full-Bridge PWM Converter Using

Zero-V oltage and Zero-Current-Switching Full-Bridge PWM Converter UsingSecondary Active Clamp Jung-Goo Cho,Member,IEEE,Chang-Yong Jeong,and Fred C.Y.Lee,Fellow,IEEEAbstract—A new zero-voltage and zero-current-switching (ZVZCS)full-bridge(FB)pulsewidth modulation(PWM) converter is proposed to improve the performance of the previously presented ZVZCS FB PWM converters.By adding a secondary active clamp and controlling the clamp switch moderately,ZVS(for leading-leg switches)and ZCS(for lagging-leg switches)are achieved without adding any lossy components or the saturable reactor.Many advantages including simple circuit topology,high efficiency,and low cost make the new converter attractive for high-voltage and high-power(>10 kW)applications.The principle of operation is explained and analyzed.The features and design considerations of the new converter are also illustrated and verified on a1.8-kW100-kHz insulated gate bipolar transistor(IGBT)-based experimental circuit.Index Terms—DC–DC power conversion.I.I NTRODUCTIONI NSULATED gate bipolar transistors(IGBT’s)are widelyused in switching power conversion applications because of their distinctive advantages such as easiness in drive and high-frequency switching capability.The performance of IGBT’s has been continuously improved,and the latest IGBT’s can be operated at10–20kHz without including any snubber circuit. Moreover,IGBT’s are replacing MOSFET’s for the several or several tens of kilowatts power range applications since IGBT’s can handle higher voltage and power with higher power density and lower cost compared to MOSFET’s.The maximum operating frequency of IGBT’s,however,is limited to20–30kHz[1]because of their tail-current characteristic. To operate IGBT’s at high switching frequencies,it is required to reduce the turn-off switching loss.Zero-voltage switching (ZVS)with a substantial external snubber capacitor or zero-current switching(ZCS)can be a solution.The ZCS,however, is deemed more effective since the minority carrier is swept out before turning off[6].ZVS full-bridge(FB)pulsewidth modulation(PWM)con-verters have received considerable attention in recent years [2]–[5].This converter is controlled by a phase-shifted PWMManuscript received July18,1996;revised October14,1997.Recom-mended by Associate Editor,L.Xu.J.-G.Cho and C.-Y.Jeong are with the Power Electronics Research Division,Korea Electrotechnology Research Institute,Changwon641-120, Korea(e-mail:jgcho@keri.re.kr).F. C.Y.Lee is with the Virginia Power Electronics Center,Virginia Polytechnic Institute and State University,Blacksburg,V A24061USA. Publisher Item Identifier S0885-8993(98)04842-X.technique which enables the use of all parasitic elements in the bridge to provide ZVS conditions for the switches.Distinctive advantages including ZVS with no additional components, and low-device voltage/current stresses make it very attractive for high-frequency high-power applications,where MOSFET’s are predominantly used as the power switches.The IGBT’s, however,are not suited for the ZVS FB PWM converter because the ZVS range is quite limited unless the leakage inductance is very large.In addition,several demerits such as duty-cycle loss and parasitic ringing in the secondary limit the maximum power rating of the converter.To apply IGBT’s for a high-frequency converter,a ZVZCS FB PWM converter was presented[7].IGBT’s with no an-tiparallel diodes are used for all primary switches.During the freewheeling period,the primary current is reset by us-ing reverse avalanche-breakdown voltage of the leading-leg IGBT’s,which provides ZCS condition to lagging-leg IGBT’s. However,it has some drawbacks as follows.The stored energy in the leakage inductance is completely dissipated in the leading-leg IGBT’s.There is parasitic ringing in the primary during the freewheeling period.The maximum controllable duty cycle is limited since the reverse avalanche-breakdown voltage is low(15–30V)andfixed.Therefore,the overall efficiency will be deteriorated unless the leakage inductance is very low.Another approach for ZVZCS FB PWM converter was presented[8].By utilizing a dc blocking capacitor and adding a saturable inductor in the primary,the primary current during the freewheeling period is reset,which provides ZCS condi-tion to the lagging-leg switches.Meanwhile,the leading-leg switches are still operated with ZVS.The stored energy in the leakage inductance is recovered to the dc blocking capacitor andfinally transferred to the load.By increasing the blocking capacitor voltage(i.e.,by reducing the capacitance of the blocking capacitor),wide duty-cycle control range is attainable even when the leakage inductance is relatively large.This converter can be effectively applied to several kilowatts power range applications.Some demerits including loss in saturable inductor and its cooling problem hinder further increase of the power level above10kW.This paper proposes a novel ZVZCS FB PWM converter (see Fig.1)to improve the performance of the previously presented ZVZCS FB PWM converters[7],[8].The ZVS mechanism of leading-leg switches is the same as that of the converters[2]–[5],[8].The ZCS of lagging-leg switches,how-0885–8993/98$10.00©1998IEEEFig.1.Circuit topology of the proposed ZVZCS FB PWM converter.ever,is achieved by adding an active clamp in the secondaryrectifier and by controlling it moderately.No lossy componentsare added to achieve ZVZCS operation.The duty-cycle loss isalmost negligible although the leakage inductance is a little bitlarge since a high voltage(higher than input voltage)is appliedto the leakage inductance to reset the primary current duringfreewheeling period.So,the new converter overcomes mostof the limitations of the soft-switching FB PWM converters,which makes the new converter very attractive for high-voltage high-power((2)This mode ends when(3)CHO et al.:FULL-BRIDGE PWM CONVERTER USING SECONDARY ACTIVE CLAMP603Fig.3.Operation waveforms.C.Mode3According to the given dutycycle,,and.The rectifier voltage is still zero.This is the end ofan operating half cycle.III.F EATURES OF THE P ROPOSED C ONVERTERA.Effective Soft Switching(ZVZCS)Soft-switching mechanism(ZVS for leading-leg switchesand ZCS for lagging-leg switches)of the proposed converterhas exactly the same as those of the ZVZCS converterspresented in[7]and[8].The converters[7],[8]use lossycomponents to achieve ZCS of lagging-leg switches.Thestored energy in the leakage inductance is completely dissi-pated in the leading-leg IGBT’s during freewheeling mode[7]or there exists the core loss of saturable reactor[8].In addition,additional loss exists in the clamp resistor forboth converters if the passive clamp circuit is used to clampthe secondary rectifier voltage.Therefore,both convertershave limited power range(several kilowatts).In the proposedconverter,however,ZCS of lagging-leg switches is achievedmore efficiently by modifying control of the active clamp[3].No lossy components are involved in achieving ZCS,and noparasitic ringing is generated in the secondary rectifier.So,theproposed converter can handle a higher power level(duringfreewheeling period asfollows:604IEEE TRANSACTIONS ON POWER ELECTRONICS,VOL.13,NO.4,JULY1998(a)(b)(c)parison of the simplified waveforms of primary voltages and currents and secondary rectifier voltages.(a)ZVS PWM converter.(b)ZVZCS PWM converters [7],[8].(c)Proposed converter.is applied to the leakage inductance,which is a kind of duty-cycle loss.In the proposed ZVZCS converter,however,asmallis achieved since the high reversevoltage is applied to the leakage inductance.So,the overall efficiency of the proposed converter is improved due to low duty-cycleloss as well assmall .C.Duty-Cycle Boost EffectThe duty cycle of the secondary rectifier is usually lowerthan that of the primary because of the duty-cycle loss.In the proposed converter,however,the duty cycle of the rectifier can be higher than that of the primary as shown in Fig.5.This phenomenon is named as duty-cycle boost effect .The duty-cycle boost effect is caused by the operation of the active clamp from the beginning of freewheeling period to provide ZCS condition to the lagging-leg switches.This means that the stored energy in the leakage inductance is recovered to the clamp capacitor and finally transferred to the load by means of the duty-cycle boost effect.This feature is very important for the ZVZCS converters,which use IGBT’s for main switches.The duty cycle of the primary is more limited than MOSFET-based ZVS converters since the minimum dead time((6)whereis determined directly by the turn-on time of the clamp switch.The duty-cycle boost effect also helps to improve the overall efficiency.IV.D ESIGN C ONSIDERATIONSA.Decision of Dead TimesAn appropriate dead time is required for both leading-and lagging-leg switches to achieve maximum performance.1)Dead Time for Leading-Leg Switches:The dead time for leading-leg switches is determined by two factors—the ZVS range and maximum duty cycle of the primary side.The minimum dead time is determined by ZVS range asfollows:(8)wheretheCHO et al.:FULL-BRIDGE PWM CONVERTER USING SECONDARY ACTIVE CLAMP605Fig.6.Illustrative waveforms of the rectifier voltage and the clamp capacitorcurrent.Fig.7.Circuit diagram of the active clamp circuit for a center-tappedtransformer.required turn-on time ofs.The primary current isquickly reset right after the primary voltage is dropped to zeroand sustained during the freewheeling period.The primary cur-rent reset time is only0.15606IEEE TRANSACTIONS ON POWER ELECTRONICS,VOL.13,NO.4,JULY1998(a)(b)Fig.10.Extended waveforms at (a)leading-leg and (b)lagging-leg switchingtransitions.(a)(b)Fig.11.Extended ZVS switching waveforms of leading-leg switches:(a)turn on and (b)turnoff.Fig.12.Extended ZCS waveforms of lagging-leg switches.waveforms of leading-leg switches.It can be seen that the antiparallel diode current flows for a short time and stays zero,and,thus,a complete ZVS turn on is achieved.The tail current is seen,but the turn-off switching loss is remarkably reduced comparing to hard switching since the rising slope of the switch voltage is slow.The ZVS range for the leading-leg switches is about 20%of full load.Fig.12shows theextended Fig.13.Waveforms of secondary active clamp.switching waveforms of lagging-leg switches.It can be seen that a complete ZCS turn off is achieved since the primary current is zero during the whole freewheeling period and the turn-on process of the other switch is almost ZCS.Small pulse current during turn-on transition is the charging current of the switch output capacitor.Fig.13shows the waveforms of the secondary active clamp.The clamp switch is turned on for aCHO et al.:FULL-BRIDGE PWM CONVERTER USING SECONDARY ACTIVE CLAMP607Fig.14.Measured efficiencies.very short time compared to the operating period(7%).The rectifier voltage waveform is a little noisy since the clamp switch operates under hard switching.The clamp capacitor current waveform is the same as the expected.Fig.14shows the measured efficiencies of the proposed ZVZCS FB PWM converter.The maximum overall efficiency is about94%at full load.The efficiency improvement is not much comparing to the previous ZVZCS converter[8],but it will be considerable at higher power(10kW)applications with high-power density.R EFERENCES[1]IGBT Designer’s Manual,International Rectifier,El Segundo,CA,1994.[2]J.A.Sabate,V.Vlatkovic,R.B.Ridley,F.C.Lee,and B.H.Cho,“Design considerations for high-voltage high-power full-bridge zero-voltage-switched PWM converter,”in IEEE APEC Rec.,1990,pp.275–284.[3],“High voltage high power ZVS full bridge PWM converteremploying active snubber,”in IEEE APEC Rec.,1991,pp.158–163.[4]R.Redl,N.O.Sokal,and L.Balogh,“A novel soft switching fullbridge dc/dc converter:Analysis,design considerations,and experi-mental results at1.5kW,100kHz,”in IEEE PESC Rec.,1990,pp.162–172.[5] A.W.Lotfi,Q.Chen,and F.C.Lee,“A nonlinear optimization tool forthe full bridge zero-voltage-switched PWM dc/dc converter,”in IEEE APEC Rec.,1992,pp.1301–1309.[6]G.Hua,E.X.Yang,Y.Jiang,and F.C.Lee,“Novel zero-current-transition PWM converters,”in IEEE PESC Rec.,1993,pp.538–544.[7]K.Chen and T.A.Stuart,“1.6kW,110kHz dc/dc converter optimizedfor IGBT’s,”IEEE Trans.Power Electron.,vol.8,no.1,pp.18–25, 1993.[8]J.G.Cho,J.Sabate,G.Hua,and F. C.Lee,“Zero voltage andzero current switching full bridge PWM converter for high power applications,”in IEEE PESC Rec.,1994,pp.102–108.Jung-Goo Cho(S’89–M’91)received the M.S.andPh.D.degrees in electrical engineering from theKorea Advanced Institute of Science and Technol-ogy(KAIST),Daejon,Korea,in1988and1992,respectively.Since1992,he has been with KAIST for one anda half years as a Post-Doctoral Fellow,where heparticipated in the development of a1-MV A mul-tilevel GTO inverter for an induction motor drive.From1993to1994,he was with the Virginia PowerElectronics Center(VPEC),Virginia Polytechnic Institute and State University,as a Visiting Research Scientist,where he studied soft-switching PWM converters and power-factor-correction circuits. Since1995,he has been with the Power Electronics Research Division, Korea Electrotechnology Research Institute(KERI),Changwon,Korea,as a Senior Researcher.His primary areas of research interests include:soft-switching converters,power-factor-correction circuits,high-power multilevel GTO inverters,high-voltage pulse power supplies,activefilters,and FACTS. Dr.Cho is a Member of KIEE andKITE.Chang-Yong Jeong received the B.S.degree fromKyungpook National University,Taegu,Korea,in1993and the M.S.degree in electrical engineeringfrom the Korea Advanced Institute of Science andTechnology(KAIST),Daejon,Korea,in1995.Since1995,he has been with the Power Elec-tronics Research Division,Korea ElectrotechnologyResearch Institute(KERI),Changwon,Korea,as aResearcher.His primary areas of research interestsinclude:activefilters,FACTS and applications ofhigh-power inverters,power circuit modeling,and data-acquisitionsystems.Fred C.Y.Lee(S’72–M’74–SM’87–F’90)receivedthe B.S.degree in electrical engineering from theNational Cheng Kung University,Taiwan,in1968and the M.S.and Ph.D.degrees from Duke Univer-sity,Durham,NC,in1971and1974,respectively.He is the Lewis A.Hester Chair of Engineering atVirginia Polytechnic Institute and State University,Blacksburg,and was the James S.Tucker EndowedProfessor at the Bradley Department of ElectricalEngineering at Virginia Polytechnic Institute andState University.He is the Founder and Director of the Virginia Power Electronics Center(VPEC),a Technology Development Center of Virginia’s Center for Innovative Technology(CIT).Under his leadership,VPEC has become one of the largest university-based power electronics research centers in the country.The Center’s Industry Partnership Program has enrolled more than70companies from around the world.His research interests include:high-frequency power conversion,distributed power systems,space power systems,device characterization,and modeling and control of converters and design optimization.During his career,he has published over100refereed journal papers,more than200technical papers in national and international conferences,and over150industry and government reports.He currently holds19U.S.patents.Dr.Lee is a recipient of the1985Ralph R.Teeter Educational Award of the Society of Automotive Engineering,the1989William E.Newell Power Electronics Award of the IEEE Power Electronics Society,the1990PCIM Award for Leadership in Power Electronics Education,and the1990Virginia Tech Alumni Award for Research Excellence.He is a Past President of the Power Electronics Society.。

SGH80N60UFD中文资料

Electrical Characteristics of DIODE TC = 25°C unless otherwise notedCES CE CES GEI GES G-E Leakage Current V GE = V GES, V CE = 0V ----± 100nAOn CharacteristicsV GE(th)G-E Threshold Voltage I C = 40mA, V CE = V GE 3.5 4.5 6.5VV CE(sat)Collector to EmitterSaturation VoltageI C = 40A, V GE = 15V-- 2.1 2.6VI C = 80A, V GE = 15V-- 2.6--VDynamic CharacteristicsC ies Input CapacitanceV CE = 30V, V GE = 0V,f = 1MHz --2790--pFC oes Output Capacitance--350--pF C res Reverse Transfer Capacitance--100--pFSwitching Characteristicst d(on)Turn-On Delay TimeV CC = 300 V, I C = 40A,R G = 5Ω, V GE = 15V,Inductive Load, T C = 25°C --23--nst r Rise Time--50--ns t d(off)Turn-Off Delay Time--90130ns t f Fall Time--50150ns E on Turn-On Switching Loss--570--uJ E off Turn-Off Switching Loss--590--uJ E ts TotalSwitchingLoss--11601500uJt d(on)Turn-On Delay TimeV CC = 300 V, I C = 40A,R G = 5Ω, V GE = 15V,Inductive Load, T C = 125°C --30--nst r Rise Time--55--ns t d(off)Turn-Off Delay Time--150200ns t f Fall Time--160250ns E on Turn-On Switching Loss--630--uJ E off Turn-Off Switching Loss--940--uJ E ts TotalSwitchingLoss--15802000uJQ g Total Gate ChargeV CE = 300 V, I C = 40A,V GE = 15V --175250nCQ ge Gate-Emitter Charge--2540nC Q gc Gate-Collector Charge--6090nC L e Internal Emitter Inductance Measured 5mm from PKG--14--nHSymbol Parameter Test Conditions Min.Typ.Max.UnitsV FM Diode Forward Voltage I F = 25A T C = 25°C-- 1.4 1.7V T C = 100°C-- 1.3--t rr Diode Reverse Recovery TimeI F = 25A,di/dt = 200A/us T C = 25°C--5095ns T C = 100°C--105--I rr Diode Peak Reverse RecoveryCurrentT C = 25°C-- 4.510AT C = 100°C--8.5--Q rr Diode Reverse Recovery Charge T C = 25°C--112375nC T C = 100°C--420--DISCLAIMERFAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY , FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.TRADEMARKSThe following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.LIFE SUPPORT POLICYFAIRCHILD S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORTDEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.As used herein:1. Life support devices or systems are devices orsystems which, (a) are intended for surgical implant intothe body, or (b) support or sustain life, or (c) whosefailure to perform when properly used in accordancewith instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.PRODUCT STATUS DEFINITIONS Definition of Terms Datasheet Identification Product Status DefinitionAdvance InformationPreliminaryNo Identification Needed Obsolete This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.This datasheet contains preliminary data, andsupplementary data will be published at a later date.Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.This datasheet contains specifications on a product that has been discontinued by Fairchild semiconductor.The datasheet is printed for reference information only.Formative or In Design First ProductionFull ProductionNot In ProductionImpliedDisconnect ISOPLANARLittleFETMicroFETMicroPakMICROWIREMSXMSXProOCXOCXProOPTOLOGIC âOPTOPLANARFACT FACT Quiet Series FAST âFASTr FRFET GlobalOptoisolator GTO HiSeCI 2CRev. I1ACEx ActiveArray Bottomless CoolFET CROSSVOLT DOME EcoSPARK E 2CMOS TM EnSigna TMPACMANPOP Power247 PowerTrench âQFET QS QT Optoelectronics Quiet Series RapidConfigure RapidConnect SILENT SWITCHER âSMART START SPMStealthSuperSOT -3SuperSOT -6SuperSOT -8SyncFET TinyLogic TruTranslation UHC UltraFET âVCXAcross the board. Around the world. The Power FranchiseProgrammable Active Droop。

变频器AFE培训教程

D Type

Serial i/o

Control Boards

Power Section

Siemens Factory Automation Engineering Ltd.

P 18 of 202

IGBT(Insulated Gate Bipolar Transistors)

电压

电流

开关损耗

开

关

一毫秒

Siemens Factory Automation Engineering Ltd.

P 9 of 202

力矩性能

Voltage Torque

0

0.5

1.0 1.2

1.5

Frequency

P 10 of 202

Siemens Factory Automation Engineering Ltd.

调速结论1

三相

Siemens Factory Automation Engineering Ltd.

P 26 of 202

逆变器的组成

•逆变模块(IGBT) •散热板 •触发电路板(IGD) •控制电源板(PSU) •主控板(CUVC) •主回路保险(熔芯) •中间回路电容. •散热风机 •显示面板(PMU) •接口转换板(IVI) •通讯板(CBP2)

Siemens Factory Automation Engineering Ltd.

P 24 of 202

整流单元结构图

Siemens Factory Automation Engineering Ltd.

P 25 of 202

整流示意图

整流二 极管

输入电 压

DC 电 压

二极管电 流

单相

SVPWM仿真与分析论文

1INTRODUCTIONPermanent magnet linear synchronous motor (PMLSM)is a kind of driving equipment for converting electrical energy into linear movement directly without any in-between transferring mechanism [1].Without the need of any mechanical transformation by using for example gears and screws,the linear drive offers high efficiency,high reliability,high performance motion control and low vibration and noise [2].PMLSM s are increasingly used as actuators in many automation control fields,including computer controlled machining tools,X-Y driving devices,robots,semiconductor manufacturing equipment,transport propulsion and levitation,and high-speed injection molding machines [3].The control performance of the PMLSM is sensitive to its load disturbance,friction variation,and end effect.Thus,it is important to adopt a proper control strategy to achieve satisfied servo performance.Digital control techniques of AC motors,such as the space vector pulse width modulation (SVPWM),have been developed with wide range industrial applications.The SVPWM was brought forward from 1980’s,specifically used for the frequency varying and speed regulation of AC motors.It controls the motor based on the switching of space voltage vectors,by which an approximate circular rotary magnetic field is paring with the sine pulse width modulation (SPWM),the main SVPWM advantage is that it has e.g.a 15%higher utilization ratio of voltage [4].In addition,SVPWM can improve the quality of the stator currents and reduce the harmonic wave generation.Consequently,SVPWM is adopted as the servo control strategy for the PMLSM in this paper and its simulation model is built in Matlab/Simulink.Two substantial simulation results are presented in this paper.One is under open-loop control system basedThis work is supported by the Chinese High-Tech Development Program (863),Project No.2007AA03Z208.SVPWM,and the control effectiveness of it is analyzed.The other is field-oriented vector control (VC)based close-loop control system,and the position-tracking control algorithm is proposed and simulated.Analytical results are obtained andpresented with comparison.2MODEL OF PMLSM2.1Coordinate transformationsPMLSM is a nonlinear and strong coupling system.Coordinate transformation can simplify the mathematic model of PMLSM.The typical mathematical model of PMLSM is described in two-axis d-q synchronous rotating reference frame.In d-q frame,if the current in the direction of d-axis can be set zero,then controlling the thrust force of PMLSM is the only need to control the current in the direction of q-axis.So the coordinate transformation is very important to decouple the nonlinear of PMLSM.The following shows transformation formulas among the stationary a-b-c frame,the stationary α-βframe and the synchronously rotating d-q frame,where V represents a space vector i.e.current,voltage or magnet flux linkage.(1)Clark transformation:stationary a-b-c frame tostationary α-βframe11122022a bc VV V V V αβ−−=−⎤⎡⎤⎥⎡⎤⎢⎥⎢⎥⎢⎥⎣⎦⎢⎥⎣⎦⎣⎦(1)(2)Clark -1transformation:stationary α-βframe tostationary a-b-c frameSimulation and Analysis of a PMLSM Control System Based on SVPWMJIN Jianxun 1,ZHAO Huibin 1,XIN Ying 2, SUN Yuwei 21.Center of Applied Superconductivity and Electrical Engineering,University of Electronic Science and Technology of China,Chengdu 61173,P.R.ChinaE-mail: jxjin@2.Innopower Superconductor Cable Co.,Ltd,Beijing ,P.R.ChinaE-mail:yingxin@Abstract:This paper aims to develop a permanent magnet synchronous motor (PMLSM)control system based on space vector pulse width modulation (SVPWM)and analyzes its control effectiveness.Mathematical simulation models of PMLSM and SVPWM are firstly presented and established in Matlab/Simulink.An open-loop simulating control system and a field-oriented vector control (VC)based close-loop system are then built,and their control effectiveness is analyzed.To overcome the shortages of great overshooting and poor dynamic response of the traditional VC and improve the precision of position,a position-tracking control strategy is proposed and simulated.Analytica l results indicate that the proposed strategy can improve the stability and precision of the PMLSM control system.Key Words:PMLSM,SVPWM,Matlab/Simulink,Vector control,SimulationProceedings of the 29th Chinese Control Conference July 29-31, 2010, Beijing, China10122122abcVVVVVαβ−=−−⎡⎤⎥⎡⎤⎥⎡⎤⎢⎥⎥⎢⎥⎢⎥⎣⎦⎢⎥⎣⎦⎢⎢⎣(2)(3)Park transformation:stationaryα-βframe tosynchronously rotating d-q framecos sinsin cosdqV VV Vαβθθθθ=−⎡⎤⎡⎤⎡⎤⎢⎥⎢⎥⎢⎥⎣⎦⎣⎦⎣⎦(3)(4)Park-1transformation:synchronously rotating d-qframe to stationaryα-βframecos sinsin cosdqVVVVαβθθθθ−=⎡⎤⎡⎤⎡⎤⎢⎥⎢⎥⎢⎥⎣⎦⎣⎦⎣⎦(4)2.2Mathematical model of PMLSMThere are a few hypotheses in the process of mathematicsmodel foundation.The iron core saturation is neglected,andthe losses of eddy currents,hysteresis and end effect aren’ttaken into account.The typical mathematical model of aPMLSM is commonly described in two-axis d-qsynchronous rotating reference frame[5],as follows.Stator voltage balance equation is given bydd d d q qdiu Ri L vL idtπτ=+−(5)()qq q q d d fdiu Ri L L i vdtπϕτ=+++(6)The electromagnetic thrust force is given by3[()]2em f d q d qF L L i iπψτ=+−(7)If i d=0,electromagnetic thrust force would be expressed as32em f q p qF i K iπτ==(8)Therefore the thrust force of PMLSM can be controlled justthrough the controlling of i q which is very like controlling aDC motor.Considering the mechanical load,the dynamic positionmovement mechanical balance equation of PMLSM is givenbyem ddvF F Bv Mdt=++(9)whereψf,F d,B, M,v, R,τare the flux linkage of permanentmagnet,external force,viscous friction coefficient,mass ofmoving part,translator velocity,phase winding resistance,pole pitch.The simulation model of PMLSM can be built inMatlab/Simulink according to its mathematic model andcoordinate transformation as shown in Figure 1.It iscombined with“Voltage balance”subsystem and“Mechanical balance”subsystem as shown in Figure2andFigure3.Fig.1Model of PMLSMFig.2Model of voltage balance equation in MatlabFig.3Model of mechanical balance and electromagnetic thrustforce calculation in Matlab3MODEL OF SVPWM3.1Principle of SVPWMThe reference stator voltage space vector for PMLSM U ref can be defined as242332()3j j j ftref a b c ref U U U eU eU eπππ=++=(10)Fig.4Space vector diagramThe three-phase voltage source inverter has six electronic switches e.g.IGBTs (Insulated gate bipolar transistors)and eight working states,which topology structure has eight voltage vectors shown in Figure 4.According to compound voltage vector and voltage s econd balance principle,stator voltage vector U ref in any switch period can be calculated by two basic adjacent voltages vectors corresponding to two switch modes of the IGBT as shown in Figure 517017sksk ref sk sk T T T T U U U U U T T T T++=+++(11)where T is switch period,T sk and T sk+1are operating time of U sk and U sk+1respectively,T 0and T 7are operating time of U 0and U 7.Fig.5Voltage space vectors linear combination3.2Simulating model of SVPWM built in MatlabSimulink According reference [6],the flow chart of building the model of SVPWM is shown in Figure 6.The simulation model of SVPWM in Matlab/Simulink is shown in Figure 7.It combined with four subsystems:“section calculate”subsystem,“operating time”subsystem,“PWM generate”subsystem and “inverter”subsystem.The output of inverter is given by formula (12).S a ,S b ,and S c represent the states of six IGBT switches in inverter21111213112a b d c a b c U S U S U S V −−=−−−−⎡⎤⎡⎤⎡⎤⎢⎥⎢⎥⎢⎥⎢⎥⎢⎥⎢⎥⎣⎦⎣⎦⎣⎦(12)Fig.6Flow chart of building the model of SVPWMSection calculateFig.7Simulation model of SVPWM4SIMULATION AND ANALYSIS OFOPEN-LOOP CONTROLFig.8:Simulating model of open-loop control systemThe simulating model of open-loop control system of PMLSM is shown in Figure 8.Parameters of the designed PMLSM are:M =10kg,R =10Ω,B =0.1,τ=10mm,L d =L q =10mH,Ψf =0.5Wb,F d =50N.Three-phase voltage signal with amplitude of 50V and frequency of 10Hz is added to Clark transformation model.The PWM period or called switch period T s of SVPWM is 0.001s,and the DC bus voltage V dc of inverter is 500V.Fig.9Simulation result of PMLSMU skU sk+1U refU sk T sk /TU sk T sk+1/TAs shown in Figure 9,the stabilized velocity 0.2m/s is same as the result calculated by formula (13).The displacement curve is the integration of velocity2v f τ=(13)where f is the PMLSM frequency of phase voltage.But the electromagnet thrust force curve in Figure 9is not a constant.The average of electromagnet thrust force is 50N,and some time F >0,some time F <0.When F >0,work of electromagnet thrust force is positive,when F <0,work is negative.The mechanical efficiency can be derived as follows.Assume the mass of moving part is m ,electromagnet thrust force is F ,and external force is f()()()1122223333400&&00&&0F f t t t F F f F t t t F f F t t t −><<=−<><<−<<<<⎧⎪⎨⎪⎩(14)The velocity of rotor is as234123312t t t t t tF F F v dt dt Cm m m=++=∫∫∫(15)Power of electromagnet thrust force is as112223334))0(0(0()W t t t W W t t t W t t t ><<=><<<<<⎧⎪⎨⎪⎩(16)212312fW W W mv W ++=+(17)where W f is the power to overcome the friction.Whether the work of electromagnet thrust force is positive or negative,the energy of motor will be consumed equally.The total energy consumed can be expressed as123'||||||W W W W =++(18)Naturally the mechanical efficiency ηis derived from (17)and (18)123123||||||W W W W W W η++=++(19)The remaining energy is converted to heat Q'(1)Q W η=−(20)So it is necessary to design a better control system to reduce the heat generating and increase η.The key to resolve the problem includes the stability of electromagnet thrust force and quick respond to velocity.So the close-loop control system need s to be established.5DESIGN AND ANALYSIS OF CLOSE-LOOP CONTROL SYSTEM BASED ON VCThe field-oriented vector control (VC)was firstly presented in 1971for induction motors and later for permanent magnet synchronous motors (PMSM)[7].According to formula (7)and (8),electromagnet thrust force is decided only by i q if i d =0.The velocity can be adjusted by thrust force according to formula (9),and the displacement is the integration of velocity,so the position can be controlled as well.That is the three-close-loop VC control strategy which is shown in Figure11.Fig.10Position step respondCurrently,the proportional-integral-derivative (PID)algorithm is the most common control algorithm used in industry.This paper use PID algorithm and position trajectory algorithm to realize accurate position control.The parameters of PIDs are listed in Table 1.If there is no trajectory plan before position loop,the position control can’t achieve a good result,greater overshoot and error will be generated as the Figure 10shown.The trajectory plan module is to realize trapezoid curve movement.Assume P s ,P f and X p is the setting position,feedback position and command position correspondingly;a cc ,and A cc is the setting acceleration and commanding acceleration.All variable are positive by default.The algorithm is as follows , a nd the simulated result is shown in Figure 12.When 13f sP P ≤then A cc = a cc ;when1233f sP P <≤thenA cc =0;when213f sP P <≤then A cc =-a cc ;s cc P A dt =∫∫and P s X pTab.1:Parameters of PID controllersT c :Time constant for derivatives;T s :Sample timeParameters K p K i K d T c (s)T s (s)Position loop PID 300100.10.5e-21e-4Speed loop PID 20020.10.5e-21e-5I q loop PID 2000.50.050.5e-31e-5I d loop PID15010.030.5e-31e-5Fig.11:Three-closed-loop control system with trajectory planFig.12:Simulation result of trajectory plan position controlComparing with Figure 10and Figure 12,the trajectory plan position control can control the velocity curve and decrease the displacement error,and the thrust force has little fluctuation which is often positive.Therefore trajectory control can improve the stabilization of the system and increase the mechanical efficiency according to the formula (19).6CONCLUSIONSimulation models of PMLSM and SVPWM are established in Matlab/Simulink.The analytical and experimental results indicate that the model is accurate and practicable.The open-loop control system of PMLSM is presented and established,and the simulation result indicates that the open-loop control system can’t reach the aim of high accurate position control and the mechanical efficiency is lower.Consequently the close-loop control system is introduced.Field-oriented vector control system can improve the position precision,but its overshootingphenomena can’t be eliminated and the velocity of moving part is volatile.So it need to add a trajectory plan module before position loop to set the displacement track which make the velocity curve trapezoid as shown by the velocity curve in Figure 12.The experiment results indicate that the proposed position-tracking control strategy can decrease the overshooting effect and improve the precision of position.REFERENCES[1]H.B.Zhao,J. X.Jin,and J.Cheng. Virtual instrument basedfuzzy control system for PMLSM drive.Chengdu:Proceeding of IEEE on Applied Superconductivity and Electromagnetic Devices,2009:299-303.[2]Y.G.Guo,J.X.Jin,J.G.Zhu,and H.Y.Lu.Design andanalysis of a prototype linear motor driving system for HTS maglev transportation,IEEE Trans.App.Super.,2007,17(2),2087-2090.[3]Y.S.Kung,M.H.Tsai,C.S.Chen.FPGA-based servocontrol IC for PMLSM drives with adaptive fuzzy control.Korea:SICE-ICASE International joint conference 2006,2006:1-6.[4]Z.G.Wang,J.X.Jin,Y.G.Guo,and J.G.Zhu.SVPWMtechniques and applications in HTS PMSM machines control,Journal of Electronic Science and Technology of China,2008,6(2),191-197.[5]L. H.Zheng,and J. X.Jin.Investigation of HTS bulk magnetlinear synchronous motors.Chengdu:Proceeding of IEEE on Applied Superconductivity and Electromagnetic Devices,2009:17-21.[6]J.X.Jin,and L.H.Zheng.A permanent magnet linearsynchronous motor control system based on space vector pulse width modulation,CAAI Transactions on Intelligent Systems,2009,4(3),251-257.[7]L.Zhong,M.F.Rarman,W.Y.Hu,et al.Analysis of directtorque control in permanent magnet synchronous motor drives,IEEE Transactions on Power Electronics,1997,12(3),528-536.。

IRGP20B120UD-E中文资料

TO-247AD

Absolute Maximum Ratings

Parameter

VCES IC @ TC = 25°C IC @ TC = 100°C ICM ILM IF @ TC = 100°C IFM VGE PD @ TC = 25°C PD @ TC = 100°C TJ TSTG Collector-to-Emitter Breakdown Voltage Continuous Collector Current (Fig.1) Continuous Collector Current (Fig.1) Pulsed Collector Current (Fig.3, Fig. CT.5) Clamped Inductive Load Current(Fig.4, Fig. CT.2) Diode Continuous Forward Current Diode Maximum Forward Current Gate-to-Emitter Voltage Maximum Power Dissipation (Fig.2) Maximum Power Dissipation (Fig.2) Operating Junction and Storage Temperature Range Soldering Temperature, for 10 seconds Mounting Torque, 6-32 or M3 screw.

P aram eter

Qg Q ge Q gc E on E off E tot E on E off E tot td (o n ) tr td (o ff) tf C ies C oes C res R BSO A

T o ta l G a te ch a rg e (tu rn -o n ) G a te - E m itte r C h a rg e (tu rn -o n ) G a te - C o lle cto r C h a rg e (tu rn -o n ) T u rn -O n S w itch in g L o ss T u rn -O ff S w itch in g L o ss T o ta l S w itch in g L o ss T u rn -o n S w itch in g L o ss T u rn -o ff S w itch in g L o ss T o ta l S w itch in g L o ss T u rn - o n d e la y tim e R ise tim e T u rn - o ff d e la y tim e F a ll tim e In p u t C a p a cita n ce O u tp u t C a p a cita n ce R e ve rse T ra n sfe r C a p a cita n ce

英飞凌IGBT及DIODE简介

Vbrces 650V @ 25°C Low Qg Low Coss / Eoss High Softness (H5) Co-pak diode robustness, low Qrr, high dI/dt, dV/dt

•Higher design margin •Cosmic radiation robustness in Solar •Low driving losses „cheap“ driver possible •High efficiency at light load •Low losses in resonant topology smaller resonant tank •low Rgon=Rgoff, Plug&Play replacement (H5) , easy of use. •Low EMI High Reliability in resonant topologies (ZVS/LLC) concerning hard commutation capability of anti-parallel diode

9/16/2013 Copyright © Infineon Technologies 2010. All rights reserved.

Turn-off controllability

Double Pulse characterization Turn-off

0.40

Vce=400V, Tc=25°C, Vge=15V, Ic=20A

25° C

Trade-off previous generation

150° C

TRENCHSTOP™5

TRENCHSTOP™5

At 150°C junction temperature the TRENCHSTOPTM5 offers: The same Vce(sat) value as the TRENCHSTOPTM family

ADP3654

High Speed, Dual, 4 A MOSFET DriverADP3654Rev. 0Information furnished by Analog Devices is believed to be accurate and reliable. However , no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners.One Technology Way, P.O. Box 9106, N orwood, MA 02062-9106, U.S.A.Tel: 781.329.4700 Fax: 781.461.3113 ©2010 Analog Devices, Inc. All rights reserved.FEATURESIndustry-standard-compatible pinout High current drive capabilityPrecise UVLO comparator with hysteresis 3.3 V-compatible inputs10 ns typical rise time and fall time at 2.2 nF load Matched propagation delays between channels Fast propagation delay 4.5 V to 18 V supply voltage Parallelable dual outputsRated from −40°C to +125°C junction temperatureThermally enhanced packages, 8-lead SOIC_N_EP and 8-lead MINI_SO_EPAPPLICATIONSAC-to-dc switch mode power supplies DC-to-dc power supplies Synchronous rectification Motor drivesGENERAL DESCRIPTIONThe ADP3654 high current and dual high speed driver is capable of driving two independent N-channel power MOSFETs. The driver uses the industry-standard footprint but adds high speed switching performance.The wide input voltage range allows the driver to be compatible with both analog and digital PWM controllers.Digital power controllers are powered from a low voltagesupply, and the driver is powered from a higher voltage supply. The ADP3654 driver adds UVLO and hysteresis functions, allowing safe startup and shutdown of the higher voltage supply when used with low voltage digital controllers.The driver is available in thermally enhanced SOIC_N_EP and MINI_SO_EP packaging to maximize high frequency and current switching in a small printed circuit board (PCB) area.FUNCTIONAL BLOCK DIAGRAMOUTAVDDOUTBNCINA PGND INB NC09054-001Figure 1.ADP3654Rev. 0 | Page 2 of 12TABLE OF CONTENTSFeatures..............................................................................................1 Applications.......................................................................................1 General Description.........................................................................1 Functional Block Diagram..............................................................1 Revision History...............................................................................2 Specifications.....................................................................................3 Timing Diagrams..........................................................................3 Absolute Maximum Ratings............................................................4 ESD Caution..................................................................................4 Pin Configuration and Function Descriptions.............................5 Typical Performance Characteristics.............................................6 Test Circuit.........................................................................................8 Theory of Operation.........................................................................9 Input Drive Requirements (INA and INB)................................9 Low-Side Drivers (OUTA, OUTB).............................................9 Supply Capacitor Selection..........................................................9 PCB Layout Considerations.........................................................9 Parallel Operation......................................................................10 Thermal Considerations............................................................10 Outline Dimensions.......................................................................12 Ordering Guide.. (12)REVISION HISTORY8/10—Revision 0: Initial VersionADP3654Rev. 0 | Page 3 of 12SPECIFICATIONSV DD = 12 V , T J = −40°C to +125°C, unless otherwise noted.1 Table 1.Parameter Symbol Test Conditions/Comments Min Typ Max Unit SUPPLY Supply Voltage Range V DD 4.5 18 V Supply Current I DD No switching 1.2 3 mA UVLOTurn-On Threshold Voltage V UVLO_ON V DD rising, T J = 25°C, see Figure 3 3.8 4.2 4.5 V Turn-Off Threshold Voltage V UVLO_OFF V DD falling, T J = 25°C, see Figure 33.5 3.94.3 V Hysteresis 0.3 V DIGITAL INPUTS (INA, INB) Input Voltage High V IH See Figure 2 2.0 V Input Voltage Low V IL See Figure 2 0.8 V Input Current I IN 0 V < V IN < V DD −20 +20 μA Internal Pull-Up/Pull-Down Current 6 μA OUTPUTS (OUTA, OUTB) Output Resistance, Unbiased VDD = PGND 80 kΩ Peak Source Current See Figure 14 4 A Peak Sink Current See Figure 14 −4 A SWITCHING TIME OUTA and OUTB Rise Time t RISE C LOAD = 2.2 nF, see Figure 2 10 25 ns OUTA and OUTB Fall Time t FALL C LOAD = 2.2 nF, see Figure 2 10 25 ns OUTA and OUTB Rising Propagation Delay t D1 C LOAD = 2.2 nF, see Figure 2 14 30 ns OUTA and OUTB Falling Propagation Delay t D2 C LOAD = 2.2 nF, see Figure 2 22 35 ns Delay Matching Between Channels 2 ns1All limits at temperature extremes guaranteed via correlation using standard statistical quality control (SQC) methods.TIMING DIAGRAMS09054-002Figure 2. Output Timing Diagram09054-003Figure 3. UVLO FunctionADP3654Rev. 0 | Page 4 of 12ABSOLUTE MAXIMUM RATINGSTable 2.Parameter RatingVDD −0.3 V to +20 VOUTA, OUTBDC −0.3 V to V DD + 0.3 V<200 ns −2 V to V DD + 0.3 VINA, INB −0.3 V to V DD + 0.3 VESDHuman Body Model (HBM) 3.5 kV Field Induced Charged Device Model(FICDM)SOIC_N_EP 1.5 kV INI_SO_EP 1.0 kV θJA , JEDEC 4-Layer Board SOIC_N_EP 159°C/W MINI_SO_EP 1 43°C/W Junction Temperature Range −40°C to +150°C Storage Temperature Range −65°C to +150°C Lead Temperature Soldering (10 sec) 300°C Vapor Phase (60 sec) 215°C Infrared (15 sec) 260°C1θJA is measured per JEDEC standards, JESD51-2, JESD51-5, and JESD51-7, as appropriate with the exposed pad soldered to the PCB.Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or anyother conditions above those indicated in the operationalsection of this specification is not implied. Exposure to absolutemaximum rating conditions for extended periods may affectdevice reliability. ESD CAUTIONADP3654Rev. 0 | Page 5 of 12PIN CONFIGURATION AND FUNCTION DESCRIPTIONSNC 1INA 2PGND 3INB 4NC8OUTA7VDD 6OUTB5ADP3654TOP VIEW(Not to Scale)NOTES1. NC = NO CONNECT.2.THE EXPOSED PAD OF THE PACKAGE IS NOT DIRECTLY CONNECTED TO ANY PIN OF THE PACKAGE, BUT IT ISELECTRICALLY AND THERMALLY CONNECTED TO THE DIE SUBSTRATE, WHICH IS THE GROUND OF THE DEVICE. IT IS RECOMMENDED TO HAVE THE EXPOSED PAD AND THE PGND PIN CONNECTED ON THE PCB.09054-004Figure 4. Pin ConfigurationTable 3. Pin Function DescriptionsPin No. Mnemonic Description 1 NC No Connect.2 INA Input Pin for Channel A Gate Driver.3 PGND Ground. This pin should be closely connected to the source of the power MOSFET.4 INB Input Pin for Channel B Gate Driver.5 OUTB Output Pin for Channel B Gate Driver.6 VDD Power Supply Voltage. Bypass this pin to PGND with a ~1 μF to 5 μF ceramic capacitor.7 OUTAOutput Pin for Channel A Gate Driver. 8 NC No Connect.9 EPADExposed Pad. The exposed pad of the package is not directly connected to any pin of the package, but it is electrically and thermally connected to the die substrate, which is the ground of the device. It is recommended to have the exposed pad and the PGND pin connected on the PCB.ADP3654Rev. 0 | Page 6 of 12TYPICAL PERFORMANCE CHARACTERISTICSV DD = 12 V , T J = 25°C, unless otherwise noted.3456789–50–30–101030507090110130TEMPERATURE (°C)U V L O (V )09054-005Figure 5. UVLO vs. Temperature02468101214–50–30–101030507090110130TEMPERATURE (°C)t FALLt RISET I M E (n s )09054-006Figure 6. Rise and Fall Times vs. Temperature102030405060–50–30–101030507090110130TEMPERATURE (°C)T I M E (n s )09054-007Figure 7. Propagation Delay vs. Temperature51015202505101520V DD (V)T I M E (n s )t FALLt RISE09054-008Figure 8. Rise and Fall Times vs. V DD01020304050607005101520t D2t D1V DD (V)T I M E (n s )09054-009Figure 9. Propagation Delay vs. V DD09054-010Figure 10. Typical Rise Propagation DelayADP3654Rev. 0 | Page 7 of 1209054-011Figure 11. Typical Fall Propagation Delay09054-012Figure 12. Typical Rise Time09054-013Figure 13. Typical Fall TimeADP3654Rev. 0 | Page 8 of 12TEST CIRCUITLOAD09054-014Figure 14. Test CircuitADP3654Rev. 0 | Page 9 of 12THEORY OF OPERATIONThe ADP3654 dual driver is optimized for driving twoindependent enhancement N-channel MOSFETs or insulated gate bipolar transistors (IGBTs) in high switching frequency applications.These applications require high speed, fast rise and fall times, as well as short propagation delays. The capacitive nature of the aforementioned gated devices requires high peak current capability as well.09054-015Figure 15. Typical Application CircuitINPUT DRIVE REQUIREMENTS (INA AND INB)The ADP3654 is designed to meet the requirements of modern digital power controllers; the signals are compatible with 3.3 V logic levels. At the same time, the input structure allows for input voltages as high as V DD .An internal pull-down resistor is present at the input, which guarantees that the power device is off in the event that the input is left floating.LOW-SIDE DRIVERS (OUTA, OUTB)The ADP3654 dual drivers are designed to drive ground referenced N-channel MOSFETs. The bias is internally connected to the V DD supply and PGND.When ADP3654 is disabled, both low-side gates are held low. Internal impedance is present between the OUTA pin and GND and between the OUTB pin and GND; this feature ensures that the power MOSFET is normally off when bias voltage is not present.When interfacing ADP3654 to external MOSFETs, the designer should consider ways to make a robust design that minimizes stresses on both the driver and the MOSFETs. These stresses include exceeding the short time duration voltage ratings on the OUTA and OUTB pins, as well as the external MOSFET.Power MOSFETs are usually selected to have a low on resistance to minimize conduction losses, which usually implies a large input gate capacitance and gate charge.SUPPLY CAPACITOR SELECTIONFor the supply input (V DD ) of the ADP3654, a local bypass capacitor is recommended to reduce the noise and to supply some of the peak currents that are drawn.An improper decoupling can dramatically increase the rise times because excessive resonance on the OUTA and OUTB pins can, in some extreme cases, damage the device, due to inductive overvoltage on the VDD, OUTA, or OUTB pin. The minimum capacitance required is determined by the size of the gate capacitances being driven, but as a general rule, a 4.7 μF, low ESR capacitor should be used. Multilayer ceramic chip (MLCC) capacitors provide the best combination of low ESR and small size. Use a smaller ceramic capacitor (100 nF) with a better high frequency characteristic in parallel to the main capacitor to further reduce noise.Keep the ceramic capacitor as close as possible to the ADP3654 device and minimize the length of the traces going from the capacitor to the power pins of the device.PCB LAYOUT CONSIDERATIONSUse the following general guidelines when designing PCBs: • Trace out the high current paths and use short, wide (>40 mil) traces to make these connections.• Minimize trace inductance between the OUTA and OUTB outputs and MOSFET gates.• Connect the PGND pin of the ADP3654 device as closely as possible to the source of the MOSFETs.• Place the V DD bypass capacitor as close as possible to the VDD and PGND pins.•Use vias to other layers, when possible, to maximize thermal conduction away from the IC.ADP3654Rev. 0 | Page 10 of 12Figure 16 shows an example of the typical layout based on the preceding guidelines.09054-016Figure 16. External Component Placement ExampleNote that the exposed pad of the package is not directly con-nected to any pin of the package, but it is electrically andthermally connected to the die substrate, which is the ground of the device.PARALLEL OPERATIONThe two driver channels present in the ADP3654 device can be combined to operate in parallel to increase drive capability and minimize power dissipation in the driver.The connection scheme is shown in Figure 17. In this configura-tion, INA and INB are connected together, and OUTA and OUTB are connected together.Particular attention must be paid to the layout in this case to optimize load sharing between the two drivers.09054-017Figure 17. Parallel OperationTHERMAL CONSIDERATIONSWhen designing a power MOSFET gate drive, the maximum power dissipation in the driver must be considered to avoid exceeding maximum junction temperature.Data on package thermal resistance is provided in Table 2 to help the designer with this task.There are several equally important aspects that must be considered, such as the following: • Gate charge of the power MOSFET being driven • Bias voltage value used to power the driver • Maximum switching frequency of operation • Value of external gate resistance• Maximum ambient (and PCB) temperature •Type of packageAll of these factors influence and limit the maximum allowable power dissipated in the driver.The gate of a power MOSFET has a nonlinear capacitance characteristic. For this reason, although the input capacitance is usually reported in the MOSFET data sheet as C ISS , it is not useful to calculate power losses.The total gate charge necessary to turn on a power MOSFET device is usually reported on the device data sheet under Q G . This parameter varies from a few nanocoulombs (nC) to several hundred nC, and is specified at a specific V GS value (10 V or 4.5 V).The power necessary to charge and then discharge the gate of a power MOSFET can be calculated as:P GATE = V GS × Q G × f SWwhere:V GS is the bias voltage powering the driver (VDD). Q G is the total gate charge.f SW is the maximum switching frequency.The power dissipated for each gate (P GATE ) still needs to be multiplied by the number of drivers (in this case, 1 or 2) being used in each package, and it represents the total power dissi-pated in charging and discharging the gates of the power MOSFETs.Not all of this power is dissipated in the gate driver because part of it is actually dissipated in the external gate resistor, R G . The larger the external gate resistor is, the smaller the amount of power that is dissipated in the gate driver.In modern switching power applications, the value of the gate resistor is kept at a minimum to increase switching speed and minimize switching losses.In all practical applications where the external resistor is in the order of a few ohms, the contribution of the external resistor can be neglected, and the extra loss is assumed in the driver, providing a good guard band to the power loss calculations.ADP3654Rev. 0 | Page 11 of 12In addition to the gate charge losses, there are also dc bias losses, due to the bias current of the driver. This current is present regardless of the switching.P DC = V DD × I DDThe total estimated loss is the sum of P DC and P GATE .P LOSS = P DC + (n × P GATE ) where n is the number of gates driven.When the total power loss is calculated, the temperature increase can be calculated asΔT J = P LOSS × θJADesign ExampleFor example, consider driving two IRFS4310Z MOSFETs with a V DD of 12 V at a switching frequency of 300 kHz, using an ADP3654 in the SOIC_N_EP package.The maximum PCB temperature considered for this design is 85°C. From the MOSFET data sheet, the total gate charge is Q G = 120 nC.P GATE = 12 V × 120 nC × 300 kHz = 432 mW P DC = 12 V × 1.2 mA = 14.4 mWP LOSS = 14.4 mW + (2 × 432 mW) = 878.4 mW The SOIC_N_EP thermal resistance is 59°C/W .ΔT J = 878.4 mW × 59°C/W = 51.8°C T J = T A + ΔT J = 136.8°C ≤ T JMAXThis estimated junction temperature does not factor in the power dissipated in the external gate resistor and, therefore, provides a certain guard band.If a lower junction temperature is required by the design, the MINI_SO_EP package can be used, which provides a thermal resistance of 43°C/W , so that the maximum junction temperature isΔT J = 878.4 mW × 43°C/W = 37.7°C T J = T A + ΔT J = 122.7°C ≤ T JMAXOther options to reduce power dissipation in the driver include reducing the value of the V DD bias voltage, reducing switching fre-quency, and choosing a power MOSFET with smaller gate charge.ADP3654Rev. 0 | Page 12 of 12OUTLINE DIMENSIONSCOMPLIANT TO JEDEC STANDARDS MS-012-AACONTROLLING DIMENSIONS ARE IN MILLIMETER; INCH DIMENSIONS(IN PARENTHESES)ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.072808-A0.25 (0.0098)0.17 (0.0067)4.00 (0.157)3.90 (0.154)3.80 (0.150)1.27 (0.05)BSC0.31 (0.012)COPLANARITY0.10(PINS UP)FOR PROPER CONNECTION OF THE EXPOSED PAD, REFER TOFigure 18. 8-Lead Standard Small Outline Package, with Exposed Pad [SOIC_N_EP]Narrow Body (RD-8-1)Dimensions shown in millimeters and (inches)071008-ACOMPLIANT TO JEDEC STANDARDS MO-187-AA-T0.94COPLANARITY0.100.230.18FUNCTION DESCRIPTIONSSECTION OF THIS DATA SHEET.Figure 19. 8-Lead Mini Small Outline Package with Exposed Pad [MINI_SO_EP](RH-8-1)Dimensions shown in millimetersORDERING GUIDEModel 1UVLO Option TemperatureRange Package Description Package Option Ordering Quantity Branding ADP3654ARDZ-RL 4.5 V −40°C to +125°C 8-Lead Standard Small Outline Package(SOIC_N_EP), 13“ Tape and ReelRD-8-1 2,500 ADP3654ARHZ-RL 4.5 V −40°C to +125°C 8-Lead Mini Small Outline Package (MINI_SO_EP),13” Tape and ReelRH-8-1 3,000 781Z = RoHS Compliant Part.©2010 Analog Devic es, Inc . All rights reserved. Trademarks and registered trademarks are the property of their respec tive owners. D09054-0-8/10(0)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

428IEEEELECTRONDEVICELETTERS,VOL.20,NO.8,AUGUST19991.2kVTrenchInsulatedGateBipolarTransistors(IGBT’s)withUltralowOn-Resistance

F.Udrea,S.S.M.Chan,J.Thomson,T.Trajkovic,P.R.Waind,G.A.J.Amaratunga,andD.E.Crees

Abstract—Inthisletter,wereportthefulldevelopmentof1.2kVTrenchIGBT’swithultralowon-resistance,latch-upfreeoperationandhighlysuperioroverallperformancewhencomparedtostateoftheartIGBT’s.Theminimumforwardvoltagedropatthestandardcurrentdensityof100A/cm2was

1.1Vfornonirradiateddevicesand2.1Vforirradiateddevices.Themaximumcontrollablecurrentdensitywasinexcessof1000A/cm2.

I.INTRODUCTION

SINCEtheinventionofTrenchMOSFETandTrenchIGBT

[1],severalleadingindustrialandacademicgroupshaveconductedresearchintrench-gatepowerdevicestoextendthelimitsoftheexistingDMOS-gatedevicestowardhigherblock-ingvoltages(e.g.4.5kV)andimprovetheon-state/switchingtradeoffperformance[2]–[7].InparticularresearchonIGBT’sintherangeof1.2kVisofincreasedinterestowingtonumerousapplicationsinmotorcontrol.Optimizationof1.2kVpunchthrough(PT)andnonpunchthrough(NPT)thirdgenerationDMOSIGBT’swasearlierreportedin[8].Duringthepastfewyears,wereportedontheon-statephysicalbehaviorofTrenchIGBT’sgivenbyadualPINdiode—PNPtransistormechanismanddemonstratedthattheTrenchIGBToffersdecisiveadvantagesovertheequivalentDMOSstructuresuchasanenhancedcarriermodulationatthecathodesideduetothePINdiodeeffect,alargerSOAduetoreducedactionoftheparasiticthyristorinherentintheIGBTstructures,andamoreflexibledesignandgeometry[9],[10].Recentlywereportedontheprocessdevelopmentofhigh-voltageTrenchIGBT’s[11]anddiscussedkeyissuessuchasoxidebreakdownvoltageandtunnellingcurrent,channelmobility,surfaceroughnessandedgeterminations.Inthisletter,wereporttheexperimentalresultsonthe1.2kVTrenchIGBTgeneration.

II.DEVICESTRUCTURE,DESIGNANDTECHNOLOGY

Wehavefabricated1.2kV25ApunchthroughTrenchIGBTdevicesbasedonstripeandhexagonalgeometry.Fieldringswereusedattheedgeofthedevicetoavoidprematurebreakdown.ThecrosssectionofatypicalcellisshowninFig.1.Thethicknessandtheresistivityofthen-baseare

ManuscriptreceivedDecember16,1998.F.Udrea,T.Trajkovic,andG.A.J.AmaratungaarewiththeDepartmentofEngineering,CambridgeUniversity,CambridgeCB21PZ,U.K.S.S.M.Chan,J.Thomson,P.R.Waind,andD.E.CreesarewithMitelSemiconductor(formerlyGECPlesseySemiconductors),LincolnLN63LF,U.K.PublisherItemIdentifierS0741-3106(99)06545-3.

Fig.1.The1.2kVPunchthroughTrenchIGBTcrosssection.Theratiobetweenthehorizontalaccumulationlayerlength,lacc,andthetrenchspacing,s/2,istermedastheaspectdesignratio.

115cmrespectively.Thebufferlayeris10cmThecellunitvariedindifferentdesignsfrom8m.Theratiobetweenthetrenchwidthandthetrenchspacing,termedasdesignaspectratiowasalsovariedbetween0.2and1.2.Thetrenchdepthwastypically5UDREAetal.:1.2KVTRENCHIGBT’S429(a)(b)Fig.2.(a)TSuprem42-DNet-dopingprofileusedsubsequentlyinMedicitosimulatedevicecharacteristics.(b)Crosssectionofatrenchstructureafterpolysiliconoxidation.

baseandhencereducedresistivityduringon-state.Theplasmadensityisafunctionofthecurrentdensityandthelifetime.Thethresholdvoltagewas4.5Vandthisvaluehasbeenconsistentlybeenreproducedwithanaccuracyof5%inalldeviceswemeasuredacrossabatchofmmdiameterSiwafers,whichshowsthatthegateoxidethicknesswasuniformacrossthewafersandtheetch-backandpolysiliconoxidationwereaccuratelycontrolled.Thevoltagedropat100A/cm.Subsequently,thedeviceswereelectronirradiatedwithadoseof16MRadandtheon-statevoltagedropincreasedto2.1V.Toourknowledge,theseareamongthemostpromisingresultsreportedforthe1.2kVIGBTclasstodate.Similarresultson1.2kVTrenchIGBT’shavebeenveryrecentlyobtainedbySiemensandreportedin[12].HowevertheseresultswerebasedonaNPTstructureusingthinwafertechnology.WehavereportedearlieronthephysicaloperationoftheTrenchIGBT[9]andwehaveshownthatalargeraspectdesignratio(i.e.,trenchwidth/trenchspacing)resultsinreducedon-stateresistanceduetotheactionofPINdiode.Wehavealsoshownthattheloweron-stateresistanceisnotaccompaniedbyareducedswitchingspeedsincetheincreasedamountofplasmaatthecathodesideisremovedrapidlyduringturn-offoperation[10].TooptimizetheperformanceofTrenchIGBTweinvestigatedexperimentallyalargevarietyofstructureswithdifferentunitcellsanddesignaspectratios.Basedonthenumericalsimulationsandtheexperimental

Fig.3.1.2kV25AirradiatedTrenchIGBTturn-offcharacteristicsininductiveconditionsat125Cwithagateresistanceof25.

resultstheunitcellanddesignaspectratioforanoptimumtradeoffbetweenasmallon-statevoltagedropandrelativelysmallsaturationcurrentwerefoundtobe10m(i.e.,4mspacing)respectively.Theswitchingcharacteristicsperformedininductiveconditionsat125areshowninFig.3.Theturn-offtimefordevicesirradiatedwiththemaximumdosewasapproximately500ns.Thetradeoffbetweentheturn-offenergylossesat125