集成电路课程设计报告三输入异或门电路

门电路实验报告心得(3篇)

第1篇一、前言在数字电路的学习过程中,门电路作为基础组成部分,扮演着至关重要的角色。

为了加深对门电路的理解,我们进行了一系列的实验。

通过这些实验,我对门电路的工作原理、逻辑功能以及实际应用有了更为深刻的认识。

以下是我对这次门电路实验的心得体会。

二、实验目的与内容1. 实验目的(1)掌握门电路的基本原理和逻辑功能;(2)了解门电路在实际电路中的应用;(3)学会使用数字电路实验设备进行实验操作;(4)提高分析问题、解决问题的能力。

2. 实验内容(1)验证与非门、或非门、异或门等基本门电路的逻辑功能;(2)搭建半加器、全加器等组合逻辑电路;(3)了解TTL集成电路的特点和使用方法;(4)掌握数字电路实验设备的操作方法。

三、实验过程与心得1. 实验过程(1)按照实验指导书的要求,连接好实验电路;(2)根据输入端的高低电平,观察输出端的状态,记录实验数据;(3)分析实验数据,验证门电路的逻辑功能;(4)搭建组合逻辑电路,观察电路的输出状态,验证电路的功能;(5)学习TTL集成电路的特点和使用方法,掌握数字电路实验设备的操作方法。

2. 心得体会(1)基本门电路的逻辑功能通过实验,我深刻理解了与非门、或非门、异或门等基本门电路的逻辑功能。

这些基本门电路是构成复杂数字电路的基础,掌握它们对于学习数字电路至关重要。

(2)组合逻辑电路的搭建在搭建组合逻辑电路的过程中,我学会了如何根据电路功能要求,选用合适的门电路进行组合。

同时,通过实验,我对半加器、全加器等组合逻辑电路的工作原理有了更深入的了解。

(3)TTL集成电路的特点和使用方法TTL集成电路具有工作速度快、输出幅度大、种类多、不易损坏等特点。

通过实验,我掌握了TTL集成电路的使用方法,为以后在实际电路中的应用奠定了基础。

(4)数字电路实验设备的操作方法在实验过程中,我学会了如何使用数字电路实验设备进行实验操作。

这对我今后在实验室进行实验研究具有重要意义。

四、实验总结通过这次门电路实验,我对门电路有了更为全面的认识。

集成逻辑门电路实验报告

一、实验目的1. 理解和掌握集成逻辑门电路的基本原理和组成。

2. 熟悉不同类型集成逻辑门电路(如与门、或门、非门、异或门等)的逻辑功能和特性。

3. 学习使用集成逻辑门电路进行基本逻辑运算和组合逻辑电路的设计。

4. 提高动手能力和电路分析能力。

二、实验原理集成逻辑门电路是数字电路中最基本的单元,由若干个逻辑门组成,可以完成基本的逻辑运算。

常见的逻辑门有与门、或门、非门、异或门等。

这些逻辑门通过输入信号和输出信号之间的逻辑关系来实现特定的功能。

三、实验器材1. 数字电路实验箱2. 万用表3. 74LS00四2输入与非门1片4. 74LS86四2输入异或门1片5. 74LS11三3输入与门1片6. 74LS32四2输入或门1片7. 74LS04反相器1片四、实验内容1. 验证常用集成门电路的逻辑功能(1)连接74LS00四2输入与非门,测试其逻辑功能。

根据输入信号的不同组合,观察输出信号的变化,验证与非门的逻辑功能。

(2)连接74LS86四2输入异或门,测试其逻辑功能。

根据输入信号的不同组合,观察输出信号的变化,验证异或门的逻辑功能。

(3)连接74LS11三3输入与门,测试其逻辑功能。

根据输入信号的不同组合,观察输出信号的变化,验证与门的逻辑功能。

(4)连接74LS32四2输入或门,测试其逻辑功能。

根据输入信号的不同组合,观察输出信号的变化,验证或门的逻辑功能。

(5)连接74LS04反相器,测试其逻辑功能。

观察输入信号和输出信号之间的关系,验证反相器的逻辑功能。

2. 学习使用集成逻辑门电路进行基本逻辑运算(1)使用与非门实现与运算:将两个输入信号分别连接到与非门的两个输入端,观察输出信号的变化,验证与非门实现与运算的功能。

(2)使用或门实现或运算:将两个输入信号分别连接到或门的两个输入端,观察输出信号的变化,验证或门实现或运算的功能。

(3)使用非门实现非运算:将输入信号连接到非门的输入端,观察输出信号的变化,验证非门实现非运算的功能。

集成电路门实验报告

一、实验目的1. 理解集成电路门的基本原理和组成;2. 掌握常用集成电路门的逻辑功能;3. 学习使用Multisim软件进行电路仿真;4. 培养动手能力和实验操作技能。

二、实验原理集成电路门是数字电路中最基本的逻辑单元,主要包括与门、或门、非门、异或门等。

这些门电路具有特定的逻辑功能,可以通过组合实现复杂的逻辑运算。

本实验主要研究TTL集成电路门的逻辑功能。

三、实验器材1. 数字电路实验箱;2. 万用表;3. 74LS00四2输入与非门;4. 74LS86四2输入异或门;5. 74LS11三3输入与门;6. 74LS32四2输入或门;7. 74LS04反相器;8. Multisim软件。

四、实验内容1. 与门实验(1)实验目的:验证与门的逻辑功能。

(2)实验步骤:① 在Multisim软件中搭建与门电路,选择74LS11三3输入与门作为测试器件;② 按照实验要求,改变输入端A、B、C的状态,观察输出端F的状态;③ 记录实验数据,分析实验结果。

(3)实验结果与分析:实验结果显示,当输入端A、B、C都为高电平时,输出端F才为高电平,符合与门的逻辑功能。

2. 或门实验(1)实验目的:验证或门的逻辑功能。

(2)实验步骤:① 在Multisim软件中搭建或门电路,选择74LS32四2输入或门作为测试器件;② 按照实验要求,改变输入端A、B的状态,观察输出端F的状态;③ 记录实验数据,分析实验结果。

(3)实验结果与分析:实验结果显示,当输入端A、B中至少有一个为高电平时,输出端F为高电平,符合或门的逻辑功能。

3. 非门实验(1)实验目的:验证非门的逻辑功能。

(2)实验步骤:① 在Multisim软件中搭建非门电路,选择74LS04反相器作为测试器件;② 按照实验要求,改变输入端A的状态,观察输出端F的状态;③ 记录实验数据,分析实验结果。

(3)实验结果与分析:实验结果显示,当输入端A为高电平时,输出端F为低电平;当输入端A为低电平时,输出端F为高电平,符合非门的逻辑功能。

CMOS异或门集成电路课程设计报告书

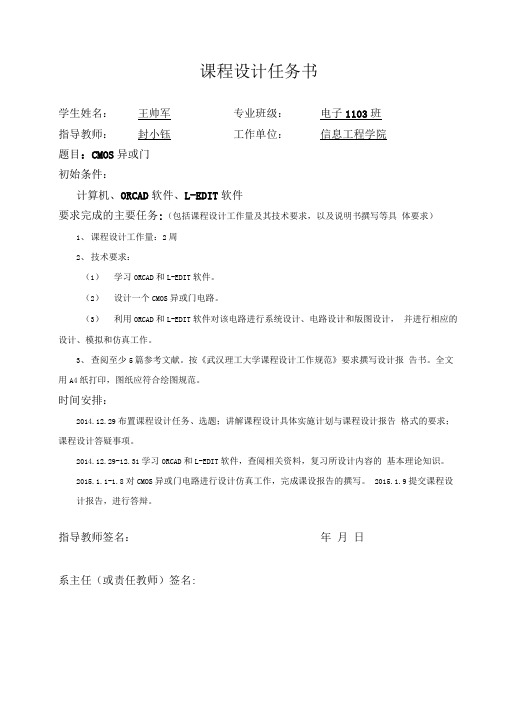

课程设计任务书学生:王帅军专业班级:电子1103班指导教师:封小钰工作单位:信息工程学院题目: CMOS异或门初始条件:计算机、ORCAD软件、L-EDIT软件要求完成的主要任务:(包括课程设计工作量及其技术要求,以及说明书撰写等具体要求)1、课程设计工作量:2周2、技术要求:(1)学习ORCAD和L-EDIT软件。

(2)设计一个CMOS异或门电路。

(3)利用ORCAD和L-EDIT软件对该电路进行系统设计、电路设计和版图设计,并进行相应的设计、模拟和仿真工作。

3、查阅至少5篇参考文献。

按《理工大学课程设计工作规》要求撰写设计报告书。

全文用A4纸打印,图纸应符合绘图规。

时间安排:2014.12.29布置课程设计任务、选题;讲解课程设计具体实施计划与课程设计报告格式的要求;课程设计答疑事项。

2014.12.29-12.31学习ORCAD和L-EDIT软件,查阅相关资料,复习所设计容的基本理论知识。

2015.1.1-1.8对CMOS异或门电路进行设计仿真工作,完成课设报告的撰写。

2015.1.9 提交课程设计报告,进行答辩。

指导教师签名:年月日系主任(或责任教师)签名:年月日目录摘要 (I)Abstract (II)1绪论 (1)2 异或门介绍 (2)3仿真电路设计 (3)3.1 ORCAD软件介绍 (3)3.2仿真电路原理图 (4)3.3仿真分析 (5)4版图设计 (8)4.1 L-EDIT软件介绍 (8)4.2版图绘制 (8)4.3 CMOS异或门版图DRC检查 (10)5心得体会 (11)参考文献 (12)附录 (123)摘要性能优越的异或门是实现各种运算集成电路的基础,可广泛应用于全加器,乘法器和算术逻辑单元等电路中。

CMOS集成电路由于工艺技术的进步以及功耗低、稳定性高、抗干扰性强、噪声容限大、可适应较宽的环境温度和电源电压等一系列的优点,成为现在IC设计的主流技术。

本文首先介绍了CMOS异或门电路,紧接着介绍了ORCAD软件,并利用此软件搭建了仿真电路图,对电路进行了仿真分析。

CMOS异或门集成电路课程设计.

课程设计任务书学生姓名:王帅军专业班级:电子1103班指导教师:封小钰工作单位:信息工程学院题目:CMOS异或门初始条件:计算机、ORCAD软件、L-EDIT软件要求完成的主要任务:(包括课程设计工作量及其技术要求,以及说明书撰写等具体要求)1、课程设计工作量:2周2、技术要求:(1)学习ORCAD和L-EDIT软件。

(2)设计一个CMOS异或门电路。

(3)利用ORCAD和L-EDIT软件对该电路进行系统设计、电路设计和版图设计,并进行相应的设计、模拟和仿真工作。

3、查阅至少5篇参考文献。

按《武汉理工大学课程设计工作规范》要求撰写设计报告书。

全文用A4纸打印,图纸应符合绘图规范。

时间安排:2014.12.29布置课程设计任务、选题;讲解课程设计具体实施计划与课程设计报告格式的要求;课程设计答疑事项。

2014.12.29-12.31学习ORCAD和L-EDIT软件,查阅相关资料,复习所设计内容的基本理论知识。

2015.1.1-1.8对CMOS异或门电路进行设计仿真工作,完成课设报告的撰写。

2015.1.9提交课程设计报告,进行答辩。

指导教师签名:年月日系主任(或责任教师)签名:目录摘要............................................................................... I•...Abstract ...................................................................................... 1J... 1绪论 (1)2异或门介绍 (2)3仿真电路设计 (3)3.1ORCAD软件介绍 (3)3.2仿真电路原理图 (4)3.3仿真分析 (5)4版图设计 (8)4.1L-EDIT软件介绍 (8)4.2版图绘制 (8)4.3 CMOS异或门版图DRC检查 (10)5心得体会 (11)参考文献 (12)附录 (123)摘要性能优越的异或门是实现各种运算集成电路的基础,可广泛应用于全加器,乘法器和算术逻辑单元等电路中。

三输入异或门真值表计算详解

三输入异或门真值表计算详解

异或门的应用范围广,在实际应用中可以用来实现奇偶发生器或模2加法器,还可以用作加法器、异或密码、异或校检、异或门倍频器、可控反相器等等。

虽然异或不是开关代数的基本运算之一,但是在实际运用中我们依然会相当普遍地使用到分立的异或门。

因此,我们为了熟练了解、掌握异或门这一基本逻辑电路,对异或门电路进行了这次课程设计。

异或门的逻辑表达式:

Y=ABC+ABC+ABC+ABC=A⊕B⊕C

进一步可得到一位比较器的真值表:

异或逻辑运算(半加运算)

异或运算通常用符号♁表示,其运算规则为:。

三输入奇偶校验电路设计

三输入奇偶校验电路设计

三输入奇偶校验电路可以用以下两种设计方法:

方法一:

1.将三个输入端分别连到一个电阻和一个LED灯,这样就有

三个电阻和三个LED灯。

2.将这三个LED灯的阳极分别连接到电源正极,将三个电阻

的另一端连接到电源负极。

3.将三个电阻的另一端通过三个开关连接到电阻和LED灯的

交点。

4.将这三个开关随意按下,观察LED灯的亮灭情况,确定奇

偶校验电路的输出。

方法二:

1.将三个输入端分别连接到三个与门的输入端。

2.将这三个与门的输出端连接到一个或门的输入端。

3.将或门的输出端连接到一个反相器的输入端。

4.将反相器的输出端接到一个LED灯和一个电阻的交点,

LED灯的另一端接到电源正极,电阻的另一端接到电源负极。

5.将三个输入端随意输入二进制数的三位,观察LED灯的亮灭情况,确定奇偶校验电路的输出。

集成逻辑门实验报告

一、实验目的1. 掌握基本逻辑门电路(与门、或门、非门、与非门、或非门、异或门等)的工作原理和逻辑功能。

2. 熟悉TTL集成逻辑门芯片的使用方法和注意事项。

3. 通过实验验证逻辑门电路的输入输出关系,加深对逻辑门电路的理解。

二、实验原理逻辑门电路是数字电路的基本组成单元,根据逻辑运算规则实现各种逻辑功能。

常见的逻辑门电路包括与门、或门、非门、与非门、或非门、异或门等。

本实验主要介绍TTL集成逻辑门芯片74LS00,该芯片内含四个2输入与非门,是数字电路中常用的基本逻辑门。

三、实验器材1. 数字电路实验箱2. 万用表3. 74LS00四2输入与非门芯片4. 开关5. 指示灯四、实验步骤1. 搭建与门电路:- 将74LS00芯片插入实验箱,将1脚(Vcc)连接到实验箱的+5V电源,将8脚(GND)连接到实验箱的GND。

- 将芯片的2、3、4、5脚分别连接到开关。

- 将芯片的6、7、8、9脚分别连接到指示灯。

- 打开开关,观察指示灯的亮灭情况,验证与门逻辑功能。

2. 搭建或门电路:- 将芯片的2、3脚连接到开关,将4、5脚连接到开关。

- 将芯片的6、7脚连接到指示灯,将8、9脚连接到指示灯。

- 打开开关,观察指示灯的亮灭情况,验证或门逻辑功能。

3. 搭建非门电路:- 将芯片的2脚连接到开关,将3脚连接到开关。

- 将芯片的6脚连接到指示灯。

- 打开开关,观察指示灯的亮灭情况,验证非门逻辑功能。

4. 搭建与非门电路:- 将芯片的2脚连接到开关,将3脚连接到开关。

- 将芯片的4脚连接到指示灯。

- 打开开关,观察指示灯的亮灭情况,验证与非门逻辑功能。

5. 搭建或非门电路:- 将芯片的2脚连接到开关,将3脚连接到开关。

- 将芯片的5脚连接到指示灯。

- 打开开关,观察指示灯的亮灭情况,验证或非门逻辑功能。

6. 搭建异或门电路:- 将芯片的2、3脚连接到开关,将4、5脚连接到开关。

- 将芯片的6脚连接到指示灯。

- 打开开关,观察指示灯的亮灭情况,验证异或门逻辑功能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

. -

**: 14461221

**: 14461223

课程设计

课程名称:集成电路设计

实验题目:三输入异或门电路设计

学生**:

学生**:

学院〔系〕:信息数理学院专业班级:

指导教师:

实习时间:2017 年06 月19 日 2017 年06 月30 日

三、电路设计:

3.1使用S—edit画出电路电路原理图总电路图:

分模块电路图1:与门

分模块电路图2:反相器

3.2使用T-Spice对画出电路原理图进展电路仿真

电路仿真代码:

vvdd Vdd GND 5.0

va A Gnd PULSE (0 5 200n 0.3n 0.3n 200n 400n)

vb B Gnd PULSE (0 5 100n 0.3n 0.3n 100n 200n)

vc C Gnd PULSE (0 5 50n 0.3n 0.3n 50n 100n)

.tran/op 1n 400n method =bdf

.print tran v(Y) v(Y) v(C) v(B) v(A)

3.3电路仿真结果:

输入信号:

输出结果:

四、幅员设计:

4.1设计规则

序号名称Rule distance

/lambda

1.1 Well Minimum Width 10.000

1.3 Well to Well(Same Potential) Spacing 6.000

2.1 Active Minimum Width

3.000

2.2 Active to Active Spacing

3.000

2.3a Source/Drain Active to Well Edge 5.000

2.3b Source/Drain Active to Well Space 5.000

2.4a WellContact(Active) to Well Edge

3.000

2.4b SubsContact(Active) to Well Spacing

3.000

3.1 Poly Minimum Width 2.000

3.2 Poly to Poly Spacing 2.000

3.3 Gate E*tension out of Active 2.000

3.4a/

4.1a Source/Drain Width 3.000

3.4b/

4.1b Source/Drain Width 3.000

3.5 Poly to Active Spacing 1.000

4.2a/2.5 Active to N-Select Edge 2.000

4.2b/2.5 Active to P- Select Edge 2.000

4.3a Select Edge to Actt 1.000

4.4a Select Minimum Width 2.000

4.4c Select to Select Spacing 2.000

光刻版对位次序:

M2→M1;M3→M1; M4→M1; M5→ M1; M6→M1; M7→M1; M9→M1;M8→M9;胖瘦标记:

4.5检测电路设计:

PMOS检测NMOS检测P+检测

N+检测Poly检测N阱检测

有源区检测4.6工艺流程:〔N阱CMOS工艺〕

1.衬底准备,选用P型衬底;

2.衬底氧化,生成和;

3.N-阱光刻,形成阱版;

4 N-阱注入,N-阱推进,退火,清洁外表;

5.生长薄氧化硅、长氮化硅;

6.光刻场区〔active反版〕;

7.N管场区光刻、注入;

8.场区氧化〔LOCOS〕,只是局部氧化;

9.清洁有源区外表、长栅氧;

10.阈值电压调整区光刻、注入;

11.多晶淀积掺杂、掺杂、光刻;

12.进展N管LDD光刻、注入;

13.进展P管LDD光刻、注入;

14.侧墙氧化物淀积、侧墙腐蚀;

15.用P-plus掩膜版光刻后进展P+有源区注入;

有源区:

多晶硅:

硼掺杂(P+):

磷掺杂(N+):刻孔:

刻蚀金属1:

刻蚀金属2:

分模块幅员1:与门

分模块电路图2:反相器

总幅员4.8 DRC检测:

4.9幅员电学性能测试:

使用T-Spice对画出电路幅员进展电路仿真

电路仿真代码:

vvdd Vdd GND 5.0

va A Gnd PULSE (0 5 200n 0.3n 0.3n 200n 400n)

vb B Gnd PULSE (0 5 100n 0.3n 0.3n 100n 200n)

vc C Gnd PULSE (0 5 50n 0.3n 0.3n 50n 100n)

.tran/op 1n 400n method =bdf

.print tran v(Y) v(Y) v(C) v(B) v(A)

输入输出信号:

4.10主要薄膜种类及性能参数要求〔包括氧化、隔离、屏蔽、电阻、互连、钝化等所有薄膜的厚度、电阻率及特殊要求〕

1. 预氧化;200nm,1100-1150℃,干湿干

干氧氧化:

湿氧氧化

氧化消耗的Si与生成的SiO2 的厚度比:

特点:氧化层致密,Si-SiO2界面陡峭,界面态密度低,氧化速率不高,获得厚氧化层困难。

2. APCVD 沉积SiO2;500nm,430-450℃

特点:低温、常压、生长速率大、沉积膜疏松

设备:

3.栅氧化;80nm

原理:

设备:氧化炉

设备图:

4. Al-Si溅射沉积;厚1.1 µm

为了保证半导体与金属间有可靠的接触,必须在连线光刻完成后做合金处理,对Al-Si 连线,在温度为430-450 C的N2/H2〔4:1〕混合气体〔Forming gas〕中进展合金,时间约30min。

H2的参加是为了降低CMOS 器件的界面态。

设备:多功能离子束增强沉积设备

原理:溅射镀膜是利用气体放电辉光产生的正离子在电场作用下高速轰击阴极靶,使靶材中的原子〔或分子〕逸出而淀积到被镀衬底〔或工件〕的外表,形成所需要的薄膜。

气体:Ar

设备图:

5. 沉积钝化层;PECVD SiO*Ny,800nm,或PI

气体:氨气、笑气

五、自我总结〔包括正确性、规*性、可用性、创新点、缺乏〕。