以太网芯片

rtl8139c以太网接口芯片

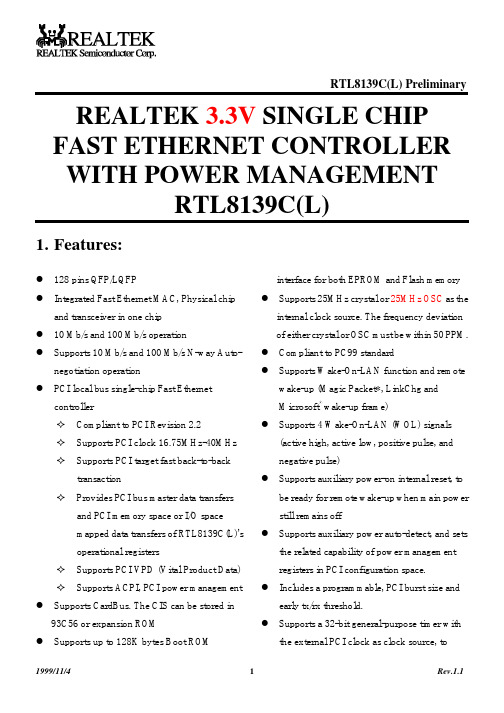

RTL8139C(L) Preliminary REALTEK 3.3V SINGLE CHIP FAST ETHERNET CONTROLLERWITH POWER MANAGEMENTRTL8139C(L)1.Features:l128 pins QFP/LQFPl Integrated Fast Ethernet MAC, Physical chip and transceiver in one chipl10 Mb/s and 100 Mb/s operationl Supports 10 Mb/s and 100 Mb/s N-way Auto-negotiation operationl PCI local bus single-chip Fast Ethernet controller²Compliant to PCI Revision 2.2²Supports PCI clock 16.75MHz-40MHz²Supports PCI target fast back-to-backtransaction²Provides PCI bus master data transfers and PCI memory space or I/O spacemapped data transfers of RTL8139C(L)'soperational registers²Supports PCI VPD (Vital Product Data)²Supports ACPI, PCI power management l Supports CardBus. The CIS can be stored in 93C56 or expansion ROMl Supports up to 128K bytes Boot ROMinterface for both EPROM and Flash memory l Supports 25MHz crystal or 25MHz OSC as the internal clock source. The frequency deviation of either crystal or OSC must be within 50 PPM. l Compliant to PC99 standardl Supports Wake-On-LAN function and remote wake-up (Magic Packet*, LinkChg andMicrosoft® wake-up frame)l Supports 4 Wake-On-LAN (WOL) signals (active high, active low, positive pulse, andnegative pulse)l Supports auxiliary power-on internal reset, to be ready for remote wake-up when main power still remains offl Supports auxiliary power auto-detect, and sets the related capability of power managementregisters in PCI configuration space.l Includes a programmable, PCI burst size and early tx/rx threshold.l Supports a 32-bit general-purpose timer with the external PCI clock as clock source, toRTL8139C(L) Preliminarygenerate timer-interruptl Contains two large (2Kbyte) independent receive and transmit FIFO’sl Advanced power saving mode when LAN function or wakeup function is not usedl Uses 93C46 (64*16-bit EEPROM) or 93C56 (128*16-bit EEPROM) to store resourceconfiguration, ID parameter, and VPD data.The 93C56 can also be used to store the CISdata structure for CardBus application.l Supports LED pins for various network activity indicationsl Supports digital and analog loopback capability on both portsl Half/Full duplex capabilityl Supports Full Duplex Flow Control (IEEE 802.3x)l 3.3V power supply with 5V tolerant I/Os.* Third-party brands and names are the property of their respective owners..N ote: The number of QFP package is RTL8139C. For the LQFP package, the number is RTL8139CL.RTL8139C(L) Preliminary 2.General DescriptionT he Realtek RTL8139C(L) is a highly integrated and cost-effective single-chip Fast Ethernet controller that provides 32-bit performance, PCI bus master capability, and full compliance with IEEE 802.3u 100Base-T specifications and IEEE 802.3x Full Duplex Flow Control. It also supports Advanced Configuration Power management Interface (ACPI), PCI power management for modern operating systems that is capable of Operating System Directed Power Management (OSPM) to achieve the most efficient power management. The RTL8139CL is suitable for the applications of CardBus or mobile with built-in network controller. The CIS data can be stored in either 93C56 EEPROM or expansion ROM.B esides the ACPI feature, the RTL8139C(L) also supports remote wake-up (including AMD Magic Packet*, LinkChg, and Microsoft® wake-up frame) in both ACPI and APM environments. Especially, the RTL8139C(L) is capable of performing internal reset whenever there is (auxiliary) power applied to. Once the auxiliary power is on whereas the main power still remains off, the RTL8139C(L) is ready and is waiting for the Magic Packet* or Link Change to wake the system up. Also, the LWAKE pin provides 4 different output signals including active high, active low, positive pulse, and negative pulse. The versatility of the RTL8139C(L) LWAKE pin satisfies all kinds of motherboards with Wake-On-LAN (WOL) function. The RTL8139C(L) also supports Analog Auto-Power-down, that is, the analog part of the RTL8139C(L) can be shut down temporarily according to the user’s requirement or when the RTL8139C(L) is in power down states with the wakeup function disabled. Besides, when the analog part is shut down and the IsolateB pin is low (i.e. the main power is off), then both the analog and digital parts stop functioning and the RTL8139C(L) will achieve the most power saving and consume extremely minor power. The RTL8139C(L) also support aux. power auto-detect function, and will auto-configure related bits of their own PCI power management registers in PCI configuration space.T he PCI Vital Product Data (VPD) is also supported to provide the information that uniquely identifies hardware (i.e., the RTL8139C(L) LAN card). The information may consist of part number, serial number, and other detailed information, and so on.RTL8139C(L) PreliminaryF or sake of cost-down, the RTL8139C(L) is capable of applying 25MHz crystal as its internal clock source. And you also can use 25MHz OSC.T he RTL8139C(L) keeps network maintenance cost low and eliminates usage barriers. It is the easiest way to upgrade a network from 10 to 100Mbps. It also supports full-duplex operation, making possible 200Mbps of bandwidth at no additional cost. To improve compatibility with other brands’ products, the RTL8139C(L) is also capable of receiving packets with InterFrameGap no less than 40 Bit-Time. The RTL8139C(L) is highly integrated and requires no “glue” logic or external memory. It includes an interface for a boot ROM and can be used in diskless workstations, providing maximum network security and ease of management.RTL8139C(L) Preliminary 3.Pin AssignmentRTL8139C(L) Preliminary4.Pin Descriptions4.1 POWER MANAGEMENT/ISOLATION INTERFACESymbol Type Pin No DescriptionPMEB (PME#)O/D76Power Management Event: Open drain, active low. Used by theRTL8139C(L) to request a change in its current power managementstate and/or to indicate that a power management event has occurred.ISOLATEB (ISOLATE#)I95Isolate pin: Active low. Used to isolate RTL8139C(L) from the PCI bus.The RTL8139C(L) does not drive its PCI outputs (excluding PME#)and does not sample its PCI input (including RST# and PCICLK) aslong as Isolate pin is asserted.LWAKE/ CSTSCHG O83LAN WAKE-UP signal (When CardB_En=0, bit2 Config3): Thissignal is used to inform motherboard to execute wake-up process. Themotherboard must support Wake-On-LAN (WOL). There are 4 choicesof output, including active high, active low, positive pulse, and negativepulse, that may be asserted from the LWAKE pin. Please refer toLWACT bit in CONFIG1 register and LWPTN bit in CONFIG4register for the setting of this output signal. The default output is anactive high signal. Once there is a PME event having come in, theLWAKE and PMEB assert at the same time when the LWPME (bit4,CONFIG4) is set to 0. If the LWPME is set to 1, the LWAKE assertsonly when the PMEB asserts and the ISOLATEB is low.CSTSCHG signal (When CardB_En=1, bit2 Config3): This signal isused in CardBus application only and is used to inform motherboard toexecute wake-up process whenever there is PME event occurs. This isalways an active high signal, the setting of LWACT (bit 4, Config1),LWPTN (bit2, Config4), and LWPME (bit4, Config4) means nothingin this case.This pin is a 3.3V signaling output pin.4.2 PCI INTERFACESymbol Type Pin No DescriptionAD31-0T/S120-123, 125-128, 4-6,8-11, 13, 26-29, 31-34,37-39, 41-45PCI address and data multiplexed pins.C/BE3-0T/S2, 14, 24, 36PCI bus command and byte enables multiplexed pins.CLK I116Clock provides timing for all transactions on PCI and is input to PCIdevice.CLKRUNB I/O75Clock Run: This signal is used by RTL8139C(L) to request starting (orspeeding up) the clock, CLK. CLKRUNB also indicates the clockstatus. For RTL8139C(L), CLKRUNB is an open drain output and alsoan input. The RTL8139C(L) requests the central resource to start, speedup, or maintain the interface clock by the assertion of CLKRUNB. Forthe host system, it is an S/T/S signal. The host system (central resource)is responsible for maintaining CLKRUNB asserted, and for driving ithigh to the negated (deasserted) state.DEVSELB S/T/S19Device Select: The RTL8139C(L) asserts this signal low when itrecognizes its target address after FRAMEB is asserted. As a busmaster, the RTL8139C(L) samples this signal to insure that a PCI targetRTL8139C(L) Preliminaryrecognizes the destination address for the data transfer.FRAMEB S/T/S15Cycle Frame is driven by the current master to indicate the beginningand duration of an access. FRAMEB is asserted to indicate a bustransaction is beginning. While FRAMEB is asserted, data transferscontinue. When FRAMEB is deasserted, the transaction is in the finaldata phase.GNTB I117Grant: This signal is asserted low to indicate to the RTL8139C(L) thatthe central arbiter has granted the ownership of the bus to theRTL8139C(L).REQB T/S118Request: The RTL8139C(L) will assert this signal low to request theownership of the bus to the central arbiter.IDSEL I3Initialization Device Select is used as a chip-select during configurationread and write transactions.INTAB O/D114INTAB is used to request an interrupt.IRDYB S/T/S16Initiator Ready indicates the initiating agent’s ability to complete thecurrent data phase of the transaction.TRDYB S/T/S17Target Ready indicates the target agent’s ability to complete the currentphase of the transaction.PAR T/S23Parity is even parity across AD31-0 and C/BE3-0.PERRB S/T/S21Parity Error: When the RTL8139C(L) is the bus master and a parityerror is detected, the RTL8139C(L) asserts both SERR bit in ISR andConfiguration Space command bit 8 (SERRB enable). Next, itcompletes the current data burst transaction, then stops operation andresets itself. After the host clears the system error, the RTL8139C(L)continues its operation.When the RTL8139C(L) is the bus target and a parity error is detected,the RTL8139C(L) asserts this PERRB pin.SERRB O/D22System Error: If an address parity error is detected and ConfigurationSpace Status register bit 15 (detected parity error) is enabled,RTL8139C(L) asserts both SERRB pin and bit 14 of Status register inConfiguration Space.STOPB S/T/S20Stop: Indicates the current target is requesting the master to stop thecurrent transaction.RSTB I115Reset: When RSTB is asserted low, the RTL8139C(L) performsinternal system hardware reset. RSTB must be held for a minimum of120 ns periods.4.3 FLASH/EEPROM INTERFACESymbol Type Pin No DescriptionMA16-3 MA8OI/O70-63, 61, 60, 57, 53-5161Boot PROM address bus: These pins are used to access up to 128k-byteflash memory or EPROM.Output pin as part of Boot PROM(or Flash) address bus after PCI reset.Input pin as Aux. Power detect pin to detect if Aux. Power exists or not,when initial power-on or PCI reset is asserted. Besides connecting thispin to Boot PROM, it should be pulled high to the Aux. Power via aresistor to detect Aux. power. If this pin is not pulled high to Aux.Power, the RTL8139C(L) assumes there is no Aux. power exists. Tosupport wakeup from ACPI D3cold or APM power-down, this pin mustbe pulled high to aux. power via a resistor.MA6/9356SEL I/O57When this pin is pulled high with a 10K£[resistor, the 93C56RTL8139C(L) PreliminaryEEPROM is used to store the resource data and CIS for theRTL8139C(L). The RTL8139C(L) latches the status of this pin atpower-up to determine what EEPROM(93C46 or 93C56) is used,afterwards, this pin is used as MA6.MA2/EESK O49The MA2-0 pins are switched to EESK, EEDI, EEDO in 93C46(93C56) programming or auto-load mode.MA1/EEDI O48MA0/EEDO O, I47EECS O5093C46 (93C56) chip selectMD0-7I/O108, 107, 105-100Boot PROM data busROMCSB O110ROM Chip Select: This is the chip select signal of the Boot PROM. OEB O88Output Enable: This enables the output buffer of the Boot PROM orFlash memory during a read operation.WEB O89Write Enable: This signal strobes data into the Flash memory during awrite cycle.4.4 POWER PINSSymbol Type Pin No DescriptionVDD P1, 12, 25, 35, 46, 58,+3.3V59, 77, 90, 96, 106,109, 119GroundGND P7, 18, 30, 40, 55, 56,62, 74, 80, 85, 93, 111,112, 113, 1244.5 LED INTERFACESymbol Type Pin No DescriptionLED0, 1, 2O99, 98, 97LED pinsLEDS1-000011011LED0TX/RX TX/RX TX TXLED1LINK100LINK10/100LINK10/100LINK100LED2LINK10FULL RX LINK10During power down mode, the LED’s are OFF.RTL8139C(L) Preliminary4.6 ATTACHMENT UNIT INTERFACESymbol Type Pin No DescriptionTXD+ TXD-OO9291100/10BASE-T transmit (Tx) data.RXIN+ RXIN-II8786100/10BASE-T receive (Rx) data.X1I7925 MHz crystal/OSC. input.X2O78Crystal feedback output. This output is used in crystal connection only.It must be left open when X1 is driven with an external 25 MHzoscillator.4.7 TEST AND THE OTHER PINSSymbol Type Pin No DescriptionRTT2-3TEST81, 82Chip test pins.RTSET I/O84This pin must pull low by 1.8KΩ resistor.NC-54, 71, 72, 73, 94Reserved5.Register DescriptionsT he RTL8139C(L) provides the following set of operational registers mapped into PCI memory space or I/O space.O ffset R/W T ag D escription0000h R/W I DR0I D Register 0, The ID register0-5 are only permitted to read/write by4-bye access.0001h R/W I DR1I D Register 10002h R/W I DR2I D Register 20003h R/W I DR3I D Register 30004h R/W I DR4I D Register 40005h R/W I DR5I D Register 50006h-0007h--R eserved0008h R/W M AR0M ulticast Register 0, The MAR register0-7 are only permitted toread/write by 4-bye access.0009h R/W M AR1M ulticast Register 1000Ah R/W M AR2M ulticast Register 2000Bh R/W M AR3M ulticast Register 3000Ch R/W M AR4M ulticast Register 4000Dh R/W M AR5M ulticast Register 5000Eh R/W M AR6M ulticast Register 6000Fh R/W M AR7M ulticast Register 70010h-0013h R/W T SD0T ransmit Status of Descriptor 00014h-0017h R/W T SD1T ransmit Status of Descriptor 10018h-001Bh R/W T SD2T ransmit Status of Descriptor 2001Ch-001Fh R/W T SD3T ransmit Status of Descriptor 30020h-0023h R/W T SAD0T ransmit Start Address of Descriptor00024h-0027h R/W T SAD1T ransmit Start Address of Descriptor1RTL8139C(L) Preliminary 0028h-002Bh R/W T SAD2T ransmit Start Address of Descriptor2002Ch-002Fh R/W T SAD3T ransmit Start Address of Descriptor30030h-0033h R/W R BSTART R eceive (Rx) Buffer Start Address0034h-0035h R E RBCR E arly Receive (Rx) Byte Count Register0036h R E RSR E arly Rx Status Register0037h R/W C R C ommand Register0038h-0039h R/W C APR C urrent Address of Packet Read003Ah-003Bh R C BR C urrent Buffer Address: The initial value is 0000h. It reflects totalreceived byte-count in the rx buffer.003Ch-003Dh R/W I MR I nterrupt Mask Register003Eh-003Fh R/W I SR I nterrupt Status Register0040h-0043h R/W T CR T ransmit (Tx) Configuration Register0044h-0047h R/W R CR R eceive (Rx) Configuration Register0048h-004Bh R/W T CTR T imer CounT Register: This register contains a 32-bit general-purpose timer. Writing any value to this 32-bit register will reset theoriginal timer and begin to count from zero.004Ch-004Fh R/W M PC M issed Packet Counter: Indicates the number of packets discarded dueto rx FIFO overflow. It is a 24-bit counter. After s/w reset, MPC iscleared. Only the lower 3 bytes are valid.W hen written any value, MPC will be reset also.0050h R/W9346CR93C46 (93C56) Command Register0051h R/W C ONFIG0C onfiguration Register 00052h R/W C ONFIG1C onfiguration Register 10053H--R eserved0054h-0057h R /W T imerInt T imer Interrupt Register. Once having written a nonzero value to thisregister, the Timeout bit of ISR register will be set whenever theTCTR reaches to this value. The Timeout bit will never be set as longas TimerInt register is zero.0058h R/W M SR M edia Status Register0059h R/W C ONFIG3C onfiguration register 3005Ah R/W C ONFIG4C onfiguration register 4005Bh--R eserved005Ch-005Dh R/W M ULINT M ultiple Interrupt Select005Eh R R ERID P CI Revision ID = 10h.005Fh--R eserved.0060h-0061h R T SAD T ransmit Status of All Descriptors0062h-0063h R/W B MCR B asic Mode Control Register0064h-0065h R B MSR B asic Mode Status Register0066h-0067h R/W A NAR A uto-Negotiation Advertisement Register0068h-0069h R A NLPAR A uto-Negotiation Link Partner Register006Ah-006Bh R A NER A uto-Negotiation Expansion Register006Ch-006Dh R D IS D isconnect Counter006Eh-006Fh R F CSC F alse Carrier Sense Counter0070h-0071h R/W N WAYTR N-way Test Register0072h-0073h R R EC R X_ER Counter0074h-0075h R/W C SCR C S Configuration Register0076-0077h--R eserved.0078h-007Bh R/W P HY1_PARM P HY parameter 1007Ch-007Fh R/W T W_PARM T wister parameter0080h R/W P HY2_PARM P HY parameter 20081-0083h--R eservedRTL8139C(L) Preliminary0084h R/W C RC0P ower Management CRC register0 for wakeup frame00085h R/W C RC1P ower Management CRC register1 for wakeup frame10086h R/W C RC2P ower Management CRC register2 for wakeup frame20087h R/W C RC3P ower Management CRC register3 for wakeup frame30088h R/W C RC4P ower Management CRC register4 for wakeup frame40089h R/W C RC5P ower Management CRC register5 for wakeup frame5008Ah R/W C RC6P ower Management CRC register6 for wakeup frame6008Bh R/W C RC7P ower Management CRC register7 for wakeup frame7008Ch–0093h R/W W akeup0P ower Management wakeup frame0 (64bit)0094h–009Bh R/W W akeup1P ower Management wakeup frame1 (64bit)009Ch–00A3h R/W W akeup2P ower Management wakeup frame2 (64bit)00A4h–00ABh R/W W akeup3P ower Management wakeup frame3 (64bit)00ACh–00B3h R/W W akeup4P ower Management wakeup frame4 (64bit)00B4h–00BBh R/W W akeup5P ower Management wakeup frame5 (64bit)00BCh–00C3h R/W W akeup6P ower Management wakeup frame6 (64bit)00C4h–00CBh R/W W akeup7P ower Management wakeup frame7 (64bit)00CCh R/W L SBCRC0L SB of the mask byte of wakeup frame0 within offset 12 to 7500CDh R/W L SBCRC1L SB of the mask byte of wakeup frame1 within offset 12 to 7500CEh R/W L SBCRC2L SB of the mask byte of wakeup frame2 within offset 12 to 7500CFh R/W L SBCRC3L SB of the mask byte of wakeup frame3 within offset 12 to 7500D0h R/W L SBCRC4L SB of the mask byte of wakeup frame4 within offset 12 to 7500D1h R/W L SBCRC5L SB of the mask byte of wakeup frame5 within offset 12 to 7500D2h R/W L SBCRC6L SB of the mask byte of wakeup frame6 within offset 12 to 7500D3h R/W L SBCRC7L SB of the mask byte of wakeup frame7 within offset 12 to 7500D4h-00D7h R/W F LASH F lash memory read/write register00D8h R/W C onfig5C onfiguration register 500D9h-00EFh--R eserved00F0h-00F3h R/W F ER F unction Event Register (Cardbus only)00F4h-00F7h R/W F EMR F unction Event Mask Register (CardBus only)00F8h-00FBh R F PSR F unction Present State Register (CardBus only)00FCh-00FFh W F FER F unction Force Event Register (CardBus only)5.1 Receive Status Register in Rx packet headerB it R/W S ymbol D escription15R M AR M ulticast Address Received: Set to 1 indicates that a multicast packet isreceived.14R P AM P hysical Address Matched: Set to 1 indicates that the destinationaddress of this packet matches the value written in ID registers.13R B AR B roadcast Address Received: Set to 1 indicates that a broadcast packetis received. BAR, MAR bit will not be set simultaneously.12-6--R eserved5R I SE I nvalid Symbol Error: (100BASE-TX only) An invalid symbol wasencountered during the reception of this packet if this bit set to 1.4R R UNT R unt Packet Received: Set to 1 indicates that the received packet lengthis smaller than 64 bytes ( i.e. media header + data + CRC < 64 bytes ) 3R L ONG L ong Packet: Set to 1 indicates that the size of the received packetexceeds 4k bytes.2R C RC C RC Error: When set, indicates that a CRC error occurred on thereceived packet.RTL8139C(L) Preliminary 1R F AE F rame Alignment Error: When set, indicates that a frame alignmenterror occurred on this received packet.0R R OK R eceive OK: When set, indicates that a good packet is received.5.2 Transmit Status Register (TSD0-3)(Offset 0010h-001Fh, R/W) T he read-only bits (CRS, TABT, OWC, CDH, NCC3-0, TOK, TUN) will be cleared by RTL8139C(L) when the Transmit Byte Count (bit12-0) in the corresponding Tx descriptor is written. It is not affected when software writes to these bits. These registers are only permitted to write by double-word access. After software reset, all bits except OWN bit are reset to “0”.B it R/W S ymbol D escription31R C RS C arrier Sense Lost: Set to 1 when the carrier is lost during transmittinga packet.30R T ABT T ransmit Abort: Set to 1 if the transmission of a packet was aborted.This bit is read only, writing to this bit is not affected.29R O WC O ut of Window Collision: Set to 1 if the RTL8139C(L) encountered an"out of window" collision during the transmission of a packet.28R C DH C D Heart Beat: The same as RTL8139(A/B).T his bit is cleared in the 100 Mbps mode.27-24R N CC3-0N umber of Collision Count: Indicates that the number of collisionsencountered during the transmission of a packet.23-22--R eserved21-16R/W E RTXTH5-0E arly Tx Threshold: Specifies the threshold level in the Tx FIFO tobegin the transmission. When the byte count of the data in the Tx FIFOreaches this level, (or the FIFO contains at least one complete packet)the RTL8139C(L) will transmit this packet.000000 = 8 bytesT hese fields count from 000001 to 111111 in unit of 32 bytes.T his threshold must be avoided from exceeding 2K byte.15R T OK T ransmit OK: Set to 1 indicates that the transmission of a packet wascompleted successfully and no transmit underrun occurs.14R T UN T ransmit FIFO Underrun: Set to 1 if the Tx FIFO was exhausted duringthe transmission of a packet. The RTL8139C(L) can re-transfer data ifthe Tx FIFO underruns and can also transmit the packet to the wiresuccessfully even though the Tx FIFO underruns. That is, whenTSD<TUN>=1, TSD<TOK>=0 and ISR<TOK>=1 (or ISR<TER>=1).13R/W O WN O WN: The RTL8139C(L) sets this bit to 1 when the Tx DMA operationof this descriptor was completed. The driver must set this bit to 0 whenthe Transmit Byte Count (bit0-12) is written. The default value is 1.12-0R/W S IZE D escriptor Size: The total size in bytes of the data in this descriptor. Ifthe packet length is more than 1792 byte (0700h), the Tx queue will beinvalid, i.e. the next descriptor will be written only after the OWN bit ofthat long packet's descriptor has been set.5.3 ERSR: Early Rx Status Register (Offset 0036h, R)B it R/W S ymbol D escription7-4--R eserved3R E RGood E arly Rx Good packet: This bit is set whenever a packet is completelyRTL8139C(L) Preliminaryreceived and the packet is good. This bit is cleared when writing 1 to it, 2R E RBad E arly Rx Bad packet: This bit is set whenever a packet is completelyreceived and the packet is bad. Writing 1 will clear this bit.1R E ROVW E arly Rx OverWrite: This bit is set when the RTL8139C(L)'s localaddress pointer is equal to CAPR. In the early mode, this is differentfrom buffer overflow. It happens that the RTL8139C(L) detected an Rxerror and wanted to fill another packet data from the beginning addressof that error packet. Writing 1 will clear this bit.0R E ROK E arly Rx OK: The power-on value is 0. It is set when the Rx byte countof the arriving packet exceeds the Rx threshold. After the whole packetis received, the RTL8139C(L) will set ROK or RER in ISR and clearthis bit simultaneously. Setting this bit will invoke a ROK interrupt.5.4 Command Register (Offset 0037h, R/W)B it R/W S ymbol D escription7-5--R eserved4R/W R ST R eset: Setting to 1 forces the RTL8139C(L) to a software reset statewhich disables the transmitter and receiver, reinitializes the FIFOs,resets the system buffer pointer to the initial value (Tx buffer is atTSAD0, Rx buffer is empty). The values of IDR0-5 and MAR0-7 andPCI configuration space will have no changes. This bit is 1 during thereset operation, and is cleared to 0 by the RTL8139C(L) when the resetoperation is complete.3R/W R E R eceiver Enable2R/W T E T ransmitter Enable1--R eserved0R B UFE B uffer Empty: Rx Buffer Empty. There is no packet stored in the Rxbuffer ring.5.5 Interrupt Mask Register (Offset 003Ch-003Dh, R/W)B it R/W S ymbol D escription15R/W S ERR S ystem Error Interrupt: 1 => Enable, 0 => Disable.14R/W T imeOut T ime Out Interrupt: 1 => Enable, 0 => Disable.13R/W L enChg C able Length Change Interrupt: 1 => Enable, 0 => Disable.12-7--R eserved6R/W F OVW R x FIFO Overflow Interrupt: 1 => Enable, 0 => Disable.5R/W P UN/LinkChg P acket Underrun/Link Change Interrupt: 1 => Enable, 0 => Disable.4R/W R XOVW R x Buffer Overflow Interrupt: 1 => Enable, 0 => Disable.3R/W T ER T ransmit Error Interrupt: 1 => Enable, 0 => Disable.2R/W T OK T ransmit OK Interrupt: 1 => Enable, 0 => Disable.1R/W R ER R eceive Error Interrupt: 1 => Enable, 0 => Disable.0R/W R OK R eceive OK Interrupt: 1 => Enable, 0 => Disable.5.6 Interrupt Status Register (Offset 003Eh-003Fh, R/W)B it R/W S ymbol D escriptionRTL8139C(L) Preliminary 15R/W S ERR S ystem Error: Set to 1 when the RTL8139C(L) signals a system error onthe PCI bus.14R/W T imeOut T ime Out: Set to 1 when the TCTR register reaches to the value of theTimerInt register.13R/W L enChg C able Length Change: Cable length is changed after Receiver isenabled.12 - 7--R eserved6R/W F OVW R x FIFO Overflow5R/W P UN/LinkChg P acket Underrun/Link Change: Set to 1 when CAPR is written but Rxbuffer is empty, or when link status is changed.4R/W R XOVW R x Buffer Overflow: Set when receive (Rx) buffer ring storageresources have been exhausted.3R/W T ER T ransmit (Tx) Error: Indicates that a packet transmission was aborted,due to excessive collisions, according to the TXRR's setting 2R/W T OK T ransmit (Tx) OK: Indicates that a packet transmission is completedsuccessfully.1R/W R ER R eceive (Rx) Error: Indicates that a packet has either CRC error orframe alignment error (FAE). The collided frame will not be recognizedas CRC error if the length of this frame is shorter than 16 byte.0R/W R OK R eceive (Rx) OK: In normal mode, indicates the successful completionof a packet reception. In early mode, indicates that the Rx byte count ofthe arriving packet exceeds the early Rx threshold.5.7 Transmit Configuration Register (Offset 0040h-0043h, R/W)B it R/W S ymbol D escription31--R eservedHardware Version ID:30-26R HWVERIDB it30B it29B it28B it27B it26B it23R TL8139110000R TL8139A111000R TL8139A-G111001R TL8139B111100R TL8130111110R TL8139C111010R eserved A ll other combination25-24R/W I FG1, 0I nterframe Gap Time: This field allows the user to adjust the interframegap time below the standard: 9.6us for 10Mbps, 960 ns for 100Mbps.The time can be programmed from 9.6 us to 8.4 us (10Mbps) and 960nsto 840ns (100Mbps). Note that any value other than zero will violate theIEEE 802.3 standard.T he formula for the inter frame gap is:10 Mbps8.4us + 0.4(IFG(1:0)) us100 Mbps840ns + 40(IFG(1:0)) ns 23R8139A-G RTL8139A rev.G ID = 1. For others, this bit is 0.22-19--Reserved。

10M以太网接入处理芯片[RTL8029AS]详细技术手册

![10M以太网接入处理芯片[RTL8029AS]详细技术手册](https://img.taocdn.com/s3/m/1762e0eae009581b6bd9eb23.png)

RTL8029ASRealtek PCI Full-Duplex Ethernet Controller with built-in SRAM ADVANCE INFORMATIONREALTEK SEMI-CONDUCTOR CO., LTD.HEAD OFFICE1F, NO. 11, INDUSTRY E. RD. IX, SCIENCE-BASEDINDUSTRIAL PARK, HSINCHU 30077, TAIWAN, R.O.C.TEL:886-3-5780211 FAX:886-3-5776047OFFICE3F, NO. 56, WU-KUNG 6 RD.,TAIPEI HSIEN, TAIWAN, R.O.C.TEL: 886-2-2980098 FAX: 886-2-2980094, 29800971. FEATURES (4)2. GENERAL DESCRIPTION (5)3. PIN CONFIGURATION (6)4. PIN DESCRIPTIONS (7)4.1. S IGNAL T YPE D EFINITION (7)4.2. P OWER P INS (7)4.3. PCI B US I NTERFACE P INS (7)4.4. M EMORY I NTERFACE P INS (INCLUDING BROM, EEPROM) (8)4.5. M EDIUM I NTERFACE P INS (9)4.6. LED O UTPUT P INS (9)5. REGISTER DESCRIPTIONS (10)5.1. G ROUP 1: NE2000 R EGISTERS (10)5.1.1. Register Table (10)5.1.2. Register Functions (12)5.1.2.1. NE2000 Compatible Registers (12)CR: Command Register (00H; Type=R/W) (12)ISR: Interrupt Status Register (07H; Type=R/W in Page0) (13)IMR: Interrupt Mask Register (0FH; Type=W in Page0, Type=R in Page2) (14)DCR: Data Configuration Register (0EH; Type=W in Page0, Type=R in Page2) (14)TCR: Transmit Configuration Register (0DH; Type=W in Page0, Type=R in Page2) (14)TSR: Transmit Status Register (04H; Type=R in Page0) (15)RCR: Receive Configuration Register (0CH; Type=W in Page0, Type=R in Page2) (15)RSR: Receive Status Register (0CH; Type=R in Page0) (15)CLDA0,1: Current Local DMA Registers (01H & 02H; Type=R in Page0) (16)PSTART: Page Start Register (01H; Type=W in Page0, Type=R in Page 2) (16)PSTOP: Page Stop Register (02H; Type=W in Page0, Type=R in Page2) (16)BNRY: Boundary Register (03H; Type=R/W in Page0) (16)TPSR: Transmit Page Start Register (04H; Type=W in Page0) (16)TBCR0,1: Transmit Byte Count Registers (05H & 06H; Type=W in Page0) (16)NCR: Number of Collisions Register (05H; Type=R in Page0) (16)FIFO: First In First Out Register (06H; Type=R in Page0) (16)CRDA0,1: Current Remote DMA Address registers (08H & 09H; Type=R in Page0) (16)RSAR0,1: Remote Start Address Registers (08H & 09H; Type=W in Page0) (16)RBCR0,1: Remote Byte Count Registers (0AH & 0BH; Type=W in Page0) (16)CNTR0: Frame Alignment Error Tally Counter Register (0DH; Type=R in Page0) (16)CNTR1: CRC Error Tally Counter Register (0EH; Type=R in Page0) (17)CNTR2: Missed Packet Tally Counter Register (0FH; Type=R in Page0) (17)PAR0-5: Physical Address Registers (01H - 06H; Type=R/W in Page1) (17)CURR: Current Page Register (07H; Type=R/W in Page1) (17)MAR0-7: Multicast Address Register (08H - 0FH; Type=R/W in Page1) (17)5.1.2.2. RTL8029AS Defined Registers (17)9346CR: 9346 Command Register (01H; Type=R/W except Bit0=R) (18)CONFIG0: RTL8029AS Configuration Register 0 (03H; Type=R) (18)CONFIG1: Reserved (18)CONFIG2: RTL8029AS Configuration Register 2 (05H; Type=R except Bit[7:5]=R/W) (18)CONFIG3: RTL8029AS Configuration Register 3 (06H; Type=R except Bit[6,2:1]=R/W) (19)HLTCLK: Halt Clock Register (09H; Type=W) (20)8029ASID0,1: RTL8029AS ID = 8029H (0E, 0FH; Type=R) (20)5.2. G ROUP 2: PCI C ONFIGURATION S PACE R EGISTERS (20)5.2.1. PCI Configuration Space Table (20)5.2.2. PCI Configuration Space functions (21)VID: Vendor ID Register (01-00H; Type=R) (21)DID: Device ID Register (03-02H; Type=R) (21)RID: Revision ID Register (08H; Type=R) (22)Command: Command Register (05-04H; Type=R except Bit1, 0=R/W) (22)Status: Status Register (07-06H; Type=R) (22)PIFR: Programming InterFace Register (09H; Type=R) (23)SCR: Sub-Class Register (0AH; Type=R) (23)BCR: Base-Class Register (0BH; Type=R) (23)HTR: Header Type Register (0EH; Type=R) (23)LTR: Latency Timer Register (0DH; Type=R) (23)BAR: Base Address Register (13-10H; Type=R/W except Bit4-0=R) (23)SVID: Subsystem Vendor ID Register (2C-2DH; Type=R) (23)SID: Subsystem ID Register (2E-2FH; Type=R) (24)BROMBAR: Boot ROM Base Address Register (33-30H; Type=R/W except Bit12-1=R) (24)ILR: Interrupt Line Register (3CH; Type=R/W) (24)IPR: Interrupt Pin Register (3DH; Type=R) (24)6. FUNCTION DESCRIPTION (25)6.1. RTL8029AS C ONFIGURATION P ROCESS (25)6.2. 9346 C ONTENTS (26)6.2.1 Detail values of 9346 CONFIG2-3 & 8029ASID0-1 bytes (26)6.2.2 ID PROM Contents (27)6.3. L OCAL M EMORY B US C ONTROL (28)6.4. F LOW C ONTROL (28)6.4.1. Control Frame Transmission (28)6.4.2. Control Frame Reception (28)6.5. LED B EHAVIORS (29)6.5.1 LED_TX: Tx LED (29)6.5.2 LED_RX: Rx LED (29)6.5.3 LED_CRS=LED_TX+LED_RX: Carrier Sense LED (30)6.5.4 LED_COL: Collision LED (30)6.5.5 LED Output States in Power Down Modes (31)6.6. L OOPBACK D IAGNOSTIC O PERATION (31)6.6.1. Loopback operation (31)(1) CRC enabled (CRC bit in TCR=0) (32)(2) CRC disabled (CRC bit in TCR=1) (32)6.6.2. To Implement Loopback Test (32)(1) To verify the integrity of data path (32)(2) To verify CRC logic (32)(3) To verify the address recognition function (33)(4) To Test Cable Connection (33)7. ELECTRICAL SPECIFICATIONS AND TIMINGS (35)7.1. A BSOLUTE M AXIMUM R ATINGS (35)7.2. D.C. C HARACTERISTICS (T C=0¢J TO 70¢J, V CC=5V+5%) (35)7.3. A.C. T IMING C HARACTERISTICS (35)7.3.1. PCI Configuration Read/Write (35)7.3.1.1. Configuration Read (36)7.3.1.2. Configuration Write (36)7.3.2. PCI I/O Read/Write (37)7.3.2.1. PCI I/O Read (37)7.3.2.2. PCI I/O Write (37)7.3.4. Output Timing for PCI Interface (38)7.3.5. Input Timing for PCI Interface (38)7.3.6. Serial EEPROM (9346) Auto-load (39)1. FEATURESm100-pin PQFP¯Pin-to-pin compatible with RTL8029¯16K byte SRAM built in¯Compliance to PCI V2.1¯Programmable PCI Vendor ID and Sub Vendor IDm PCI local bus single-chip Ethernet controllerm Compliant to Ethernet II and IEEE802.3 10Base5, 10Base2, 10BaseTm Supports Full-Duplex Ethernet function to double channel bandwidth¯Support Flow Control(802.3x) to improve network performance in full-duplex modem Supports three level power down modes:- Sleep- Power down with internal clock running- Power down with internal clock haltedm Built-in data prefetch function to improve performancem Built-in 10BaseT transceiverm Provides auto-detect capability between integrated 10BaseT transceiver and Attachment Unit Interface (AUI)m Supports auto polarity correction for 10BaseTm Supports Boot ROM function for PCI busm Supports 8K, 16K and 32K Boot ROM sizem Use 9346 (64*16-bit EEPROM) to store resource configurations and ID parametersm Capable of programming blank 9346 on board for manufacturing conveniencem Supports 4 diagnostic LED pins with programmable outputsP.S. “¯” denotes new feature of RTL8029AS2. GENERAL DESCRIPTIONThe RTL8029AS controller is an NE2000 compatible Ethernet Controller for PCI interface. Taking the benefit of PCI's high throughput rate, the RTL8029AS controller offers a 32-bit data path to highly improve the data transfer rate compared with traditional Ethernet card on ISA, EISA and MCA bus. Due to the additional benefits of PCI, the RTL8029AS controller provides a low maintaining cost network environment without usage barriers. The Auto-configuration function of PCI can relieve the users from pains of taking care the system resource conflict. The RTL8029AS controller also supports full-duplex and power down features. With three levels power down control features, the RTL8029AS controller is made to be an ideal choice of the network device for a GREEN PCI PC system. The full-duplex function enables simultaneously transmission and reception on the twisted-pair link to a full-duplex Ethernet switching hub. This feature not only increases the channel bandwidth from 10 to 20 Mbps but also avoids the performance degrading problem due to the channel contention characteristics of the Ethernet CSMA/CD protocol.The RTL8029AS controller requires no glue logic and integrates with Manchester Encoder/Decoder and 10BaseT transceiver on chip. The built-in 10BaseT transceiver can automatically correct the polarity error on its receiving pair. The RTL8029AS controller also has the capability of auto-sensing for 10Base2 or 10BaseT connection. Four diagnostic LEDs supported by RTL8029AS controller simplify the troubleshooting procedure in a network. Furthermore, The RTL8029AS controller supports 8K, 16K & 32K byte Boot ROM. It can be applied in a workstation without disk to improve the network security and management convenience. Data prefetch function in RTL8029AS controller can enhance the data transmission and highly uplift the network performance without extra fee.3. PIN CONFIGURATION4. PIN DESCRIPTIONS4.1. Signal Type DefinitionP Power pins include VDD and GND.I Input is a standard input-only signal.O It indicates output signal.T/S Tri-State is a bi-directional, tri-state input/output pin.S/T/S Sustained Tri-State is an active low tri-state signal owned and driven by one and only one agent at a time. The agent that drives an S/T/S pin low must drive it highfor at least one clock before letting it float.O/D Open Drain allowed multiple device to share as a wire-OR.4.2. Power Pins Type Description 22, 39, 52,75, 85, 100VDD P+5V DC power11, 17, 34,48, 72, 80,91GND P Ground4.3. PCI Bus Interface Pins Type Descriptions90CLK I Bus Clock provides timing for all transactions on PCI andis an input pin to every PCI device. All bus signals aresampled on the rising edge of CLK and all parameters aredefined with respect to this edge.92-99, 3-10, 20, 21, 23-28, 30-33, 35-38AD31-0T/S Address/Data are multiplexed on the same PCI pins. A bustransaction consists of an address phase followed by one ormore data phases. The address phase is the clock cycle inwhich FRAMEB is asserted. During data phase AD7-0contain the least significant byte(lsb) and AD31-24 containthe most significant byte(msb). Write data is stable andvalid when IRDYB is asserted and read data is stable andvalid when TRDYB is asserted.1, 12, 19,29CBE3-0B T/S Bus Command/Byte Enables are multiplexed on the samePCI pins. During the address phase of a transaction, CBE3-0B define the Bus Command. During the data phase CBE3-0B are used as Byte Enables. The Byte Enables definewhich physical byte lanes carry meaning data. CBE0Bapplies to byte 0(lsb) and CBE3B applies to byte 3(msb).18PAR T/S Parity is even parity across AD31-0 and CBE3-0B. PAR isstable and valid one clock after the address phase. For dataphases PAR is stable and valid one clock after eitherIRDYB is asserted on a write transaction or TRDYB isasserted on a read transaction.13FRAMEB S/T/S Cycle Frame is driven by the current master to indicate thebeginning and duration of an access. FRAMEB is assertedto indicate a bus transaction is beginning. While FRAMEBis asserted, data transfers continue. When FRAMEB isdeasserted, the transaction is in the final data phase.14IRDYB S/T/S Initiator Ready indicates the initiating agent's ability tocomplete the current data phase of the transaction. IRDYBis used in conjunction with TRDYB. A data phase iscompleted on any clock when both IRDYB and TRDYB areasserted. During a write, IRDYB indicates that valid data ispresent on AD31-0. During a read, it indicates the master isprepare to accept data. Wait cycles are inserted until bothIRDYB and TRDYB are asserted simultaneously.15TRDYB S/T/S Target Ready indicates the target's agent's ability tocomplete the current data phase of the transaction. TRDYBis used in conjunction with IRDYB. A data phase iscompleted on any clock when both TRDYB and IRDYB areasserted. During a read, TRDYB indicates that valid data ispresent on AD31-0. During a write, it indicates the target isprepare to accept data. Wait cycles are inserted until bothIRDYB and TRDYB are asserted simultaneously.16DEVSELB S/T/S Device Select, when actively driven, indicates the drivingdevice has decoded its address as the target of the currentaccess. As an input, DEVSELB indicates whether anydevice on the bus has been selected.2IDSEL I Initialization Device Select is used as a chip select forRTL8029AS controller during configuration read and writetransaction.89RSTB I When RSTB is asserted low, the RTL8029AS performs aninternal system hardware reset. RSTB must be held for aminimum of 120 ns periods. RSTB may be asynchronous toCLK when asserted or deasserted. It is recommended thatthe deassertion be synchronous to guarantee clean andbounce free edge.88INTAB O/D Interrupt A is an asynchronous attention signal which isused to request an interrupt.4.4. Memory Interface Pins (including BROM, EEPROM) Type Description49BOEB O Boot ROM chip select. Active low signal, asserted whenBoot ROM is read.50NC-Unused53EECS O9346 chip select. Active high signal, asserted when 9346 isread/write.51, 67-54MA14-0O Boot ROM address bus[57][EESK]O9346 serial data clock[56][EEDI]O9346 serial data input[55][EEDO]I9346 serial data output40-47MD7-0I/O Boot ROM data bus4.5. Medium Interface Pins Type Description82, 81CD+,CD-I This AUI collision input pair carries the differentialcollision input signal from the MAU.84, 83RX+,RX-I This AUI receive input pair carries the differential receiveinput signal from the MAU.77, 76TX+,TX-O This AUI transmit output pair contains differential linedrivers which send Manchester encoded data to the MAU.These outputs are source followers and require 270 ohmpull-down resistors to GND.87, 86TPIN+,TPIN-I This TP input pair receives the 10 Mbits/s differentialManchester encoded data from the twisted-pair wire.73, 74TPOUT+,TPOUT-O This pair carries the differential TP transmit output. Theoutput Manchester encoded signals have been pre-distortedto prevent overcharge on the twisted-pair media and thusreduce jitters.78X1I20Mhz crystal or external oscillator input.79X2O Crystal feedback output. This output is used in crystalconnection only. It must be left open when X1 is driven withan external oscillator.4.6. LED Output Pins Type Description71LED_BNC O This pin goes high when RTL8029AS's medium type is setto 10Base2 mode or auto-detect mode with link test failure.Otherwise, this pin is low. This pin can be used to controlthe power of the DC converter for CX MAU and connectedto an LED to indicate the used medium type.70LED0O When LEDS0 bit (in CONFIG3 register of RTL8029ASPage3) is 0, this pin acts as LED_COL. When LEDS0=1, itacts as LED_LINK.69, 68LED1,LED2O When LEDS1 bit (in CONFIG3 register of RTL8029ASPage3) is 0, these 2 pins act as LED_RX & LED_TXrespectively. When LEDS1=1, these pins act as LED_CRS& MCSB. Please refer to section 6.5 for details of thelightening behavior of all LEDs.5. REGISTER DESCRIPTIONSThe registers in RTL8029AS controller can be roughly divided into two groups by their address and functions -- one for NE2000, the other for PCI Configuration Space.5.1. Group 1: NE2000 RegistersThis group includes 4 pages of registers which are selected by bit PS0 & PS1 in the CR register. Each page contains 16 registers. Besides those registers compatible with NE2000, the RTL8029AS controller defines some registers for software configuration and feature enhancement.5.1.1. Register TableNo (Hex)Page0Page1Page2Page3[R][W][R/W][R][R][W]00CR CR CR CR CR CR01CLDA0PSTART PAR0PSTART9346CR9346CR02CLDA1PSTOP PAR1PSTOP--03BNRY BNRY PAR2-CONFIG0-04TSR TPSR PAR3TPSR--05NCR TBCR0PAR4-CONFIG2CONFIG206FIFO TBCR1PAR5-CONFIG3CONFIG307ISR ISR CURR---08CRDA0RSAR0MAR0---09CRDA1RSAR1MAR1--HLTCLK0A8029ID0RBCR0MAR2---0B8029ID1RBCR1MAR3---0C RSR RCR MAR4RCR--0D CNTR0TCR MAR5TCR--0E CNTR1DCR MAR6DCR8029ASID0-0F CNTR2IMR MAR7IMR8029ASID1-10-17Remote DMA Port18-1F Reset PortNotes: "-" denotes reserved. Registers with names typed in bold italic format are RTL8029AS defined registers and are not supported in a standard NE2000 adapter.Page 0 (PS1=0, PS0=0) Type Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0 00H CR R/W PS1PS0RD2RD1RD0TXP STA STP 01H CLDA0R A7A6A5A4A3A2A1A0 PSTART W A15A14A13A12A11A10A9A8 02H CLDA1R A15A14A13A12A11A10A9A8 PSTOP W A15A14A13A12A11A10A9A8 03H BNRY R/W A15A14A13A12A11A10A9A8 04H TSR R OWC CDH0CRS ABT COL-PTX TPSR W A15A14A13A12A11A10A9A8 05H NCR R0000NC3NC2NC1NC0 TBCR0W TBC7TBC6TBC5TBC4TBC3TBC2TBC1TBC0 06H FIFO R D7D6D5D4D3D2D1D0 TBCR1W TBC15TBC14TBC13TBC12TBC11TBC10TBC9TBC8 07H ISR R/W RST RDC CNT OVW TXE RXE PTX PRX 08H CRDA0R A7A6A5A4A3A2A1A0 RSAR0W A7A6A5A4A3A2A1A0 09H CRDA1R A15A14A13A12A11A10A9A8 RSAR1W A15A14A13A12A11A10A9A8 0AH8029ID0R01010000 RBCR0W RBC7RBC6RBC5RBC4RBC3RBC2RBC1RBC0 0BH8029ID1R01000011 RBCR1W RBC15RBC14RBC13RBC12RBC11RBC10RBC9RBC8 0CH RSR R DFR DIS PHY MPA0FAE CRC PRX RCR W--MON PRO AM AB AR SEP 0DH CNTR0R CNT7CNT6CNT5CNT4CNT3CNT2CNT1CNT0 TCR W---OFST ATD LB1LB0CRC 0EH CNTR1R CNT7CNT6CNT5CNT4CNT3CNT2CNT1CNT0 DCR W-FT1FT0ARM LS LAS BOS WTS 0FH CNTR2R CNT7CNT6CNT5CNT4CNT3CNT2CNT1CNT0 IMR W-RDCE CNTE OVWE TXEE RXEE PTXE PRXE Page 1 (PS1=0, PS0=1) Type Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0 00H CR R/W PS1PS0RD2RD1RD0TXP STA STP 01H PAR0R/W DA7DA6DA5DA4DA3DA2DA1DA0 02H PAR1R/W DA15DA14DA13DA12DA11DA10DA9DA8 03H PAR2R/W DA23DA22DA21DA20DA19DA18DA17DA16 04H PAR3R/W DA31DA30DA29DA28DA27DA26DA25DA24 05H PAR4R/W DA39DA38DA37DA36DA35DA34DA33DA32 06H PAR5R/W DA47DA46DA45DA44DA43DA42DA41DA40 07H CURR R/W A15A14A13A12A11A10A9A8 08H MAR0R/W FB7FB6FB5FB4FB3FB2FB1FB0 09H MAR1R/W FB15FB14FB13FB12FB11FB10FB9FB8 0AH MAR2R/W FB23FB22FB21FB20FB19FB18FB17FB16 0BH MAR3R/W FB31FB30FB29FB28FB27FB26FB25FB24 0CH MAR4R/W FB39FB38FB37FB36FB35FB34FB33FB32 0DH MAR5R/W FB47FB46FB45FB44FB43FB42FB41FB40 0EH MAR6R/W FB55FB54FB53FB52FB51FB50FB49FB48 0FH MAR7R/W FB63FB62FB61FB60FB59FB58FB57FB56Page 2(PS1=1, PS0=0) Type Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 000H CR R/W PS1PS0RD2RD1RD0TXP STA STP01H PSTART R A15A14A13A12A11A10A9A802H PSTOP R A15A14A13A12A11A10A9A803H-04H TPSR R A15A14A13A12A11A10A9A8 -05H|0BH0CH RCR R--MON PRO AM AB AR SEP0DH TCR R---OFST ATD LB1LB0CRC0EH DCR R-FT1FT0ARM LS LAS BOS WTS0FH IMR R-RDCE CNTE OVWE TXEE RXEE PTXE PRXE Page 3(PS1=1, PS0=1) Type Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0 00H CR R/W PS1PS0RD2RD1RD0TXP STA STP 01H9346CR R EEM1EEM0--EECS EESK EEDI EEDOW EEM1EEM0--EECS EESK EEDI-02H-03H CONFIG0R-----BNC00 04H-05H CONFIG2R PL1PL0*FCE*PF--BS1BS0W*PL1PL0*FCE-----06H CONFIG3R-FUDUP LEDS1LEDS0-SLEEP PWRDN-W*-*FUDUP---SLEEP PWRDN-07H TEST1-Reserved08H--Unused09H HLTCLK W HLT7HLT6HLT5HLT4HLT3HLT2HLT1HLT0 0AH TEST2-Reserved0B-0DH--Unused*0EH8029ASID0R00101001*0FH8029ASID1R10000000 Notes: The registers marked with type='W*' can be written only if bits EEM1=EEM0=1.Notes: "*" denotes the bits or registers which are RTL8029AS defined bits or registers and are not supported in RTL8029.5.1.2. Register Functions5.1.2.1. NE2000 Compatible RegistersCR: Command Register (00H; Type=R/W)This register is used to select register pages, enable or disable remote DMA operation and issue commands.Bit Symbol Description7, 6PS1, PS0PS1PS0Register Page Remark000NE2000 compatible011NE2000 compatible102NE2000 compatible113RTL8029ASConfiguration5-3RD2-0RD2RD1RD0Function000Not allowed001Remote Read010Remote Write011Send Packet1**Abort/Complete remote DMA 2TXP This bit must be set to transmit a packet. It is internally reset either after thetransmission is completed or aborted. Writing a 0 has no effect.1STA The STA bit controls nothing. It only reflects the value written to this bit.POWER UP=0.0STP This bit is the STOP command. When it is set, no packets will be received ortransmitted. POWER UP=1.STA STP Function10Start Command01Stop CommandISR: Interrupt Status Register (07H; Type=R/W in Page0)This register reflects the NIC status. The host reads it to determine the cause of an interrupt.Individual bits are cleared by writing a "1" into the corresponding bit. It must be cleared after power up.Bit Symbol Description7RST This bit is set when NIC enters reset state and is cleared when a start command isissued to the CR. It is also set when receive buffer overflows and is cleared whenone or more packets have been read from the buffer.6RDC Set when remote DMA operation has been completed.5CNT Set when MSB of one or more of the network tally counters has been set.4OVW This bit is set when the receive buffer has been exhausted.3TXE Transmit error bit is set when a packet transmission is aborted due to excessivecollisions.2RXE This bit is set when a packet received with one or more of the following errors:- CRC error- Frame alignment error- Missed packet1PTX This bit indicates packet transmitted with no errors.0PRX This bit indicates packet received with no errors.IMR: Interrupt Mask Register (0FH; Type=W in Page0, Type=R in Page2)All bits correspond to the bits in the ISR register. POWER UP=all 0s. Setting individual bits will enable the corresponding interrupts.DCR: Data Configuration Register (0EH; Type=W in Page0, Type=R in Page2) Bit Symbol Description7-Always 16, 5FT1, FT0FIFO threshold select bit 1 and 0.4ARM Auto-initialize Remote0: Send Packet Command not executed.1: Send Packet Command executed.3LS Loopback Select0: Loopback mode selected. Bits 1 and 2 of the TCR must also be programmed forLoopback operation.1: Normal Operation2LAS This bit must be set to zero. NIC only supports dual 16-bit DMA mode.POWER UP =11BOS Byte Order Select0: MS byte placed on MD15-8 and LS byte on MD7-0. (32xxx,80x86)1: MS byte placed on MD7-0 and LS byte on MD15-8. (680x0)0WTS Word Transfer Select0: byte-wide DMA transfer1: word-wide DMA transferTCR: Transmit Configuration Register (0DH; Type=W in Page0, Type=R in Page2) Bit Symbol Description7-5-Always 1.4OFST Collision Offset Enable.3ATD Auto Transmit Disable.0: normal operation1: reception of multicast address hashing to bit 62 disables transmitter,reception of multicast address hashing to bit 63 enables transmitter.2, 1LB1, LB0LB1LB0Mode Remark000Normal Operation011Internal Loopback102External Loopback113External Loopback0CRC The NIC CRC logic comprises a CRC generator for transmitter and a CRCchecker for receiver. This bit controls the activity of the CRC logic. If this bit set,CRC is inhibited by transmitter. Otherwise CRC is appended by transmitter.Conditions CRC Logic ActivitiesCRC Bit Mode CRC Generator CRC Checker0normal enabled enabled1normal disabled enabled0loopback enabled disabled1loopback disabled enabledTSR: Transmit Status Register (04H; Type=R in Page0)This register indicates the status of a packet transmission.Bit Symbol Description7OWC Out of Window Collision. It is set when a collision is detected after a slot time(51.2us). Transmissions are rescheduled as in normal collisions.6CDH CD Heartbeat. The NIC watches for a collision signal (i.e., CD Heartbeat signal) during the first 6.4us of the interframe gap following a transmission. This bit isset if the transceiver fails to send this signal.5-Always 0.4CRS Carrier Sense lost bit is set when the carrier is lost during transmitting a packet.3ABT It indicates the NIC aborted the transmission because of excessive collisions.2COL It indicates the transmission collided with some other station on the network.1-Always 1.0PTX This bit indicates the transmission completes with no errors.RCR: Receive Configuration Register (0CH; Type=W in Page0, Type=R in Page2) Bit Symbol Description7, 6-Always 1.5MON When monitor mode bit is set, received packets are checked for address match, good CRC and frame alignment but not buffered to memory. Otherwise, packetswill be buffered to memory.4PRO If PRO=1, all packets with physical destination address accepted.If PRO=0, physical destination address must match the node address programmedin PAR0-5.3AM If AM=1, packets with multicast destination address are accepted.If AM=0, packets with multicast destination address are rejected.2AB If AB=1, packets with broadcast destination address are accepted.If AB=0, packets with broadcast destination address are rejected.1AR If AR=1, packets with length fewer than 64 bytes are accepted.If AR=0, packets with length fewer than 64 bytes are rejected.0SEP If SEP=1, packets with receive errors are accepted.If SEP=0, packets with receive errors are rejected.RSR: Receive Status Register (0CH; Type=R in Page0)Bit Symbol Description7DFR Deferring. Set when a carrier or a collision is detected.6DIS Receiver Disabled. When the NIC enters the monitor mode, this bit is set and receiver is disabled. Reset when receiver is enabled after leaving the monitormode.5PHY PHY bit is set when the received packet has a multicast or broadcast destination address. It is reset when the received packet has a physical destination address.4MPA Missed Packet bit is set when the incoming packet can not be accepted by NIC because of a lack of receive buffer or if NIC is in monitor mode. IncrementCNTR2 tally counter.3-Always 0.2FAE Frame Alignment Error bit reflects the incoming packet didn't end on a byte boundary and CRC did not match at last byte boundary. Increment CNTR0 tallycounter.1CRC CRC error bit reflects packet received with CRC error. This bit will also be setfor FAE errors. Increment CNTR1 tally counter.0PRX This bit indicates packet received with no errors.CLDA0,1: Current Local DMA Registers (01H & 02H; Type=R in Page0)These two registers can be read to get the current local DMA address.PSTART: Page Start Register (01H; Type=W in Page0, Type=R in Page 2)The Page Start register sets the start page address of the receive buffer ring.PSTOP: Page Stop Register (02H; Type=W in Page0, Type=R in Page2)The Page Stop register sets the stop page address of the receive buffer ring.BNRY: Boundary Register (03H; Type=R/W in Page0)This register is used to prevent overwrite of the receive buffer ring. It is typically used as a pointer indicating the last receive buffer page the host has read.TPSR: Transmit Page Start Register (04H; Type=W in Page0)This register sets the start page address of the packet to the transmitted.TBCR0,1: Transmit Byte Count Registers (05H & 06H; Type=W in Page0)These two registers set the byte counts of the packet to be transmitted.NCR: Number of Collisions Register (05H; Type=R in Page0)The register records the number of collisions a node experiences during a packet transmission.FIFO: First In First Out Register (06H; Type=R in Page0)This register allows the host to examine the contents of the FIFO after loopback.CRDA0,1: Current Remote DMA Address registers (08H & 09H; Type=R in Page0) These two registers contain the current address of remote DMA.RSAR0,1: Remote Start Address Registers (08H & 09H; Type=W in Page0)These two registers set the start address of remote DMA.RBCR0,1: Remote Byte Count Registers (0AH & 0BH; Type=W in Page0)These two registers set the data byte counts of remote DMA.CNTR0: Frame Alignment Error Tally Counter Register (0DH; Type=R in Page0)。

EBT3001串口转以太网芯片基础配置功能详解

EBT3001串口转以太网芯片基础功能介绍以太网芯片网页配置设备内置网页服务器,方便用户通过网页方式设置、查询参数。

Web 服务器的端口可自定义(2-65535),默认:80操作方式(Microsoft Edge 版本94.0.992.50 为例,建议使用谷歌内核浏览器,不支持IE 内核浏览器):1、打开浏览器,地址栏输入设备的IP 地址,例192.168.3.7(IP 地址和电脑需保持同一网段),忘记本机IP 可通过AT 指令和配置软件查询;2、网页弹出主界面,即可查询设置相关参数;3、点击提交在输入正确密钥后可保存配置参数,出厂默认密钥为:123456;4、进度条提示配置进度,配置完成后请勿再次刷新网页(刷新网页再次进入配置模式,可通过重启设备或再次提交进入通讯模式);也可通过配置软件的打开网页配置按键打开。

【注】若修改了端口号,地址输入栏要加上端口号,例如修改网页访问端口为8080,连接网页配置需要在地址栏输入192.168.3.7:8080。

以太网芯片的子网掩码/IP地址配置IP 地址是模块在局域网中的身份识别,在局域网中有唯一性。

因此不能与同局域网的其他设备重复。

模块的IP 地址有静态IP 和DHCP 两种获取方式。

(1)静态IP :静态IP 是需要用户手动设置,设置的过程中注意同时写入IP、子网掩码和网关,静态IP 适合于需要对IP 和设备进行统计并且要一一对应的场景。

优点:接入无法分配IP 地址的设备都能够通过全网段广播模式搜索到,方便统一管理;缺点:不同局域网内网段不同,导致不能进行正常的TCP/UDP 通讯。

(2)动态DHCP :DHCP 主要作用是从网关主机动态的获得IP 地址、网关地址、DNS 服务器地址等信息,从而免去设置IP 地址的繁琐步骤。

适用于对IP 没有什么要求,也不强求要IP 跟模块一一对应的场景。

优点:接入路由器等有DHCP Server 的设备能够直接通讯,减少设置IP 地址网关和子网掩码的麻烦。

以太网PHY芯片

/iawitfkso/blog/item/5b2155c2318598bd8326ac71.html

2011-3-27

以太网PHY芯片_iawitfkso的空间_空间Page 2 of 3

RTL8111(LOM、PCI Express)系列,VIA的VT612*系列等等。 Marvell的88E8001千兆芯片

网卡要与电脑相连接才能正常使用,电脑上各种接口层出不穷,这也造成了网卡所采用的总线接口类型纷呈。此外,提到

总线接口,需要说明的是人们一般将这类接口俗称为“金手指”,为什么叫金手指呢?是因为这类插卡的线脚采用的是镀钛金 (或其它金属),保证了反复插拔时的可*接触,既增大了自身的抗干扰能力又减少了对其他设备的干扰。 为了方便您了解,下面我们就分别来图解一下常见的各种接口类型的网卡。

①ISA接口网卡 ISA是早期网卡使用的一种总线接口,ISA网卡采用程序请求I/O方式与CPU进行通信,这种方式的网络传输速率低,CPU资

●网线接口 在桌面消费级网卡中常见网卡接口有BNC接口和RJ-45接口(类似电话的接口),也有两种接口均有的双口网卡。接口的选择

与网络布线形式有关,在小型共享式局域网中,BNC口网卡通过同轴电缆直接与其它计算机和服务器相连;RJ-45口网卡通过双 绞线连接集线器(HUB)或交换机,再通过集线器或交换机连接其它计算机和服务器。 目前BNC接口这种接口类型的网卡已很少见,主要因为用细同轴电缆作为传输介质的网络就比较少及组网方式问题较多有关。 RJ-45是8芯线,而电话线的接口是4芯的,通常只接2芯线(ISDN的电话线接4芯线);但大家可以仔细看看,其实10M网卡的RJ45插口也只用了1、2、3、6四根针,而100M或1000M网卡的则是八根针都是全的,这也是区别10M和100M网卡的一种方法(见 上图8)。 ●传输介质类型

EBT3001以太网串口服务器芯片模块配置方式简介

EBT3001以太网芯片模块功能及配置方式简介EBT3001以太网芯片产品简介EBT3001以太网芯片是实现串口数据与以太网数据互相转换的串口芯片;该串口转以太网芯片具有多种Modbus网关模式以及MQTT/HTTP物联网网关模式,可满足各类串口设备/PLC 的联网功能。

EBT3001串口转以太网芯片功能特点支持多种工作模式(TCP Server、TCP Client、UDP Server、UDP Client);支持网页设置、配置工具设置、AT 指令设置参数;支持多路Socket 连接;支持多种校验(None、Odd、Even、Mark、Space);支持DHCP 功能;支持DNS 功能、域名解析;支持DNS 服务器地址自定义;支持多种Modbus 网关(简单协议转换、多主机模式、存储型网关、可配置型网关);支持快速接入阿里云、百度云、OneNET、华为云、3.1 版本标准MQTT 服务器;支持HTTP 协议(GET/POST 请求);支持虚拟串口;支持超时重启功能,重启时间自定义;支持短连接功能,短连接间隔时间自定义;支持心跳包、注册包功能;支持缓存清理功能;支持访问外网、局域网;独立设计测试套件,方便用户调试使用;支持在线升级功能。

EBT3001串口转以太网芯片Web设置配置可通过Web 设置方式,自定义设置相关参数。

打开浏览器,在地址栏输入设备IP(默认:192.168.3.7),进入页面,可查询、设置参数,最后点击“提交”菜单等待网页返回成功提示,即可生效。

注意:请勿在正常使用中进入网页配置,可能导致数据丢失,若进入网页配置则需要通过重启才能进入通讯模式。

网页配置初始化密码:123456,可自定义配置,仅支持6 位大小写字母与数值配置。

网页配置需要使用较新内核的浏览器才能正常使用,比如Microsoft Edge(96.0.1054.62)、Google chrome(96.0.4664.110)、Firefox(95.0.2)等。

以太网控制芯片RTL8019AS数据帧分析

N O .2 8

T

技

术

SCI N F 左 T CHN OGYIN M F C E OL F石 AfION

睡自M

以 太 网控 制 芯 片

RTL8019AS

数 据 帧 分 析

目 前基于TCP/ IP 技术的国际互联网(Int ern et )遍布世界的各个角落, 人们正在In ter net 上获得取之不尽的信息和知识, 然而, 具有 海t 信息的In ter et 却因其应用终端大多局 n 限于P C 机、工作站、服务器等昂贵的设备, 严重的限制了Inter et 的应用范围。因此, n 降 低In ter et 应用终端的成本, n 使之简单化、智 能化、“ 傻瓜’ 化已成为人们面临的迫切课题 , 而研制低成本,低功耗的基于TCP / IP 的嵌 入式系统是这一课题的关链所在。一旦墓干 TCP / IP 的嵌人式系统应用到各类家电和工 业设备中, 人们就可以利用Inter et 将信息源 n 和需要控制的设备、仪器用 机械等连接起 具、

实际开始 。

目 标和源地址 表示发送和 接收帧的工作 站的地址, 各占据6 个字节。其中, 标地址 目 可以是单址, 也可以是多点传送或广播地址。 类型/ 长度:占用2 个 字节, 指定接收数据 的高层协议/ 表示紧随其后的以字节为单位

表 l IEF E802 .3 标准帧格式

} ‘ F S 一下D - D A不- 4 一厂Y T

网进行பைடு நூலகம்绍.

的数据段的长度。 数据;IEEE 802 .3 帧在数据段中对接收 数据的上层协议进行规定。如果数据段长度 过小, 使帧的总长度无法达到 64 个字节的最 小值, 那么相应软件将会自动填充数据段, 以 确保整个帧的长度不低于 64 个字节。 帧校脸序列(F SC ) :该序列包含长度为4 个字节的循环1L余校验值(CRC) , 由发送设备 计算产生, 在接收方被重新计算以确定帧在传 送过程中是否被损坏. RTL80I9 AS 网络控制芯片, 它是一种遵 从IEEE802.3 标准的以太网控制芯片.它传愉 数据的格式符合以太网帧标准。但是接收端 的数据帧又不是IEEE802 .3 以太网帧的帧子 集, 往往会给系统的开发者带来困惑 , 造成收 发双方数据的混乱。下面分析 RTL80 19A S 网络控制芯片的发送数据帧和接收数据帧.

以太网PHY芯片之MIIMDIO接口详解

以太⽹PHY芯⽚之MIIMDIO接⼝详解本⽂主要分析MII/RMII/SMII,以及GMII/RGMII/SGMII接⼝的信号定义,及相关知识,同时本⽂也对RJ-45接⼝进⾏了总结,分析了在10/100模式下和1000M模式下的设计⽅法。

MII接⼝提供了MAC与PHY之间、PHY与STA(Station Management)之间的互联技术,该接⼝⽀持10Mb/s与100Mb/s的数据传输速率,数据传输的位宽为4位。

提到MII,就有可能涉及到RS,PLS,STA等名词术语,下⾯讲⼀下他们之间对应的关系。

所谓RS即Reconciliation sublayer,它的主要功能主要是提供⼀种MII和MAC/PLS之间的信号映射机制。

它们(RS与MII)之间的关系如下图:MII接⼝的Management Interface可同时控制多个PHY,802.3协议最多⽀持32个PHY,但有⼀定的限制:要符合协议要求的connector特性。

所谓Management Interface,即MDC信号和MDIO信号。

前⾯已经讲过RS与PLS的关系,以及MII接⼝连接的对象。

它们是通过MII接⼝进⾏连接的,⽰意图如下图。

由图可知,MII的Management Interface是与STA(Station Management)相连的。

接⼝⽀持10Mb/s以及100Mb/s,且在两种⼯作模式下所有的功能以及时序关系都是⼀致的,唯⼀不同的是时钟的频率问题。

802.3要求PHY 不⼀定⼀定要⽀持这两种速率,但⼀定要描述,通过Management Interface反馈给MAC。

下⾯将详细介绍MII接⼝的信号定义,时序特性等。

由于MII接⼝有MAC和PHY模式,因此,将会根据这两种不同的模式进⾏分析,同时还会对RMII/SMII进⾏介绍。

MII接⼝可分为MAC模式和PHY模式,⼀般说来MAC和PHY对接,但是MAC和MAC也是可以对接的。

千兆网卡芯片哪个好

千兆网卡芯片哪个好千兆网卡芯片是一种网络通信设备,广泛应用于计算机、服务器、网络交换设备等领域。

它能够实现高速、稳定、可靠的网络连接,对于现代网络通信至关重要。

在市场上有许多不同品牌和型号的千兆网卡芯片,本文将介绍几个较为知名的千兆网卡芯片,以供参考。

1. Intel I350:Intel I350是Intel公司推出的一款千兆以太网控制器芯片,被认为是千兆网卡芯片中的佼佼者。

它具有出色的性能和稳定性,能够支持高速数据传输和网络流量管理。

该芯片支持电源管理功能,能够提高能效和降低能耗。

此外,Intel I350还支持多种网络协议和安全特性,适用于各种应用场景。

2. Broadcom BCM5709:Broadcom BCM5709是Broadcom公司推出的一款千兆以太网芯片,被广泛应用于服务器等高性能计算设备中。

该芯片具有优异的数据处理能力和网络传输性能,能够支持高速数据传输和低延迟的网络连接。

它还支持多队列和虚拟化技术,能够提高服务器的性能和效率。

3. Realtek RTL8111:Realtek RTL8111是Realtek公司推出的一款千兆以太网芯片,价格相对较低但性能仍然可靠。

该芯片具有良好的兼容性和稳定性,能够实现高速、稳定的网络连接。

它支持流量控制和优先级调度,能够实现灵活的网络流量管理。

此外,RealtekRTL8111还具备较低的功耗和高集成度,适合一些对成本和功耗有一定要求的应用场景。

4. Marvell Yukon:Marvell Yukon是Marvell公司推出的一款千兆以太网芯片,具有高性能、低功耗和高兼容性等特点。

该芯片支持高速网络连接和数据传输,能够实现高效的网络通信。

它采用了先进的电源管理技术,能够在减少能耗的同时提供稳定的网络连接。

综上所述,以上介绍的几款千兆网卡芯片都是市场上较为知名且性能可靠的选择。

在选择千兆网卡芯片时,可以根据具体应用场景和需求进行评估,考虑性能、兼容性、稳定性,以及功耗等因素,选择适合自己需求的千兆网卡芯片。

Broadcom提供业界最丰富的节能以太网芯片解决方案

种 适 合 当地 的 信 号 传 输 方 式 .各 种 传 输 方 式 的投 资 可 联 系

后通过 C MMB 发 信 道 解 调 器 对 接 收 到 的 信 号 进 行 分 发 信 道 分 解 调 解 码 ,还 原 出 C MB复 用 流 。 M

国内设备 厂商进 行性价 比的考量 衄

B od o r a c m提供 业界最丰富 的节能以太 网芯片解决 方案

专有 A tGEE r 技术超越标准 ,使节能网络得 以快速部署 u rEnM o

; 00年 1 月 1 2 1 0 5日 , 全 球 有 线 和 无 线 通 信 半 导 体 市 场 的 领 导 者 B o d o ( 通 )公 司宣 布 ,就 支 持 新 批 准 的 ra c m 博 IE St . 82 3 z 2 1 节 能 以太 网 ( n r y E f in E h r e ,简 称 E E E d 0 .a 一 0 0 E eg fie t ten t c EE)标 准而 言 ,B o d o r a c m拥 有最 丰 富 的可 用 芯片 解 决 方案 。这 些 芯片 解 决方 案 包括 : 涵盖 从 A I级 非 管理 式 到企 业 级和 城域 级 交换 机 的交 换 芯片 ; 口 、4 ' 3 单

盖 整 个 城 市 ,再 用 微 波 天 线 和 降 频 器 接 收 。 具 有 传 输 信 号 信

C MB复 用流经 过有线 分发调 制器进 行分 发信道编 码和 M Q M调制 . A 生成带宽 为 8 H M z的 U H V F有线电视射 频信 号。 F/ H 然后 经过 H C有 线 电视网络 ,发送至 各个 C F MMB发射 站点 ;

M S网 络 .发 送 至 各 个 C MD MMB接 收 站 点 。C MMB接 收 站 点

比较常用的以太网物理层接口芯片---AC101