verilog FIFO序列(深度可调)

systemverilog断言例子(一)

systemverilog断言例子(一)SystemVerilog断言什么是SystemVerilog断言SystemVerilog断言是一种在硬件设计中使用的验证技术,用于检查设计行为和性质的正确性。

断言可以描述设计中的时序序列、性质规则或者约束条件,并在设计运行时进行验证。

SystemVerilog断言的语法SystemVerilog断言采用assert关键字来定义。

断言语句由一个条件表达式和一个可选的信息字符串组成,语法如下:assert condition;assert condition else failure_message;断言实例例子1:检查FIFO写入操作的空闲状态assert (wr_en == 0) |-> (is_empty == 1);上述例子中,断言检查了当写使能信号wr_en为0时,FIFO的空状态is_empty应为1。

如果断言条件不满足,则产生错误。

例子2:验证FIFO读取操作的一致性assert (rd_en == 0) |-> (rd_data === rd_data[$rose (wr_en)]);这个例子中,断言检查了当读使能信号rd_en为0时,已读取的数据rd_data应与最近的写入数据wr_data相等。

使用$rose函数来检测写入使能信号的上升沿。

例子3:检查FIFO写入和读取的顺序assert (wr_en & rd_en) |-> (wr_index <= rd_index);此例中,断言验证了在写入使能信号和读取使能信号同时为1时,写入的索引地址wr_index应小于等于读取的索引地址rd_index。

例子4:检查FIFO的深度不超过上限int depth = 16;assert (wr_en & !rd_en) |-> (wr_index - rd_index < dept h);这个例子中,断言验证了在写使能信号为1且读使能信号为0时,写入的索引地址与读取的索引地址之差应小于FIFO的深度上限。

verilog if语句

verilog if语句Verilog if语句是 Verilog HDL 中的一种常见控制结构,它可以用来控制程序代码的执行流程。

Verilog if 语句和C语言中的if语句有很多相似之处,它们都具有相同的格式和功能,只是在Verilog HDL中使用不同的语法。

Verilog if语句的基本语法格式如下:if(条件表达式) begin 语句1; 语句2; ... end在上面的语法格式中,“if(条件表达式)”部分是Verilog if语句的基本结构,它用来定义条件表达式,如果条件表达式的值为真,则执行begin-end之间的语句,否则将跳过begin-end之间的语句,继续执行后面的语句。

Verilog if语句的条件表达式可以是逻辑表达式、关系表达式或位表达式。

例如,可以使用逻辑表达式A && B 来表示A和B都为真时,才执行begin-end之间的语句;同样可以使用关系表达式A >= B来表示A大于等于B时,才执行begin-end之间的语句;还可以使用位表达式A[3]来表示当A的第三位为1时,才执行begin-end之间的语句。

此外,Verilog if语句还可以支持嵌套,即在if语句内部可以嵌套if语句,以实现复杂的流程控制。

例如,可以使用下面的代码来实现复杂的流程控制:if(条件表达式1) begin 语句1; if(条件表达式2) begin 语句2; end end在上面的代码中,首先会检查条件表达式1,如果条件表达式1的值为真,则执行begin-end之间的语句,如果条件表达式1的值为假,则不执行begin-end之间的语句,而是直接跳过begin-end之间的语句,继续执行后面的语句。

如果条件表达式1的值为真,则会执行begin-end 之间的语句,并且会继续检查条件表达式2,如果条件表达式2的值为真,则会执行begin-end之间的语句,否则会跳过begin-end之间的语句,继续执行后面的语句。

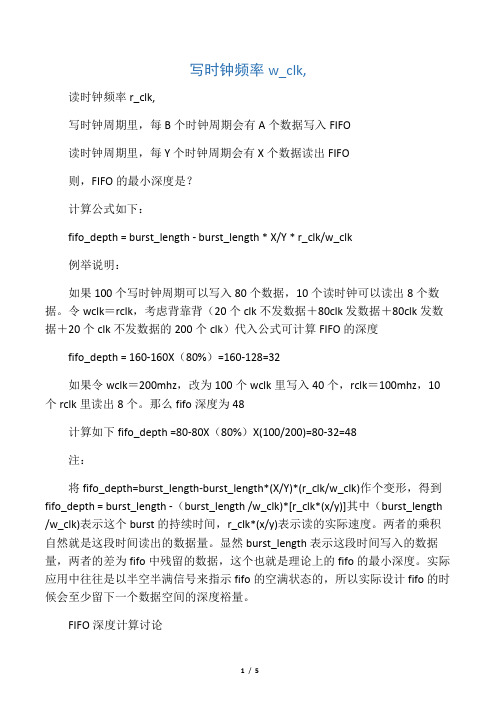

FIFO深度计算方法

通常,为了安全起见,都会多留一些depth的余度

个人觉得,公式应该是这样:

A/(B * w_clk) = X/(Y * r_clk)

fifo_depth = burst_length - burst_length * X/Y * w_clk /r_clk

举例说明:

如果100个写时钟周期可以写入80个数据,10个读时钟可以读出8个数据A/B * w_来自lk = X/Y * r_clk

其次,算出写数据的最大burst_length。考虑最坏情况

比如,如果条件给出,每100个写时钟,写入80个数据,那么在背靠背的情况下,burst_length = 2*80=160

最后,fifo_depth = burst_length - burst_length * X/Y * r_clk/w_clk

32。"

如果令wclk=200mhz,改为100个wclk里写入40个,rclk=100mhz,10个rclk里读出8个。那么fifo深度为48

续上:

讲数据带入公式fifo_depth = burst_length - burst_length * X/Y * r_clk/w_clk

正好也是这个结果。所以我觉得公式是对的。

原帖由windzjy于2007-1-14 17:18发表

个人觉得,公式应该是这样:

A/(B * w_clk) = X/(Y * r_clk)

fifo_depth = burst_length - burst_length * X/Y * w_clk /r_clk

举例说明:

如果100个写时钟周期可以写入80个数据,10个读时钟可以读出...我以前看到过这个公式,是用来计算同步fifo的。

07.IP核之FIFO使用讲解

07.IP核之FIFO使用讲解HELLO FPGA 之软件工具篇第七节IP核之FIFO使用讲解§1.1 IP核之FIFO的介绍FIFO(First Input First Output),即先进先出队列,在计算机中,先进先出队列是一种传统的按序执行方法,先进入的指令先完成并引退,跟着才执行第二条指令。

就好比我们在超市购物,买好了东西之后,我们便会推着我们满满的购物车来到收银台排在结账队伍的最后面等待结账,前面先来排队的客户先得到结账,然后一个一个的结完帐离开,后面后来的客户需要等到前面的客户结完帐之后才能进行结账。

这就是一种先进先出的机制,相信大家还是很容易就能理解的。

FIFO一般用于不同时钟域之间的数据传输,比如FIFO的一端是采样速率比较慢的一个接口,另一端是采样速度比较快的一个接口,假设采样慢的接口速度为1Mhz,而采样快的接口速度为100Mhz,如果我们直接将这两个接口相连接,那么将会出现各种问题,如何解决呢,我们可以在这两个不同的时钟域间采用FIFO来作为数据缓冲。

另外对于不同宽度的数据接口也可以用FIFO,比如一端的接口输出数据是8位的,而另一端输出数据可能是16位的,我们就可以在这两个不同宽度的数据接口中使用FIFO来达到数据匹配的。

同我们之前讲的PLL、ROM和RAM IP核一样,Altera也提供了FIFO IP核,用于实现FIFO存储器。

§1.2 IP核之FIFO的配置介绍完了FIFO IP核,接下来我们来看一下FIFO IP核是如何进行配置的。

大家看,如图7.1所示是FIFOIP核的配置页面。

图7.1 FIFO IP核的配置页面从该图中我们可以看出,FIFO IP核的配置也是很简单的,我们想要配置一个FIFO IP核,也同ROM和RAMIP核一样,只需要完成以下三个步骤:1、Parameter Settings(参数设置);2、EDA(电子设计自动化);3、Summary(总结);1.2.1参数设置(Parameter Settings)首先我们先来介绍一下ParameterSettings(参数设置),在Parameter Settings(参数设置)配置中,我们可以看到它有4个标签,这4个标签分别是Width,Clks,Synchronization、SCFIFO Options、Rdreq Option,Blk Type和Optimization,Circuitry Protection。

实现fifo的关键代码

实现FIFO的关键代码实现该FIFO的关键部分verilog代码如下:(1)将指向下一个读地址的读指针转为格雷码表示:assign rgraynext = (rbinnext >> 1)^rbinnext。

(2)将指向下一个写地址的写指针转为格雷码表示:assign wgraynext = (wbinnext >> 1)^wbinnext。

(3)将读指针用两级触发器与写时钟同步:always @(posedge wclk or negedge wrst_n)if(!wrst_n) {wq2_rptr,wq1_rptr} <= 0;else {wq2_rptr,wq1_rptr} <= {wq1_rptr,rptr};(4)将写指针用两级触发器与读时钟同步:always @(posedge rclk or negedge rrst_n)if(!rrst_n) {rq2_wptr,rq1_wptr} <= 0;else {rq2_wptr,rq1_wptr} <= {rq1_wptr,wptr};(5)产生写满标志:assignwfull_val = (wgraynext == {~wq2_rptr[ADDRSIZE:ADDRSIZE-1],wq2_rptr[ADDRSIZE-2:0]});always @ (posedge wclk or negedge wrst_n)if(!wrst_n) wfull <= 1’b0;else wfull<= wfull_val;(6)产生读空标志:assign rempty_val = (rgraynext == rq2_wptr);always @ (posedge rclk or negedge rrst_n)if(!rrst_n) rempty <= 1’b1;else rempty<= rempty_val;(7)产生FIFO存储单元,并写入、读出数据:always@ (posedge wclk)if(winc&&!wfull) mem[waddr] <= wdataassign rdata = gp15?mem[raddr] : 16’bzzzzzzzzzzzzzzzz;。

verilog的for语句

verilog的for语句Verilog中的for语句是一种循环结构,用于重复执行一段代码块。

在Verilog中,for语句通常用于生成硬件描述,例如生成一系列时钟信号或数据序列。

下面列举了一些常见的Verilog for语句的应用场景:1. 生成时钟信号:在数字电路设计中,时钟信号是非常重要的。

使用for语句可以生成一系列时钟信号,如下所示:```verilogreg clk;integer i;always beginfor (i=0; i<10; i=i+1) begin#10 clk = 1; // 时钟高电平持续10个时间单位#10 clk = 0; // 时钟低电平持续10个时间单位endend```2. 遍历数组元素:在某些情况下,需要对数组进行遍历操作。

使用for语句可以方便地遍历数组元素,如下所示:```verilogreg [7:0] data [0:9];integer i;initial beginfor (i=0; i<10; i=i+1) begindata[i] = i; // 将数组元素赋值为索引值endend```3. 实现计数器:计数器是数字电路中常见的组件,用于计数。

使用for语句可以实现一个简单的计数器,如下所示:```verilogreg [3:0] count;integer i;always @(posedge clk) beginfor (i=0; i<16; i=i+1) beginif (count == i) begincount <= count + 1; // 计数器加1endendend```4. 生成数据序列:在某些应用中,需要生成一系列特定的数据序列。

使用for语句可以方便地生成这些序列,如下所示:```verilogreg [7:0] data;integer i;initial beginfor (i=0; i<256; i=i+1) begindata = i; // 生成0~255的数据序列endend```5. 实现状态机:状态机是数字电路设计中常见的组件,用于描述系统的不同状态和状态之间的转移关系。

ise中fifo的例化模板

ise中fifo的例化模板ISE中的FIFO(First In, First Out)例化模板FIFO(First In, First Out)是一种常见的数据结构,它遵循先进先出的原则,即最早进入队列的元素最先被取出。

在Xilinx的ISE设计工具中,我们可以使用FIFO例化模板快速实现FIFO功能。

本文将介绍如何在ISE中使用FIFO例化模板,并提供详细的操作步骤。

一、简介FIFO是一种常用的数据结构,用于在数字电路中存储和传输数据。

通过FIFO可以实现数据的缓存管理、实时数据传输等功能。

FIFO的主要特点是先进先出,即首先进入队列的元素将首先被读取和移除。

二、FIFO的例化模板在ISE设计工具中,我们可以通过FIFO例化模板快速实现FIFO功能。

FIFO例化模板提供了一种简单、方便的方式来实例化FIFO模块。

下面是一个使用FIFO例化模板的基本步骤:1. 打开ISE设计工具并创建一个新的工程。

2. 在Design视图中右键单击“Hierarchy”面板,并选择“In sert Template”。

3. 在弹出的窗口中,选择“FIFO Generator”模板。

4. 根据需要设置FIFO的参数,如宽度、深度、时钟频率等。

可以根据具体应用需求自定义这些参数。

5. 点击“Generate”按钮生成FIFO模块。

6. 将生成的FIFO模块添加到设计中,并完成连接。

三、实例演示假设我们需要设计一个基于FIFO的数据传输模块。

以下是一些示例代码,展示了如何在ISE中使用FIFO例化模板来实现这个功能。

```verilogmodule fifo_example(input wire clk,input wire rst,input wire [7:0] data_in,output wire [7:0] data_out,input wire read_enable,input wire write_enable);// 实例化FIFO模块fifo #(8, 16) fifo_inst (.clk(clk),.rst(rst),.data_in(data_in),.data_out(data_out),.read_enable(read_enable),.write_enable(write_enable));endmodule```在上述代码中,我们首先实例化了一个宽度为8位,深度为16的FIFO模块。

fifo深度计算公式 推导

fifo深度计算公式推导FIFO深度计算公式及其应用一、引言在计算机科学中,FIFO(First In, First Out)是一种常用的数据结构和调度算法。

在许多应用中,FIFO深度的计算非常重要,它决定了系统的性能和资源利用率。

本文将探讨FIFO深度的计算公式及其应用。

二、FIFO深度的定义FIFO深度是指在一个FIFO队列中能够容纳的最大元素数量。

它决定了队列中元素的排队顺序和处理顺序。

当队列已满时,新的元素将无法入队,因此FIFO深度的大小对系统性能和资源利用率具有重要影响。

三、FIFO深度的计算公式FIFO深度的计算公式如下:FIFO深度 = (数据流的最大速率) * (数据传输延迟)其中,数据流的最大速率是指进入FIFO队列的数据流的最大传输速率;数据传输延迟是指数据从队列中出队的延迟时间。

根据这个公式,我们可以根据系统的特性和需求来计算FIFO深度,以满足对系统性能和资源利用率的要求。

四、FIFO深度的应用1. 带宽规划:根据系统中各个模块的数据流量和传输延迟,可以计算出每个模块的FIFO深度,从而合理规划系统的带宽需求,避免数据丢失和传输延迟过高。

2. 缓冲管理:在网络通信中,为了保证数据的有序传输和流量控制,常常使用FIFO队列进行数据缓冲。

通过计算FIFO深度,可以确定合适的缓冲大小,从而提高数据传输的效率和稳定性。

3. 调度算法:在操作系统中,FIFO调度算法被广泛应用于进程调度和磁盘调度。

通过计算FIFO深度,可以确定合适的调度策略,提高系统的响应速度和资源利用率。

4. 队列管理:在生产制造和物流管理中,常常使用FIFO队列进行物品的排队和处理。

通过计算FIFO深度,可以确定合适的队列长度,从而提高生产效率和物流运输的顺畅性。

五、FIFO深度计算的注意事项1. 数据流的最大速率和数据传输延迟需要准确测量和评估,以保证计算得到的FIFO深度符合实际需求。

2. 在实际应用中,FIFO深度可能受到硬件资源的限制,如存储器容量等。

verilog 时序控制

verilog 时序控制Verilog时序控制是数字电路设计中非常重要的一个概念。

Verilog语言提供了一系列的时序控制语句,可以方便地实现各种时序逻辑和时序控制。

1. 概念时序控制是指数字电路中需要按照时间顺序执行的操作。

在数字电路中,每个操作的执行有其自身的时间限制和执行顺序。

当电路中的各个操作不能按照正确的时序执行时,电路无法正确地工作。

Verilog时序控制语句可以在一定程度上保证电路按照正确的时序执行。

常见的Verilog时序控制语句有if-else语句、case语句和for循环语句等。

2. if-else语句if-else语句是Verilog中最简单的一种时序控制语句。

其语法结构如下:if (条件) begin //条件判断//执行语句块1end else begin //否则执行//执行语句块2end条件为一个逻辑表达式,若表达式成立,则执行语句块1;否则执行语句块2。

例子:module if_else_example(input A, input B, output O);reg output_value;always @(A or B) begin //A或B发生变化时执行if(A & B) begin //当A与B同时为1时output_value = 1;end else begin //否则output_value = 0;endendassign O = output_value; //输出endmodule3. case语句条件为一个数值表达式或逻辑表达式, case语句将根据条件的值,执行对应的语句块。

如果条件值没有匹配的值,则执行默认的语句块。

case语句通常用于多选一的情况。

endmodule4. for循环语句for循环语句允许你在一个固定的次数范围内重复执行相同的代码块。

其语法结构如下:for (初始化; 循环终止条件; 循环迭代) begin//执行语句块end初始化是循环执行前对循环进行初始配置的语句;循环终止条件是循环执行是否停止的条件;循环迭代是在循环周期内循环条件的跟新的语句。

异步FIFO的Verilog HDL设计

异步FIFO的Verilog HDL设计

蔡发志;苏进;叶兵

【期刊名称】《仪器仪表用户》

【年(卷),期】2008(015)003

【摘要】使用异步FIFO(First-In First-Out)同步源自不同时钟域之间的数据是在数字IC设计中经常用的方法.本文对异步FIFO进行了分析和研究,采用格雷码指针将地址指针同步到另一时钟域中,利用将地址分区的方法来判断空满状态.用Verilog HDL硬件描述语言对电路进行RTL级设计,使用Modelshn进行功能仿真,最后用FPGA通过了验证.

【总页数】2页(P68-69)

【作者】蔡发志;苏进;叶兵

【作者单位】合肥工业大学,理学院,合肥,230009;合肥工业大学,理学院,合

肥,230009;合肥工业大学,理学院,合肥,230009

【正文语种】中文

【中图分类】TN432

【相关文献】

1.基于Verilog HDL的异步FIFO设计与实现 [J], 魏芳;刘志军;马克杰

2.异步FIFO的Verilog设计 [J], 卜宪宪

3.基于Verilog HDL语言的32X8 FIFO设计 [J], 夏传红;王祖强;李秀娟

4.基于VERILOG—HDL的简化异步收发器的设计与仿真 [J], 刘丽佳

5.基于Verilog HDL的异步FIFO设计 [J], 李红科;王庆春;余顺园

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

公司招聘时给大家出的题目,我自己也给做了一下,帮助大家学习。

主程序和tb文件都在。

可用modelsim直接仿真。

主程序:

module fifo(

datain,

clk,

reset,

dataout,

wr,

rd,

full,

empty

);

input[7:0]datain;

input clk,reset,rd,wr;

output[7:0]dataout;

output full,empty;

reg[7:0]dataout;

reg rp,wp;

reg[3:0]counter;

reg[7:0]ram[15:0];

wire full,empty;

always@(posedge clk)

if(!reset)

begin

rp=0;

wp=0;

counter=0;

dataout=0;

end

else

case({rd,wr})

2'b00:counter=counter;

2'b01:begin

if(!full)

begin

ram[wp]=datain;

counter=counter+1;

wp=(wp==15)?0:wp+1;

end

end

if(!empty)

begin

dataout=ram[rp];

counter=counter-1;

rp=(rp==15)?0:rp+1;

end

end

2'b11:begin

if(counter==0)

dataout=datain;

else

begin

ram[wp]=datain;

wp=(wp==15)?0:wr+1;

dataout=ram[rp];

rp=(rp==15)?0:rp+1;

end

end

endcase

assign full=(counter==5);

assign empty=(counter==0); endmodule

测试文件(testbench):

`timescale1ns/1ns

module fifo_tb;

reg reset,clk,wr,rd;

reg[7:0]datain;

wire[7:0]dataout;

wire full,empty;

always#50begin

clk=~clk;

datain={$random}%256;

end

initial

begin

reset=0;

clk=0;

{rd,wr}=2'b00;

#100reset=1;

{rd,wr}=2'b01;

#2000{rd,wr}=2'b10;

#2000{rd,wr}=2'b11;

#500$stop;

end

fifo

m0(.datain(datain),.clk(clk),.reset(reset),.dataout(dataout),.wr(wr),.rd(rd),.full(full),.empty(empty)) ;

endmodule。