《微机原理及接口技术》习题集与答案

微机原理与接口技术习题答案

微机原理与接口技术习题答案一、单项选择题1、80486CPU进行算术和逻辑运算时,可处理的信息的长度为 D ;A、32位B、16位C、8位D、都可以2、在下面关于微处理器的叙述中,错误的是 C ;A、微处理器是用超大规模集成电路制成的具有运算和控制功能的芯片B、一台计算机的CPU含有1个或多个微处理器C、寄存器由具有特殊用途的部分内存单元组成,是内存的一部分D、不同型号的CPU可能具有不同的机器指令3、若用MB作为PC机主存容量的计量单位,1MB等于 B 字节;A、210个字节B、220个字节C、230个字节D、240个字节4、运算器在执行两个用补码表示的整数加法时,判断其是否溢出的规则为 D ;A、两个整数相加,若最高位符号位有进位,则一定发生溢出B、两个整数相加,若结果的符号位为0,则一定发生溢出C、两个整数相加,若结果的符号位为1,则一定发生溢出D、两个同号的整数相加,若结果的符号位与加数的符号位相反,则一定发生溢出5、运算器的主要功能是 C ;A、算术运算B、逻辑运算C、算术运算与逻辑运算D、函数运算6、指令ADD CX,55HBP的源操作数的寻址方式是D ;A、寄存器寻址B、直接寻址C、寄存器间接寻址D、寄存器相对寻址7、设SS=3300H,SP=1140H,在堆栈中压入5个字数据后,又弹出两个字数据,则SP=AA、113AHB、114AHC、1144HD、1140H8、若SI=0053H,BP=0054H,执行SUB SI,BP后,则 C;A、CF=0,OF=0B、CF=0,OF=1C、CF=1,OF=0D、CF=1,OF=19、已知BP=0100H,DS=7000H,SS=8000H,80100H=24H,80101H=5AH,70100H=01H,70101H=02H,指令MOV BX,BP执行后,BX=D ;A、0102HB、0201HC、245AHD、5A24H10、实模式下80486CPU对指令的寻址由A 决定;A、CS,IPB、DS,IPC、SS,IPD、ES,IP11、使用80486汇编语言的伪操作指令定义: VAL DB 2 DUP1,2,3 DUP3,2 DUP1,0 则在VAL存储区内前十个字节单元的数据是 D;A、1,2,3,3,2,1,0,1,2,3B、1,2,3,3,3,3,2,1,0,1C、2,1,2,3,3,2,1,0D、1,2,3,3,3,1,0,1,0,112、下列四条指令都可用来使累加器清"0",但其中不能清"进位"位的是C ;A、XOR AL,ALB、AND AL,0C、MOV AL,0D、SUB AL,AL13、若AX=96H,BX=65H,依次执行ADD AX,BX指令和DAA指令后,AL=C ;A、0FBHB、01HC、61HD、0BH14、下列能使CF标志置1的指令是C ;A、CMCB、CLCC、STCD、CLD15、MOV AX,BP+SI隐含使用的段寄存器是D ;A、CSB、DSC、ESD、SS16、计算机工作中只读不写的存储器是 B ;A、DRAMB、ROMC、SRAMD、EEPROM17、下面关于主存储器也称为内存的叙述中,不正确的是 B ;A、当前正在执行的指令与数据都必须存放在主存储器内,否则处理器不能进行处理B、存储器的读、写操作,一次仅读出或写入一个字节C、字节是主存储器中信息的基本编址单位D、从程序设计的角度来看,cache高速缓存也是主存储器18、CPU对存储器或I/O端口完成一次读/写操作所需的时间称为一个 B 周期;A、指令B、总线C、时钟D、读写19、存取周期是指 D ;A、存储器的写入时间B、存储器的读出时间C、存储器进行连续写操作允许的最短时间间隔D、存储器进行连续读/写操作允许的最短时间3间隔20、下面的说法中, C 是正确的;A、EPROM是不能改写的B、EPROM是可改写的,所以也是一种读写存储器C、EPROM是可改写的,但它不能作为读写存储器D、EPROM只能改写一次21、主存和CPU之间增加高速缓存的目的是 A ;A、解决CPU和主存间的速度匹配问题B、扩大主存容量C、既扩大主存容量,又提高存取速度D、增强CPU的运算能力22、采用虚拟存储器的目的是 C ;A、提高主存速度B、扩大外存的容量C、扩大内存的寻址空间D、提高外存的速度23、某数据段位于以70000起始的存储区,若该段的长度为64KB,其末地址是 C ;A、70FFFHB、80000HC、7FFFFHD、8FFFFH24、微机系统中的存储器可分为四级,其中存储容量最大的是 D ;A、内存B、内部寄存器C、高速缓冲存储器D、外存25、下面的说法中, B 是正确的;A、指令周期等于机器周期B、指令周期大于机器周期C、指令周期小于机器周期D、指令周期是机器周期的两倍26、按与存储器的关系,I/O端口的编址方式分为 C ;A、线性和非线性编址B、集中与分散编址C、统一和独立编址D、重叠与非重叠编址27、在中断传送方式下,主机与外部设备间的数据传送通路是 A ;A、数据总线DBB、专用数据通路C、地址总线ABD、控制总线CB28、状态信息是通过 A 总线进行传送的;A、数据B、地址C、控制D、外部29、下列总线中,属于局部总线的是 D ;A、ISAB、EISAC、MCAD、PCI30、利用程序查询方式传送数据时,CPU必须读 A 以判断是否传送数据;A、外设的状态B、DMA的请求信号C、数据输入信息D、外设中断请求31、CPU与外设间数据传送的控制方式有 D ;A、中断方式B、DMA方式C、程序控制方式D、以上三种都是32、CPU与I∕O设备间传送的信号有 D ;A、数据信息B、控制信息C、状态信息D、以上三种都是33、在中断方式下,外设数据输入到内存的路径是 D ;A、外设→数据总线→内存B、外设→数据总线→CPU→内存C、外设→CPU→DMAC→内存D、外设→I∕O接口→CPU→内存34、CPU响应中断请求和响应DMA请求的本质区别是 D ;A、中断响应靠软件实现 B速度慢 C控制简单D、响应中断时,CPU仍然仍控制总线,而响应DMA请求时,CPU要让出总线35、将微处理器、内存储器及I/O接口连接起来的总线是C ;A、片总线B、外总线C、系统总线D、局部总线36、在下列指令中,能使PC机CPU对I/O端口进行读写访问的是 C ;A、中断指令B、串操作指令C、输入输出指令D、传送指令37、下列几种芯片是PC机的常用芯片,它们之中可接管总线控制数据传送的是 D ;A、定时器/计数器芯片B、串行接口芯片C、并行接口芯片D、DMA控制器芯片38、下列几种芯片是PC机的常用I/O接口芯片,它们之中可接管总线控制数据传送的是 BA、8253AB、8237AC、8259AD、8255A39、在下列指令中,能使PC机CPU对I/O端口进行读写访问的是 C ;A、中断指令B、串操作指令C、输入/输出指令D、传送指令40、将微处理器、内存储及I/O接口连接起来的总线是 C ;A、片总线B、外总线C、系统总线D、内部总线41、支持无条件传送方式的接口电路中,至少应包含 D ;A、数据端口,控制端口B、状态端口C、控制端口D、数据端口42、CPU与慢速的外设进行数据传送时,采用 B 方式可提高CPU的效率;A、查询B、中断C、DMAD、无条件传送43、当采用 A 输入操作情况时,除非计算机等待,否则无法传送数据给计算机;A、程序查询方式B、中断方式C、DMA方式D、IOP处理机方式44、微机中地址总线的作用是 C ;A、用于选择存储单元B、用于选择进行信息传输的设备C、用于指定存储单元和I/O设备接口电路的选择地址D、用于确定操作对象45、计算机使用总线结构便于增减外设,同时 C ;A、减少了信息的传输量 B提高了信息的传输量C、减少了信息传输线的条数D、增加了信息传输线的条数46、若AL=3BH,AH=7DH,则AL和AH中的内容相加后,标志CF、SF和OF的状态分别是 AA、0、1、1B、1、1、1C、0、0、0D、1、1、047、若AL=3BH,AH=7DH,则AL和AH中的内容相减后,标志CF、AF和PF的状态分别是 BA、0、0、1B、1、1、1C、0、1、0D、1、0、048、下列有关指令指针寄存器的说法中,哪一个是正确的 B ;A 、IP 存放当前正在执行的指令在代码段中的偏移地址B 、IP 存放下一条将要执行的指令在代码段中的偏移地址C 、IP 存放当前正在执行的指令在存储器中的物理地址D 、IP 存放当前正在执行的指令在存储器中的段地址49、最小模式时,当M/IO -----为低电平时,表示CPU 正在对 B 进行访问;A 、存储器B 、I/O 端口C 、外部存储器D 、EPROM50、下面有关MN/M X ----------的叙述正确的是 CA 、是工作模式选择信号,由CPU 产生,为高电平时CPU 工作在最小模式,为低电平时,CPU 工作在最大模式B 、是工作模式选择信号,由CPU 产生,为低电平时CPU 工作在最小模式,为高电平时,CPU 工作在最大模式C 、是工作模式选择信号,由外部输入,为低电平时CPU 工作在最小模式,为高电平时,CPU 工作在最大模式D 、是工作模式选择信号,由外部输入,为高电平时CPU 工作在最小模式,为低电平时,CPU 工作在最大模式51、某CPU 的主频为250MHZ,则它的时钟周期为 DA 、250nsB 、50nsC 、40nsD 、4ns52、如果访问存储器时使用BP 寻址,则默认的段寄存器是 DA 、CSB 、ESC 、DSD 、SS53、某单元在数据段中,已知DS=1000H,偏移地址为1200H,则它的物理地址为 BA 、10000HB 、11200HC 、12100HD 、13000H54、某系统中,已知SS=2360H,SP=0800H,若将20H 个字节的数据入栈,则SP 的内容为 DA 、0780HB 、0820HC 、23E20HD 、07E0H55、某系统中,已知建立堆栈时SS=2360H,SP=0800H,经过一段时间后,SP 的内容变为0700H,则堆栈中有多少个字的数据 AA 、80HB 、50HC 、100D 、100H56、在下列伪指令中定义字变量的是 B;A 、DDB 、DWC 、DQD 、DT57、下列指令中,能使AL 的内容固定为偶数的是 C;A、ADD AL,01 HB、OR AL,0FEHC、AND AL,0FEHD、XOR AL,0FEH58、改变 C寄存器的值,可改变堆栈中栈顶元素的位置;A、BPB、IPC、SPD、BX59、加减类运算指令对标志位的状态 A;A、有影响B、部分影响C、无影响D、任意60、当AH= C时,执行INT 21H指令可在屏幕上显示一组字符;A、01HB、02HC、09HD、0AH61、已知VAR DW 1,2,$+2,5,6 若汇编时VAR分配的偏移地址是2010和,则汇编后2014H单元的内容是 D;A、6HB、14HC、5HD、16H62、若某数据段位于存储区68000H~7FFFFH,则该数据段的段基址是 D;A、68000HB、7FFFFHC、6000HD、6800H63、SP的作用是用来指示 A;A、栈顶元素的有效地址B、下一条要执行指令的地址C、下一条要取的指令的地址D、栈底元素的有效地址64、在数据传送指令执行过程中,不能直接与立即数进行传送的是B;A、通用寄存器B、段寄存器C、存储器D、通用寄存器和存储器65、转移类指令对标志位的状态 C;A、有影响B、部分影响C、无影响D、随意66、欲从存储单元取某操作数,可采用 D;A、寄存器寻址、寄存器间接寻址B、立即寻址、直接寻址C、立即寻址、寄存器间接寻址D、寄存器间接寻址、直接寻址67、在指令MOV AX,0 执行后,CPU状态标志位ZF的取值 D;A、为0B、为1C、不确定D、不改变68、已知AL=H,BL=00010101H,执行ADD AL,BL指令后,OF、SF、CF、ZF标志的状态为 B;A、1、0、1、1B、1、1、0、0C、0、0、1、1D、0、1、0、169、下列指令中,错误的是 C;A、MOV BX,OFFSET BUFB、LEA SI,BUFC、LEA DI,OFFSET BUFD、MOV BP,SEG BUF70、输入/输出指令对标志位的状态 C;A、有影响B、部分影响C、无影响D、任意71、用3片8259A级联,最多可管理的中断数是 B ;A、24级B、22级C、23级D、21级72、CPU响应INTR和NMI中断时,相同的必要条件是 A ;A、当前指令执行结束B、允许中断C、当前访问内存结束D、总线空闲73、通常,中断服务程序中的一条STI指令目的是 B ;A、允许低一级中断产生B、开放所有可屏蔽中断C、允许同级中断产生 D允许高一级中断产生74、特殊屏蔽方式要解决的主要问题是 C ;A、屏蔽所有中断B、设置最低优先级C、开放低级中断D、响应同级中断75、对可编程接口芯片进行读/写操作的必要条件是 D .A、RD=0B、WR=0C、RD=0或WR=0D、CS=076、用两只中断控制器8259A级联后,CPU的可屏蔽硬中断可扩大到 D ;A、64级B、32级C、16级D、15级77、在PC机中,启动硬中断服务程序执行的是 B ;A、主程序中安排的中断指令B、中断控制器发出的中断请求信号C、主程序中安排的转移指令D、主程序中安排的调用指令78、如果有多个中断请求同时发生,系统将根据它们的优先级高低,响应优先级最高的中断请求,若要调整响应顺序,则应使用 C ;A、中断嵌套B、中断响应C、中断屏蔽D、中断向量79、当系统发生某个事件时,CPU暂停现行程序的执行转去执行相应程序的过程,称为 B ;A、中断请求B、中断响应C、中断嵌套D、中断屏蔽80、8086/8088CPU采用 B 方式,保证在有多个中断源的中断系统中,确定一个中断源并转入相应的中断服务程序;A、中断向量B、向量中断C、优先排队D、并行工作81、运算器由很多部件组成,其核心部分是 B ;A、数据总线B、算术逻辑单元C、累加器D、多路开关82、在一般的微处理器中, D 包含在CPU中;A、内存B、输入/输出单元C、磁盘驱动器D、算术逻辑单元83、80486CPU的标志寄存器中,OF标志表示运算结果的 C 情况;A、进/借位B、符号C、溢出D、辅助进位84、若某数据段位于存储区38000H~47FFFH,则该数据段的段基址为 D ;A、38000HB、47FFFHC、3000HD、3800H85、程序设计中所使用的地址是 A ;A、逻辑地址B、有效地址C、物理地址D、段基址86、80X86执行程序时,对存储器进行访问时,物理地址可由 B 组合产生;A、SS和IPB、CS和IPC、DS和IPD、CS和BP87、某处理器与内存进行数据交换的外部数据总线为32位,它属于 C;A、8位处理器B、16位处理器C、32位处理器D、64位处理器88、在堆栈操作中,隐含使用的通用寄存器是 D ;A、AXB、BXC、SID、SP89、主要决定微机性能的是 AA、CPUB、耗电量C、质量D、价格90、十进制负数–38的八位二进制补码是 BA、01011011BB、BC、BD、01011010B91、设AL=7FH,要使AL=80H,应使用下列哪一条指令 D ;A、AND AL,80HB、OR AL,80HC、XOR AL,80HD、NOT AL92、在执行十进制调整指令 DAA,DAS之前必须将结果存放于 C 中;A、AXB、AHC、ALD、BL93、下列指令执行后影响标志位的是 C ;A、MOVB、PUSHC、ADDD、XCHG94、唯一能对应存储单元的地址是 A ;A、物理地址B、端口地址C、有效地址D、逻辑地址95、计算机能直接执行的语言是 A ;A、机器语言B、汇编语言C、高级语言D、程序设计语言96、需采用先进后出原则操作的存储区是 D ;A、寄存器组B、地址缓冲器C、数据寄存器D、堆栈区97、寄存器SP用于对 B 的操作;A、空闲单元B、堆栈单元C、数据单元D、指令单元98、若BX=1000H,DS=2000H,21000H=12H,21001H=34H,执行LEA SI,BX指令后,SI寄存器的内容是C ;A、1234HB、3412HC、1000HD、0010H99、若AL=80H,执行 NEG AL指令后,CF和OF标志位的状态分别为 C ;A、0和0B、0和1C、1和0D、1和1100、若要完成AX7/2运算,则在下列四条指令之后添加 C 指令; MOV BX,AX ;MOV CL,3 ;SAL AX,CL ;SUB AX,BX ;A、ROR AX,1B、SAL AX,1C、SAR AX,1D、DIV AX,2101、计算机的主内存有3K字节,则内存地址寄存器需 C 位就足够;A、10B、11C、12D、13102、若256KB的SRAM具有8条数据线,那么它具有 B 地址线;A、10B、18C、20D、32103、可以直接存取1M字节内存的微处理器,其地址线需 C 条;A、8B、16C、20D、24104、规格为4096×8的存储芯片4片,组成的存储体容量为 C ;A、4KBB、8KBC、16KBD、32KB105、一个有16字的数据区,其起始地址为70A0:DDF6H,则该数据区末字单元的物理地址为 B ;A、14E96HB、7E814HC、7E7F6HD、7E816H106、某微型计算机可直接寻址64M字节的内存空间,其CPU的地址总线至少应有 D 条;A、20B、30C、16D、26107、对于地址总线为32位的微处理器来说,其直接寻址范围可达 D ;A、64MBB、256MBC、512MBD、4GB108、通常高速缓存是由快速 A 组成;A、SRAMB、DRAMC、EEPROMD、Flash109、CPU在执行指令的过程中,每完成一次对存储器或I/O端口的访问过程,称为 B ;A、时钟周期B、总线周期C、总线读周期D、总线写周期110、某CPU有32条地址线,与之相连的一个I/O芯片的口地址为210H~21FH,则该I/O芯片的片选信号至少应由 D 条地址线译码后产生;A、16B、10C、4D、6111、设某一个单元的物理地址是54321H,则正确的逻辑地址表示为 CA、4321H:50000HB、54320H:1HC、5430H:0021HD、5432H:00001H112、如果一个程序在执行前CS=1000H,IP=2000H,该程序的起始地址是 BA、3000HB、12000HC、21000HD、1000H113、如果一个堆栈从地址1250H:0100H开始,SP=0050,则SS的段地址是 BA、12600HB、1260HC、1265HD、125BH114、若已知X补=B,Y补=01001010B,则X – Y 补= AA、BB、BC、BD、溢出115、下列描述正确的是 B ;A、汇编语言仅由指令性语句组成B、汇编语言包括指令性语句和伪指令语句C、指令性语句和伪指令语句的格式是完全相同的D、指令性语句和伪指令语句需经汇编程序翻译成机器代码后才能执行116、下列指令中不属于逻辑运算指令的是 B;A、XORB、CWDC、NOTD、OR117、假定DX=B,CL=3,CF=1,则执行指令SHL DX,CL后,DX的值为 D;A、005CHB、0017HC、1700HD、05C8H118、下列指令中不会改变指令指针寄存器内容的是 A;A、MOVB、JMPC、CALLD、RET119、伪指令ENDP告诉汇编程序 B;A、宏定义结束B、过程定义结束C、段定义结束D、过程运行结束120、利用DOS系统功能调用的9号AH=9功能,显示一个字符串,其入口参数应为 A;A、DS:DX=字符串首地址B、DS:DX=字符串末地址C、CS:DX=字符串首地址D、CS:DX=字符串末地址121、PC机中,确定硬中断的服务程序入口地址的是 C ;A、主程序中的调用指令B、主程序中的转移指令C、中断控制器发出的类型码D、中断控制器中的中断服务寄存器122、8086/8088 CPU的引脚中,接有硬中断信号的引脚有 C ;A、15个B、8个C、2个D、1个123、设8259A当前最高优先级为IR5,如果要使该中断在下一循环中变为最低优先级,则OCW2应设为 C ;A、 B、C、 D、01100101124、欲读取8259A的IMR内容,可 D ;A、先向8259A写入OCW3;然后读8259A的奇地址B、直接读8259A的偶地址C、先向8259A写入OCW3;然后读8259A的偶地址D、直接读8259A的奇地址125、80486CPU响应中断时,自动压入堆栈的信息是 D ;A、AX,BX,CX,DX的内容B、AX,CX的内容C、CS,IP,SP的内容D、CS,IP,标志寄存器的内容126、实模式下,80486管理的内存空间中,地址为00000H~003FFH中存放着 DA、用户程序代码B、BIOS代码C、DOS系统代码D、中断向量表127、设某中断服务程序在中断向量表的地址为:0:70H,则该中断的中断类型码应是 D ;A、35HB、18HC、1BHD、1CH128、下列引起CPU程序中断的四种情况中, C 需要由硬件提供中断类型码;A、INTOB、NMIC、INT RD、INT n129、实模式下,对于80486微机系统,其中断类型码为18H的中断向量从内存中物理地址为 D 开始存放,共占个字节;A、00072H,4B、00048H,2C、00030H,2D、00060H,4130、若8259工作在自动循环方式下,当前IR3上的中断请求已执行并返回,则8个中断源中优先级最高的是 A ;A、IR4B、IR2C、IR3D、IR0131、8259A应用中,需对IR5,IR3进行屏蔽,操作命令字OCW1应写入 B ;A、D7HB、28HC、53HD、35H132、中断向量可以提供 C ;A、被选中设备的起始地址B、传送数据的起始地址C、中断服务程序入口地址D、主程序的断点地址133、非屏蔽中断的中断类型号是 B ;A、1B、2C、3D、4134、通常情况下,一个外中断服务程序的第一条指令是STI,其目的是 C ;A、开放所有屏蔽中断B、允许低一级中断产生C、允许高一级中断产生D、允许同一级中断产生135、执行返回指令,退出中断服务程序,这时返回地址来自 C ;A、ROM区B、程序计数器C、堆栈区D、CPU的暂存寄存器136、实模式下,NMI中断的中断矢量在中断矢量表中的位置是 C ;A、由DOS自动分配B、由程序指定C、固定在已0008H开始的2个字单元中D、固定在中断矢量表表首137、4片8259级联工作,可管理的外部中断源的级数为 D ;A、4B、32C、28D、29138、PC机中为使工作于一般全嵌套方式的8259中断控制器能接受下一个中断请求,在中断服务程序结束处应 C ;A、执行IRET指令B、执行POP指令C、发送EOI命令D、发送OCW3命令139、80486CPU工作在实模式下执行指令INT 30H时,中断服务程序的入口地址存放在以 C 开始的两个字节单元中;A、00120HB、00090HC、000C0HD、00060H140、下列说法中,错误的是 C ;A、8259A的自动EOI方式只适用于不出现多重中断的场合;B、8259A的初始化结束后,在写入OCW2之前,它按完全嵌套方式工作;C、在PC/XT下不能扩展新的8259A;D、8259A的8个中断源的中断向量在中断向量表中是连续存放的;141、微机中控制总线提供 D ;A、来自I/O设备和存储器的响应信号B、所有存储器和I/O设备的时序信号和控制信号C、存储器和I/O设备的地址码D、上述BA142、占用CPU时间最长的数据传送方式是 C ;A、DMAB、中断C、查询D、无条件143、在微型计算机中将各个主要组成部件连接起来,组成一个可扩充基本系统的总线称之为D ;A、外部总线B、内部总线C、局部总线D、系统总线144、现行PC机中,I/O口常用的I/O地址范围是 D ;A、0000H~FFFFHB、0000H~7FFFHC、0000H~3FFFHD、0000H~03FFH145、PC机执行输出指令OUT时,向相应的I/O接口芯片产生的有效控制信号是 C ;A、AENB、IORC、IOWD、ALE146、当M/IO=0, W/R=0时,80486CPU完成的操作为 B ;A、存储器读B、I/O读C、存储器写D、I/O写147、以80486CPU构成的PC机,其系统总线至少应采用 C ;A、EISA总线B、S—100总线C、ISA总线D、PC/XT总线148、通常一个外设的状态信息在状态端口内占有 A 位;A、1B、2C、4D、8149、按与存储器的关系,I/O端口的编址方式分为 C ;A、线性和非线性编址B、集中与分散编址C、统一和独立编址D、重叠与非重叠编址150、在中断传送方式下,主机与外部设备间的数据传送通路是 A ;A、数据总线DBB、专用数据通路C、地址总线ABD、控制总线CB151、状态信息是通过 A 总线进行传送的;A、数据B、地址C、控制D、外部152、下列总线中,属于局部总线的是 D ;A、ISAB、EISAC、MCAD、PCI153、利用程序查询方式传送数据时,CPU必须读 A 以判断是否传送数据;A、外设的状态B、DMA的请求信号C、数据输入信息D、外设中断请求154、若8259A工作在自动循环方式下,当前IR1上的中断请求已执行并返回,则8个中断源中优先级最高的是 A ;A、IR2B、IR0C、IR7D、IR5155、要屏蔽某外部中断,可通过改变8259A B 的内容实现;A、IRRB、IMRC、ISRD、PR156、欲读取8259A的IRR的内容,必须先写 D 命令字;A、ICW1B、OCW2C、ICW2D、OCW3157、80X86系统中硬件中断服务程序的入口地址可由 C 得到;A、主程序中的调用指令B、主程序中的转移指令158、80486CPU有 C 引脚可接收外部中断请求信号;A、15个B、8个C、2个D、1个159、中断控制器8259A采用级连方式时最多可管理 A 中断源;A、64个B、32个C、16个D、15个160、在下列各种中断中,需由外部电路提供中断类型号的是 D ;A、INTOB、INT nC、NMID、INTR161、台微型计算机的型号是奔四800,则其中800的含义是 DA、CPU中有800个寄存器B、CPU中有800个运算器C、该微机的内存为800MBD、时钟频率为800MHZ162、算机内部,一切信息的存取,处理和传送都是以 D 形式进行;A、EBCDIC码B、ASCII码C、十六进制编码D、二进制编码163、位PC机中整数的有效范围是 DA、- 32768―32767B、- 32767―32767C、0―65535D、- 32768―32767或0―65535164、 C 表示中,二进制数B表示十进制数–1A、原码B、反码C、补码D、BCD码165、位的二进制数的补码形式表示一个带符号数,它能表示的整数范围是 DA、-127—+127B、-128—+128C、-127—+128D、-128—+127166、机中运算器和控制器合称为 AA、CPUB、ALUC、主机D、ENIAC167、位的个人计算机,一个字节Byte由 B 位bit组成;A、4B、8C、16D、32168、机器中浮点数的表示格式如下:151****1100当尾数用补码,阶码阶码基数为2,尾数以规格化数表示用补码表示时,- 123 . 625的表示形式为A ;A、010B、010C、001D、110169、能上,8086的CPU由 C 两部分组成;A、SP、ALUB、控制器、FLAGSC、EU、BIUD、EU、ALU170、存器FLAGS中存放两类标志,即 B ;A、符号标志、溢出标志B、控制标志、状态标志C、方向标志、进位标志D、零标志、奇偶标志171、在保护模式下,代码段的段基址存在于 D中;A、段选择符B、指令指针寄存器C、段寄存器D、段描述符172、查表指令XLAT规定,待查表的首址应存入 D中;A、BPB、SIC、DID、BX173、取的某一条指令的偏移地址由 D提供;A、SIB、BPC、SPD、IP174、寄存器间接寻址方式中,操作数在 C中;A、通用寄存器B、堆栈C、主存单元D、段寄存器175、运算型指令的寻址和转移型指令的寻址,其不同点在于 A;A、前者取操作数,后者决定程序的转移地址B、后者取操作数,前者决定程序的转移地址C、两者都是取操作数D、两者都是决定程序的转移地址176、JMP WORD PTR DI是 A;A、段内间接转移B、段间间接转移C、段内直接转移D、段间直接转移177、INC指令不影响 B标志;A、OFB、CFC、SFD、ZF178、逻辑移位指令SHL用于 C;A、带符号数乘2B、带符号数除2C、无符号数乘2D、无符号数除2179、算术移位指令SAR用于 B;A、带符号数乘2B、带符号数除2C、无符号数乘2D、无符号数除2180、下列指令中,有语法错误的是 D;A、MOV SI,AXB、IN AL,DXC、XOR AX,1234HD、OUT 210H,AL181、采用高速缓存Cache的目的是 B ;A、提高总线速度B、提高主存速度C、使CPU全速运行D、扩大寻址空间182、堆栈的工作方式是 D ;A、先进先出B、随机读写C、只能读出,不能写入D、后进先出183、EPROM是指 D ;A、随机读写存储器B、可编程只读存储器C、只读存储器D、可擦除可编程只读存储器184、连续启动两次独立的存储器操作之间的最小间隔叫A ;A、存取时间B、读周期C、写周期D、存取周期185、对存储器访问时,地址线有效和数据线有效的时间关系应该是C ;A、数据线较先有效B、二者同时有效C、地址线较先有效D、同时高电平186、微机的内存器可用 A 构成;A、RAM和ROMB、硬盘C、软盘D、光盘187、和外存储器相比,内存储器的特点是 C 〕;A、容量大、速度快、成本低B、容量大、速度慢、成本高C、容量小、速度快、成本高D、容量小、速度快、成本低188、若内存容量为64KB,则访问内存所需地址线 A 条A、16B、20C、18D、19189、若用6264SRAM芯片8K×8位组成128KB的存储器系统,需要 A 片6264芯片;A、16B、24C、32D、64190、若内存容量为64KB,则访问内存所需地址线 A 条;A、16B、20C、18D、19二、判断题1、80486的逻辑段不允许有段的重叠和交叉; F2、在80486的32位标志寄存器中,其每一位都有一定的含义; F3、若一个数据块的起始地址为20A0H:0F6H,则该数据块起始地址的实际地址是21B60H; F4、SP的内容可以不指向堆栈的栈顶; F5、寄存器寻址其运算速度较低; F6、指令MOV AX,BX的源操作数是寄存器寻址方式; F7、对堆栈区的操作必须遵循先进先出的原则; F8、比较两个带符号数的大小,可根据CF标志来判断; F9、逻辑操作符AND,OR,XOR和NOT,只能用于数字表达式; T10、不能给段寄存器赋立即数; T11、OF位可用来表示有符号数的溢出; T12、无条件转移指令只能用于段内直接转移; F13、MOV AX,BP的源操作数的物理地址为16DS+BP; F14、指令MOV DI,OFFSET BXSI是正确的; F15、指令MOV CS,BX是非法的; T16、静态随机存储器中的内容可以永久保存; F17、总线周期是指CPU执行一条指令所需的时间; F18、无论采用何种工艺,动态RAM都是利用电容存储电荷的原理来保存信息的; T19、Cache是一种快速的静态RAM,它介于CPU与内存之间; T20、寻址256M字节内存空间,需28条地址线; T21、字长是描述CPU数据总线宽度的指标; T22、计算机的堆栈是一种特殊的数据存储区,数据存取采用先进先出的原则; F23、当运算结果各位全部为零时,标志ZF=0; F24、逻辑地址不是物理地址,但它是唯一的; F25、指令NOT AX,BX是合法的; F26、MOV BXBP,AX是对的; F27、80486中对堆栈单元的存取操作是以字节为单位的; F28、JMP指令要影响标志位; F29、INC指令影响所有状态标志; F30、欲交换寄存器SI,DI的内容,可用指令XCHG SI,DI实现; T31、CPU中的程序计数器IP中存放的是指令的逻辑地址; T32、两个符号相同的数相减不会产生溢出; T33、汇编程序就是汇编语言程序; F34、相对寻址中的位移量只能用16位表示; F35、EPROM是指可擦除可编程随机读写存储器; T36、某内存模块的地址范围为80000H~0BFFFFH,该模块的容量为256K T37、在查询方式下输入输出时,在I/O接口中设有状态寄存器,通过它来确定I/O设备是否准备好;输入时,准备好表示已满;输出时,准备好表示已空; T38、无条件式的I/O是按先读状态口,再读数据口的顺序传送数据的; T39、I/O数据缓冲器主要用于协调CPU与外设在速度上的差异; T40、查询式输入输出是按先读状态端口,后读/写数据端口的顺序传送数据的; T41、CLD指令是MOVSB指令的使用条件之一; F42、段寄存器间不能直接进行数据传送; T43、要把变量BUFF的有效地址送给BX,可用MOV BX,BUFF指令; F44、当对堆栈段的数据进行操作时,其操作数的有效地址可保存在BP中; T45、TEST指令属于逻辑运算指令; T46、CS和IP都不能作传送指令的目的操作数; T47、连接CPU和外设的接口电路中必须要有状态端口; F48、总线是专门用于完成数据传送的一组信号线; F49、I/O接口的基本功能之一是完成数据的缓冲 ; T50、要实现微机与慢速外设间的数据传送,只能利用查询方式完成; F51、单片8259A最多可接8个中断源; T52、中断服务程序结束时,可用RET指令代替IRET指令返回主程序; F。

《微机原理与接口技术》参考答案完整版

《微机原理与接口技术》习题参考答案习题21.为何说8086CPU是16位CPU?答:16位指的是8086CPU的字长,而字长一般来说和运算器、寄存器、总线宽度一致。

因为8086CPU的内部寄存器、内部运算部件以及内部操作都是按16位设计的,这决定了它的字长为16位。

2.8086CPU由哪两个单元组成?其中,指令队列在哪个单元中,有何作用?答:总线接口单元(Bus Interface Unit,BIU)和执行单元(Execution Unit,EU)。

指令队列在BIU中。

它的作用是当EU在执行指令时,空闲的BIU可以从内存读取后续指令到指令队列,这样就可以将取指令工作和执行指令工作重叠进行,从而提高CPU的工作效率,加快指令的执行速度。

3.8086CPU中8位寄存器和16位寄存器是什么关系?答:8086的通用寄存器包括数据寄存器、指针寄存器和变址寄存器。

其中数据寄存器包含AX、BX、CX、DX四个16位寄存器,但他们每个都可以分开作为两个单独的8位寄存器使用。

8086的指针寄存器和变址寄存器不可分割为8位寄存器。

4.8086CPU中的IP寄存器有何用途?答:IP寄存器是指令指针寄存器,用来存放下一条要执行的指令在代码段中的偏移地址。

在程序运行过程中,IP寄存器始终指向下一条指令的首地址,与CS寄存器联合确定下一条指令的物理地址。

8086就是通过IP寄存器来控制指令序列的执行流程。

5.在标志寄存器中,用于反映运算结果属性的标志位有哪些?它们每一位所表示的含义是什么?答:有CF、PF、AF、ZF、SF、OF。

它们的含义如下:CF:进位标志。

它记录运算时从最高有效位产生的进位值或结果值。

最高有效位有进位或有借位时CF=1,否则CF=0。

PF:奇偶标志。

它记录运算结果的奇偶检验条件。

当结果操作数中“1”的个数为偶数时PF=1,否则PF=0。

AF:辅助进位标志。

在字节运算时,由低半字节(字节的低4位)向高半字节有进位或借位时,AF=1,否则AF=0。

《微型计算机原理与接口技术》(尹建华)习题答案资料讲解

《微型计算机原理与接口技术》(尹建华)习题答案第一章2、156D = 10011100B = 9CH79D = 1001111B = 4FH0.675D = 0.1011B = 0.BH37.164D = 100101.0011B = 25.3H3、136D = 10001000B111010.111B = 3A.EH110010.11B = 62.6Q157Q = 06FH133Q = 910AE7.D2H = 101011100111.11010010B0.468D = 0.0111B4、无符号数:151符号数:-1058421BCD:976、+1原码 = 00000001反码 = 00000001补码= 00000001-1原码 = 10000001反码 = 11111110补码 = 11111111+36原码= 00100100反码 = 00100100补码 = 00100100-36原码= 10100100反码 = 11011011补码 = 11011100-128原码= 1000000010000000反码 = 111111*********补码 = 100000007、⑴ -128⑵ -1⑶ 15⑷ -868、⑴ 0 ~ 255⑵ -127 ~ +127⑶ -32767 ~ +32768 11、34H + 89H无溢出0AFH+ 45H无溢出76H-0FEH无溢出第二章2、1MB,64KB3、不能4、4,1,时钟5、0FFFF0H寄存器名FRIPCSDSSSES指令队列其它寄存器复位状态0000H0000HFFFFH0000H0000H0000H清空0000H6、段基地址和偏移地址1230H:0045H1000H:2345H7、90000H ~ 9FFFFH11、等待周期:8086CPU与慢速的存储器和I/O设备交换信息时,为了防止丢失数据,在总线周期的和之间,插入一些必要的等待状态,用来给予必要的时间补偿。

微机原理及接口技术考试试题及答案

微机原理及接口技术考试试题及答案第一部分:微机原理1. 基本知识部分答:微机是由微处理器、内存、输入输出设备以及系统总线构成的计算机系统。

2. CPU部分答:CPU主要由控制单元和算术逻辑单元组成,控制单元负责解码指令、控制程序流程,算术逻辑单元则负责进行算术和逻辑运算。

3. 存储器部分答:存储器按照存取方式可以分为随机存储器(RAM)和只读存储器(ROM),按照存储介质又可分为内存芯片和磁盘等。

4. 总线部分答:总线包括数据总线、地址总线和控制总线,用于在CPU、存储器和输入输出设备之间传输数据、地址和控制信息。

5. 输入输出部分答:输入输出设备用于将人与计算机之间的信息转换为计算机内部能处理的形式,常见的输入输出设备有键盘、鼠标、显示器和打印机等。

第二部分:接口技术1. 并行接口答:并行接口是指同时传送多个位的接口,常见的并行接口有并行打印接口(LPT接口)和并行通信接口(例如IEEE1284接口)。

2. 串行接口答:串行接口是指逐位传送数据的接口,常见的串行接口有串行打印接口(COM接口)和串行通信接口(例如RS-232C接口)。

3. USB接口答:USB接口是一种通用的外部总线接口,具有热插拔、高速传输和多设备连接等优点。

4. 接口传输速率答:接口传输速率是指单位时间内接口所能传输的数据量,常见的接口传输速率有Mbps、Gbps等。

5. 接口阻抗匹配答:接口阻抗匹配是指信源电路和信宿电路的阻抗之间的匹配关系,目的是提高信号传输的质量。

第三部分:考试试题1. 选择题:(1)微机是由以下哪些部分构成的?A. CPU、内存、输入输出设备B. CPU、显卡、硬盘C. 内存、硬盘、显示器D. CPU、显卡、键鼠(2)CPU由以下哪些单元构成?A. 控制单元和算术逻辑单元B. 存储单元和控制单元C. 控制单元和输入输出单元D. 算术逻辑单元和输入输出单元2. 简答题:(1)请简要解释存储器的随机存取特性。

《微机原理与接口技术》习题问题详解(1)

《微机原理与接口技术》习题答案一、单项选择题1、80486CPU进展算术和逻辑运算时,可处理的信息的长度为( D )。

A、32位B、16位C、8位D、都可以2、在下面关于微处理器的表示中,错误的答案是( C ) 。

A、微处理器是用超大规模集成电路制成的具有运算和控制功能的芯片B、一台计算机的CPU含有1个或多个微处理器C、存放器由具有特殊用途的局部存单元组成,是存的一局部D、不同型号的CPU可能具有不同的机器指令3、假如用MB作为PC机主存容量的计量单位,1MB等于( B )字节。

A、210个字节B、220个字节C、230个字节D、240个字节4、运算器在执行两个用补码表示的整数加法时,判断其是否溢出的规如此为( D )。

A、两个整数相加,假如最高位〔符号位〕有进位,如此一定发生溢出B、两个整数相加,假如结果的符号位为0,如此一定发生溢出C、两个整数相加,假如结果的符号位为1,如此一定发生溢出D、两个同号的整数相加,假如结果的符号位与加数的符号位相反,如此一定发生溢出5、运算器的主要功能是( C )。

A、算术运算B、逻辑运算C、算术运算与逻辑运算D、函数运算6、指令ADD CX,55H[BP]的源操作数的寻址方式是(D )。

A、存放器寻址B、直接寻址C、存放器间接寻址D、存放器相对寻址7、设(SS)=3300H,(SP)=1140H,在堆栈中压入5个字数据后,又弹出两个字数据,如此(SP)=(A )A、113AHB、114AHC、1144HD、1140H8、假如SI=0053H,BP=0054H,执行SUB SI,BP后,如此( C)。

A、CF=0,OF=0B、CF=0,OF=1C、CF=1,OF=0D、CF=1,OF=19、(BP)=0100H,(DS)=7000H,(SS)=8000H,(80100H)=24H,(80101H)=5AH,(70100H)=01H,(70101H)=02H,指令MOV BX,[BP]执行后,(BX)=(D ) 。

微机原理及接口技术课后习题及参考答案

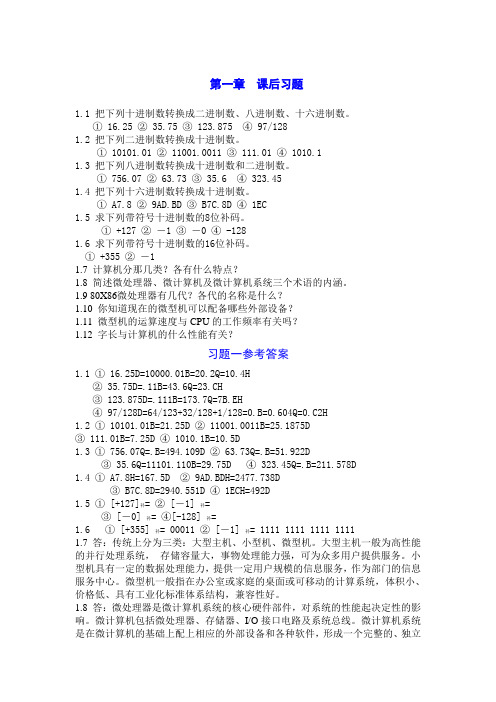

第一章课后习题1.1 把下列十进制数转换成二进制数、八进制数、十六进制数。

① 16.25 ② 35.75 ③ 123.875 ④ 97/1281.2 把下列二进制数转换成十进制数。

① 10101.01 ② 11001.0011 ③ 111.01 ④ 1010.11.3 把下列八进制数转换成十进制数和二进制数。

① 756.07 ② 63.73 ③ 35.6 ④ 323.451.4 把下列十六进制数转换成十进制数。

① A7.8 ② 9AD.BD ③ B7C.8D ④ 1EC1.5 求下列带符号十进制数的8位补码。

① +127 ② -1 ③ -0 ④ -1281.6 求下列带符号十进制数的16位补码。

① +355 ② -11.7 计算机分那几类?各有什么特点?1.8 简述微处理器、微计算机及微计算机系统三个术语的内涵。

1.9 80X86微处理器有几代?各代的名称是什么?1.10 你知道现在的微型机可以配备哪些外部设备?1.11 微型机的运算速度与CPU的工作频率有关吗?1.12 字长与计算机的什么性能有关?习题一参考答案1.1 ① 16.25D=10000.01B=20.2Q=10.4H② 35.75D=.11B=43.6Q=23.CH③ 123.875D=.111B=173.7Q=7B.EH④ 97/128D=64/123+32/128+1/128=0.B=0.604Q=0.C2H1.2 ① 10101.01B=21.25D ② 11001.0011B=25.1875D③ 111.01B=7.25D ④ 1010.1B=10.5D1.3 ① 756.07Q=.B=494.109D ② 63.73Q=.B=51.922D③ 35.6Q=11101.110B=29.75D ④ 323.45Q=.B=211.578D1.4 ① A7.8H=167.5D ② 9AD.BDH=2477.738D③ B7C.8D=2940.551D ④ 1ECH=492D1.5 ① [+127]补= ② [-1]补=③ [-0]补= ④[-128]补=1.6 ① [+355]补= 00011 ② [-1]补= 1111 1111 1111 11111.7 答:传统上分为三类:大型主机、小型机、微型机。

微机原理与接口技术习题及参考答案精选全文完整版

可编辑修改精选全文完整版《微机原理与接口技术》复习题一、填空题1、微型计算机由、、和构成。

2、在8086CPU中,寄存器指向下一条要执行的指令。

3、微型计算机的总线根据功能可分为、和。

4、主存储器和CPU之间增加高速缓冲存储器的目的是。

5、在计算机系统中定时信号一般可以用和两种方法来获得。

6、中断类型码为31H的中断向量存放在从开始的4个存储单元。

7、系统工作于实模式,设BX=4000H,DI=0100H,DS=3100H,在指令MOV AX,[BX+DI]中,源操作数的寻址方式为;物理地址为。

8、在异步传输中,设每个字符对应1个起始位、7个数据位、1个奇偶校验位、1个停止位,如果波特率为1200bps,则每秒钟传输的最大字符数是个。

9、CPU和输入/输出设备之间的信号分为、和三类。

10、CPU的可屏蔽中断受标志的影响,如果允许CPU接受可屏蔽中断请求,则该标志取值为。

11、是微型计算机的核心。

12、在8086CPU中,一个最基本的总线周期有个时钟周期组成。

M/为高电平,表示。

13、在最小模式下,如果8086CPU的引脚IO14、8086CPU有16根数据线和20根地址线,所以可寻址的地址空间最大为字节。

15、存储器扩展有两种方法,分别是扩展和扩展。

16、8086复位时,代码寄存器CS和指令指针寄存器IP分别初始化为和。

17、系统工作于实模式,设BX=4000H,SI=0100H,DS=3100H,在指令MOV DX,[BX+SI]中,源操作数的寻址方式为;物理地址为。

18、9片8259中断控制器组成两级级联,则最多能提供个中断。

19、8086CPU的编程结构包括和。

20、CPU和外设之间的数据传送方式包括、和。

21、当CS=,WR=,RD=,A0=时,CPU设置8259的ICW1。

二、选择题1、8086CPU的指令队列为 ( ) 个字节。

A 2B 4C 6D 82、标志寄存器的标志位ZF=1表示运算结果()。

微机原理与接口技术习题答案

1、(1)1101B=0DH、(2)B=26H、(3)0A9B4H=10100B(4) 0CDH=B3、[97]原=[97]反=[97]补=B[-38]原=B[-38]反=B[-38]补=B[117]原=[117]反=[117]补=B[-1]原=B[-1]反=B[-1]补=B[0]原=[0]反=[0]补=B4、8位定点数[X]原=1.B[X]反=1.B[X]补=1.B[Y]原=[Y]反=[Y]补0.B浮点数[X]=0000B,B[Y]=1111B,B6、略第75页2、略3、略,物理地址为10800H4、由于8086系统的地址的低16位与数据引脚公用,地址信号与数据信号是分时复用这些引脚的。

这样先送出的地址信号可能被后送出的数据信号所代替,因此要有一个地址锁存器来保存先送出来的地址信息。

锁存器主要用来锁存地址的低16位。

5、AH内容送到9100H时,由于执行的是写操作,并且是数据的高8位数据,所以WR、BHE/S7为低电平。

数据由9100H到CPU的AL时,由于执行的是读写操作,并且是数据的低8位数据,所以RD、DT/R6、分时复用是由于CPU引脚数量有限,使得一些引脚起多个作用,在某一时刻传送地址,在另一时刻传送数据,这样的工作方式就称为分时复用的地址/数据总线。

8086CPU分时复用的引脚有:①地址/数据复用的AD0~AD15②地址/状态复用引脚A19/S6~A16/S3③高8位数据允许/状态复用信号引脚BHE/S7分时复用只要解决CPU制造工艺,因为管脚不能太多,引脚过多会使相邻两个引脚间距过小,不利于PCB板的焊接第100页1、(1) 源操作数为立即寻址,源操作数没有物理地址(2)源操作数为直接寻址方式,源操作数物理地址为:10100H(3)源操作数为直接寻址方式,源操作数物理地址为:10050H(4)源操作数为变址寻址方式,源操作数物理地址为:100A0H(5)源操作数为基址加变址寻址方式,源操作数物理地址为:10150H(6)源操作数为相对基址寻址方式,源操作数物理地址为:150B0H(7)源操作数为寄存器寻址方式,源操作数没有物理地址(8)源操作数为立即寻址方式,源操作数物理地址为:CS*10H+IP(9) 源操作数为变址寻址方式,源操作数物理地址为:200A0H(10) 源操作数为相对基址加变址寻址方式,源操作数物理地址为:101A2H2、(1)LEA BX,,[BLOCK+4]MOV DX,[BX](2)LEA BX,,BLOCKMOV DX,4[BX](3)LEA BX,[BLOCK]MOV SI,4MOV DX,[BX+SI]3、B、执行第一个PUSH指令后堆栈C、执行第二个PUSH指令后的堆D、执行第一个POP指令后的堆栈4、(1)、(AX)=1800H (2)、(AX)=100H(3)(BX)=(21200H)=4CAH (4)、(DX)=(21200H)=4CAH (5)、(H)=7856H (6)、(AX)=(21202H)=65B7H 5、执行MOV AX,TABLE 指令后(AX)=1234H执行lea AX,TABLE 指令后(AX)=0048H6、(1)MOV AX,ZADD AX,XADD AX,WMOV Z,AX(2) MOV AX,XADD AX,6MOV BX,RSUB BX,9MOV CX,WSUB CX,AXSUB CX,BXMOV Z,CX7、MOV BX,OFFSET TABLE ;或LEA BX,TABLEMOV AL,CLXLAT8、(1) MOV AX,WMUL XMOV BX,RADD BX,6DIV BXMOV Z,AX(2) MOV W,AXSUB AX,XMOV BL,5DIV BLCBW ;这里商在AL中,余数在AH中,为了使商乘以YMUL YSAL AX,1RCL DX,1MOV Z,AXMOV Z+2,DX9、(1)(DX)=4D2BH (2) (DX)=9A6CH(3)(DX)=35B6h (4)(DX)=1356H(5) (DX)=0D356H (6)=0D5B4H(7) (DX)=9ADBH (8) (DX)=0D5B6H10、(1)CF=1、 SF=0、OF=1、ZF=0(2)CF=0、 SF=1、OF=0、ZF=0(3)CF=0、 SF=1、OF=0、ZF=0(4)CF=0、 SF=1、OF=0、ZF=011、(1)(BX)=009AH (2)(BX)=0061H(3)(BX)=00FBH (4)(BX)=001CH(5)(BX)=0000H (6)(BX)=00E3H12、该程序段是完成将DL寄存器的低4位与AH寄存器的低四位合成一个新的字节(DL寄存器的低4位在前,AH寄存器的低四位在后)13、(1)MOV AX,1234H ;(AX)=1234HMOV CL,4 ;(AX)=1234HROL AX,CL ;(AX)=2341HDEC AX ;(AX)=2340HMOV CX,4 ;(AX)=2340HMUL CX ;(AX)=3400H(2)MOV AX,1234H ;CF=0、SF=0、ZF=0MOV CL,4 ; CF=0、SF=0、ZF=0ROL AX,CL ; CF=0、SF=0、ZF=0DEC AX ; CF=0、SF=0、ZF=0MOV CX,4 ; CF=0、SF=0、ZF=0MUL CX ; CF=1、SF=0、ZF=0(3)AX=3400H,DX=002H14、(1);AX=14C6H,BX=80DCHADD AX,BX ;AX=95A2HJNC L2 ;CF=0,在此转向L2SUB AX,BXJNC L3JMP SHORT L5所以转向L2处执行(2);AX=B568H,BX=54B7HADD AX,BX ;AX=4B0AHJNC L2 ;CF=1SUB AX,BX ; B568HJNC L3 ;CF=1JMP SHORT L5 ;执行该指令所以转向L5处执行 15、MOV CX,5 LEA SI,OLDS LEA DI,NEWS CLR DF NEXT:CMPSBJZ NEWS_LESS LOOP NEXT …… NEWS_LESS : …… 第124页 1、(1)STAD DB 18,-59,0ABH,49H(2)ARRAY DW 1235H,65H,100,0C7H (3)ALPHA DD 12H,H,0EH (4)BETA DB 4 DUP(8), 6 DUP(‘A ’),10 DUP(?), 10 DUP(5,6) (5)STRING DB ‘THIS IS A STR ’ (6)SUM EQU 180 2、3、COUNT 的值为10,他表示X2、X3两个数组所占字节空间数 4、5、字数据3000H 的偏移地址为33H 6、(1)LEA BX,BUF1 ;或MOV BX ,OFFSET BUF1(2)MOV AL ,BYTE PTR [BUF2+4] (3)MOV AL ,24H MOV [BUF3+2],AL(4)COUNT EQU BUF4-BUF2 (5)MOV AX ,BUF2+1 MOV BL ,BUF4 MOV BH ,0 ADD AX ,BX MOV BUF3,AL MOV BUF3+1,AH 7、(1)AX=0A47CH (2)BX=6752H (3)CH=67H (4)DL=34H (5)DH=48、先执行后面的AND 指令,得09h 后执行前面的AND 指令,AX=9AND AX ,9 9、MOV BX ,AX MOV DX ,0 SAL AX ,1 RCL DX ,1ADD AX,BXADC DX,0SAL AX,1RCL DX,1ADD AX,BXADC DX,010、AX=1D00H11、DA TA SEGMENTBUF DW 0ABC3H, 0F7AH, 6E78H FLAG DB ?DA TA ENDSCODE SEGMENTASSUME CS:CODE,DS:DATAMOV AX,DATAMOV DS,AXMOV AX,BUFCMP AX,BUF+2JZ EQ1CMP AX,BUF+4JZ EQ2MOV AX,BUF+2CMP AX,BUF+4JZ EQ2MOV FLAG,0JMP EXITEQ1:CMP AX,BUF+4JNZ EQ2MOV FLAG,2JMP EXITEQ2:MOV FLAG,1EXIT:MOV AH,4CHINT 21HCODE ENDSEND12、AX=85,CX=013、所以N2区的数据依次为:5、6、7、8、914、DA TA SEGMENTDA T1 DW 0ABC3H, 0F7AH, 6E78H,3,6,9,3,0Dw 3,643,5324,324,995,67,6575,68 ;这里定义100个数MAX DW 8000HMIN DW 7FFFHDA TA ENDSCODE SEGMENTASSUME CS:CODE,DS:DATAMOV AX,DA TAMOV DS,AXMOV CX,100MOV SI,OFFSET DA T1LOP:MOV AX,[SI]CMP AX,MAXJL LITTLEMOV MAX,AXJMP NEXTLITTLE:CMP AX,MINJG EQ2MOV MIN,AXNEXT:INC SILOOP LOPMOV AH,4CHINT 21HCODE ENDSEND15、DA TA SEGMENTNUM DB 0ABH,0C3H, 0F7H,3AH, 6EH,78H,3,6,9,3,0DB 3H,63H,53H,24,3,24,99,5,67H,65,75,68 ;这里定义100个数CNT DB $-NUMPLUS DB CNT DUP(?)DA TA ENDSCODE SEGMENTASSUME CS:CODE,DS:DATAMOV AX,DA TAMOV DS,AXMOV CX,CNTMOV SI,OFFSET NUMMOV DI,OFFSET PLUSLOP:MOV AL,[SI]CMP AL,0JL NEXTMOV [DI],ALINC DINEXT:INC SILOOP LOPMOV AH,4CHINT 21HCODE ENDSEND16、DA TA SEGMENTARRAY DB 34H,53H, 063H,3AH, 64H,78,30,60,90,63,80DB 73H,63H,53H,84,83,64,99,65,67H,26,75,68 ;这里定义200个数CNT DB 200NUM90 DB 0NUM80 DB 0NUM70 DB 0NUM60 DB 0NUM DB 0LTEV DB 0DA TA ENDSCODE SEGMENTASSUME CS:CODE,DS:DATAMOV AX,DA TAMOV DS,AXMOV CL,CNTMOV CH,0MOV SI,OFFSET NUMMOV DX,0LOP:MOV AL,[SI]CMP AL,90JL NEXT1INC NUM90JMP NEXTNEXT1:CMP AL,80JL NEXT2INC NUM80JMP NEXTNEXT2:CMP AL,70JL NEXT3INC NUM70JMP NEXTNEXT3:CMP AL,60JL NEXT4INC NUM60JMP NEXTNEXT4:INC NUMJMP NEXTNEXT: MOV AH,0ADD DX,AXINC SILOOP LOPMOV AX,DXDIV CNTMOV LTEV,ALMOV AH,4CHINT 21HCODE ENDSEND17、CODE SEGMENTASSUME CS:CODENEXT :MOV AL,1INT 21HCMP AL,’*’JZ EXITCMP AL,’a’JB NEXTCMP AL,’z’JA NEXTSUB AL,20HMOV DL,ALMOV AH,2INT 21HJMP NEXTEXIT:MOV AH,4CHINT 21HCODE ENDSEND18、DA TA SEGMENTDAT DB 34H,’#’,‘#’,3AH, 64H,78,30,60,90,63,80,”ETEWTRGEG#”,’9’DB 73H,63H,53H,84,83,64,99,65,67H,’#’,75,68 ;这里定义100个数CUT DB 00DA TA ENDSCODE SEGMENTASSUME CS:CODE,DS:DATAMOV AX,DA TAMOV DS,AXMOV CX,100MOV SI,OFFSET DATLOP:MOV AL,[SI]CMP AL,’#’JNZ NEXTINC CUTNEXT:INC SILOOP LOPMOV AX,DXDIV CNTMOV LTEV,ALMOV AH,4CHINT 21HCODE ENDSEND19、DA TA SEGMENTARRAY DB “wdeqwdfvfbrexzacvrgrewafkazc$”DA TA ENDSCODE SEGMENTASSUME CS:CODE,DS:DATAMOV AX,DA TAMOV DS,AXMOV SI,OFFSET NUMMov di,siLOPW: MOV BL,[DI]CMP BL,’$’JZ EXITLOPN: INC SIMOV AL,[SI]CMP AL,’$’JZ EXIT1CMP AL,[DI]JAE NEXTMOV [DI],ALMOV [SI],BLNEXT: INC SIJMP LOPNEXIT1:INC DIJMP LOPWExit:MOV AH,4CHINT 21HCODE ENDSEND20、.MODEL SMALL.DA TADA T1 DB 30H,31H,32H,33H,34H,35H,36H,37H,38H,39H,41H,42H,43H,44H,45,46H DA T2 DB 1,2,3,5,0AH,4,9,0,7,0FH,0BH,4,3,7COUNT DW $-DAT2DA T3 DB 20 DUP(?),'$'.CODEMOV AX,@DA TAMOV DS,AXMOV SI,OFFSET dat2LEA DI,DA T3MOV CX,COUNTMOV BX,OFFSET DA T1LOPW: MOV AL,[SI]XLATMOV [DI],ALINC SIINC DILOOP LOPWLEA DX,DA T3MOV AH,9INT 21HMOV AH,4CHINT 21HEND21、CODE SEGMENTASSUME CS:CODEMOV CX,10MOV BL,00 ;最大值MOV BH,0FH ;最小值LOPN: MOV AH,1INT 21HSUB AL,30HCMP AL,BHJAE ABOVEMOV BH,ALABOVE:CMP AL,BLJBE NEXTMOV BL,ALNEXT:MOV DL,BHADD DL,30HMOV AH,2INT 21HMOV DL,BLADD DL,30HMOV AH,2INT 21HMOV AH,4CHINT 21HCODE ENDSEND第151页1~3略4、由于计算机的CPU速度很高,而主RAM 存储器速度低于微处理器的速度。

《微机原理及接口技术》典型习题参考答案

第2章2.14, 2.27, 2.40, 2.46, 2.49,2.52第5章5.10, 5.14, 5.17,第6章6.2, 6.10, 6.12, 6.14第7章7.9, 7.11第10章10.4, 10.5第2章2.9(1) 读操作占一次总线周期(4个时钟+1个时钟的等待周期)共5个时钟周期每个时钟周期=1/4MHz=0.25us,所以共需要0.25us*5=1.25us(2) 复位至少需要4个时钟周期,4*0.25us=1us复位后内部除CS=FFFFH外,其它寄存器清0。

第一条指令的地址FFFF0H2.10 T1:地址锁存T2:地址撤销,准备数据T3:数据稳定到总线上T4:读写总线上的数据READY2.1(1)数据段首地址DS*16=01500H,堆栈段首地址=SS*16=02500H,所以数据段中存放信息不能与堆栈段重合,故数据段末地址=0250H-1=024FFH即数据段范围:01500H~024FFH(2)堆栈段末地址=SS*16+SP=02500H+1200H=03700H大小为1200H字节=4608字节,可存放16位的字4608/2=2304个(3)代码段由于下限没有其它限制,故最大64KB首地址=06400H,末地址=06400H+64KB-1=06400H+FFFFH=163FFH所以代码段地址范围:06400H~163FFH(4)现在SP=0300H,则原来SP+12=0300H+0CH=030CH注:数的表示范围仅与内部通用寄存器的位数(字长)有关,与外部数据线条数无关。

相同颜色,表示之间有决定关系2.46(1)G=0段界以字节为单位,地址范围:089C0000H~089C003FH大小为3FH+1=40H=64,可容纳64/2=32个汉字(2)G=1段大小=(界+1)*4K=40H*4K=40000H段的最后一页起始地址=089C0000H+40000H=089A0000H,一页有4KB大小,因此段的末地址=089A0000H+FFFH=089A0FFFH注:书上P.64个末地址小加了FFFH(一页的界),结果为0048FFFFH(不是48F000H)2.48(1)DS*16+EAX=20000H+00003000H=00023000H(2)DS*16+ESI=1A000H+00002000H=0001C000H(3)SS*16+ESP=C0000H+0000A000H=000CA000H(4)DS*16+EDI=12390H+0000A000H=0001C390H2.49(1)访问权=11110010B=F2H,段基地址=03000000H,段界=末地址-首地址=1FFFH<10000H 所以G=0,D=1,A VL=1,段描述符=0350F20000001FFFH(2)访问权=11110010B=F2H,段基地址=01000000H,段界=末地址-首地址=01800FFF>10000H, 所以G=1,D=1,A VL=1,段界=大小/4K=1800H=1800H 段描述符=01D0F20000001800H2.51(1)DS=0000000000001011B选中(TI=0)GDT表GDTR=001000001FFFH,GDT首地址=00100000H,段描述符界=1FFFH,可容纳8KB,因此可放8KB/8=1K个描述符。

《微机原理与接口技术》复习练习题与答案

13级《微机原理与接口技术》复习练习题与答案(韶关学院计算机科学学院彭玄璋)一、填空题1、8086/8088 CPU内部结构按功能分为两部分,即由执行单元和总线接口单元组成。

2、若CPU的数据线宽度为16位,则它的字长为16 位;地址线宽度为20位,则它的寻址空间为1MB 。

3、8086CPU为了适应各种应用场合有两种工作模式,即是最小模式和最大模式。

4、8086/8088CPU复位后,CS的内容为0FFFFH ,IP的内容为0000H 。

5、8086的16位标志寄存器包括 6 个状态标志位和3个控制标志位。

6、计算机的I/O端口地址的编址方式有统一编址和独立编址 ,而8086CPU寻址外设采用独立编址方式。

7、CPU与外设间有4种I/O信息传送方式,即无条件传送、查询传送中断传送、直接存储器存取(DMA) 。

8、若某输出外设的I/O接中的数据端口地址为100H,要将字节数据从8086CPU输出到外设的指令是MOV DX,100H 和OUT DX,AL 。

9、响应可屏蔽中断INTR的条件是控制标志IF= 1 。

10、若8253的某一计数器用于输出方波,该计数器的工作方式为 3 ;若该计数器输入频率为100KHz,输出方波频率为10KHz,则计数初值应设为10。

11、串行通信协议分为异步通信和同步通信。

12、波特率是指单位时间内传送二进制数据的位数。

13、8088组成的系统中,存储器分若干个不超过64K字节的段。

14、当8088CPU的INTR端输入一个高电平时, 可屏蔽中断获得了中断请求。

15、8088工作于最小工作模式时,控制总线由CPU本身产生,工作于最大工作模式时,控制总线由总线控制器8288 产生。

16、数据的并行I/O方式是以字节或字为单位进行传送;数据的串行I/O方式是以位为单位进行传送。

17、从地址/数据复用线中分离出地址信息需用逻辑芯片锁存器,地址/数据复用线中的双向数据传送需用逻辑芯片双向缓冲器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《微机原理及接口技术》习题集 一、 填空题 1、16位补码能表示的数的范围是( )到( )。 2、语句MOV AX,ES:[BX]的源操作数是( )寻址方式,其物理地址可以表示为( )。 3、IF为( )标志,当IF=1时,含义为( )。 4、上机时,源文件建立后,对源文件进行( ),产生二进制的( )文件,其扩展名为( )。 5、接口电路与外部设备交换数据的方式可分为( )方式和( )方式。 6、8位补码能表示的数的范围是( )到( )。 7、语句MOV AX,[BX][DI]的源操作数是( )寻址方式,其物理地址可以表示为( )。 8、一中断向量占4个字节单元,其中低地址的两个字节单元存放 ( ),高地址的两个字节单元存放 ( )。 9、80x86 CPU通常从 ( )接收总线请求信号,若其同意放弃总线控制权,则将从 ( )引脚发出总线响应信号。 10、设(CS)=2500H,(DS)=2400H,(SS)=2430H,(ES)=2520H,(BP)=0200H,(SI)=0010H,(DI)=0206H,则指令“MOV AX,[BP+SI+4]”源操作数的物理地址为( );指令“MOV AX,[DI+100H]”源操作数的物理地址为 ( )。

二、 计算题 1、 把下列数化为BCD码形式(8421码)。 (42)10 (10001010)2 (A8)16

2、求下列数的补码(机器长为8位) -117 32

3、已知DS=091DH、AX=1234H、BX=0024H、SI=0012H、[09926H]=00F6H求执行下列指令后CX的值。 XCHG 20H[BX][SI],AX XCHG CX,32H[BX]

4、(AH)=11111111B,(AL)=00000000B计算下列表达式后AH,AL的值 AND AH,F0H TEST AL,40H

5、把下列数化为BCD码形式(8421码)。 (30)10 (00100010)2 (74)16

6、求下列数的补码(机器长为8位) 117 -46 7、已知DS=091DH、BX=0024H、CX=5678H、SI=0012H、[09926H]=00F6H求执行下列指令后AX的值。 XCHG CX,32H[BX] XCHG 20H[BX][SI],AX

8、(AH)=11111111B,(AL)=00000000B计算下列表达式后AH,AL的值 XOR AH,0FH TEST AL,80H

三、 简答题 1、简叙微型计算机的软件组成。

2、汇编程序中如何安全地返回DOS操作系统? 3、什么是地址重叠? 4、什么是硬件非屏蔽中断,它和可屏蔽中断有哪些区别? 5、简述查询方式数据传送的工作原理和优缺点。 6、数据定义伪指令为ARRAY3 DB 2 DUP(2 DUP(1,2),3)画出其在内存中的结构。

7、简叙微型计算机的硬件组成。 8、什么是部分译码法,它和全译码法有哪些区别? 9、什么是中断向量表。 10、简述查询方式数据传送的工作原理和优缺点。 四、 程序设计 1、将存放于XX单元的十进制数23转换为字符串‘23’输出。设输出缓冲区起始地址为BUF。 2、设计一程序要求:不断从键盘接收字符并将其在屏幕上显示,如果输入的是大写英文字符要转换为小写,当输入字符为回车时退出程序。 注:DOS功能调用无回显键盘输入和显示器输出的功能号为07H和01H;回车的ASCII码为0DH。 3、使用模块化的设计方法编写一个等待键盘按键的功能子程序,要求使用寄存器传递参数。(要求写出调用过程的例子) 《微机原理及接口技术》习题集答案 一、 填空题 1、-128 127 2、寄存器间接寻址方式 (ES)*16+(BX) 3、中断允许标志 允许CPU相应外部可屏蔽中断 4、汇编 目标文件 OBJ 5、串行传输方式 并行传输方式 6、-128 127 7、基址变址寻址方式 (DS)*16+(BX)+(DI) 8、中断服务程序入口地址的偏移量 中断服务程序入口地址的段基址 9、HOLD HLDA 10、24514H 24306H

二、 计算题 1、01000010 000100111000 000101101000 2、10001011 00100000 3、(CX)=1234H 4.(AH)=11110000B (AL)=00000000B 5、00110000 00110100 000100010110 6、01110101 11010010 7、(AX)=5678H 8、(AH)=11110000 (AL)=00000000B

三、 简答题 1、答:计算机软件可分为系统软件和应用软件两类。系统软件包括操作系统和语言处理程序。应用软件用来为用户解决具体问题。 2、答:一种方法是使用标准序,将主程序定义成一个远过程,并在程序开始将一段固定代码 PUSH DS MOV AX,0 PUSH AX 另一种方法是使用DOS功能调用,这种方法不需要将主程序定义成一个远过程,在需要返回DOS系统时,使用下列代码 MOV AH,4CH INT 21H 3、答:比如使用部分译码法将存储器与CPU相连时,由于没有使用全部高位地址线产生片选信号,未参加译码的高位地址线不影响片选信号的产生,所以造成逻辑上多个地址对应一个物理内存单元的情况称之为地址重叠。 4、由CPU的NMI引脚出现中断请求信号CPU产生的中断称为非屏蔽中断,与可屏蔽中断相比它不受中断允许标志的限制,并且中断类型码固定为2。 5、答:在查询方式中,CPU首先对外设的状态进行查询,只有外设处于就绪状态时,才与外设进行数据交换,否则,一直处于查询等待状态。 查询方式的优点是硬件接口电路较简单,软件容易实现,传送可靠。但CPU必须花费大量的时间查询外设的工作状态,因而CPU的使用效率不高。 6、 01H 02H 01H 02H 03H 01H 02H 01H 02H 03H

7、答:通用微型计算机的硬件由五个部分组成:中央处理器(CPU);内存储器(RAM、ROM);外存储器(磁盘系统);输入/输出设备;总线(BUS)。 8、答:部分译码法使用片内寻址外的高位地址的一部分译码产生片选信号。和全译码法相比,部分译码法译码电路较简单,但因为没用使用全部高位地址线,所以会产生地址重叠。 9、答:最低1K字节(0000:0000~0000:03FFH区域)有一个表格, 共256个单元,每个单元占4个字节,用以顺序存放256个中断向量。中断向量是中断服务子程序的地址,中断向量的前两个字节为中断服务子程序的偏移量,后两个字节段地址。 10、答:在查询方式中,CPU首先对外设的状态进行查询,只有外设处于就绪状态时,才与外设进行数据交换,否则,一直处于查询等待状态。 查询方式的优点是硬件接口电路较简单,软件容易实现,传送可靠。但CPU必须花费大量的时间查询外设的工作状态,因而CPU的使用效率不高。

四、 程序设计 1、 DATA SEGMENT BUF DW ? XX DB 23 DATA ENDS

CODE SEGMENT ASSUME CS:CODE,DS:DATA START MOV AX,DATA MOV DS,AX ;设置数据段寄存器 MOV CL,10 MOV AH,0 MOV AL,XX DIV CL ADD AL,30H MOV BUF,AL ADD AH,30H MOV [BUF+1],AH MOV AH,4CH INT 21H CODE ENDS END START 2、 CODE SEGMENT ASSUME CS:CODE START: GetChar: MOV AH,7 INT 21H CMP AL,41H JB NotLow ;非小写字符 CMP AL,5AH JA NotLow ADD AL,20H ;大写转小写 NotLow: CMP AL,0DH JE Exit ;遇到回车退出 MOV AH,2 ;打印刚才输入的字符 MOV DL,AL INT 21H JMP GetChar ;接收下一个字符 Exit: MOV AH,4CH INT 21H CODE ENDS END START 3、 功能子程序:

PUBLIC KeyWait FUNCTION SEGMENT ASSUME CS:FUNCTION KeyWait PROC FAR TryAgain: MOV AH,08H INT 21H CMP AL,BL ;BL用来传递参数 JNE TryAgain ;no match RET KeyWait ENDP FUNCTION ENDS END

主调过程: EXTRN KeyWait:FAR CODE SEGMENT ASSUME CS:CODE START: MOV BL,'q' ;传递参数 CALL KeyWait MOV AH,4CH INT 21H CODE ENDS END START