微捷码软件应用于高性能并行计算系统中复杂交换芯片的物理实现

智能计算 HCIA 题库

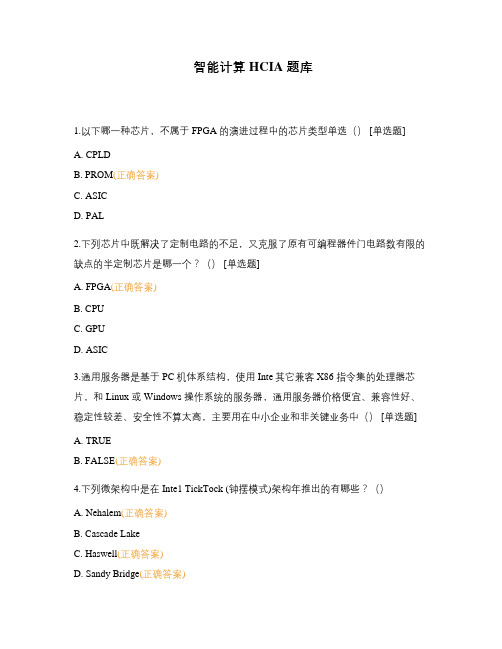

智能计算 HCIA 题库1.以下哪一种芯片,不属于 FPGA 的演进过程中的芯片类型单选() [单选题]A. CPLDB. PROM(正确答案)C. ASICD. PAL2.下列芯片中既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点的半定制芯片是哪一个?() [单选题]A. FPGA(正确答案)B. CPUC. GPUD. ASIC3.通用服务器是基于 PC 机体系结构,使用 Inte其它兼客 X86 指令集的处理器芯片,和 Linux 或 Windows 操作系统的服务器,通用服务器价格便宜、兼容性好、稳定性较差、安全性不算太高,主要用在中小企业和非关键业务中() [单选题]A. TRUEB. FALSE(正确答案)4.下列微架构中是在 Inte1 TickTock (钟摆模式)架构年推出的有哪些?()A. Nehalem(正确答案)B. Cascade LakeC. Haswell(正确答案)D. Sandy Bridge(正确答案)5.智能计算中打破 CPU 边界是指使用服务器集群处理复杂应用() [单选题]A.对B.错(正确答案)6.下列不属于 GPU 典型应用场景的是?() [单选题]A.通用计算,完成复杂逻辑运算(正确答案)B.视频图像处理场景C.HPC 混合应用高吞吐量场景D.HPC 高性能加速场景7.ARM 微处理器已遍及工业控制、消费类电子产品、通信系统、网络系统、无线系统等各类产品市场,下列关于 ARM 架构特点描述错误的是() [单选题]A.支持 16 位、32 位、64 位多种指令集,能很好的兼容从 IOT,终端到云端的各类应用场景B.采用复杂指令集,处理效率高(正确答案)C.大量使用寄存器,大多数数据操作都在寄存器中完成,指令执行速度更快D.同样功能、性能占用的芯片面积小、功耗低、集成度更高,更多的硬件 CPU 核具备更好的并发性能8.下列关于专用计算的说法中错误的是?() [单选题]A.专用计算平台主要是指大型机和小型机B.专用计算平台多使用 RISC 架构C.专用计算平台价格贵、应用少,只有少数企业、少部分应用才用得上计算机D.华为的 KunLun 小型机属于封闭计算架构(正确答案)9.以下关于芯片的说法错误的是() [单选题]A.芯片通常是由半导体制成B.目前芯片普遍使用的半导体组件为二极管(正确答案)C.当前芯片的制程工艺为纳米级D.芯片的本质是集成电路10.下列不属于边缘计算兴起原因的是() [单选题]A.保证断网时的数据可靠性B.实现 IT 资源的按需、按量便用(正确答案)C.考虑到数据隐私,有些应用不希望把数据传输到云端D.工业应用对延迟要求高11.下列处理器类型中属于 RISC 指令集架构的是?()A. ARM(正确答案)B. MIPS(正确答案)C. PowerPC(正确答案)D. X8612.软件是一系列按照特定顺序组织的计算机数据和指令,下列关于软件的说法错误的是() [单选题]A.中间件,是提供系统软件和应用软件之间连接的软件B.系统软件负责管理计算机系统中各种独立的硬件,为正在运行的应用软件提供平台,适配于不同的应用软件C.应用软件是为了某种特定的用途而被开发的软件D.计算机软件划分为系统软件、应用软件和介于这两者之间的中间件(正确答案)13.硬件资源池化是服务器硬件的未来演进趋势,下列哪一项不是其优势() [单选题]A.资源解耦B.单系统独立高效运行(正确答案)C.资源动态分配D.实现智能调度和优化14.计算机软件划分为编程语言、系统软件、应用软件和中间件系统软件为计算机使用提供最基本的功能() [单选题]A.对(正确答案)B.错15.华为为人工智能应用计算平台研制的一系列设备是() [单选题]A.KunLun 系列B.Atlas 系列(正确答案)C.E9000 系列D.TaiShan 系列16.操作系统(Operating System.简称 OS)是管理和控制计算机硬件与软件资源的计算机程序,下列属于其核心功能的是()A.驱动管理(正确答案)B.文件系统管理(正确答案)C.程序管理(正确答案)D.系统呼叫接(正确答案)17.CPU 主频也叫时钟频率,单位是兆赫兹(MHz)或千兆赫兹(GHz),其作用是()[单选题]A.用来表示 CPU 的运算、处理数据的速度(正确答案)B.决定总线数据传输速度C.决定着整块主板的运行速度D.决定 CPU 与内存数据交换的速度18.以下不属于服务器虚拟化软件的是() [单选题]A.FusionComputeB.XenServerC.FusionAccess(正确答案)D.VMware ESXi19.某内存条标识上显示字样"PC3L" ,请问"PC3L"中的"L"表示() [单选题]A.该内存条类型是 UDIMMB.其额定功率为 30WC.其额定电压为 1.35V(正确答案)D.其内存颗粒的位宽为 64*3bit20.按应用领域划分的三类操作系统是()服务器操作系统和(),其中服务器操作系统一般指的是安装在大型计算机上的操作系统,比如 Web 服务器、应用服务器和数据库服务器等()A.开源操作系统B.嵌入式操作系统(正确答案)C.桌面操作系统(正确答案)D.智能卡操作系统21.CPU 是采用的典型的冯诺依曼架构,其中数据信号由输入设备进入控制器,再到达运算器进行计算() [单选题]A.对B.错(正确答案)22.BIOS 提供交互界面让用户进行设置,并将设置值保存在cmos RAM中, 由 RTC 电池供电,保证 CMOS RAM的内容在设备下电后不丢配置() [单选题]A.对(正确答案)B.错23.内存是计算机中重要的部件之一,关于内存定义的说法错误的是() [单选题]A.内存是相对于外存而言的,其主要特点是存取速率快B.内存也被称为内存储器,其作用是用于备份复制并永久保管 CPU 中的运算数据,提高数据的可靠性(正确答案)C.内存又称主存,是 CPU 能直接寻址的存储空间,由半导体器件制成D.计算机在运行时, CPU 会把需要运算的数据调到内存中进行运算,当运算完成后 CPU 再将结果传送出来,内存的运行也决定了计算机的稳定运行24.什么是面向客户的逻辑层软件,比如 ERP,CRM、HR 等() [单选题]A.应用软件B.数据库软件C.业务应用层软件(正确答案)D.中间件25.以下描述 BIOS 运行流程正确的是单选() [单选题]A.上电开机->硬件初始化->CPU 加载 BIOS->加载引导项-> POST 开机硬件自检->处理系统指令B.上电开机->硬件初始化>CPU 加载 BIOS->POST 开机硬件自检->加载引导项->处理系统指令C.上电开机->CPU 加载 BIOS->硬件初始化加载引导项-> POST 开机硬件自检->处理系统指令D.上电开机->CPU 加载 BIOS >硬件初始化->POST 开机硬件自检->加载引导项->处理系统指令(正确答案)26.下列关于 UDIMM, RDIMM, LRDIMM 的对比说法正确的是()A.相比于 RDIMM, LRDIMM 降低了内存总线的负载和功耗,又提供了内存的最大支持容量(正确答案)B. UDIHM 需保证 CPU 到每个内存颗粒之间的传输距离相等,这样并行传输才有效,而这需要较高的制造工艺,因此 UDIMM 在容量和频率上都较低(正确答案)C. UDIMM,无缓冲双列直插内存模块,地址和控制信号不经缓冲器,直接到达DIMM 上的 DRAM 芯片,因此价格便宜(正确答案)D. RDIMM 支持 Buffered 模式和高性能的 Registered 模式,较 UDIMM 更为稳定,同时支持服务器内存最高容量(正确答案)27.iBMC 提供了丰富的接,以下属于的是()A. IPMI 集成接(正确答案)B. Redfish 集成接(正确答案)C. SNMP 集成接(正确答案)D. Web 界面的用户接(正确答案)28.工程师 A 想要查看内存运行的容量、电压、频率等,可以通以下哪种方法实现多选()A.通过 SOL 功能保存系统串(使用 Windows 下 ipmitool 工具,配置 BM IP 和 BMC 密码,连接服务器 BMC网,保存串 10g),搜索"DDR3-或"DDR4-"即可(正确答案)B. Linux 下通过 dmicode -t memory 查询(正确答案)C. 通过 BIOS 查看基本信息(正确答案)D.登陆 iBMC Web 界面查看(正确答案)29. 外频是 CPU 的基准频率,单位是 MHz CPU 的外频直接决定 CPU 与内存数据交换的速度() [单选题]A.对B.错(正确答案)30.RAID6 便用二维校验,支持横向校验或者斜向校验,因此至少需要 N+2 块磁盘() [单选题]A.对(正确答案)B.错31.PaaS 提供了应用程序的开发和运行环境,包括中间件和数据库以下服务器上层软件属于 PaaS 层的软件是()A. KVMB. MySQL(正确答案)C. CRMD. Java(正确答案)32.CPU 的频率有主频、外频、总线频率和倍频,以下关于倍频的说法错误的是单选() [单选题]A. PC 机通常超频操作是针对不锁倍频 CPU 调节倍频,调节倍顷的超频方式比调节外频稳定得多B. CPU 与系统之间数据传输速度是有限的,-味追求高主频而得到高倍频的 CPU 就会出现明显的“瓶颈"效应C.在相同的外频下,倍频越高 CPU 的频率也越高,不受限制(正确答案)D.倍频系数是指 CPU 主频与外频之间的相对比例关系33.智能平台管理接口(IPMI)是种开放标准的硬件管理接口规格,定义了管理子系统进行通信的特定方法() [单选题]A.组合式B.嵌入式(正确答案)C.平铺式D.接式34.以下关于 RAID10 的理解错误的是() [单选题]A.第一级是 RAID1 镜像对,第二级为 RAID OB. RAID10 的硬盘利用率为 50%C. RAID10 是将镜像和条带进行两级组合的 RAID 级别D. RAID10 的读写性能表现一致(正确答案)35.数据库系统一般由数据库、数据库管理系统、和数据库用户几部分组成() [单选题]A.业务应用层系统B.应用程序系统(正确答案)C.数据逻辑系统36.传统 BIOS 专为传统的 16 位处理器定制,寻址能力低下,效能表现很差,而UEFI 可以适用于任何 64 位处理器,寻址能力强很多,效能表现优() [单选题]A.对(正确答案)B.错37.以下 PIN 脚总数为 64 的是 PCIe- () [单选题]A.16xB.1xC.8xD.4x(正确答案)38.挑选硬盘时,需要根据系统槽位数和业务需求容量,选择正确的容量适配下列关于硬盘容量说法正确的是() [单选题]A. NL SAS/SATA 容量一般为 250G 的整数倍, 10K/ 15K SAS 硬盘容股为 500G 的整数倍B. NL SAS/SATA 容量一般为 200G 的整数倍, 10K/15K SAS 硬盘容一股为 300G 的整数倍C. NL SAS/SATA 容量般为 250G 的整数倍, 10K/15K SAS 硬盘容股为 300G 的整数倍(正确答案)D. NL SAS/SATA 容量股为 200G 的整教倍, 10K/15K SAS 硬盘容般为 1T 的整数倍39.以下不属于 iBMC 功能特征的是() [单选题]A.管理硬件虚拟化功能(正确答案)B.故障诊断与管理C.虚拟 KVM 和虚拟媒体D.丰富的管理接口40.网卡按照协议类型分类,分为()A.以太网卡(正确答案)B. IB 网卡(正确答案)C. FC 网卡(正确答案)41.早期硬盘接有 IDE, SCSI 等,随着硬盘技术发展,这些接类型已经消失,当前主流的硬盘使用的接有SATA, SAS, PCIE 等,下列关于 SAS 和 SATA 的说法正确的是() [单选题]A.物理层来说, SAS 接和 SATA 接两者互相兼容, SATA 硬盘可以直接使用在SAS的环境中, SAS 也可以使用在 SATA环境中B. 目前家用类别的移动硬盘多为 SAS 接, SATA 接则为企业级应用C. SAS 是新-代的 SCSI 技术,采用并行技术以获得更高的传输速度并通过缩短连结线改内部空间等D. SAS 可满足高性能、高可靠性的应用, SATA 则满足大容量、非关键业务的应用(正确答案)42.总线技术的发展,PC/XT->ISA 总线->扩展 ISA 总线->AGP 总线->PCI 总线-> PCI-Express,总线() [单选题]A.对B.错(正确答案)43.Inte1 的 QuickPath Interconnect 技术缩写为 QPl.译为快速通道互联用来实现芯片之间的直接互联下列关于 QPI 的说法正确的是() [单选题]A.QPI 另一个亮点就是支持多条系统总线连接, Inte1 称之为 multi-FSBB.一组 QPI 具有 10 条数据传输线,以及发送(TX)和接收方(RO)的时钟信号C.QPI 总线总带宽=每秒传输次数(即 QPI 频率)x 每次传输的有效数据(即16bit/8=2Byte)x 双向(正确答案)D.QPI 是一种基于包传输的串行式高速点对点连接协议采用差分信号与专门的时钟进行传输44.以下对服务器特性的理解,不正确的是单选() [单选题]A.可靠性指产品在尽可能长的时间内保持其所有功能都能够正常提供的能力B.RAS 设计的核心指导理念就是最大程度保证客户业务可持续正常运行C.易用性指系统发生故障后,可尽快完成定位和修复的能力(正确答案)D.可用性指产品在尽可能长的时间内保持其所有功能都能够正常提供的能力45.以哪个组件不属于常见的计算单元() [单选题]A.CPUB.ASICC.NPU(正确答案)D.GPUE.FPGA46.以下是工程师 A 对 CPU 的理解,正确的是多选()A.CPU 的管理能力强,擅长管理和调度,比如据读取,文件管理等等(正确答案)B.相较于 GPU,在数据处理时,CPU 是并行的,所以适合处理大规模数据运算C.CPU 是一台计算机的运算核心和控制核心(正确答案)D.相较其他芯片,CPU 是运算能力最强,核处理数最多47.关于运行在集群外部的服务器,下列说法错误的是单选() [单选题]A.监视集群的健康状况B.这些服务器上的客户端是需要集群感知的集群节点(正确答案)C.可以充当在集群内部运行的应用程序的许可服务器D.充当中央用户账户数据库48.服务器集群具有很强的可伸缩性,随着需求和负荷的增长,一般可以通过以下哪个方式增加集群的性能() [单选题]A.增加集群中组网带宽B.增加集群中单服务器的内存容量C.向集群系统添加新的集群服务器(正确答案)D.更换集群中单服务器的硬盘为高 IO 的固态硬盘49.以下是工程师 A 对 LVS 集群的理解,正确的是()A.LVS 有三种工作方式 LVS-NAT (地址转换)、LVS-DR (直接路由), LVS-TUN (隧道)(正确答案)B.LVS 常用的调度策略有,轮询调度、加权轮询调度、最小连接数、快速响应优先等(正确答案)C.LVS 是一个虚拟的服务器集群,工作在网络体系第七层,采用 IP 负载均衡技术和基于内容请求分发技术第四层D.LVS 集群主要由负载调度器、服务器池(server pool/ Realserver)、共享存储(shared storage)三部分组成(正确答案)50.以下对 LVS+tomcat 集群模型理解正确的是多选()A.LVS-NAT,网络地址转换 NetworkAddress Translation,修改请求报文的目标IP(正确答案)B.像这种在 Linux 内核中实现的负载调度技术,我们称之为 Linux 虚拟服务器(LVS)(正确答案)C.LVS-DR:直接路由 Direct Routing,操纵封装新的 MAC 地址(正确答案)D.LVS-TUN:IP 隧道 IP Tunneling,在原请求 IP 报文之外新加一个 P 首部(正确答案)51.以下关于无状态计算管理理解错误的是() [单选题]A.不依赖框外管理工具也可直接完框内全部基本配置管理B.可简化交换板的网络特性,便于以后扩展支持其它交换板C.当基本的配置管理扩展到单柜时,仍不需要依框外管理工具来配置D.支持状态无关的计算,做到同规格的硬件更换时,需要额外的配置(正确答案)52.集群是一组协同工作的服务实体,通过提高单位时,执行的任务数来提升效率() [单选题]A.对(正确答案)B.错53.以下关于异构计算特点理解正确的是()A.GPU 和 CPU 协同工作可组成异构计算系统,异构计算的优势为计算加速和节(正确答案)B.常见的异构系统架构有,CPU+ GPU. GPU + FPGA,CPU +专用芯片C.异构计算的目的主要是为了解决 CPU 计算能力不足的问题(正确答案)D.异构计算就是制定出一系列软件与硬件的标准,让不同类型的计算设备能够共享计算的过程和结果(正确答案)54.由一个或若干个通用计算单元加一个或若干个专用计算单元构建的系统就是异构计算系统,异构系统执行通用计算任务的计算方式就是异构计算() [单选题]A.对(正确答案)B.错55.Puppet 和 Ansib1e 都属于自动化运维管理工具,对这两个运维工具理解错误的是() [单选题]A. Ansible 最大的特点是不需要在对接设备上安装代理B. Puppet 可支持的资源类型包括文件、安装包、计划任务、用户管理等C. Ansible 用 Python 语言编写,默认使用 SSH 密钥进行验证D.相对于 Ansible, Puppet 远程主机无需客户端(正确答案)56.以下关于 HPC 高性能计算的说法错误的是() [单选题]A.早期 HPC 基于定制计算机,专用于基础科学研究和国防战略等特定领域,随着技术的发展,现在绝大部分 HPC 基于 X86 服务器的集群架构进行构成B.HPC 即高性能计算,指以计算为目的,使用了很多处理器的单个计算机系统或使用了多台计算机集群的计算系统和环境C.HPC 就是超级计算,是用计算机去研究、设计产品及支持复杂的决策(正确答案)D.HPC 计算集群主要由计算服务器、共享存储、高速互连设备以及配套的管理软件、平台软件和应用软件构成57.云计算常用的部署模式有哪些()A.混合云计算(正确答案)B.社区云计算(正确答案)C.公有云计算(正确答案)D.私有云计算(正确答案)58.以下关于 HPC 系统的基本构成的主要模块中,哪个不具备应用场景专属性()[单选题]A.操作系统B.开发工具C.中间件D.作业管理(正确答案)59.Azure Stack 是微软公有云平台 Azure 的延伸,是微软的混合云解决方案 [单选题]A.对(正确答案)B.错60.华为海思公司参与芯片产业链中的哪个角色() [单选题]A.终端应用B.芯片设计(正确答案)C.芯片制造D.芯片封装测试61.下列关于 CISC 和 RISC 的对比中说法正确的是()A.CISC 比 RISC 的指令系统更复杂(正确答案)B.CISC 对存储器的控制指令更多(正确答案)C.CISC 程序需要大内存空间,不易设计D.CISC 芯片设计周期短62.ARMv7 架构以后, ARM 的处理器架构命名改为 Cortex,华为自研的手机处理器芯片麒麟使用的是哪种ARM 架构() [单选题]A.Cortex-A(正确答案)B.Cortex-MC.Cortex-R63.下列不属于 FPGA 的应用场景的是() [单选题]A.电信设备芯片(正确答案)B.NFV 通用服务器性能提升C.云计算加速服务D.PaaS 服务64.下列关于 FPGA 优势的说法中正确的是()A.通用处理器,研发周期最短B.适用图形及视频处理C.适合深度定制,可快速上线(正确答案)D.适用于不规则并行计算,实时性好,能效比高(正确答案)65.《硅谷秘史》的作者,精益创业之父 Steve Blank 2018 年撰文指出,摩尔定早在十年前就已经失效了,只是消费者还未察觉,下列分析摩介定律失效的原因正确的是。

计算机组成原理第四五章答案

期末试卷(四、五、六章)一、选择题(每小题1分)1 单地址指令中为了完成两个数的算术运算,除地址码指明的一个操作数外,另一个常需采用(C )。

A 堆栈寻址方式B 立即寻址方式C 隐含寻址方式D 间接寻址方式2 RISC访内指令中,操作数的物理位置一般安排在( D )。

A 栈顶和次栈顶B 两个主存单元C 一个主存单元和一个通用寄存器D 两个通用寄存器3寄存器间接寻址方式中,操作数在(B )。

A 通用寄存器B 主存单元C 程序计数器 D 堆栈4 机器指令与微指令之间的关系是(A )。

A 用若干条微指令实现一条机器指令B 用若干条机器指令实现一条微指令C 用一条微指令实现一条机器指令D 用一条机器指令实现一条微指令5描述多媒体CPU基本概念中,不正确的是( D )。

A 多媒体CPU是带有MMX技术的处理器B MMX是一种多媒体扩展结构C MMX指令集是一种多指令流多数据流的并行处理指令D 多媒体CPU是以超标量结构为基础的CISC机器6 流水线中造成控制相关的原因是执行( A )指令而引起。

A 条件转移B 访内C 算逻D 无条件转移7 PCI总线是一个高带宽且与处理器无关的标准总线。

下面描述中不正确的是(B )。

A 采用同步定时协议B 采用分布式仲裁策略C 具有自动配置能力D 适合于低成本的小系统8 同步控制是( C )。

A 只适用于CPU控制的方式B 只适用于外围设备控制的方式C 由统一时序信号控制的方式D 所有指令执行时间都相同的方式9 描述PCI总线中基本概念不正确的句子是(CD )。

A PCI总线是一个与处理器无关的高速外围设备B PCI总线的基本传输机制是猝发式传送C PCI设备一定是主设备D 系统中只允许有一条PCI总线10当前的CPU由( B )组成。

A 控制器B 控制器、运算器、cacheC 运算器、主存D 控制器、ALU、主存11流水CPU是由一系列叫做“段”的处理部件组成。

和具备m个并行部件的CPU相比,一个m段流水CPU的吞吐能力是( D )。

单片微型计算机原理及应用_课后习题答案

《单片微型计算机原理及应用》习题参考答案姜志海刘连鑫王蕾编著电子工业出版社目录第1章微型计算机基础 (2)第2章半导体存储器及I/O接口基础 (4)第3章MCS-51系列单片机硬件结构 (11)第4章MCS-51系列单片机指令系统 (16)第5章MCS-51系列单片机汇编语言程序设计 (20)第6章MCS-51系列单片机中断系统与定时器/计数器 (26)第7章MCS-51系列单片机的串行口 (32)第8章MCS-51系列单片机系统扩展技术 (34)第9章MCS-51系列单片机键盘/显示器接口技术 (36)第10章MCS-51系列单片机模拟量接口技术 (40)第11章单片机应用系统设计 (44)第1章微型计算机基础1.简述微型计算机的结构及各部分的作用微型计算机在硬件上由运算器、控制器、存储器、输入设备及输出设备五大部分组成。

运算器是计算机处理信息的主要部分;控制器控制计算机各部件自动地、协调一致地工作;存储器是存放数据与程序的部件;输入设备用来输入数据与程序;输出设备将计算机的处理结果用数字、图形等形式表示出来。

通常把运算器、控制器、存储器这三部分称为计算机的主机,而输入、输出设备则称为计算机的外部设备(简称外设)。

由于运算器、控制器是计算机处理信息的关键部件,所以常将它们合称为中央处理单元CPU(Central Process Unit)。

2.微处理器、微型计算机、微型计算机系统有什么联系与区别?微处理器是利用微电子技术将计算机的核心部件(运算器和控制器)集中做在一块集成电路上的一个独立芯片。

它具有解释指令、执行指令和与外界交换数据的能力。

其内部包括三部分:运算器、控制器、内部寄存器阵列(工作寄存器组)。

微型计算机由CPU、存储器、输入/输出(I/O)接口电路构成,各部分芯片之间通过总线(Bus)连接。

以微型计算机为主体,配上外部输入/输出设备、电源、系统软件一起构成应用系统,称为微型计算机系统。

计算机组成原理试题及答案

计算机组成原理题集含答案题库题目总数:293第一章单选题1、控制器、运算器和存储器合起来一般称为(主机):I/O部件内存储器外存储器主机2、冯•诺依曼机工作方式的基本特点是(按地址访问并顺序执行指令):按地址访问并顺序执行指令精确结果处理存储器按内部地址访问自动工作3、输入、输出设备以及辅助存储器一般统称为(外围设备):I/O系统外围设备外存储器执行部件4、计算机硬件能直接识别和执行的语言是(机器语言):高级语言汇编语言机器语言符号语言判断题5、若某计算机字代表一条指令或指令的一部分,则称数据字(错)。

6、若某计算机字是运算操作的对象,即代表要处理的数据,则称指令字(错)。

7、数字计算机的特点:数值由数字量(如二进制位)来表示,运算按位进行.(对)8、模拟计算机的特点:数值由连续量来表示,运算过程是连续的。

(对)填空题9、系统软件包括:服务程序、语言程序、(操作系统)、数据库管理系统。

10、计算机系统的发展按其核心部件采用器件技术来看经历了五代的变化,分别是(电子管)、(晶体管)、(集成电路)、(大规模集成电路)、(巨大规模集成电路)五个部分。

11、计算机系统是一个由硬件和软件组成的多级层次结构,这通常由(微程序级)、(一般机器级)、(操作系统级)、(汇编语言级)和(高级语言级)等组成,在每一级上都可以进行(程序设计).12、计算机的软件一般分为(系统软件)和(应用软件)两大部分.13、计算机的硬件基本组成包括(控制器)、(运算器)、(存储器)、(输入设备)和(输出设备)五个部分。

简答题14、什么是存储容量?什么是单元地址?存储器所有存储单元的总数称为存储器的存储容量。

灭个存储单元都有编号,称为单元地址。

15、什么是外存?简述其功能.外存:为了扩大存储容量,又不使成本有很大的提高,在计算机中还配备了存储容量更大的磁盘存储器和光盘存储器,称为外存储器,简称外存。

外存可存储大量的信息,计算机需要使用时,再调入内存。

基于cc2530无线数据采集

基于CC2530的无线数据的采集摘要随着信息和通信技术的迅速发展,人们的生活相应会发送很大的进步,对周围环境的要求越来越高,在环境监测中大规模的无线传感器通信系统应用将越发普遍。

ZigBee是一种新兴的无线传感器网络技术,专注于短距离,低速率的无线通信网络,使用全球免许可2.4GHZ频段,遵循IEEE802.15.4通信协议的个域网技术。

如今,ZigBee已经广泛的被应用于消费电子控制,能源监测,商业和室内自动化以及工业化生产过程中[1]。

数据采集是工业现场中应用最广的技术之一,企业在生产时需要实时监测电压、温度、压力、流量的变化。

现有的采集系统大多采用预先布线,通过有线方式进行数据采集,主要存在的问题有:扩展性较差、布线繁琐、不方便对移动设备监测,不能进行临时数据采集。

为此本文介绍了如何利用射频芯片CC2530与单片机实现基于ZigBee的无线数据采集系统。

以单片机和射频芯片CC2530为核心设计了低功耗的无线数据采集系统,文章介绍了ZigBee技术、并给出了基于ZigBee的无线数据采集系统的组成,最后通过使用CC2530芯片完成了采集节点、主控单元的硬件与软件设计,实现了数据的采集和无线传输。

关键词:ZigBee,IEEE802.15.4,CC2530,无线传感器网络,单片机1.Zigbee简介ZigBee是一种基于IEEE 802.15.4标准的无线协议,主要应用于低通信速率,低功耗设备的组网,支持250kbit/s的数据传输速率,可以实现一点对多点的快速组网。

ZigBee技术的主要优点有省电、可靠、成本低、时延短、网络容量大、安全。

完整的ZigBee协议栈由物理层、介质访问控制层、网络层、安全层和应用层组成。

IEEE 802.15.4定义了物理层和介质访问控制层协议, 网络层和安全层由ZigBee联盟制定,应用层根据用户自己需要,对其进行开发利用。

无线通信技术上,采用免冲突多载波信道接入(CSMA-CA)方式避免了无线电载波之间冲突。

2022年南开大学《并行程序设计》在线作业-00001

2022年南开大学《并行程序设计》在线作业-00001对于效率E,下面描述错误的是____。

A:理想并行E=1B:总是在0~1之间C:可能>1D:可能随着处理器数量增大趋向于0正确选择:BOpenMP相对于Pthread的优点是____。

A:功能更强大B:可达更高并发度C:可降低通信开销D:由编译器生成线程创建和管理代码,更简单正确选择:Dpthread_join的作用是____。

A:强制终止指定线程B:检测指定线程是否结束C:等待指定线程结束才返回D:向指定线程发送数据正确选择:C在使用条件变量之后必须对其进行____。

A:初始化B:加锁C:解锁D:销毁正确选择:D在SSE intrinsics程序中整数数据类型是____。

A:__m128B:__m128fC:__m128dD:__m128i正确选择:D控制流语句进行SIMD并行化很困难的原因是控制流语句导致____。

A:连续数据执行不同指令B:连续数据执行相同指令C:同一数据执行不同指令D:同一数据执行相同指令正确选择:ACUDA共享内存是由____共享。

A:Grid中所有线程B:一个Block中所有线程C:一个Warp中所有线程D:GPU中所有线程正确选择:B在使用条件变量之前必须对其进行____。

A:初始化B:加锁C:解锁D:销毁正确选择:A在SSE intrinsics程序中单精度浮点数数据类型是____。

A:__m128B:__m128fC:__m128dD:__m128i正确选择:A和一对多广播对应的组通信操作是____。

A:多对一收集B:多对多收集C:多对一归约D:多对多归约正确选择:C竞争条件是指程序执行过程中两个或多个事件的____影响执行结果。

A:时序B:时长C:结果D:运算对象正确选择:A下面矩阵运算中,哪个进行简单的数据并行效果不佳____。

A:矩阵求和B:矩阵相乘C:矩阵向量相乘D:高斯消去正确选择:DCPU cache大小为32KB,如希望(单精度浮点数)矩阵乘法计算过程中所有数据都驻留cache中,则矩阵大小最大为A:16*16B:32*32C:64*64D:128*128正确选择:C关于MPI_recv对消息的区分,下列说法正确的是____。

计算机体系结构期末试题-湖南城市学院

题一11.计算机系统结构的层次结构由高到低分别为应用语言机器级,高级语言机器级,汇编语言机器级,操作系统机器级,传统机器语言机器级,微程序机器级12.计算机系统弗林(Flynn)分类法,把计算机系统分成单指令流单数据流(SISD)、单指令流多数据流(SIMD)、多指令单数据流和多指令多数据流四大类。

13.透明指的是客观存在的事物或属性从某个角度看不到,它带来的好处是简化某级的设计,带来的不利是无法控制。

22.数据结构和数据表示之间是什么关系?确定和引入数据表示的基本原则是什么?数据表示是能由硬件直接识别和引用的数据类型。

数据结构反映各种数据元素或信息单元之间的结构关系。

数据结构要通过软件映象变换成机器所具有的各种数据表示实现,所以数据表示是数据结构的组成元素。

(2分)不同的数据表示可为数据结构的实现提供不同的支持,表现在实现效率和方便性不同。

数据表示和数据结构是软件、硬件的交界面。

(2分)除基本数据表示不可少外,高级数据表示的确定和引入遵循以下原则:(1)看系统的效率有否提高,是否减少了实现时间和存储空间。

(2)看引入这种数据表示后,其通用性和利用率是否高。

15.引入数据表示的两条基本原则是:一看系统的效率有否提高;二看数据表示的通用性和利用率是否高。

13.计算机组成指的是计算机系统结构的逻辑实现,包括机器级内的数据流和控制流的组成及逻辑设计等。

计算机实现指的是计算机组成的物理实现,。

21、软件和硬件在什么意义上是等效的?在什么意义上是不等效的?逻辑上等效,性能、价格、实现难易程度上不一样。

22.说明翻译和解释的区别和联系.区别:翻译是整个程序转换,解释是低级机器的一串语句仿真高级机器的一条语句。

联系:都是高级机器程序在低级机器上执行的必须步骤。

19.计算机系统结构也称计算机体系结构,指的是传统机器级的系统结构。

它是软件和硬件/固件的交界面,是机器语言汇编语言程序设计者或编译程序设计者看到的机器物理系统的抽象。

生活中应用射频技术的案例

生活中应用射频技术的案例1.零辐射——潍坊市人民医院心内科电生理射频技术不断突破近期,医院心内一科完成一例腔内超声指导下零射线房颤射频消融术,标志着医院在房颤射频消融术方面达到了新的高度,电生理技术不断突破。

医院心内科自1995年开展二维DSA下行隐匿性左侧旁道射频消融开始,2010年由“二维”升级“三维”,在全市率先开展“三维标测系统”指导下射频消融术,随后陆续独立开展房颤、房扑、房速、室早、室速等复杂心律失常,至今已累计完成射频消融术2000余例,其中三维手术1500余例,房颤、房速、室早、室速等复杂心律失常近千例。

2020年,心内科完成全市首例“零射线”操作下射频消融术。

一年来,随着术式的完善,经验的提高,科室电生理技术不断突破。

传统的房颤射频消融术需要在X射线透视下进行操作,透视时间长、射线量大,对患者和医生都有一定程度的辐射损伤。

最新的国际发展术式,可以借由“腔内超声”指导上述步骤,达到完全零射线、零辐射下完成手术,不开刀,无缝线,术后患者恢复快速,一般观察2天康复出院。

2.在公安领域中的应用(1)、交通管控上的RFIDETC系统,即通常所说的不停车收费系统,它是以现代通信技术、电子技术、自动控制技术、计算机和网络技术等高新技术为主导,实现车辆不停车自动收费的智能交通电子系统。

当装有RFID标签的车辆在距离0~10米范围内接近ETC读写器时,ETC 读写器受控发出微波查询信号,安装在受查车辆固定位置的电子标签收到读写器的查询信号后,将此信号与电子标签自身的数据信息(如高速里程)反射回读卡器。

这种技术无疑可以减少人为的乱收费现象,同时提高通关速度、防止堵车。

这显然已是一种物联网了。

ETC系统要求RFID能够实现至少十米的远距离识别。

由于技术要求和实际情况的不同,所采用的读卡器的型号也不同。

日本、美国、中国等大多数国家的标准定在5.8~5.9GHz频段。

在我国选用5.8GHz频段具有如下优点:首先,我国通信系统标准体系靠近欧洲体系,无线电频率资源的分配大致相同。

2022年职业考证-软考-嵌入式系统设计师考试全真模拟全知识点汇编押题第五期(含答案)试卷号:74

2022年职业考证-软考-嵌入式系统设计师考试全真模拟全知识点汇编押题第五期(含答案)一.综合题(共15题)1.单选题总线主设备指的是()。

问题1选项A.总线上的智能设备B.总线目标设备C.可申请并能获得总线使用权的设备D.总线控制器【答案】C【解析】连接在总线上的单元电路被称为总线设备。

在这些设备中,控制信息传送的总线设备称为总线主设备(即获得总线控制权的设备)。

接受总线主设备控制的设备称为从设备。

2.单选题DMA是一种高速的数据传输模式,下列描述中,错误的是()。

问题1选项A.DMA传输方式可以产生中断B.DMA传输过程主要由硬件来实现C.DMA传输过程包含3个阶段:申请阶段、响应阶段和数据传输阶段D.DMA操作可以通过软件来启动,也可以通过内部部件的请求来启动【答案】C【解析】输入/输出技术的三种方式:直接查询控制:有无条件传送和程序查询方式,都需要通过CPU执行程序来查询外设的状态,判断外设是否准备好接收数据或准备好了向CPU输入的数据。

在这种情况下CPU不做别的事情,只是不停地对外设的状态进行查询。

中断方式:当I/O系统与外设交换数据时,CPU无须等待也不必查询I/O的状态,而可以抽身来处理其他任务。

当I/O系统准备好以后,则发出中断请求信号通知CPU,CPU接到中断请求信号后,保存正在执行的程序的现场,转入I/O中断服务程序的执行,完成于I/O系统的数据交换,然后再返回被打断的程序继续执行。

与程序控制方式相比,中断方式因为CPU无需等待而提高了效率。

DMA:直接寄存器存取方式,是指数据在内存与I/O设备间的直接成块传送,即在内存与I/O设备间传送一个数据块的过程中,不需要CPU的任何干涉,只需要CPU正在过程开始启动与过程结束时的处理,实际操作由DMA硬件直接执行完成。

DMA传输方式可以产生中断;DMA传输过程主要由硬件来实现;DMA操作可以通过软件来启动,也可以通过内部部件的请求来启动;DMA传输过程包含4个阶段:请求阶段、响应阶段、传输阶段和结束阶段。

基于“神威·太湖之光”的数据密集型计算并行优化

计算通信优化与协同计算策略

计算通信优化

采用高效的通信协议和算法,减少计算节点之间的通信开销,提高系统整体的协同计算能力。

协同计算

将多个计算节点联合起来,协同解决一个大规模的计算问题,充分利用计算资源和加速问题解决进程 。

05

基于“神威·太湖之光”的数据 密集型计算并行优化实验与分析

实验设计

实验目的

计算资源需求

数据密集型计算需要大量 的计算资源,如何满足不 断增长的计算需求是另一 个挑战。

算法优化

针对不同的应用领域,需 要对算法进行优化,以提 高计算效率和准确性。

03

“神威·太湖之光”超级计算机

“神威·太湖之光”的硬件架构

处理器

使用国产申威处理器,采 用64位自主指令集。

架构

基于多核多线程架构,每 个处理器核心都具有独立 的计算和内存单元。

数据压缩与缓存策略

压缩数据

使用压缩算法对数据进行压缩,以减少存储空间和提高传输效率。

缓存数据

将频繁访问的数据存储在高速缓存中,以减少访问时间和提高系统性能。

并行任务调度与负载均衡策略

并行任务调度

使用多线程、多进程等技术将任务分解为多个子任务,并分配到不同的处理单元上执行,以提高处理速度。

负载均衡

基于“神威·太湖之光”的数据密集 型计算并行优化

2023-11-10

目录

• 引言 • 数据密集型计算概述 • “神威·太湖之光”超级计算机 • 基于“神威·太湖之光”的数据

密集型计算并行优化策略

目录

• 基于“神威·太湖之光”的数据 密集型计算并行优化实验与分析

• 结论与展望

01

引言

研究背景与意义

数据密集型计算概述

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

微捷码软件应用于高-性髓并行计算系统中复杂交换芯片的物理实现HuaShenl,DingshanYoul,XiaoxiaoJian91.-,LikeLiul,JiaYan91,一,RongrongQu01・2(1.中国科学院计算技术研究所;2.中国科学院研究生院)★摘要:本文主要介绍了面向并行计算系统互连应用的复杂交换芯片(SwitchhSlC)的芯片结构、设计权衡和物理实现。

该交换芯片通过集成3路16x16交叉开关和特别垫垒处理单元,不仅可支持具有高吞吐量和低延迟的多层多功能包交换,而且还在其16个RX/TX端口间提供了先进的全局垫垒处理加速功能:以156.25MHz频率运行,拥有80Gbps端口交换和2406bps内部包交换容量以及3.12Gbps的端口吞吐量。

通过对一些芯片路径多模多角下时序的仔细调整以及对输出片上时钟网络的0CV优化,以微捷码的B1ast工具为主达成了4种功能模式、3个PVT角点下芯片物理实现的完全时序收敛。

目前,该芯片已通过0.18um/6MetalCMOS技术完成投片,拥有约2000万个晶体管、17个不同的时钟域、48个RAM宏块、12.39mmx12.39mm芯片尺寸以及1053个引脚倒装芯片封装。

关键词:高性能、交换、时序收敛、CDC、多模、OCV、OFT1D5000SwitchASIC的结构D5000SwitchASIC是作为一款应用于高性能、高效率大型计算系统【11的关键互连芯片而设计。

在大型计算系统的建造中,高度可扩展的互连光纤(interconnectfabric)技术起着重要作用;为增强互连光纤的可扩展性,它不仅必须集中优化光纤的拓扑结构、光纤交换芯片的带宽、延迟、端口吞吐量,而且还需改善交换芯片的全局同步机制和功能。

D5000SwitchASIC是一款高性能多功能交换芯片,支持源一目的地布线、流程控制、单播包和多播包交换以及专用于加速全局同步的垫垒处理。

D5000SwitchASIC的结构如图l所示,它拥有16个全双工RXgI'X端口,在每个RX端口各有3个应用于其进人数据包的VC(虚拟通道),且每个VC都与其在3个16x16交叉开关中的响应开关以及芯片内一个垫垒处理单元相连接。

具有多个VC和多个交叉开关的D5000SwitchASIC的多层式结构通过更好地调整以支持大型互连网络和计算系统上的并行应用,可改善高负载环境中流量堵塞并减小包交换延迟。

通过集成经专门设计的垫垒处理单元,这款交换芯片可显著降低全局垫垒通信延迟,特别是用于大型互连网络计算系统时更是如此,从而可改善并行算法和应用的可扩展性f21。

D5000SwitchASIC采用了O.18斗nlCMOS技术,已集成了约2000万个晶体管;以156.25MHz频率运行,拥有80Gbps端口交换和240Gbps内部包交换带宽以及3.125Gbps单向端口吞吐量;零负载・该项目由中国国家高技术研究开发计划提供经费资助,合同号为No.2006AA01A102.h¨^.,^……,’;m^,。

,、…万方数据端口到端口延迟小于100ns。

对于采用D5000SwitchASIC创建的1024节点互连网络,其硬件全局垫垒处理延迟在1“s以下,这个数字比目前市场中商用芯片Infiniband交换芯片效果好很多。

2DS000SwitchASlC的时序约束设计时序约束设计是成功ASIC物理设计的第一步,它直接关系到芯片功能的正确性以及芯片实现的质量。

对于D5()00SwitchASIC的时序约束设计,我们主要集中于芯片的时钟定义、输入输出端口约束以及内部CDC(跨时钟域)时钟约束。

D5000SwitchASIC具有如下特性:(1)17个运行频率达156.25MHz的时钟域(2)16个19位SSD(源同步数据)输入端口和16个19位SSD输出端口,所有时钟频率为156.25MHz。

clk一7(3)约4000个内部CDC信号,主要是RX与TX时钟域(RX和TX在此系指FIFO的接收端口和传输端口)间异步FIFO内并行地址指针(addresspointers)o(4)一个异步处理器双向总线接口。

2.1SSD输入和输出端口的时序约束D5000SwitchASIC的SSD型输出的结构如图2所示。

考虑到Serdes芯片的时序需求以及最大化输出数据有效时序窗口的要求,将输出时钟的上升沿(riseedge)调整到输出数据窗口中心来达成下列时序等式会具有更好效果:7I?。

ⅡL呻≥To+Toq+T‘皿,.啊“.一y+7I:dup(1)图1D5000SwitchASIC的结构、、~.,~r~……-,。

,‘,,T,ts_图205000¥witchASICSSD输出端13的结构凡柚≤1k柚+1凶+1k(2)LfThdd≤0.5木h(3)k<氏枷(4)对于芯片中SSD型输人端口,其结构如图3所示。

为了让输入数据窗口在从外部Serdes芯片送出后尽可能保持不变,要求在芯片内输入RX时钟路径的延迟与其相关的输入数据路径延迟最好相匹配,以下时序等式中对这些要求进行了定义:Td岫≥k+tq+Tdk,—。

咖(4)Td哪≤k+钆(5)I-‘●^,^....…:……一万方数据■———■HiT咖TⅢ!RX帅r]RX_唑!m门!刁io图3SSD型输入端口的结构2.2CDC接口的时序约束D5000SwitchASIC的CDC接口结构如图4所IXC1kRX—Clk图4CDC接口结构在D5000SwitchASIC中约有4000条CDC信号路径,其中多数是RX时钟域与TX时钟域间异步FIFO中并行地址指针。

为了降低跨时钟域数据交流期间亚稳态,这些并行FIFO地址位首先以格雷码(Graycoding)进行编码并在发送端寄存,然后采用双同步D触发器在其RX端取样。

对这种CDC路径广泛使用的时序约束是设置虚假路径(falsepath)。

当路径被作为虚假路径设置时,EDA工具将忽略它们,不会对这些虚假路径进行任何控制,因此对这些路径也就没有任何延迟匹配和控制问题。

在深亚微米ASIC中,芯片内逻辑门级电路间各种线路延迟问题已上升到了不容忽视的程度。

没有进行时序控制,这类并行CDC路径的时序可能从各方面导致所交流CDC数据正确性失效,包括FIFO接收方出现错误的数据取样。

这些都是出了名的芯片设计师难以调试的bug,因为其往往http://www.cicmag.com是随机发生的。

因此,为了将这类CDC失效机率降至最低,采用保守方式来执行CDC数据交流会更好,而且为了将错误取样机率降至最低,需约束这类并行CDC路径以让其时序控制在一定安全范围内。

在我们的案例中,我们使用如下时序等式来约束CDC路径:T‘赴珊≤Min(T诎删,T吲k删】(7)△k≤1/4Min{T蒯k删,Rd驯J(8)3D5000SwitchASIC的DFT设计该芯片集成2000万个晶体管并拥有1053个引脚,若没有在芯片中内嵌DIPI'(可测性设计)设计,那么对如此复杂ASIC进行测试要得到好的故障覆盖率是不可能的。

D5000SwitchASIC的DFF设计目标是制定出一款能采用通用逻辑分析器和向量产生器,通过片上JTAG接口在我们的实验室简单测试板上测试这款复杂ASIC的DFF解决方案,同时避免使用昂贵的ATE(自动测试设备)和专门设计的ATE负载板。

为达到这一目标,我们在D5000SwitchASIC中插入了扫描链(SCAN)、压缩扫描链(CompressedSCAN)、时速存储器内建自测试(At—speedMBIST)、边界扫描(BSCAN)和片上时钟控制器。

该芯片的DITF结构如图5所示。

通过集成这些DFT结构,所有测试矢量都可通过片上JTAG控制器轻松地加以控制、加载和捕捉。

对于粘粘(stack—at)故障,SCAN的覆盖率是96.45%、CompressedSCAN的覆盖率为95.90%,时速存储器内建自测试覆盖率为100%;对于桥接故障(bridgingfault),其测试覆盖率约为94%。

4D5000SwitchASlC的物理规划设计规划设计包括有IO规划、平面布局以及电源网万方数据图5D5000SwitchASIC的DFT结构格设计等。

D5000SwitchASIC的物理设计是以联电和舰(UMCHJ)的通用0.18IXm/6MCMOS技术为基础,同时使用了Faraday的标准单元库、PLL、可编程IO库、双端口寄存器堆编译器。

该芯片拥有48个17x2048位双端口寄存器堆宏单元、内嵌有一个PLL,同时它还拥有690个信号IO引脚,包括PWD/GND引脚在内的话引脚总数高达1053个,因此它属于引脚限制(Pad—limited)、IO密集型ASIC设计。

为了提供更好的IO信号完整性并将SSN(同步交换噪声)负面影响降至最低,我们选择了倒装芯片平面布局和封装。

压焊垫块(BumpPad)尺寸为130IXm×130IXm,使用M6金属层、间距为200斗m;锡球间距为1.0mm,使用12层封装基板、35mmX35mm尺寸的1053个锡球引脚。

所有端口的引脚均以成组方式分配,如图6所示。

为最小化芯片的电源网格中电压降(IR—Drop),使用M6/M5/M4进行电源网格布线,同时使用许多Power/GNDIOPad和宽电源环。

在交互迭代和优化后,最终的芯片平面布局如图7所示。

基于SAIF向量文件的功耗分析显示此交换芯片的功耗约为3—4W。

带有IO环的芯片内核尺寸约为9.8lnnlx9.8nlnl,带有压焊垫块阵列的芯片尺寸约为12.39pmx12.39斗m。

图6倒装芯片封装基板平面布局图7交换芯片平面布局5D5000SwitchASIC的物理设计细节D5000SwitchASIC的物理设计细节包括有许多方面:CTS、布局、布线、DRC/LVS和各种相关分析和验证。

在本文中,我们着重介绍了我们所遇到的难题以及设计过程中我们在该芯片的CTS、多模多角时序收敛以及OCV优化中所使用到的解决方案。

5.1时钟树设计对于D5000SwitchASIC的时钟树设计,它需对http://www.cicmag.tom万方数据16个输入时钟和一个芯片的核心时钟进行综合,每个时钟域建立独立的时钟树。

主要程序如下:(1)设置时钟树时序约束,如:定义每个时钟树的根点(rootpoint)和端点、定义相关的插入延迟、偏差、允许布线的金属层。

(2)设置允许仅为时钟树所用的单元,如:CLKINV、CLKBUF。

(3)基于偏差和余量需求来综合时钟树并进行优化。

(4)进行迭代直到时序收敛。

微捷码的Blast—fusion工具可基于偏差组(skewgroup)来综合并平衡时钟树,因此我们可如表1般定义偏差组。